Support & training

**CC2642R** SWRS194J - JANUARY 2018 - REVISED NOVEMBER 2023

# CC2642R SimpleLink<sup>™</sup> Bluetooth ® 5.2 Low Energy Wireless MCU

# 1 Features

- Microcontroller

- Powerful 48 MHz Arm<sup>®</sup> Cortex<sup>®</sup>-M4F processor

- EEMBC CoreMark® score: 148

- 352 kB of in-system programmable flash

- 256 kB of ROM for protocols and library functions

- 8 kB of cache SRAM (alternatively available as general-purpose RAM)

- 80 kB of ultra-low leakage SRAM. The SRAM is protected by parity to ensure high reliability of operation.

- 2-pin cJTAG and JTAG debugging

- Supports over-the-air (OTA) update

- Ultra-low power sensor controller with 4 kB of SRAM

- Sample, store, and process sensor data

- Operation independent from system CPU

- Fast wake-up for low-power operation

- TI-RTOS, drivers, bootloader, Bluetooth® 5.2 low energy controller in ROM for optimized application size

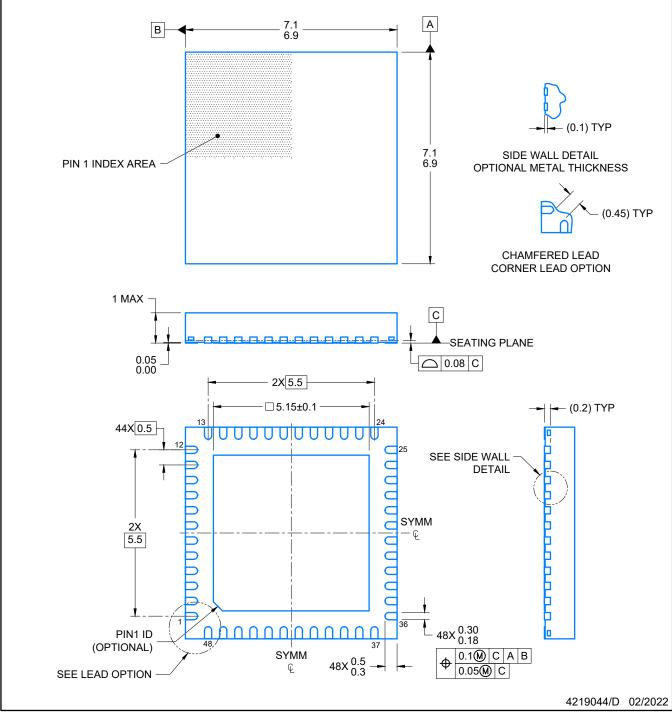

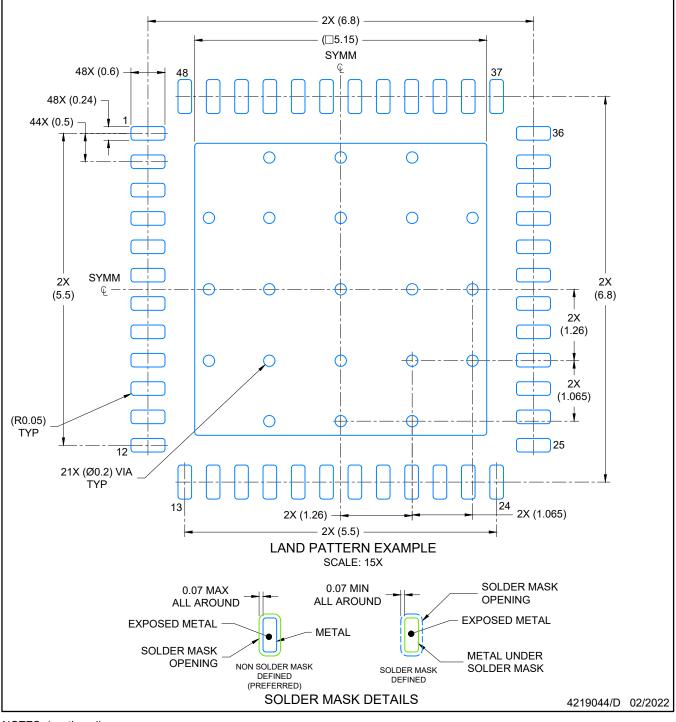

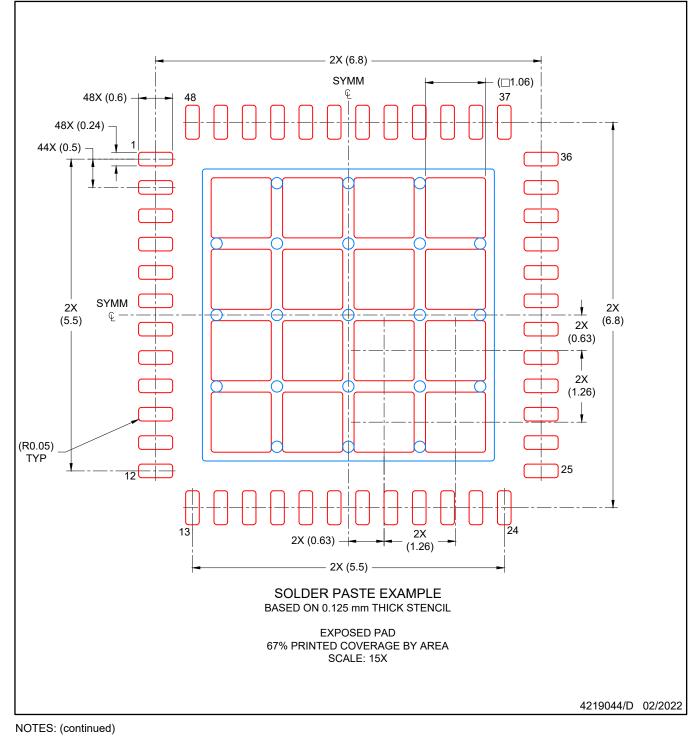

- **RoHS-compliant package**

- 7 mm × 7 mm RGZ VQFN48 (31 GPIOs)

- Peripherals

- Digital peripherals can be routed to any GPIO

- 4× 32-bit or 8× 16-bit general-purpose timers

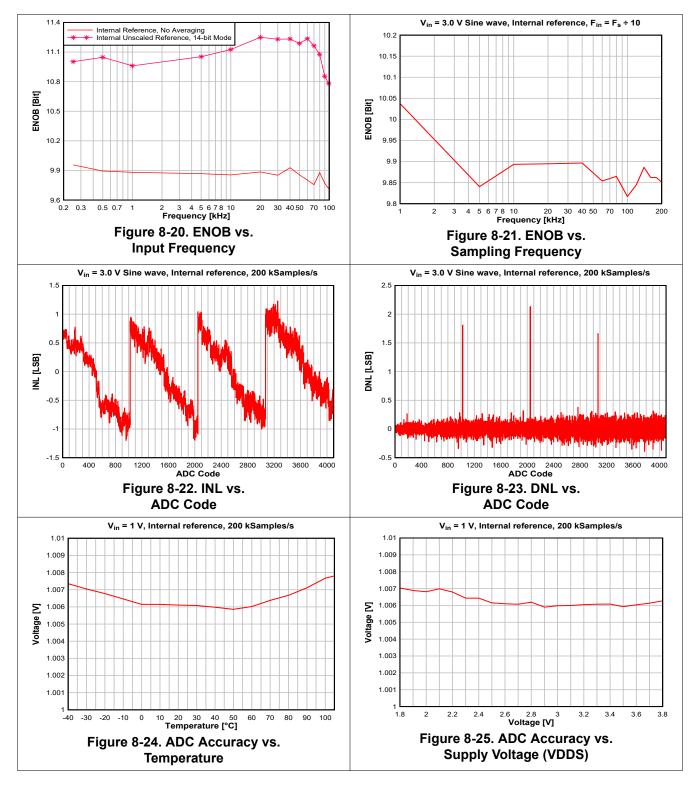

- 12-bit ADC, 200 kSamples/s, 8 channels

- 2× comparators with internal reference DAC (1× continuous time, 1× ultra-low power)

- Programmable current source

- 2× UART

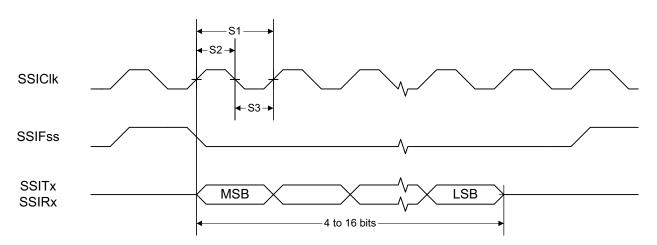

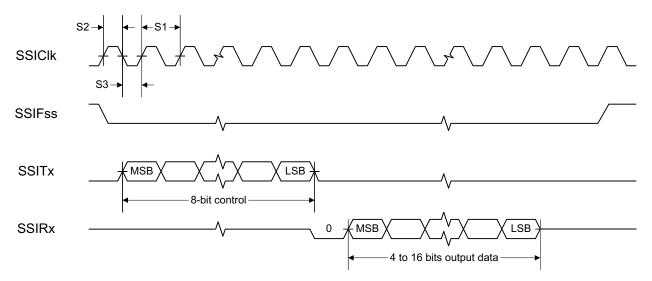

- 2× SSI (SPI, MICROWIRE, TI)

- I<sup>2</sup>C and I<sup>2</sup>S

- Real-time clock (RTC)

- AES 128- and 256-bit cryptographic accelerator

- ECC and RSA public key hardware accelerator

- SHA2 accelerator (full suite up to SHA-512)

- True random number generator (TRNG)

- Capacitive sensing, up to 8 channels

- Integrated temperature and battery monitor

- External system

- On-chip buck DC/DC converter

- Low power

- Active mode RX: 6.9 mA

- Active mode TX 0 dBm: 7.0 mA

- Active mode TX 5 dBm: 9.2 mA

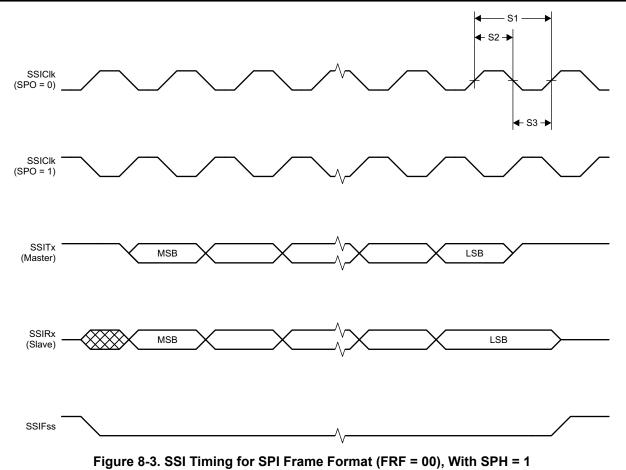

- Active mode MCU 48 MHz (CoreMark): 3.4 mA (71 µA/MHz)

- Sensor controller, low power-mode, 2 MHz, running infinite loop: 30.1 µA

- Sensor controller, active mode, 24 MHz, running infinite loop: 808 µA

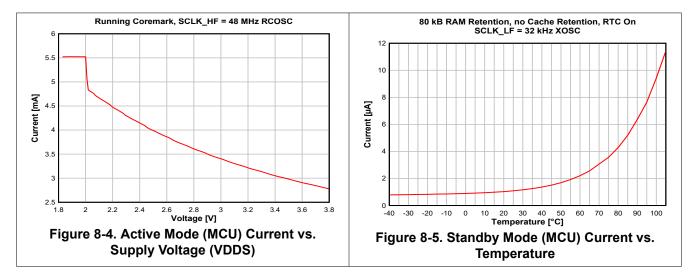

- Standby: 0.94 µA (RTC on, 80 kB RAM and CPU retention)

- Shutdown: 150 nA (wakeup on external events)

- Radio section

- 2.4 GHz RF transceiver compatible with Bluetooth 5.2 Low Energy and earlier LE specifications

- 3-wire, 2-wire, 1-wire PTA coexistence mechanisms

- Excellent receiver sensitivity: -105 dBm for Bluetooth 125 kbps (LE Coded PHY)

- -97 dBm for 1 Mbps PHY

- Output power up to +5 dBm with temperature compensation

- Suitable for systems targeting compliance with worldwide radio frequency regulations

- EN 300 328, (Europe)

- EN 300 440 Category 2

- FCC CFR47 Part 15

- ARIB STD-T66 (Japan)

- Development Tools and Software

- CC26x2R LaunchPad<sup>™</sup> Development Kit

- SimpleLink™ LOWPOWER F2 Software Development Kit (SDK)

- SmartRF<sup>™</sup> Studio for simple radio configuration

- Sensor Controller Studio for building low-power sensing applications

# 2 Applications

- Mobile phones battery pack for mobile phone

- Medical

- Building automation

- Building security systems motion detector, electronic smart lock, door and window sensor, garage door system, gateway

- HVAC thermostat, wireless environmental sensor, HVAC system controller, gateway

- Fire safety system smoke and heat detector, fire alarm control panel (FACP)

- Video surveillance IP network camera

- Factory automation and control

- Electronic point of sale (EPOS) RFID reader

- Grid infrastructure

- Smart meters water meter, gas meter, electricity meter, and heat cost allocators

- Grid communications wireless communications – Long-range sensor applications

- Other alternative energy energy harvesting

- Communication equipment

- Wired networking wireless LAN or Wi-Fi access points, edge router

- Personal electronics

- Portable electronics RF smart remote control

- Home theater & entertainment smart speakers, smart display, set-top box

- Connected peripherals consumer wireless module, pointing devices, keyboards and keypads

- Gaming electronic and robotic toys

- Wearables (non-medical) smart trackers, smart clothing

# 3 Description

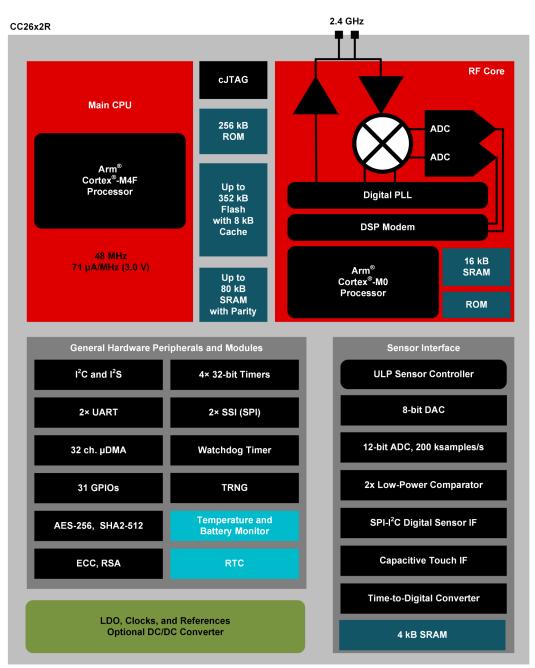

The SimpleLink<sup>™</sup> CC2642R device is a 2.4 GHz wireless microcontroller (MCU) supporting *Bluetooth*<sup>®</sup> 5.2 Low Energy and Proprietary 2.4 GHz applications. The device is optimized for low-power wireless communication and advanced sensing in building security systems, HVAC, asset tracking, medical, wired networking, portable electronics, home theater & entertainment, and connected peripherals markets markets, and applications where industrial performance is required. The highlighted features of this device include:

- Support for *Bluetooth* <sup>®</sup> 5.2 features: LE Coded PHYs (Long Range), LE 2 Mbit PHY (High Speed), Advertising Extensions, Multiple Advertisement Sets, CSA#2, Diirection Finding, as well as backwards compatibility and support for key features from the *Bluetooth* <sup>®</sup> 4.2 and earlier Low Energy specifications.

- Fully-qualified *Bluetooth* <sup>®</sup> 5.2 software protocol stack included with the SimpleLink™ LOWPOWER F2 Software Development Kit (SDK).

- Longer battery life wireless applications with low standby current of 0.94 µA with full RAM retention.

- Industrial temperature ready with lowest standby current of 11 μA at 105°C.

- Advanced sensing with a programmable, autonomous ultra-low power Sensor Controller CPU with fast wake-up capability. As an example, the sensor controller is capable of 1 Hz ADC sampling at 1 µA system current.

- Low SER (Soft Error Rate) FIT (Failure-in-time) for long operation lifetime with no disruption for industrial markets with always-on SRAM parity against corruption due to potential radiation events.

- Dedicated software controlled radio controller (Arm<sup>®</sup> Cortex<sup>®</sup>-M0) providing flexible low-power RF transceiver capability to support multiple physical layers and RF standards, such as real-time localization (RTLS) technologies.

- Excellent radio sensitivity and robustness (selectivity and blocking) performance for *Bluetooth* <sup>®</sup> Low Energy (-105 dBm for 125 kbps LE Coded PHY).

The CC2642R device is part of the SimpleLink<sup>™</sup> MCU platform, which consists of Wi-Fi<sup>®</sup>, *Bluetooth* Low Energy, Thread, Zigbee, Sub-1 GHz MCUs, and host MCUs. The CC2642R is part of a scalable portfolio with flash sizes from 32 kB to 704 kB with pin-to-pin compatible package options and share a common, easy-to-use development environment with a single core software development kit (SDK) and rich tool set. A one-time integration of the SimpleLink<sup>™</sup> platform enables you to add any combination of the portfolio's devices into your design, allowing a high degree of code reuse when your design requirements change. For more information, visit SimpleLink<sup>™</sup> MCU platform.

| Device Information         |           |                   |  |  |  |  |

|----------------------------|-----------|-------------------|--|--|--|--|

| PART NUMBER <sup>(1)</sup> | PACKAGE   | BODY SIZE (NOM)   |  |  |  |  |

| CC2642R1FRGZ               | VQFN (48) | 7.00 mm × 7.00 mm |  |  |  |  |

(1) For the most current part, package, and ordering information for all available devices, see the Package Option Addendum in Section 12, or see the TI website.

# **4 Functional Block Diagram**

# **Table of Contents**

| 1 | Features1                                         |

|---|---------------------------------------------------|

| 2 | Applications2                                     |

| 3 | Description2                                      |

| 4 | Functional Block Diagram3                         |

| 5 | Revision History4                                 |

|   | Device Comparison5                                |

| 7 | Terminal Configuration and Functions              |

|   | 7.1 Pin Diagram – RGZ Package (Top View)6         |

|   | 7.2 Signal Descriptions – RGZ Package7            |

|   | 7.3 Connections for Unused Pins and Modules8      |

| 8 | Specifications9                                   |

|   | 8.1 Absolute Maximum Ratings9                     |

|   | 8.2 ESD Ratings9                                  |

|   | 8.3 Recommended Operating Conditions9             |

|   | 8.4 Power Supply and Modules9                     |

|   | 8.5 Power Consumption - Power Modes 10            |

|   | 8.6 Power Consumption - Radio Modes 11            |

|   | 8.7 Nonvolatile (Flash) Memory Characteristics 11 |

|   | 8.8 Thermal Resistance Characteristics 11         |

|   | 8.9 RF Frequency Bands 11                         |

|   | 8.10 Bluetooth Low Energy - Receive (RX) 12       |

|   | 8.11 Bluetooth Low Energy - Transmit (TX)15       |

|   | 8.12 Timing and Switching Characteristics         |

|   | 8.13 Peripheral Characteristics20                 |

|   | 8.14 Typical Characteristics28                    |

| 9 | Detailed Description34                            |

|   | 9.1 Overview                                      |

|    | 9.2 System CPU                            | 34  |

|----|-------------------------------------------|-----|

|    | 9.3 Radio (RF Core)                       |     |

|    | 9.4 Memory                                | 35  |

|    | 9.5 Sensor Controller                     | .36 |

|    | 9.6 Cryptography                          | 36  |

|    | 9.7 Timers                                | .38 |

|    | 9.8 Serial Peripherals and I/O            | .39 |

|    | 9.9 Battery and Temperature Monitor       | 39  |

|    | 9.10 µDMA                                 | .39 |

|    | 9.11 Debug                                |     |

|    | 9.12 Power Management                     |     |

|    | 9.13 Clock Systems                        | 42  |

|    | 9.14 Network Processor                    |     |

| 1  | 0 Application, Implementation, and Layout |     |

|    | 10.1 Reference Designs                    |     |

|    | 10.2 Junction Temperature Calculation     |     |

| 1  | 1 Device and Documentation Support        |     |

|    | 11.1 Tools and Software                   |     |

|    | 11.2 Documentation Support                |     |

|    | 11.3 Support Resources                    |     |

|    | 11.4 Trademarks                           |     |

|    | 11.5 Electrostatic Discharge Caution      |     |

|    | 11.6 Glossary                             | 48  |

| 1: | 2 Mechanical, Packaging, and Orderable    |     |

|    | Information                               |     |

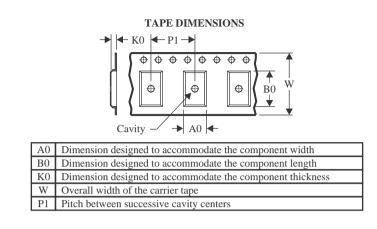

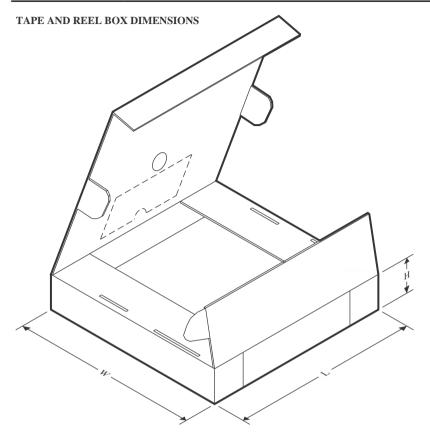

|    | 12.1 Packaging Information                | 49  |

|    |                                           |     |

# **5 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| (November 2023)) | Changes from June 12, 2023 to November 28, 2023 (from Revision I (June 2023) to Revision J |  |

|------------------|--------------------------------------------------------------------------------------------|--|

|                  | (November 2023))                                                                           |  |

| • | Updated Radio consumption (TX currents)                                                          | 1              |   |

|---|--------------------------------------------------------------------------------------------------|----------------|---|

|   | Updated SDK to new naming convention and updated the URL throughout the document                 |                |   |

| • | Updated unit formatting throughout the document                                                  | 1              |   |

| • | Added details about memory scalability in Section 3                                              | 2              | ) |

| • | Updated Device Comparison table                                                                  | 5              | 5 |

|   | Updated typical Tx currents in Section 8.6, Power Consumption - Radio Modes                      |                |   |

| • | Added footnote about DAC output impedance in Section 8.13.2.1, Digital-to-Analog Converter (DAC) |                |   |

|   | Characteristics                                                                                  | <mark>9</mark> | ) |

| • | Updated Typical TX Current and Output Power                                                      | 30             | ) |

| • | Added EnergyTrace information to Section 9.11                                                    | 39             | ) |

|   |                                                                                                  |                |   |

Page

# 6 Device Comparison

|                         |                 |              |                | F            | RADIO        | SUP          | PORT          | Г            |              |               |              |               |                        | PACKAGE SIZE |                    |                    |                    |                    |                    |                    |

|-------------------------|-----------------|--------------|----------------|--------------|--------------|--------------|---------------|--------------|--------------|---------------|--------------|---------------|------------------------|--------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| Device                  | Sub-1 GHz Prop. | 2.4GHz Prop. | Wireless M-Bus | mioty        | Wi-SUN®      | Sidewalk     | Bluetooth® LE | ZigBee       | Thread       | Multiprotocol | +20 dBm PA   | FLASH<br>(kB) | RAM +<br>Cache<br>(kB) | GPIO         | 4 × 4 mm VQFN (24) | 4 × 4 mm VQFN (32) | 5 × 5 mm VQFN (32) | 5 × 5 mm VQFN (40) | 7 × 7 mm VQFN (48) | 8 × 8 mm VQFN (64) |

| CC1310                  | $\checkmark$    |              | $\checkmark$   | $\checkmark$ |              |              |               |              |              |               |              | 32-128        | 16-20 + 8              | 10-30        |                    | $\checkmark$       | $\checkmark$       |                    | $\checkmark$       |                    |

| CC1311R3                | $\checkmark$    |              | $\checkmark$   | $\checkmark$ |              |              |               |              |              |               |              | 352           | 32 + 8                 | 22-30        |                    |                    |                    | $\checkmark$       | $\checkmark$       |                    |

| CC1311P3                | $\checkmark$    |              | $\checkmark$   | $\checkmark$ |              |              |               |              |              |               | $\checkmark$ | 352           | 32 + 8                 | 26           |                    |                    |                    |                    | $\checkmark$       |                    |

| CC1312R                 | $\checkmark$    |              | $\checkmark$   | $\checkmark$ | $\checkmark$ |              |               |              |              |               |              | 352           | 80 + 8                 | 30           |                    |                    |                    |                    | $\checkmark$       |                    |

| CC1312R7                | $\checkmark$    |              | $\checkmark$   | $\checkmark$ | $\checkmark$ | $\checkmark$ |               |              |              | $\checkmark$  |              | 704           | 144 + 8                | 30           |                    |                    |                    |                    | $\checkmark$       |                    |

| CC1314R10               | $\checkmark$    |              | $\checkmark$   | $\checkmark$ | $\checkmark$ | $\checkmark$ |               |              |              | $\checkmark$  |              | 1024          | 256 + 8                | 30-46        |                    |                    |                    |                    | $\checkmark$       | $\checkmark$       |

| CC1352R                 | $\checkmark$    | $\checkmark$ | $\checkmark$   | $\checkmark$ | $\checkmark$ |              | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$  |              | 352           | 80 + 8                 | 28           |                    |                    |                    |                    | $\checkmark$       |                    |

| CC1354R10               | $\checkmark$    | $\checkmark$ | $\checkmark$   | $\checkmark$ | $\checkmark$ |              | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$  |              | 1024          | 256 + 8                | 28-42        |                    |                    |                    |                    | $\checkmark$       | $\checkmark$       |

| CC1352P                 | $\checkmark$    | $\checkmark$ | $\checkmark$   | $\checkmark$ | $\checkmark$ |              | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$  | V            | 352           | 80 + 8                 | 26           |                    |                    |                    |                    | $\checkmark$       |                    |

| CC1352P7                | $\checkmark$    | $\checkmark$ | $\checkmark$   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$  | V            | 704           | 144 + 8                | 26           |                    |                    |                    |                    | $\checkmark$       |                    |

| CC1354P10               | $\checkmark$    | $\checkmark$ | $\checkmark$   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$  | $\checkmark$ | 1024          | 256 + 8                | 26-42        |                    |                    |                    |                    | $\checkmark$       |                    |

| CC2340R5 <sup>(1)</sup> |                 | $\checkmark$ |                |              |              |              | $\checkmark$  | $\checkmark$ | $\checkmark$ |               |              | 512           | 36                     | 12-26        | $\checkmark$       |                    |                    | V                  |                    |                    |

| CC2640R2F               |                 |              |                |              |              |              | $\checkmark$  |              |              |               |              | 128           | 20 + 8                 | 10-31        |                    | $\checkmark$       | $\checkmark$       |                    | $\checkmark$       |                    |

| CC2642R                 |                 |              |                |              |              |              | $\checkmark$  |              |              |               |              | 352           | 80 + 8                 | 31           |                    |                    |                    |                    | $\checkmark$       |                    |

| CC2642R-Q1              |                 |              |                |              |              |              | $\checkmark$  |              |              |               |              | 352           | 80 + 8                 | 31           |                    |                    |                    |                    | $\checkmark$       |                    |

| CC2651R3                |                 | $\checkmark$ |                |              |              |              | $\checkmark$  | $\checkmark$ |              |               |              | 352           | 32 + 8                 | 23-31        |                    |                    |                    | $\checkmark$       | $\checkmark$       |                    |

| CC2651P3                |                 | $\checkmark$ |                |              |              |              | $\checkmark$  | $\checkmark$ |              |               | $\checkmark$ | 352           | 32 + 8                 | 22-26        |                    |                    |                    | $\checkmark$       | $\checkmark$       |                    |

| CC2652R                 |                 | $\checkmark$ |                |              |              |              | $\checkmark$  |              | $\checkmark$ | $\checkmark$  |              | 352           | 80 + 8                 | 31           |                    |                    |                    |                    | $\checkmark$       |                    |

| CC2652RB                |                 | $\checkmark$ |                |              |              |              | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$  |              | 352           | 80 + 8                 | 31           |                    |                    |                    |                    | $\checkmark$       |                    |

| CC2652R7                |                 | $\checkmark$ |                |              |              |              | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$  |              | 704           | 144 + 8                | 31           |                    |                    |                    |                    | $\checkmark$       |                    |

| CC2652P                 |                 | $\checkmark$ |                |              |              |              | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$  | $\checkmark$ | 352           | 80 + 8                 | 26           |                    |                    |                    |                    | $\checkmark$       |                    |

| CC2652P7                |                 | $\checkmark$ |                |              |              |              | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$  | $\checkmark$ | 704           | 144 + 8                | 26           |                    |                    |                    |                    | $\checkmark$       |                    |

| CC2674R10               |                 | $\checkmark$ |                |              |              |              | $\checkmark$  |              | $\checkmark$ | $\checkmark$  |              | 1024          | 256 + 8                | 31-45        |                    |                    |                    |                    | $\checkmark$       |                    |

| CC2674P10               |                 | $\checkmark$ |                |              |              |              | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$  |              | 1024          | 256 + 8                | 26-45        |                    |                    |                    |                    | $\checkmark$       |                    |

(1) ZigBee and Thread support enabled by future software update

# 7 Terminal Configuration and Functions

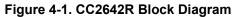

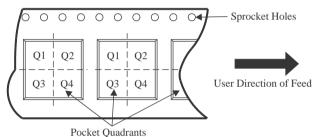

# 7.1 Pin Diagram – RGZ Package (Top View)

Figure 7-1. RGZ (7 mm × 7 mm) Pinout, 0.5 mm Pitch (Top View)

The following I/O pins marked in Figure 7-1 in **bold** have high-drive capabilities:

- Pin 10, DIO\_5

- Pin 11, DIO\_6

- Pin 12, DIO\_7

- Pin 24, JTAG\_TMSC

- Pin 26, DIO\_16

- Pin 27, DIO\_17

The following I/O pins marked in Figure 7-1 in *italics* have analog capabilities:

- Pin 36, DIO\_23

- Pin 37, DIO\_24

- Pin 38, DIO 25

- Pin 39, DIO\_26

- Pin 40, DIO\_27

- Pin 41, DIO\_28

- Pin 42, DIO\_29

- Pin 43, DIO\_30

# 7.2 Signal Descriptions – RGZ Package

| PIN           |    | 1/0 | TYPE              | DESCRIPTION                                                                                                   |  |  |

|---------------|----|-----|-------------------|---------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO.      |    | I/O | TYPE              | DESCRIPTION                                                                                                   |  |  |

| DCDC_SW       | 33 | _   | Power             | Output from internal DC/DC converter <sup>(1)</sup>                                                           |  |  |

| DCOUPL        | 23 | _   | Power             | For decoupling of internal 1.27 V regulated digital-supply <sup>(2)</sup>                                     |  |  |

| DIO_0         | 5  | I/O | Digital           | GPIO                                                                                                          |  |  |

| DIO_1         | 6  | I/O | Digital           | GPIO                                                                                                          |  |  |

| DIO_2         | 7  | I/O | Digital           | GPIO                                                                                                          |  |  |

| DIO_3         | 8  | I/O | Digital           | GPIO                                                                                                          |  |  |

| DIO_4         | 9  | I/O | Digital           | GPIO                                                                                                          |  |  |

| DIO_5         | 10 | I/O | Digital           | GPIO, high-drive capability                                                                                   |  |  |

| DIO_6         | 11 | I/O | Digital           | GPIO, high-drive capability                                                                                   |  |  |

| DIO_7         | 12 | I/O | Digital           | GPIO, high-drive capability                                                                                   |  |  |

| DIO_8         | 14 | I/O | Digital           | GPIO                                                                                                          |  |  |

| DIO_9         | 15 | I/O | Digital           | GPIO                                                                                                          |  |  |

| DIO_10        | 16 | I/O | Digital           | GPIO                                                                                                          |  |  |

| DIO_11        | 17 | I/O | Digital           | GPIO                                                                                                          |  |  |

| DIO_12        | 18 | I/O | Digital           | GPIO                                                                                                          |  |  |

| DIO_13        | 19 | I/O | Digital           | GPIO                                                                                                          |  |  |

| DIO_14        | 20 | I/O | Digital           | GPIO                                                                                                          |  |  |

| DIO_15        | 21 | I/O | Digital           | GPIO                                                                                                          |  |  |

| DIO_16        | 26 | I/O | Digital           | GPIO, JTAG_TDO, high-drive capability                                                                         |  |  |

| DIO_17        | 27 | I/O | Digital           | GPIO, JTAG_TDI, high-drive capability                                                                         |  |  |

| DIO_18        | 28 | I/O | Digital           | GPIO                                                                                                          |  |  |

| DIO_19        | 29 | I/O | Digital           | GPIO                                                                                                          |  |  |

| DIO_20        | 30 | I/O | Digital           | GPIO                                                                                                          |  |  |

| DIO_21        | 31 | I/O | Digital           | GPIO                                                                                                          |  |  |

| DIO_22        | 32 | I/O | Digital           | GPIO                                                                                                          |  |  |

| DIO_23        | 36 | I/O | Digital or Analog | GPIO, analog capability                                                                                       |  |  |

| DIO_24        | 37 | I/O | Digital or Analog | GPIO, analog capability                                                                                       |  |  |

| DIO_25        | 38 | I/O | Digital or Analog | GPIO, analog capability                                                                                       |  |  |

| DIO_26        | 39 | I/O | Digital or Analog | GPIO, analog capability                                                                                       |  |  |

| DIO_27        | 40 | I/O | Digital or Analog | GPIO, analog capability                                                                                       |  |  |

| <br>DIO 28    | 41 | I/O | Digital or Analog | GPIO, analog capability                                                                                       |  |  |

| <br>DIO 29    | 42 | I/O | Digital or Analog | GPIO, analog capability                                                                                       |  |  |

| <br>DIO_30    | 43 | I/O | Digital or Analog | GPIO, analog capability                                                                                       |  |  |

| EGP           |    |     | GND               | Ground – exposed ground pad <sup>(3)</sup>                                                                    |  |  |

| JTAG_TMSC     | 24 | I/O | Digital           | JTAG TMSC, high-drive capability                                                                              |  |  |

| <br>JTAG_TCKC | 25 | I   | Digital           | JTAG TCKC                                                                                                     |  |  |

| <br>RESET_N   | 35 | I   | Digital           | Reset, active low. No internal pullup resistor                                                                |  |  |

| <br>RF_P      | 1  | _   | RF                | Positive RF input signal to LNA during RX<br>Positive RF output signal from PA during TX                      |  |  |

| RF_N          | 2  | _   | RF                | Negative RF input signal to LNA during RX<br>Negative RF output signal from PA during TX                      |  |  |

| VDDR          | 45 |     | Power             | Internal supply, must be powered from the internal DC/DC converter or the internal LDO <sup>(2)</sup> (4) (6) |  |  |

#### Table 7-1. Signal Descriptions – RGZ Package

Copyright © 2023 Texas Instruments Incorporated

#### Table 7-1. Signal Descriptions – RGZ Package (continued)

| PIN       |     | I/O | TYDE             | DESCRIPTION                                                                                                                  |  |  |

|-----------|-----|-----|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME      | NO. | /U  | TYPE DESCRIPTION |                                                                                                                              |  |  |

| VDDR_RF   | 48  | _   | Power            | Internal supply, must be powered from the internal DC/DC converter or the internal $LDO^{(2)}$ <sup>(5)</sup> <sup>(6)</sup> |  |  |

| VDDS      | 44  | _   | Power            | 1.8 V to 3.8 V main chip supply <sup>(1)</sup>                                                                               |  |  |

| VDDS2     | 13  | _   | Power            | 1.8 V to 3.8 V DIO supply <sup>(1)</sup>                                                                                     |  |  |

| VDDS3     | 22  | _   | Power            | 1.8 V to 3.8 V DIO supply <sup>(1)</sup>                                                                                     |  |  |

| VDDS_DCDC | 34  | _   | Power            | 1.8 V to 3.8 V DC/DC converter supply                                                                                        |  |  |

| X48M_N    | 46  | _   | Analog           | 48 MHz crystal oscillator pin 1                                                                                              |  |  |

| X48M_P    | 47  | _   | Analog           | 48 MHz crystal oscillator pin 2                                                                                              |  |  |

| X32K_Q1   | 3   | _   | Analog           | 32 kHz crystal oscillator pin 1                                                                                              |  |  |

| X32K_Q2   | 4   | —   | Analog           | 32 kHz crystal oscillator pin 2                                                                                              |  |  |

(1) For more details, see technical reference manual listed in Section 11.2.

(2) Do not supply external circuitry from this pin.

(3) EGP is the only ground connection for the device. Good electrical connection to device ground on printed circuit board (PCB) is imperative for proper device operation.

(4) If internal DC/DC converter is not used, this pin is supplied internally from the main LDO.

(5) If internal DC/DC converter is not used, this pin must be connected to VDDR for supply from the main LDO.

(6) Output from internal DC/DC and LDO is trimmed to 1.68 V.

# 7.3 Connections for Unused Pins and Modules

#### Table 7-2. Connections for Unused Pins

| FUNCTION                       | SIGNAL NAME | PIN NUMBER                      | ACCEPTABLE PRACTICE <sup>(1)</sup> | PREFERRED<br>PRACTICE <sup>(1)</sup> |

|--------------------------------|-------------|---------------------------------|------------------------------------|--------------------------------------|

| GPIO                           | DIO_n       | 5–12<br>14–21<br>26–32<br>36–43 | NC or GND                          | NC                                   |

| 32.768 kHz crystal             | X32K_Q1     | 3                               | NC or GND                          | NC                                   |

| 52.700 KHZ CIYSTAI             | X32K_Q2     | 4                               |                                    | NC                                   |

| DC/DC converter <sup>(2)</sup> | DCDC_SW     | 33                              | NC                                 | NC                                   |

| DC/DC converter <sup>(2)</sup> | VDDS_DCDC   | 34                              | VDDS                               | VDDS                                 |

(1) NC = No connect

(2) When the DC/DC converter is not used, the inductor between DCDC\_SW and VDDR can be removed. VDDR and VDDR\_RF must still be connected and the 22 µF DCDC capacitor must be kept on the VDDR net.

# **8 Specifications**

#### 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup> (2)

|                     |                            |                                               | MIN  | MAX                  | UNIT |

|---------------------|----------------------------|-----------------------------------------------|------|----------------------|------|

| VDDS <sup>(3)</sup> | Supply voltage             |                                               | -0.3 | 4.1                  | V    |

|                     | Voltage on any digital pir | (4) (5)                                       | -0.3 | VDDS + 0.3, max 4.1  | V    |

|                     | Voltage on crystal oscilla | tor pins, X32K_Q1, X32K_Q2, X48M_N and X48M_P | -0.3 | VDDR + 0.3, max 2.25 | V    |

|                     |                            | Voltage scaling enabled                       | -0.3 | VDDS                 |      |

| V <sub>in</sub>     | Voltage on ADC input       | Voltage scaling disabled, internal reference  | -0.3 | 1.49                 | V    |

|                     |                            | Voltage scaling disabled, VDDS as reference   | -0.3 | VDDS / 2.9           |      |

|                     | Input level, RF pins       |                                               |      | 5                    | dBm  |

| T <sub>stg</sub>    | Storage temperature        |                                               | -40  | 150                  | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime

(2) All voltage values are with respect to ground, unless otherwise noted.

(3) VDDS\_DCDC, VDDS2 and VDDS3 must be at the same potential as VDDS.

(4) Including analog capable DIOs.

(5) Injection current is not supported on any GPIO pin

#### 8.2 ESD Ratings

|      |                         |                                                                       |          | VALUE | UNIT |

|------|-------------------------|-----------------------------------------------------------------------|----------|-------|------|

| V    | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | All pins | ±2000 | V    |

| VESD | Electrostatic discharge | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | All pins | ±500  | V    |

(1) JEDEC document JEP155 states that 500 V HBM allows safe manufacturing with a standard ESD control process

(2) JEDEC document JEP157 states that 250 V CDM allows safe manufacturing with a standard ESD control process

#### 8.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                 | MIN | MAX | UNIT  |

|-------------------------------------------------|-----|-----|-------|

| Operating junction temperature <sup>(2)</sup>   | -40 | 105 | °C    |

| Operating supply voltage (VDDS)                 | 1.8 | 3.8 | V     |

| Rising supply voltage slew rate                 | 0   | 100 | mV/µs |

| Falling supply voltage slew rate <sup>(1)</sup> | 0   | 20  | mV/µs |

(1) For small coin-cell batteries, with high worst-case end-of-life equivalent source resistance, a 22 µF VDDS input capacitor must be used to ensure compliance with this slew rate.

(2) For thermal resistance characteristics refer to Thermal Resistance Characteristics. For application considerations, refer to Junction Temperature.

# 8.4 Power Supply and Modules

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                                                         |                   | MIN TYP MAX | UNIT |

|-------------------------------------------------------------------|-------------------|-------------|------|

| VDDS Power-on-Reset (POR) threshold                               |                   | 1.1 - 1.55  | V    |

| VDDS Brown-out Detector (BOD) <sup>(1)</sup>                      | Rising threshold  | 1.77        | V    |

| VDDS Brown-out Detector (BOD), before initial boot <sup>(2)</sup> | Rising threshold  | 1.70        | V    |

| VDDS Brown-out Detector (BOD) <sup>(1)</sup>                      | Falling threshold | 1.75        | V    |

For boost mode (VDDR =1.95 V), TI drivers software initialization will trim VDDS BOD limits to maximum (approximately 2.0 V)

Brown-out Detector is trimmed at initial boot, value is kept until device is reset by a POR reset or the RESET\_N pin

### 8.5 Power Consumption - Power Modes

When measured on the CC26x2REM-7ID reference design with  $T_c$  = 25 °C,  $V_{DDS}$  = 3.0 V with DC/DC enabled unless otherwise noted.

|                   | PARAMETER                                                                                                                                                                                        | TEST CONDITIONS                                                           | MIN | ТҮР   | MAX | UNIT |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----|-------|-----|------|

| Core Curre        | ent Consumption                                                                                                                                                                                  | · · · ·                                                                   |     |       | I   |      |

|                   | Reset and<br>Shutdown         Reset. RESET_N pin asserted or VDDS below power-on-reset<br>threshold         150           Shutdown         Shutdown. No clocks running, no retention         150 |                                                                           | 150 |       | nA  |      |

|                   | Shuldown                                                                                                                                                                                         | Shutdown. No clocks running, no retention                                 |     | 150   |     |      |

|                   | Standby<br>without cache                                                                                                                                                                         | RTC running, CPU, 80 kB RAM and (partial) register retention.<br>RCOSC_LF |     | 0.94  |     | μA   |

|                   | retention                                                                                                                                                                                        | RTC running, CPU, 80 kB RAM and (partial) register retention XOSC_LF      |     | 1.09  |     | μA   |

| I <sub>core</sub> | Standby                                                                                                                                                                                          | RTC running, CPU, 80 kB RAM and (partial) register retention.<br>RCOSC_LF |     | 3.2   |     | μA   |

|                   | with cache retention                                                                                                                                                                             | RTC running, CPU, 80 kB RAM and (partial) register retention.<br>XOSC_LF  |     | 3.3   |     | μA   |

|                   | Idle                                                                                                                                                                                             | Supply Systems and RAM powered<br>RCOSC_HF                                |     | 675   |     | μA   |

|                   | Active                                                                                                                                                                                           | MCU running CoreMark at 48 MHz<br>RCOSC_HF                                |     | 3.39  |     | mA   |

| Peripheral        | Current Consumption, (1)                                                                                                                                                                         | , (2)                                                                     |     |       |     |      |

|                   | Peripheral power<br>domain                                                                                                                                                                       | Delta current with domain enabled                                         |     | 97.7  |     |      |

|                   | Serial power domain                                                                                                                                                                              | Delta current with domain enabled                                         |     | 7.2   |     |      |

|                   | RF Core                                                                                                                                                                                          | Delta current with power domain enabled, clock enabled, RF core idle      | 2   | 210.9 |     |      |

|                   | μDMA                                                                                                                                                                                             | Delta current with clock enabled, module is idle                          | ·   | 63.9  |     |      |

|                   | Timers                                                                                                                                                                                           | Delta current with clock enabled, module is idle <sup>(5)</sup>           | ·   | 81.0  |     |      |

| peri              | 12C                                                                                                                                                                                              | Delta current with clock enabled, module is idle                          | ·   | 10.1  |     | μA   |

|                   | 12S                                                                                                                                                                                              | Delta current with clock enabled, module is idle                          |     | 26.3  |     |      |

|                   | SSI                                                                                                                                                                                              | Delta current with clock enabled, module is idle                          |     | 82.9  |     |      |

|                   | UART                                                                                                                                                                                             | Delta current with clock enabled, module is idle <sup>(3)</sup>           | 1   | 167.5 |     |      |

|                   | CRYPTO (AES)                                                                                                                                                                                     | Delta current with clock enabled, module is idle <sup>(4)</sup>           |     | 25.6  |     |      |

|                   | PKA                                                                                                                                                                                              | Delta current with clock enabled, module is idle                          |     | 84.7  |     |      |

|                   | TRNG                                                                                                                                                                                             | Delta current with clock enabled, module is idle                          |     | 35.6  |     |      |

| Sensor Cor        | ntroller Engine Consump                                                                                                                                                                          | tion                                                                      |     |       |     |      |

|                   | Active mode                                                                                                                                                                                      | 24 MHz, infinite loop                                                     |     | 308.5 |     |      |

| SCE               | Low-power mode 2 MHz, infinite loop 30.1                                                                                                                                                         |                                                                           |     | μA    |     |      |

Adds to core current I<sub>core</sub> for each peripheral unit activated. I<sub>peri</sub> is not supported in Standby or Shutdown modes. Only one UART running Only one SSI running Only one GPTimer running (1)

(2) (3)

(4)

(5)

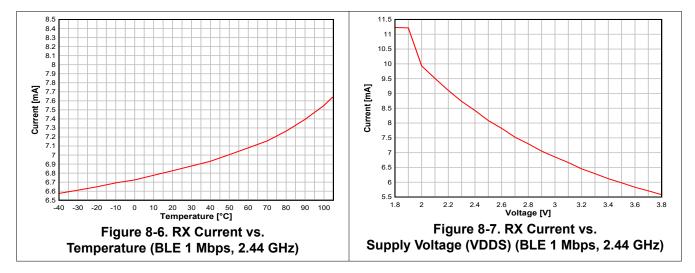

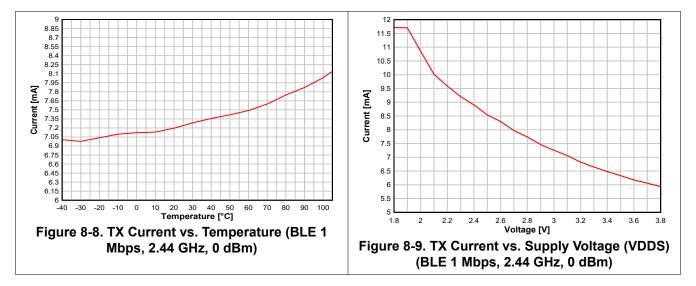

#### 8.6 Power Consumption - Radio Modes

When measured on the reference design with  $T_c = 25 \degree C$ ,  $V_{DDS} = 3.0 V$  with DC/DC enabled unless otherwise noted.

| PARAMETER             | TEST CONDITIONS                         | MIN | TYP | MAX | UNIT |

|-----------------------|-----------------------------------------|-----|-----|-----|------|

| Radio receive current | 2440 MHz                                |     | 6.9 |     | mA   |

|                       | 0 dBm output power setting<br>2440 MHz  |     | 7.0 |     | mA   |

|                       | +5 dBm output power setting<br>2440 MHz |     | 9.2 |     | mA   |

#### 8.7 Nonvolatile (Flash) Memory Characteristics

Over operating free-air temperature range and V<sub>DDS</sub> = 3.0 V (unless otherwise noted)

| PARAMETER                                                                       | TEST CONDITIONS                          | MIN  | TYP  | MAX | UNIT                |

|---------------------------------------------------------------------------------|------------------------------------------|------|------|-----|---------------------|

| Flash sector size                                                               |                                          |      | 8    |     | KB                  |

| Supported flash erase cycles before failure, full bank <sup>(1) (5)</sup>       |                                          | 30   |      |     | k Cycles            |

| Supported flash erase cycles before failure, single sector <sup>(2)</sup>       |                                          | 60   |      |     | k Cycles            |

| Maximum number of write operations per row before sector $\ensuremath{e}^{(3)}$ |                                          |      |      | 83  | Write<br>Operations |

| Flash retention                                                                 | 105 °C                                   | 11.4 |      |     | Years at 105<br>°C  |

| Flash sector erase current                                                      | Average delta current                    |      | 10.7 |     | mA                  |

| Flash sector erase time <sup>(4)</sup>                                          | Zero cycles                              |      | 10   |     | ms                  |

| Flash write current                                                             | Average delta current, 4 bytes at a time |      | 6.2  |     | mA                  |

| Flash write time <sup>(4)</sup>                                                 | 4 bytes at a time                        |      | 21.6 |     | μs                  |

(1) A full bank erase is counted as a single erase cycle on each sector

(2) Up to 4 customer-designated sectors can be individually erased an additional 30k times beyond the baseline bank limitation of 30k cycles

(3) Each wordline is 2048 bits (or 256 bytes) wide. This limitation corresponds to sequential memory writes of 4 (3.1) bytes minimum per write over a whole wordline. If additional writes to the same wordline are required, a sector erase is required once the maximum number of write operations per row is reached.

(4) This number is dependent on Flash aging and increases over time and erase cycles

(5) Aborting flash during erase or program modes is not a safe operation.

#### 8.8 Thermal Resistance Characteristics

| THERMAL METRIC <sup>(1)</sup> |                                              | PACKAGE       |                     |

|-------------------------------|----------------------------------------------|---------------|---------------------|

|                               |                                              | RGZ<br>(VQFN) | UNIT                |

|                               |                                              | 48 PINS       |                     |

| R <sub>θJA</sub>              | Junction-to-ambient thermal resistance       | 23.4          | °C/W <sup>(2)</sup> |

| R <sub>0JC(top)</sub>         | Junction-to-case (top) thermal resistance    | 13.3          | °C/W <sup>(2)</sup> |

| R <sub>θJB</sub>              | Junction-to-board thermal resistance         | 8.0           | °C/W <sup>(2)</sup> |

| Ψ <sub>JT</sub>               | Junction-to-top characterization parameter   | 0.1           | °C/W <sup>(2)</sup> |

| Ψ <sub>JB</sub>               | Junction-to-board characterization parameter | 7.9           | °C/W <sup>(2)</sup> |

| R <sub>0JC(bot)</sub>         | Junction-to-case (bottom) thermal resistance | 1.7           | °C/W <sup>(2)</sup> |

(1) For more information about traditional and new thermal metrics, see Semiconductor and IC Package Thermal Metrics.

(2) °C/W = degrees Celsius per watt.

#### 8.9 RF Frequency Bands

Over operating free-air temperature range (unless otherwise noted).

| PARAMETER       | MIN  | TYP | MAX  | UNIT |

|-----------------|------|-----|------|------|

| Frequency bands | 2360 |     | 2500 | MHz  |

# 8.10 Bluetooth Low Energy - Receive (RX)

When measured on the CC26x2REM-7ID reference design with  $T_c = 25$  °C,  $V_{DDS} = 3.0$  V,  $f_{RF} = 2440$  MHz with DC/DC enabled unless otherwise noted. All measurements are performed at the antenna input with a combined RX and TX path. All measurements are performed conducted.

| PARAMETER                                               | TEST CONDITIONS                                                                                                                                                               | MIN TYP                 | MAX UI | NIT |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------|-----|

| 125 kbps (LE Coded)                                     |                                                                                                                                                                               |                         |        |     |

| Receiver sensitivity                                    | Differential mode. BER = 10 <sup>-3</sup>                                                                                                                                     | -105                    | df     | Bm  |

| Receiver saturation                                     | Differential mode. BER = 10 <sup>-3</sup>                                                                                                                                     | >5                      | df     | Bm  |

| Frequency error tolerance                               | Difference between the incoming carrier frequency and the internally generated carrier frequency                                                                              | > (-300 / 300)          | k      | Hz  |

| Data rate error tolerance                               | Difference between incoming data rate and the internally generated data rate (37 byte packets)                                                                                | > (-320 / 240)          | р      | pm  |

| Data rate error tolerance                               | Difference between incoming data rate and the internally generated data rate (255 byte packets)                                                                               | > (–125 / 100)          | р      | pm  |

| Co-channel rejection <sup>(1)</sup>                     | Wanted signal at $-79$ dBm, modulated interferer in channel, BER = $10^{-3}$                                                                                                  | -1.5                    | с      | dB  |

| Selectivity, ±1 MHz <sup>(1)</sup>                      | Wanted signal at –79 dBm, modulated interferer at ±1 MHz, BER = $10^{-3}$                                                                                                     | 8 / 4.5 <sup>(2)</sup>  | с      | dB  |

| Selectivity, ±2 MHz <sup>(1)</sup>                      | Wanted signal at –79 dBm, modulated interferer at ±2 MHz, BER = $10^{-3}$                                                                                                     | 44 / 37 (2)             | с      | dB  |

| Selectivity, ±3 MHz <sup>(1)</sup>                      | Wanted signal at –79 dBm, modulated interferer at ±3 MHz, BER = $10^{-3}$                                                                                                     | 46 / 44 <sup>(2)</sup>  | c      | dB  |

| Selectivity, ±4 MHz <sup>(1)</sup>                      | Wanted signal at –79 dBm, modulated interferer at ±4 MHz, BER = $10^{-3}$                                                                                                     | 44 / 46 <sup>(2)</sup>  | с      | dB  |

| Selectivity, ±6 MHz <sup>(1)</sup>                      | Wanted signal at –79 dBm, modulated interferer at $\ge \pm 6$ MHz, BER = $10^{-3}$                                                                                            | 48 / 44 <sup>(2)</sup>  | с      | dB  |

| Selectivity, ±7 MHz                                     | Wanted signal at –79 dBm, modulated interferer at $\ge \pm 7$ MHz, BER = $10^{-3}$                                                                                            | 51 / 45 <sup>(2)</sup>  | c      | dB  |

| Selectivity, Image frequency <sup>(1)</sup>             | Wanted signal at –79 dBm, modulated interferer at image frequency, BER = $10^{-3}$                                                                                            | 37                      | с      | dB  |

| Selectivity, Image frequency $\pm 1$ MHz <sup>(1)</sup> | Note that Image frequency + 1 MHz is the Co- channel<br>-1 MHz. Wanted signal at -79 dBm, modulated interferer<br>at $\pm$ 1 MHz from image frequency, BER = 10 <sup>-3</sup> | 4.5 / 44 <sup>(2)</sup> | с      | dB  |

| 500 kbps (LE Coded)                                     |                                                                                                                                                                               |                         |        |     |

| Receiver sensitivity                                    | Differential mode. BER = 10 <sup>-3</sup>                                                                                                                                     | -100                    | df     | Bm  |

| Receiver saturation                                     | Differential mode. BER = $10^{-3}$                                                                                                                                            | > 5                     | df     | Bm  |

| Frequency error tolerance                               | Difference between the incoming carrier frequency and the internally generated carrier frequency                                                                              | > (-300 / 300)          | k      | Hz  |

| Data rate error tolerance                               | Difference between incoming data rate and the internally generated data rate (37 byte packets)                                                                                | > (-450 / 450)          | р      | pm  |

| Data rate error tolerance                               | Difference between incoming data rate and the internally generated data rate (255 byte packets)                                                                               | > (-150/ 175)           | р      | pm  |

| Co-channel rejection <sup>(1)</sup>                     | Wanted signal at $-72$ dBm, modulated interferer in channel, BER = $10^{-3}$                                                                                                  | -3.5                    | c      | dB  |

| Selectivity, ±1 MHz <sup>(1)</sup>                      | Wanted signal at –72 dBm, modulated interferer at ±1 MHz, BER = $10^{-3}$                                                                                                     | 8 / 4 <sup>(2)</sup>    | с      | dB  |

| Selectivity, ±2 MHz <sup>(1)</sup>                      | Wanted signal at –72 dBm, modulated interferer at ±2 MHz, BER = $10^{-3}$                                                                                                     | 43 / 35 (2)             | с      | dB  |

| Selectivity, ±3 MHz <sup>(1)</sup>                      | Wanted signal at –72 dBm, modulated interferer at ±3 MHz, BER = $10^{-3}$                                                                                                     | 46 / 46 <sup>(2)</sup>  | c      | dB  |

| Selectivity, ±4 MHz <sup>(1)</sup>                      | Wanted signal at –72 dBm, modulated interferer at ±4 MHz, BER = $10^{-3}$                                                                                                     | 45 / 47 <sup>(2)</sup>  | с      | dB  |

| Selectivity, ±6 MHz <sup>(1)</sup>                      | Wanted signal at –72 dBm, modulated interferer at $\ge \pm 6$ MHz, BER = $10^{-3}$                                                                                            | 46 / 45 <sup>(2)</sup>  | с      | dB  |

| Selectivity, ±7 MHz                                     | Wanted signal at –72 dBm, modulated interferer at $\ge \pm 7$ MHz, BER = $10^{-3}$                                                                                            | 49 / 45 <sup>(2)</sup>  | с      | dB  |

| Selectivity, Image frequency <sup>(1)</sup>             | Wanted signal at $-72$ dBm, modulated interferer at image frequency, BER = $10^{-3}$                                                                                          | 35                      | с      | dB  |

# 8.10 Bluetooth Low Energy - Receive (RX) (continued)

When measured on the CC26x2REM-7ID reference design with  $T_c = 25$  °C,  $V_{DDS} = 3.0$  V,  $f_{RF} = 2440$  MHz with DC/DC enabled unless otherwise noted. All measurements are performed at the antenna input with a combined RX and TX path. All measurements are performed conducted.

| PARAMETER                                             | TEST CONDITIONS                                                                                                                                                 | MIN TYP                | MAX | UNIT |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|------|

| Selectivity, Image frequency ±1<br>MHz <sup>(1)</sup> | Note that Image frequency + 1 MHz is the Co- channel $-1$ MHz. Wanted signal at $-72$ dBm, modulated interferer at ±1 MHz from image frequency, BER = $10^{-3}$ | 4 / 46 <sup>(2)</sup>  |     | dB   |

| 1 Mbps (LE 1M)                                        |                                                                                                                                                                 |                        |     |      |

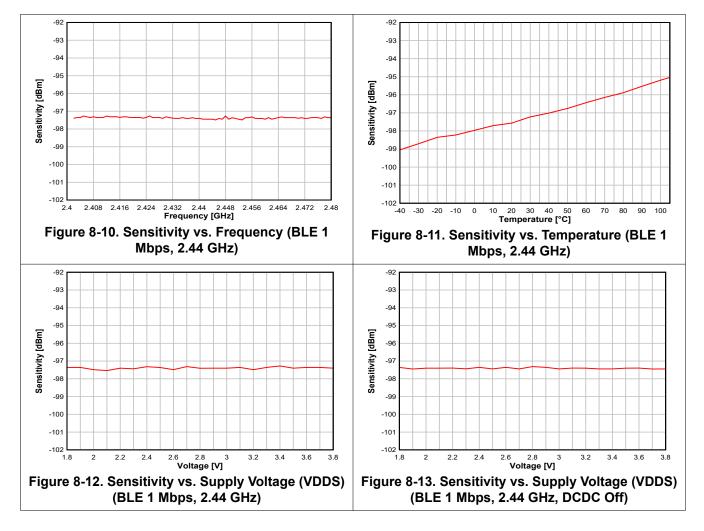

| Receiver sensitivity                                  | Differential mode. BER = 10 <sup>−3</sup>                                                                                                                       | -97                    |     | dBm  |

| Receiver saturation                                   | Differential mode. BER = 10 <sup>-3</sup>                                                                                                                       | > 5                    |     | dBm  |

| Frequency error tolerance                             | Difference between the incoming carrier frequency and the internally generated carrier frequency                                                                | > (-350 / 350)         |     | kHz  |

| Data rate error tolerance                             | Difference between incoming data rate and the internally generated data rate (37 byte packets)                                                                  | > (-650 / 750)         |     | ppm  |

| Co-channel rejection <sup>(1)</sup>                   | Wanted signal at –67 dBm, modulated interferer in channel, BER = $10^{-3}$                                                                                      | -6                     |     | dB   |

| Selectivity, ±1 MHz <sup>(1)</sup>                    | Wanted signal at –67 dBm, modulated interferer at ±1 MHz, BER = $10^{-3}$                                                                                       | 7 / 4 <sup>(2)</sup>   |     | dB   |

| Selectivity, ±2 MHz <sup>(1)</sup>                    | Wanted signal at –67 dBm, modulated interferer at $\pm 2$ MHz,BER = $10^{-3}$                                                                                   | 39 / 33 <sup>(2)</sup> |     | dB   |

| Selectivity, ±3 MHz <sup>(1)</sup>                    | Wanted signal at –67 dBm, modulated interferer at $\pm 3$ MHz, BER = $10^{-3}$                                                                                  | 36 / 40 <sup>(2)</sup> |     | dB   |

| Selectivity, ±4 MHz <sup>(1)</sup>                    | Wanted signal at –67 dBm, modulated interferer at ±4 MHz, BER = $10^{-3}$                                                                                       | 36 / 45 <sup>(2)</sup> |     | dB   |

| Selectivity, ±5 MHz or more <sup>(1)</sup>            | Wanted signal at –67 dBm, modulated interferer at $\ge \pm 5$ MHz, BER = $10^{-3}$                                                                              | 40                     |     | dB   |

| Selectivity, image frequency <sup>(1)</sup>           | Wanted signal at –67 dBm, modulated interferer at image frequency, BER = $10^{-3}$                                                                              | 33                     |     | dB   |

| Selectivity, image frequency<br>±1 MHz <sup>(1)</sup> | Note that Image frequency + 1 MHz is the Co- channel $-1$ MHz. Wanted signal at $-67$ dBm, modulated interferer at ±1 MHz from image frequency, BER = $10^{-3}$ | 4 / 41 <sup>(2)</sup>  |     | dB   |

| Out-of-band blocking <sup>(3)</sup>                   | 30 MHz to 2000 MHz                                                                                                                                              | -10                    |     | dBm  |

| Out-of-band blocking                                  | 2003 MHz to 2399 MHz                                                                                                                                            | -18                    |     | dBm  |

| Out-of-band blocking                                  | 2484 MHz to 2997 MHz                                                                                                                                            | -12                    |     | dBm  |

| Out-of-band blocking                                  | 3000 MHz to 12.75 GHz                                                                                                                                           | -2                     |     | dBm  |

| Intermodulation                                       | Wanted signal at 2402 MHz, –64 dBm. Two interferers at 2405 and 2408 MHz respectively, at the given power level                                                 | -42                    |     | dBm  |

| Spurious emissions,<br>30 to 1000 MHz <sup>(4)</sup>  | Measurement in a 50 $\Omega$ single-ended load.                                                                                                                 | <59                    |     | dBm  |

| Spurious emissions,<br>1 to 12.75 GHz <sup>(4)</sup>  | Measurement in a 50 $\Omega$ single-ended load.                                                                                                                 | < -47                  |     | dBm  |

| RSSI dynamic range                                    |                                                                                                                                                                 | 70                     |     | dB   |

| RSSI accuracy                                         |                                                                                                                                                                 | ±4                     |     | dB   |

| 2 Mbps (LE 2M)                                        |                                                                                                                                                                 |                        |     |      |

| Receiver sensitivity                                  | Differential mode. Measured at SMA connector, BER = $10^{-3}$                                                                                                   | -91                    |     | dBm  |

| Receiver saturation                                   | Differential mode. Measured at SMA connector, BER = $10^{-3}$                                                                                                   | > 5                    |     | dBm  |

| Frequency error tolerance                             | Difference between the incoming carrier frequency and the internally generated carrier frequency                                                                | > (-500 / 500)         |     | kHz  |

| Data rate error tolerance                             | Difference between incoming data rate and the internally generated data rate (37 byte packets)                                                                  | > (-700 / 750)         |     | ppm  |

| Co-channel rejection <sup>(1)</sup>                   | hel rejection <sup>(1)</sup> Wanted signal at -67 dBm, modulated interferer in channel,BER = 10 <sup>-3</sup>                                                   |                        |     | dB   |

| Selectivity, ±2 MHz <sup>(1)</sup>                    | Wanted signal at –67 dBm, modulated interferer at $\pm 2$ MHz, Image frequency is at –2 MHz, BER = $10^{-3}$                                                    | 8 / 4 <sup>(2)</sup>   |     | dB   |

# 8.10 Bluetooth Low Energy - Receive (RX) (continued)

When measured on the CC26x2REM-7ID reference design with  $T_c = 25$  °C,  $V_{DDS} = 3.0$  V,  $f_{RF} = 2440$  MHz with DC/DC enabled unless otherwise noted. All measurements are performed at the antenna input with a combined RX and TX path. All measurements are performed conducted.

| PARAMETER                                                                                                                              | TEST CONDITIONS                                                                                                                                             | MIN | ТҮР                    | MAX | UNIT |

|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|-----|------|

| Selectivity, ±4 MHz <sup>(1)</sup>                                                                                                     | Wanted signal at –67 dBm, modulated interferer at $\pm 4$ MHz, BER = $10^{-3}$                                                                              |     | 36 / 34 <sup>(2)</sup> |     | dB   |

| Selectivity, ±6 MHz <sup>(1)</sup>                                                                                                     | Wanted signal at –67 dBm, modulated interferer at $\pm 6$ MHz, BER = $10^{-3}$                                                                              |     | 37 / 36 <sup>(2)</sup> |     | dB   |

| Selectivity, image frequency <sup>(1)</sup>                                                                                            | Wanted signal at –67 dBm, modulated interferer at image frequency, BER = $10^{-3}$                                                                          |     | 4                      |     | dB   |

| Selectivity, image frequency<br>±2 MHz <sup>(1)</sup>                                                                                  | Note that Image frequency + 2 MHz is the Co-channel.<br>Wanted signal at –67 dBm, modulated interferer at $\pm 2$ MHz from image frequency, BER = $10^{-3}$ |     | -7 / 36 <sup>(2)</sup> |     | dB   |

| Out-of-band blocking <sup>(3)</sup>                                                                                                    | 30 MHz to 2000 MHz                                                                                                                                          |     | -16                    |     | dBm  |

| Out-of-band blocking                                                                                                                   | 2003 MHz to 2399 MHz                                                                                                                                        |     | -21                    |     | dBm  |

| Out-of-band blocking                                                                                                                   | 2484 MHz to 2997 MHz                                                                                                                                        |     | -15                    |     | dBm  |

| Out-of-band blocking                                                                                                                   | 3000 MHz to 12.75 GHz                                                                                                                                       |     | -12                    |     | dBm  |

| ermodulation Wanted signal at 2402 MHz, -64 dBm. Two interferers<br>at 2408 and 2414 MHz respectively, at the given power<br>level -38 |                                                                                                                                                             |     | dBm                    |     |      |

(1) Numbers given as I/C dB

(2) X / Y, where X is +N MHz and Y is -N MHz

(3) Excluding one exception at F<sub>wanted</sub> / 2, per Bluetooth Specification

(4) Suitable for systems targeting compliance with worldwide radio-frequency regulations ETSI EN 300 328 and EN 300 440 Class 2 (Europe), FCC CFR47 Part 15 (US), and ARIB STD-T66 (Japan)

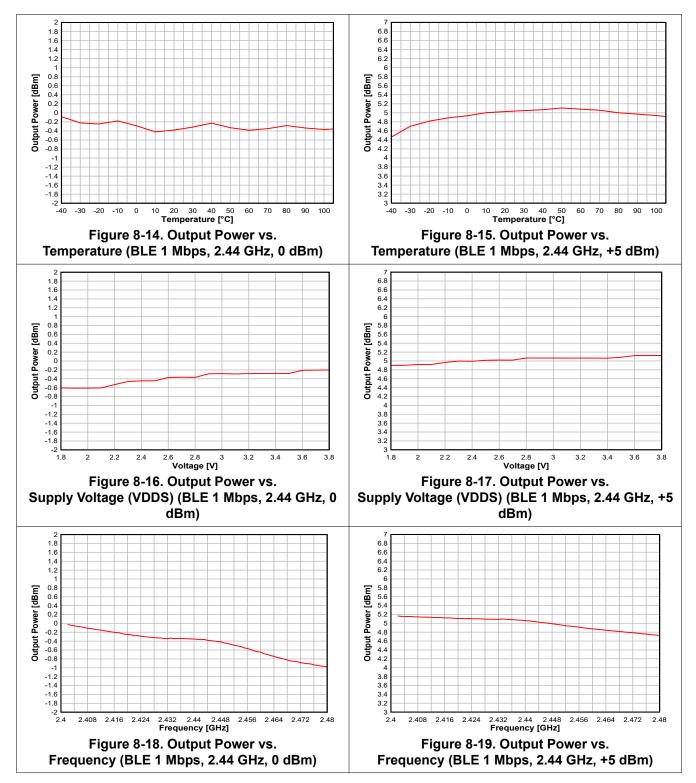

### 8.11 Bluetooth Low Energy - Transmit (TX)

When measured on the CC26x2REM-7ID reference design with  $T_c = 25$  °C,  $V_{DDS} = 3.0$  V,  $f_{RF} = 2440$  MHz with DC/DC enabled unless otherwise noted. All measurements are performed at the antenna input with a combined RX and TX path. All measurements are performed conducted.

| PARAMETER                          | •                                                                               | TEST CONDITIONS                           | MIN | TYP   | MAX | UNIT |

|------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------|-----|-------|-----|------|

| General Parameters                 |                                                                                 |                                           |     |       |     |      |

| Max output power                   | Differential mode, delivered to a sing                                          | le-ended 50 $\Omega$ load through a balun |     | 5     |     | dBm  |