Order

Now

**DLPA4000** DLPS132 – MAY 2018

# DLPA4000 PMIC and High-Current LED Driver

Technical

Documents

### 1 Features

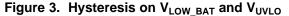

- High-Efficiency, High-Current RGB LED Driver with High-Side Pump Functionality

- Drivers for External Buck FETs up to 32 A

- Drivers for External RGB Switches

- 10-Bit Programmable Current per Channel

- Inputs for Selecting Color-Sequential RGB LEDs

- Generation of DMD High Voltage Supplies

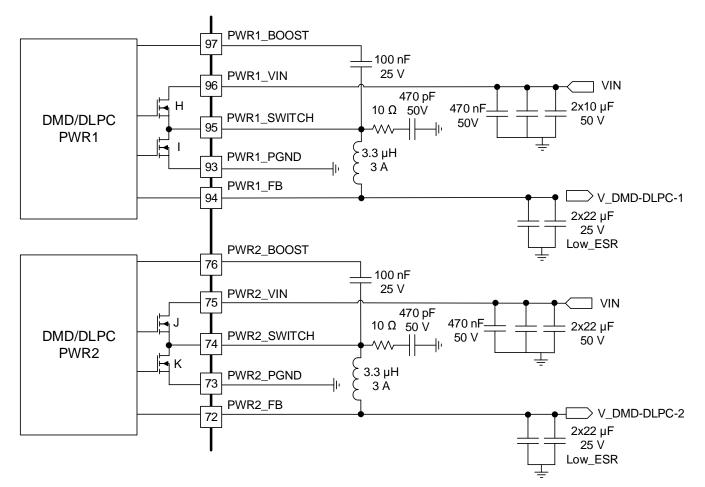

- Two High Efficiency Buck Converters to Generate the DLPC4422 controller and DMD Supply

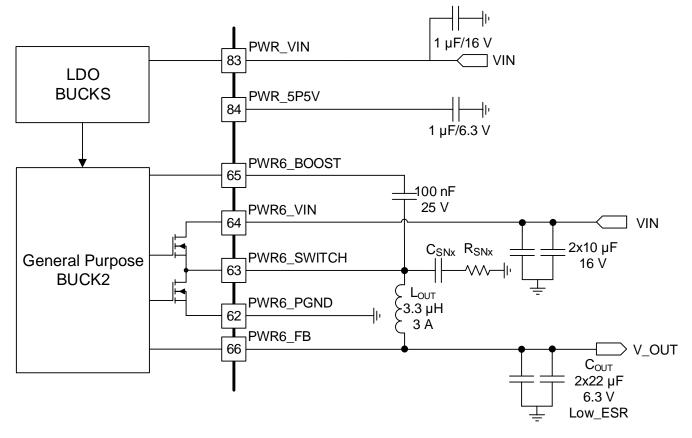

- A High Efficiency, 8-Bit Programmable Buck Converter (PWR6) for FAN Driver Application or General Purpose

- Two LDOs Supplying Auxiliary Voltages

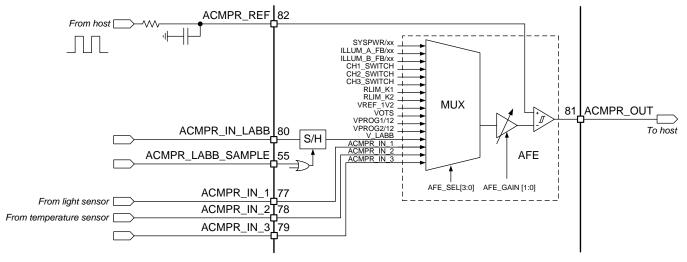

- Analog MUX for Measuring Internal and External Nodes

- Protections: Thermal Shutdown, Hot Die, Low Battery, and Undervoltage Lockout (UVLO)

## 2 Applications

Smart Led Projectors Screenless TV Digital Signage Stage Lighting

## 3 Description

Tools &

Software

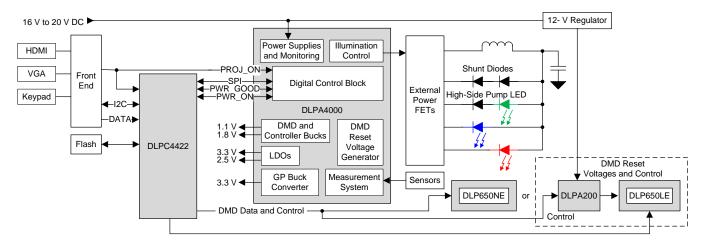

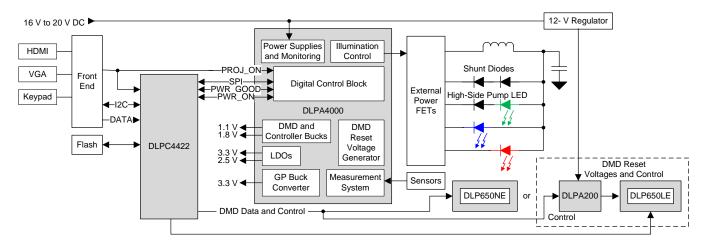

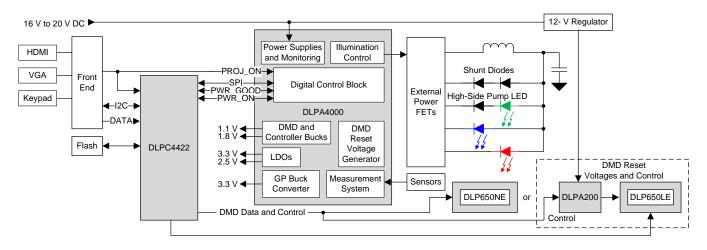

The DLPA4000 device is a highly-integrated power management driver. It is optimized for DLP® LED DLPA4000 projector systems. The supports projectors up to 32 A per LED with high-side pump functionality. An integrated, high-efficiency buck controller energizes the device. The drivers control switches support the sequencing of R, G, and B LEDs. The device contains five buck converters, two of which are dedicated for the DLPC4422 controller low-voltage supply. Another dedicated regulated supply energizes the DLPA200 DMD micromirror driver and the three timing critical DC supplies for the DMD: VBIAS, VRST, and VOFS.

Support &

Community

20

The DLPA4000 device contains several auxiliary blocks. These blocks allow flexibility in LED projector system design. An 8-bit programmable buck converter can drive an RGB projector fan or make an auxiliary supply line. Two LDOs can generate a lower-current supply, up to 200 mA. These LDOs are specified to operate at 2.5 V and 3.3 V.

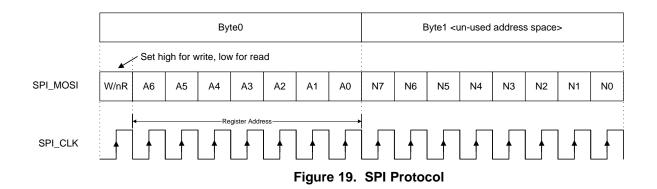

The serial protocol interface (SPI) addresses all blocks of the DLPA4000 device. These addressable features include: the generation of the system reset, power sequencing, input signals for sequentially selecting the active LED, IC self-protections, and an analog MUX for routing analog information to an external ADC.

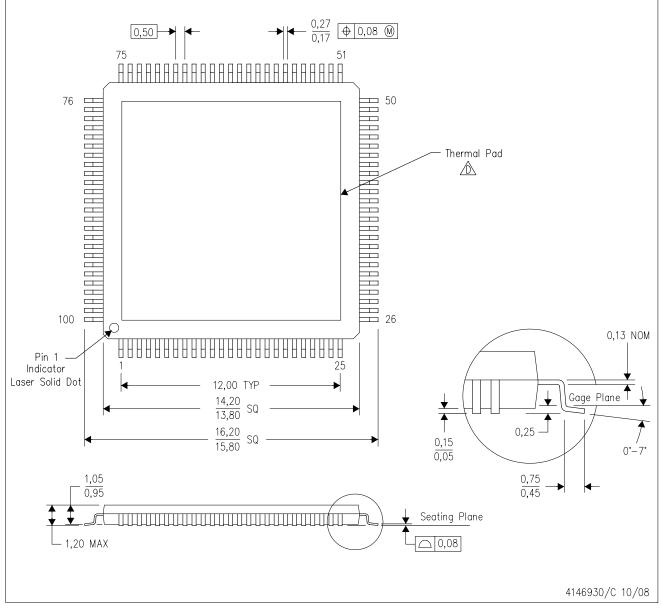

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)     |

|-------------|-------------|---------------------|

| DLPA4000    | HTQFP (100) | 14.00 mm × 14.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

### System Block Diagram

**A**

# **Table of Contents**

| 1 | Feat | tures                            | 1               |  |  |  |  |  |  |  |

|---|------|----------------------------------|-----------------|--|--|--|--|--|--|--|

| 2 | Арр  | Applications 1                   |                 |  |  |  |  |  |  |  |

| 3 | Des  | cription                         | 1               |  |  |  |  |  |  |  |

| 4 |      | ision History                    |                 |  |  |  |  |  |  |  |

| 5 | Pin  | Configuration and Functions      | 3               |  |  |  |  |  |  |  |

| 6 | Spe  | cifications                      | 7               |  |  |  |  |  |  |  |

|   | 6.1  | Absolute Maximum Ratings         | 7               |  |  |  |  |  |  |  |

|   | 6.2  | ESD Ratings                      | 8               |  |  |  |  |  |  |  |

|   | 6.3  | Recommended Operating Conditions | 8               |  |  |  |  |  |  |  |

|   | 6.4  | Thermal Information              | 8               |  |  |  |  |  |  |  |

|   | 6.5  | Electrical Characteristics       | 9               |  |  |  |  |  |  |  |

|   | 6.6  | SPI Timing Parameters            | 14              |  |  |  |  |  |  |  |

| 7 | Deta | ailed Description                | 15              |  |  |  |  |  |  |  |

|   | 7.1  | Overview                         | 15              |  |  |  |  |  |  |  |

|   | 7.2  | Functional Block Description     | 15              |  |  |  |  |  |  |  |

|   | 7.3  | Feature Description              | 16              |  |  |  |  |  |  |  |

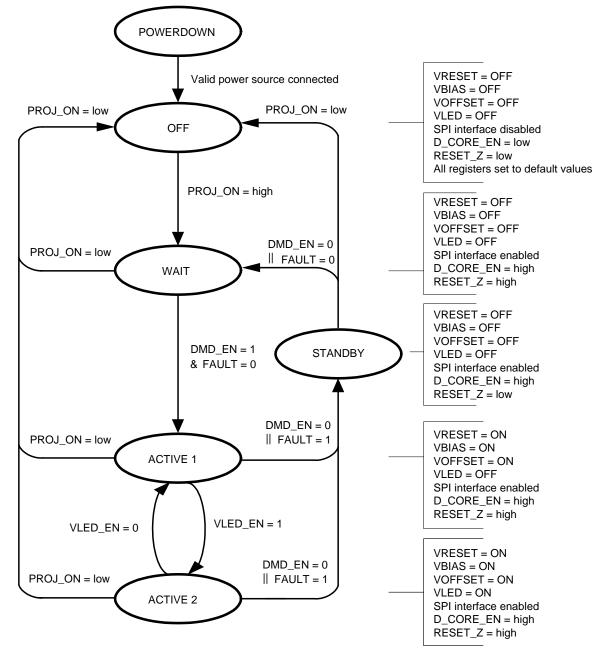

|   | 7.4  | Device Functional Modes          | 36              |  |  |  |  |  |  |  |

|   | 7.5  | Programming                      | 38              |  |  |  |  |  |  |  |

|   | 7.6  | Register Maps                    | 41              |  |  |  |  |  |  |  |

| 8 | Арр  | blication and Implementation     | <mark>51</mark> |  |  |  |  |  |  |  |

|   |      |                                  |                 |  |  |  |  |  |  |  |

|    | 8.1  | Application Information                             | 51 |

|----|------|-----------------------------------------------------|----|

|    | 8.2  | Typical Application                                 | 51 |

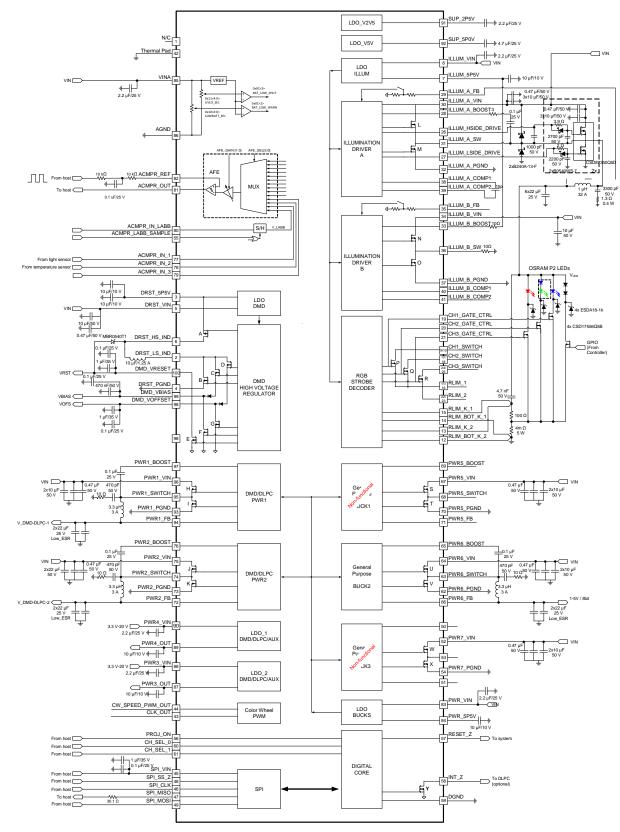

|    | 8.3  | System Example With DLPA4000 Internal Block Diagram | 54 |

| 9  | Pow  | er Supply Recommendations                           | 55 |

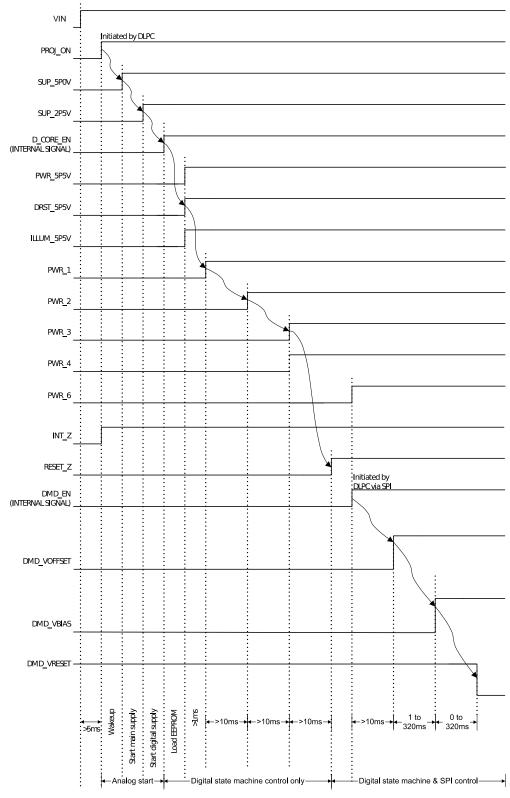

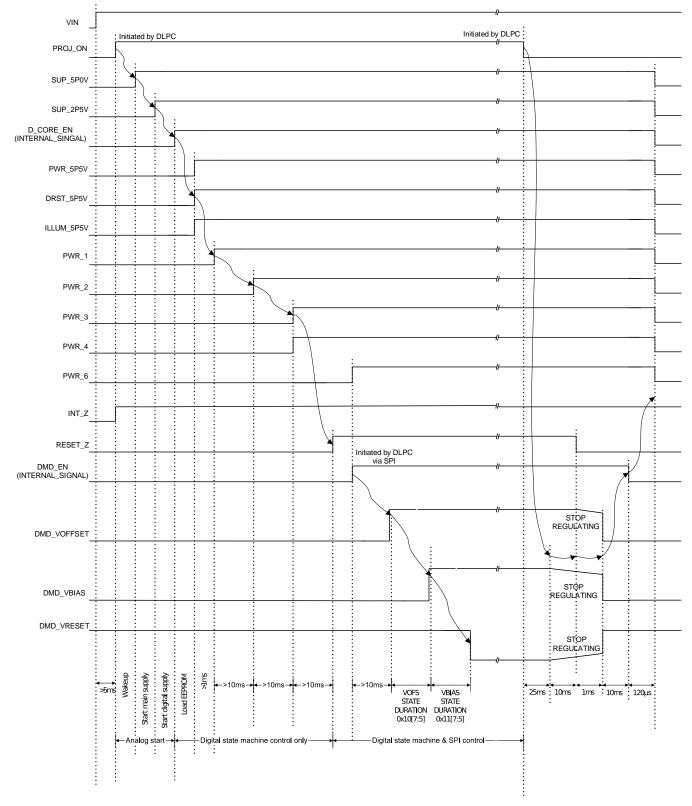

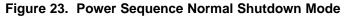

|    | 9.1  | Power-Up and Power-Down Timing                      | 55 |

| 10 | Lay  | out                                                 | 59 |

|    | 10.1 | Layout Guidelines                                   | 59 |

|    | 10.2 | Layout Example                                      | 68 |

|    | 10.3 | Thermal Considerations                              | 69 |

| 11 | Dev  | ice and Documentation Support                       | 71 |

|    | 11.1 | Device Support                                      | 71 |

|    | 11.2 | Receiving Notification of Documentation Updates     | 71 |

|    | 11.3 | Community Resources                                 | 71 |

|    | 11.4 | Trademarks                                          | 71 |

|    | 11.5 | Lieed cetale Dicentaryo cauterin                    |    |

|    | 11.6 | Glossary                                            | 71 |

| 12 |      | hanical, Packaging, and Orderable                   |    |

|    | Info | rmation                                             | 72 |

|    | 12.1 | Package Option Addendum                             | 73 |

|    |      |                                                     |    |

# 4 Revision History

| DATE     | REVISION | NOTES            |

|----------|----------|------------------|

| May 2018 | *        | Initial release. |

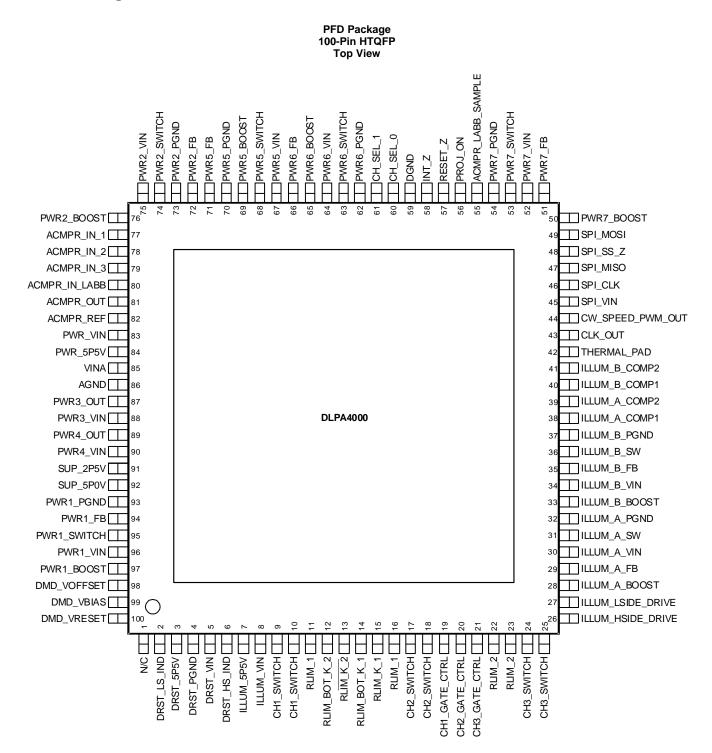

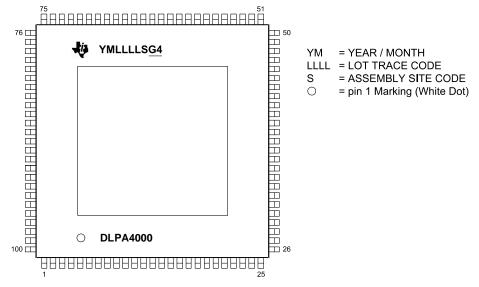

### 5 Pin Configuration and Functions

### **Pin Functions**

| PIN                  |    | I/O | Pin Functions<br>DESCRIPTION                                                                                                               |  |

|----------------------|----|-----|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| N/C                  | 1  |     | No connect                                                                                                                                 |  |

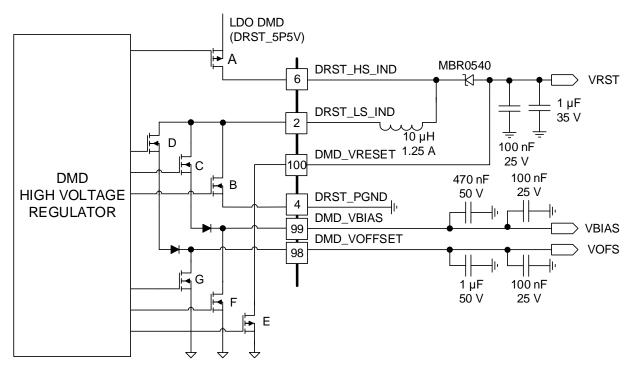

| DRST_LS_IND          | 2  | I/O | Connection for the DMD SMPS-inductor (low-side switch).                                                                                    |  |

| DRST_5P5V            | 3  | 0   | Filter pin for LDO DMD. Power supply for internal DMD reset regulator, typical 5.5 V.                                                      |  |

| DRST_PGND            | 4  | GND | Power ground for DMD SMPS. Connect to ground plane.                                                                                        |  |

| DRST_VIN             | 5  | P   | Power supply input for LDO DMD. Connect to system power.                                                                                   |  |

| DRST_HS_IND          | 6  | I/O | Connection for the DMD SMPS-inductor (high-side switch).                                                                                   |  |

| ILLUM_5P5 V          | 7  | 0   | Filter pin for LDO ILLUM. Power supply for internal ILLUM block, typical 5.5 V.                                                            |  |

| ILLUM_VIN            | 8  | P   | Supply input of LDO ILLUM. Connect to system power.                                                                                        |  |

| CH1_SWITCH           | 9  | 1   | Low-side MOSFET switch for LED Cathode. Connect to RGB LED assembly.                                                                       |  |

|                      | 10 | 1   |                                                                                                                                            |  |

| CH1_SWITCH<br>RLIM 1 | 11 | 0   | Low-side MOSFET switch for LED Cathode. Connect to RGB LED assembly.<br>Connection to LED current sense resistor for CH1 and CH2.          |  |

|                      | 12 | 1   |                                                                                                                                            |  |

| RLIM_BOT_K_2         | 12 | 1   | Kelvin sense connection to ground side of LED current sense resistor.                                                                      |  |

| RLIM_K_2             | -  | -   | Kelvin sense connection to top side of current sense resistor.                                                                             |  |

| RLIM_BOT_K_1         | 14 |     | Kelvin sense connection to ground side of LED current sense resistor.                                                                      |  |

| RLIM_K_1             | 15 |     | Kelvin sense connection to top side of current sense resistor.                                                                             |  |

| RLIM_1               | 16 | 0   | Connection to LED current sense resistor for CH1 and CH2.                                                                                  |  |

| CH2_SWITCH           | 17 |     | Low-side MOSFET switch for LED cathode. Connect to RGB LED assembly.                                                                       |  |

| CH2_SWITCH           | 18 | I   | Low-side MOSFET switch for LED cathode. Connect to RGB LED assembly.                                                                       |  |

| CH1_GATE_CTRL        | 19 | 0   | Gate control of CH1 external MOSFET switch for LED cathode.                                                                                |  |

| CH2_GATE_CTRL        | 20 | 0   | Gate control of CH2 external MOSFET switch for LED cathode.                                                                                |  |

| CH3_GATE_CTRL        | 21 | 0   | Gate control of CH3 external MOSFET switch for LED cathode.                                                                                |  |

| RLIM_2               | 22 | 0   | Connection to LED current sense resistor for CH3.                                                                                          |  |

| RLIM_2               | 23 | 0   | nnection to LED current sense resistor for CH3.                                                                                            |  |

| CH3_SWITCH           | 24 | I   | Low-side MOSFET switch for LED Cathode. Connect to RGB LED assembly.                                                                       |  |

| CH3_SWITCH           | 25 | I   | Low-side MOSFET switch for LED Cathode. Connect to RGB LED assembly.                                                                       |  |

| ILLUM_HSIDE_DRIVE    | 26 | 0   | Gate control for external high-side MOSFET for ILLUM Buck converter.                                                                       |  |

| ILLUM_LSIDE_DRIVE    | 27 | 0   | Gate control for external low-side MOSFET for ILLUM Buck converter.                                                                        |  |

| ILLUM_A_BOOST        | 28 | I   | Supply voltage for high-side N-channel MOSFET gate driver. A 100 nF capacitor (typical) must be connected between this pin and ILLUM_A_SW. |  |

| ILLUM_A_FB           | 29 | I   | Input to the buck converter loop controlling ILED.                                                                                         |  |

| ILLUM_A_VIN          | 30 | Р   | Power input to the ILLUM Driver A.                                                                                                         |  |

| ILLUM_A_SW           | 31 | I/O | Switch node connection between high-side NFET and low-side NFET. Serves as common connection for the flying high side MOSFET driver.       |  |

| ILLUM_A_PGND         | 32 | GND | Ground connection to the ILLUM Driver A.                                                                                                   |  |

| ILLUM_B_BOOST        | 33 | I   | Supply voltage for high-side N-channel MOSFET gate driver.                                                                                 |  |

| ILLUM_B_VIN          | 34 | Р   | Power input to the ILLUM driver B.                                                                                                         |  |

| ILLUM_B_FB           | 35 | I   | Input to the buck converter loop controlling ILED.                                                                                         |  |

| ILLUM_B_SW           | 36 | I/O | Switch node connection between high-side NFET and low-side NFET.                                                                           |  |

| ILLUM_B_PGND         | 37 | GND | Ground connection to the ILLUM driver B.                                                                                                   |  |

| ILLUM_A_COMP1        | 38 | I/O | Connection node for feedback loop components                                                                                               |  |

| ILLUM_A_COMP2        | 39 | I/O | Connection node for feedback loop components                                                                                               |  |

| ILLUM_B_COMP1        | 40 | I/O | Connection node for feedback loop components                                                                                               |  |

| ILLUM_B_COMP2        | 41 | I/O | Connection node for feedback loop components                                                                                               |  |

| THERMAL_PAD          | 42 | GND | Thermal pad. Connect to clean system ground.                                                                                               |  |

| CLK_OUT              | 43 | 0   | Color wheel clock output                                                                                                                   |  |

| CW_SPEED_PWM_OUT     | 44 | 0   | Color wheel PWM output                                                                                                                     |  |

| SPI_VIN              | 45 | 1   | Supply for SPI interface                                                                                                                   |  |

| SPI_CLK              | 45 | 1   | SPI clock input                                                                                                                            |  |

|                      | 40 | I   |                                                                                                                                            |  |

## Pin Functions (continued)

| PIN               |    | I/O | DESCRIPTION                                                                                                                             |

|-------------------|----|-----|-----------------------------------------------------------------------------------------------------------------------------------------|

| SPI_MISO          | 47 | 0   | SPI data output                                                                                                                         |

| SPI_SS_Z          | 48 | I   | SPI chip select (active low)                                                                                                            |

| SPI_MOSI          | 49 | I   | SPI data input                                                                                                                          |

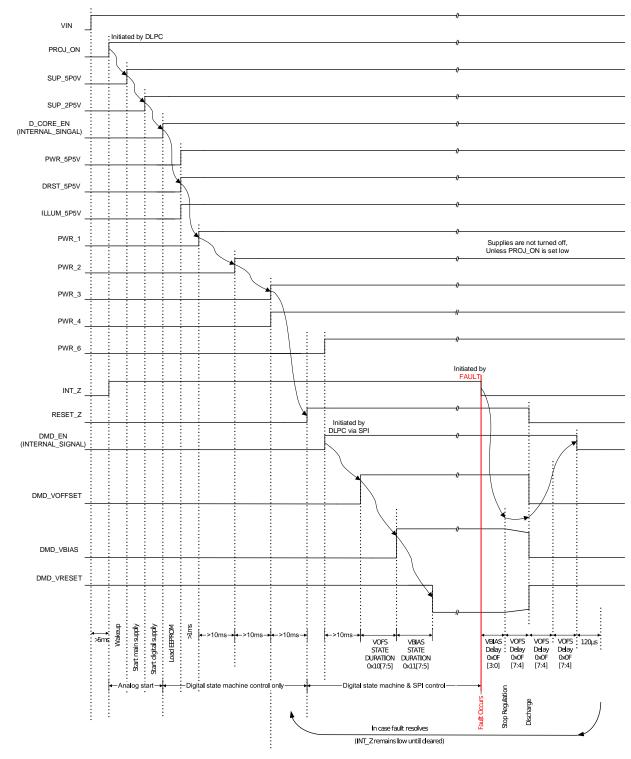

| PWR7_BOOST        | 50 | I   | Charge-pump-supply input for the high-side MOSFET gate drive circuit. Connect 100 nF capacitor between PWR7_BOOST and PWR7_SWITCH pins. |

| PWR7_FB           | 51 | Ι   | Converter feedback input. Connect to converter output voltage.                                                                          |

| PWR7_VIN          | 52 | Р   | Power supply input for converter.                                                                                                       |

| PWR7_SWITCH       | 53 | I/O | Switch node connection between high-side NFET and low-side NFET.                                                                        |

| PWR7_PGND         | 54 | GND | Ground pin. Power ground return for switching circuit.                                                                                  |

| ACMPR_LABB_SAMPLE | 55 | Ι   | Control signal to sample voltage at ACMPR_IN_LABB.                                                                                      |

| PROJ_ON           | 56 | Ι   | Input signal to enable/disable the IC and DLP projector.                                                                                |

| RESET_Z           | 57 | 0   | Reset output to the DLP system (active low). Pin is held low to reset DLP system.                                                       |

| INT_Z             | 58 | 0   | Interrupt output signal (open drain, active low). Connect to pull-up resistor.                                                          |

| DGND              | 59 | GND | Digital ground. Connect to ground plane.                                                                                                |

| CH_SEL_0          | 60 | I   | Control signal to enable either of CH1,2,3.                                                                                             |

| CH_SEL_1          | 61 | Ι   | Control signal to enable either of CH1,2,3.                                                                                             |

| PWR6_PGND         | 62 | GND | Ground pin. Power ground return for switching circuit.                                                                                  |

| PWR6_SWITCH       | 63 | I/O | Switch node connection between high-side NFET and low-side NFET.                                                                        |

| PWR6_VIN          | 64 | Р   | Power supply input for converter.                                                                                                       |

| PWR6_BOOST        | 65 | I   | Charge-pump-supply input for the high-side MOSFET gate drive circuit. Connect 100 nF capacitor between PWR6_BOOST and PWR6_SWITCH pins. |

| PWR6_FB           | 66 | Ι   | Converter feedback input. Connect to output voltage.                                                                                    |

| PWR5_VIN          | 67 | Р   | Power supply input for converter.                                                                                                       |

| PWR5_SWITCH       | 68 | I/O | Switch node connection between high-side NFET and low-side NFET.                                                                        |

| PWR5_BOOST        | 69 | I   | Charge-pump-supply input for the high-side MOSFET gate drive circuit. Connect 100nF capacitor between PWR5_BOOST and PWR5_SWITCH pins.  |

| PWR5_PGND         | 70 | GND | Ground pin. Power ground return for switching circuit.                                                                                  |

| PWR5_FB           | 71 | I   | Converter feedback input. Connect to output voltage.                                                                                    |

| PWR2_FB           | 72 | I   | Converter feedback input. Connect to output voltage.                                                                                    |

| PWR2_PGND         | 73 | GND | Ground pin. Power ground return for switching circuit.                                                                                  |

| PWR2_SWITCH       | 74 | I/O | Switch node connection between high-side NFET and low-side NFET.                                                                        |

| PWR2_VIN          | 75 | Р   | Power supply input for converter.                                                                                                       |

| PWR2_BOOST        | 76 | I   | Charge-pump-supply input for the high-side MOSFET gate drive circuit. Connect 100 nF capacitor between PWR2_BOOST and PWR2_SWITCH pins. |

| ACMPR_IN_1        | 77 | Ι   | Input for analog sensor signal.                                                                                                         |

| ACMPR_IN_2        | 78 | I   | Input for analog sensor signal.                                                                                                         |

| ACMPR_IN_3        | 79 | I   | Input for analog sensor signal.                                                                                                         |

| ACMPR_IN_LABB     | 80 | I   | Input for ambient light sensor, sampled input                                                                                           |

| ACMPR_OUT         | 81 | 0   | Analog comparator out                                                                                                                   |

| ACMPR_REF         | 82 | I   | Reference voltage input for analog comparator                                                                                           |

| PWR_VIN           | 83 | Р   | Power supply input for LDO_Bucks. Connect to system power.                                                                              |

| PWR_5P5V          | 84 | 0   | Filter pin for LDO_BUCKS. Internal analog supply for buck converters, typical 5.5 V.                                                    |

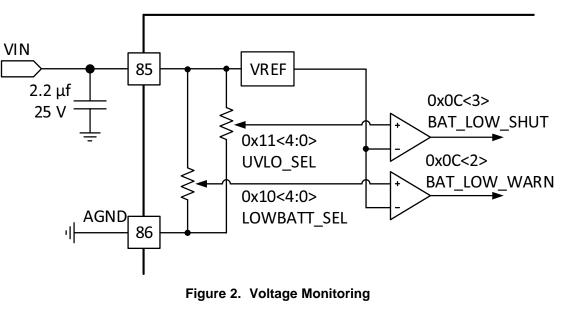

| VINA              | 85 | Р   | Input voltage supply pin for Reference system.                                                                                          |

| AGND              | 86 | GND | Analog ground pin.                                                                                                                      |

| PWR3_OUT          | 87 | 0   | Filter pin for LDO_2 DMD/DLPC/AUX, typical 2.5 V.                                                                                       |

| PWR3_VIN          | 88 | Р   | Power supply input for LDO_2. Connect to system power.                                                                                  |

| PWR4_OUT          | 89 | 0   | Filter pin for LDO_1 DMD/DLPC/AUX, typical 3.3 V.                                                                                       |

| <br>PWR4_VIN      | 90 | Р   | Power supply input for LDO_1. Connect to system power.                                                                                  |

## Pin Functions (continued)

| PIN         |     | I/O | DESCRIPTION                                                                                                                            |

|-------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------|

| SUP_2P5V    | 91  | 0   | Filter pin for LDO_V2V5. Internal supply voltage, typical 2.5 V.                                                                       |

| SUP_5P0V    | 92  | 0   | Filter pin for LDO_V5V. Internal supply voltage, typical 5 V.                                                                          |

| PWR1_PGND   | 93  | GND | Ground pin. Power ground return for switching circuit.                                                                                 |

| PWR1_FB     | 94  | Ι   | Converter feedback input. Connect to output voltage.                                                                                   |

| PWR1_SWITCH | 95  | I/O | Switch node connection between high-side NFET and low-side NFET.                                                                       |

| PWR1_VIN    | 96  | Р   | Power supply input for converter.                                                                                                      |

| PWR1_BOOST  | 97  | I   | Charge-pump-supply input for the high-side MOSFET gate drive circuit. Connect 100nF capacitor between PWR1_BOOST and PWR1_SWITCH pins. |

| DMD_VOFFSET | 98  | 0   | VOFS output rail. Connect to ceramic capacitor.                                                                                        |

| DMD_VBIAS   | 99  | 0   | VBIAS output rail. Connect to ceramic capacitor.                                                                                       |

| DMD_VRESET  | 100 | 0   | VRESET output rail. Connect to ceramic capacitor.                                                                                      |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

Over operating free-air temperature (unless otherwise noted).<sup>(1)</sup>

|                  |                                                                                                                                     | MIN  | MAX | UNIT |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|

|                  | ILLUM_A,B_BOOST                                                                                                                     | -0.3 | 28  |      |

|                  | ILLUM_A,B_BOOST (10 ns transient)                                                                                                   | -0.3 | 30  |      |

|                  | ILLUM_A,B_BOOST vs ILLUM_A,B_SWITCH                                                                                                 | -0.3 | 7   |      |

|                  | ILLUM_LSIDE_DRIVE                                                                                                                   | -0.3 | 7   |      |

|                  | ILLUM_HSIDE_DRIVE                                                                                                                   | -2   | 28  |      |

|                  | ILLUM_A_BOOST vs ILLUM_HSIDE_DRIVE                                                                                                  | -0.3 | 7   |      |

|                  | ILLUM_A,B_SW                                                                                                                        | -2   | 22  |      |

|                  | ILLUM_A,B_SW (10 ns transient)                                                                                                      | -3   | 27  |      |

|                  | PWR_VIN, PWR1_VIN, PWR2_VIN, PWR3_VIN, PWR4_VIN, PWR5_VIN, PWR6_VIN, PWR7_VIN, VINA, ILLUM_VIN, ILLUM_A,B_VIN, DRST_VIN             | -0.3 | 22  |      |

|                  | PWR1_BOOST, PWR2_BOOST, PWR5_BOOST, PWR6_BOOST, PWR7_BOOST                                                                          | -0.3 | 28  |      |

|                  | PWR1_BOOST, PWR2_BOOST, PWR5_BOOST, PWR6_BOOST, PWR7_BOOST (10 ns transient)                                                        | -0.3 | 30  |      |

|                  | PWR1_SWITCH, PWR2_SWITCH, PWR5_SWITCH, PWR6_SWITCH, PWR7_SWITCH                                                                     | -2   | 22  |      |

|                  | PWR1_SWITCH, PWR2_SWITCH, PWR5_SWITCH, PWR6_SWITCH, PWR7_SWITCH (10 ns transient)                                                   | -3   | 27  |      |

|                  | PWR1_FB, PWR2_FB, PWR5_FB, PWR6_FB, PWR7_FB                                                                                         | -0.3 | 6.5 |      |

| Voltage          | PWR1_BOOST, PWR2_BOOST, PWR5_BOOST, PWR6_BOOST,<br>PWR7_BOOST vs PWR1_SWITCH, PWR2_SWITCH, PWR5_SWITCH,<br>PWR6_SWITCH, PWR7_SWITCH | -0.3 | 6.5 | V    |

|                  | CH1_SWITCH, CH2_SWITCH, CH3_SWITCH, DRST_LS_IND, ILLUM_A,B_FB                                                                       | -0.3 | 20  |      |

|                  | ILLUM_A,B_COMP1, ILLUM_A,B_COMP2, INT_Z, PROJ_ON                                                                                    | -0.3 | 7   |      |

|                  | DRST_HS_IND                                                                                                                         | -18  | 7   |      |

|                  | ACMPR_IN_1, ACMPR_IN_2, ACMPR_IN_3, ACMPR_REF, ACMPR_IN_LABB, ACMPR_LABB_SAMPLE, ACMPR_OUT                                          | -0.3 | 3.6 |      |

|                  | SPI_VIN, SPI_CLK, SPI_MOSI, SPI_SS_Z, SPI_MISO, CH_SEL_0, CH_SEL_1, RESET_Z                                                         | -0.3 | 3.6 |      |

|                  | RLIM_K_1, RLIM_K_2, RLIM_1, RLIM_2                                                                                                  | -0.3 | 3.6 |      |

|                  | DGND, AGND, DRST_PGND, ILLUM_A,B_PGND, PWR1_PGND,<br>PWR2_PGND, PWR5_PGND, PWR6_PGND, PWR7_PGND, RLIM_BOT_K_1,<br>RLIM_BOT_2        | -0.3 | 0.3 |      |

|                  | DRST_5P5V, ILLUM_5P5V, PWR_5P5, PWR3_OUT, PWR4_OUT, SUP_5P0V                                                                        | -0.3 | 7   |      |

|                  | CH1 _GATE_CTRL,CH2_GATE_CTRL, CH3_GATE_CTRL                                                                                         | -0.3 | 7   |      |

|                  | CLK_OUT                                                                                                                             | -0.3 | 3.6 |      |

|                  | CW_SPEED_PWM                                                                                                                        | -0.3 | 7   |      |

|                  | SUP_2P5V                                                                                                                            | -0.3 | 3.6 |      |

|                  | DMD_VOFFSET                                                                                                                         | -0.3 | 12  |      |

|                  | DMD_VBIAS                                                                                                                           | -0.3 | 20  |      |

|                  | DMD_VRESET                                                                                                                          | -18  | 7   |      |

| Source current   | RESET_Z, ACMPR_OUT                                                                                                                  |      | 1   | m^   |

| Source current   | SPI_DOUT                                                                                                                            |      | 5.5 | mA   |

| Sink current     | RESET_Z, ACMPR_OUT                                                                                                                  |      | 1   | mA   |

|                  | SPI_DOUT, INT_Z                                                                                                                     |      | 5.5 | ША   |

| T <sub>stg</sub> | Storage temperature                                                                                                                 | -65  | 150 | °C   |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DLPA4000** DLPS132 – MAY 2018

www.ti.com

### 6.2 ESD Ratings

|                                   |               |                                                                                   | VALUE | UNIT |

|-----------------------------------|---------------|-----------------------------------------------------------------------------------|-------|------|

| V (1)                             | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(2)</sup>       | ±2000 | V    |

| V <sub>(ESD)</sub> <sup>(1)</sup> | discharge     | Charged device model (CDM), per JEDEC specification JESD22-C101, all $pins^{(3)}$ | ±500  | V    |

(1) Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges in to the device.

(2) JEDEC document JEP155 states that 500 V HBM allows safe manufacturing with a standard ESD control process.

(3) JEDEC document JEP157 states that 250 V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted).

|                        |                                                                                                                                         | MIN  | MAX  | UNIT |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

|                        | PWR_VIN, PWR1_VIN, PWR2_VIN, PWR3_VIN, PWR4_VIN,<br>PWR5_VIN, PWR6_VIN, PWR7_VIN, VINA, ILLUM_VIN,<br>ILLUM_A_VIN,ILLUM_B_VIN, DRST_VIN | 16   | 20   |      |

|                        | CH1_SWITCH, CH2_SWITCH, CH3_SWITCH, ILLUM_A,B_FB,                                                                                       | -0.1 | 8.6  |      |

|                        | INT_Z, PROJ_ON                                                                                                                          | -0.1 | 6    |      |

|                        | PWR1_FB, PWR2_FB, PWR5_FB, PWR6_FB, PWR7_FB                                                                                             | -0.1 | 5    |      |

| Input voltage range    | ACMPR_REF, CH_SEL_0, CH_SEL_01, SPI_CLK, SPI_MOSI,<br>SPI_SS_Z                                                                          | -0.1 | 3.6  | V    |

|                        | RLIM_BOT_K_1, RLIM_BOT_K_2                                                                                                              | -0.1 | 0.1  |      |

|                        | ACMPR_IN_1, ACMPR_IN_2, ACMPR_IN_3, LABB_IN_LABB                                                                                        | -0.1 | 1.5  |      |

|                        | SPI_VIN                                                                                                                                 | 1.7  | 3.6  |      |

|                        | RLIM_K_1, RLIM_K_2                                                                                                                      | -0.1 | 0.25 |      |

|                        | ILLUM_A,B_COMP1, ILLUM_A,B_COMP2                                                                                                        | -0.1 | 5.7  |      |

| Ambient temperature ra | ange                                                                                                                                    | 0    | 70   | °C   |

| Operating junction tem | perature                                                                                                                                | 0    | 120  | °C   |

### 6.4 Thermal Information

|                       |                                                             | DLPA4000    |      |

|-----------------------|-------------------------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                               | PFD (HTQFP) | UNIT |

|                       |                                                             | 100 PINS    |      |

| $R_{	ext{	heta}JA}$   | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 7.0         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 0.7         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance                        | N/A         | °C/W |

| ΨJT                   | Junction-to-top characterization parameter <sup>(4)</sup>   | 0.6         | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter <sup>(5)</sup> | 3.4         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance                | N/A         | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

(2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, but because the device is intended to be cooled with a heatsink from the top case of the package, the simulation includes a fan and heatsink attached to the DLPA4000 device. The heatsink is a 22 mm × 22 mm × 12 mm aluminum pin fin heatsink with a 12 × 12 × 3 mm stud. Base thickness is 2 mm and pin diameter is 1.5 mm with an array of 6 × 6 pins. The heatsink is attached to the DLPA4000 device with 100 um thick thermal grease with 3 W/m-K thermal conductivity. The fan is 20 × 20 × 8 mm with 1.6 cfm open volume flow rate and 0.22 in. water pressure at stagnation.

(3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

(4) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $R_{\theta JA}$ , using a procedure described in JESD51-2a (sections 6 and 7), but modified to include the fan and heatsink described in note 2.

(5) The junction-to-board characterization parameter, ψ<sub>JB</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining R<sub>0JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7), but modified to include the fan and heatsink described in note 2.

### 6.5 Electrical Characteristics

Over operating free-air temperature range.  $V_{IN} = 19.5 \text{ V}$ ,  $T_A = 0$  to +40°C, typical values are at  $T_A = 25$ °C, Configuration according to *Typical Application* ( $V_{IN} = 19.5 \text{ V}$ ,  $I_{OUT} = 32 \text{ A}$ , LED, external MOSFETs ) (unless otherwise noted).

|                       | PARAMETER                       | TEST CONDITIONS                                                                                                                                                  | MIN               | TYP  | MAX  | UNIT |

|-----------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|------|------|

|                       |                                 | SUPPLIES                                                                                                                                                         |                   |      |      |      |

| INPUT VOLT            | AGE                             |                                                                                                                                                                  |                   |      |      |      |

| V <sub>IN</sub>       | Input voltage range             | VINA – pin                                                                                                                                                       | 16 <sup>(1)</sup> | 19.5 | 20   | V    |

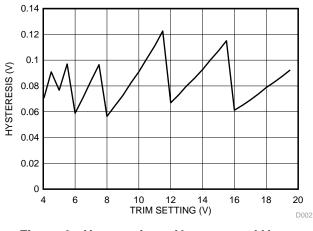

| V <sub>LOW_BAT</sub>  | Low battery warning threshold   | VINA falling (via 5 bit trim function, 0.5 V steps)                                                                                                              | 3.9               |      | 18.4 | V    |

|                       | Hysteresis                      | VINA rising                                                                                                                                                      |                   | 90   |      | mV   |

| V <sub>UVLO</sub>     | UVLO threshold                  | VINA falling (via 5 bit trim function, 0.5 V steps)                                                                                                              | 3.9               |      | 18.4 | V    |

| 0120                  | Hysteresis                      | VINA rising                                                                                                                                                      |                   | 90   |      | mV   |

| V <sub>STARTUP</sub>  | Startup voltage                 | DMD_VBIAS, DMD_VOFFSET,<br>DMD_VRESET loaded with 10 mA                                                                                                          | 6                 |      |      | V    |

| INPUT CURR            | ENT                             |                                                                                                                                                                  |                   |      |      |      |

| I <sub>IDLE</sub>     | Idle current                    | IDLE mode, all VIN pins combined                                                                                                                                 |                   | 15   |      | μA   |

| I <sub>STD</sub>      | Standby current                 | STANDBY mode, analog, internal<br>supplies and LDOs enabled, DMD,<br>ILLUMINATION and BUCK<br>CONVERTERS disabled.                                               |                   | 3.7  |      | mA   |

| I <sub>Q_DMD</sub>    | Quiescent current (DMD)         | Quiescent current DMD block (in addtion to I <sub>STD</sub> ), VINA + DRST_VIN                                                                                   |                   | 0.49 |      | mA   |

| I <sub>Q_ILLUM</sub>  | Quiescent current (ILLUM)       | Quiescent current ILLUM block (in<br>addtion to I <sub>STD</sub> ), V_openloop= 3 V<br>(0x18, ILLUM_OLV_SEL), VINA +<br>ILLUM_VIN + ILLUM_A_VIN +<br>ILLUM_B_VIN |                   | 21   |      | mA   |

|                       | Quiescent current<br>(per BUCK) | Quiescent current per BUCK converter<br>(in addtion to I <sub>STD</sub> ), Normal mode, VINA<br>+ PWR_VIN + PWR1,2,5,6,7_VIN,<br>PWR1,2,5,6,7_VOUT = 1 V         |                   | 4.3  |      |      |

|                       |                                 | Quiescent current per BUCK converter<br>(in addtion to I <sub>STD</sub> ), Normal mode, VINA<br>+ PWR_VIN + PWR1,2,5,6,7_VIN,<br>PWR1,2,5,6,7_VOUT = 5 V         |                   | 15   |      | - mA |

| I <sub>Q_BUCK</sub>   |                                 | Quiescent current per BUCK converter<br>(in addtion to I <sub>STD</sub> ), Cycle-skipping<br>mode, VINA + PWR_VIN +<br>PWR1,2,5,6,7_VIN = 1 V                    |                   | 0.41 |      |      |

|                       |                                 | Quiescent current per BUCK converter<br>(in addtion to I <sub>STD</sub> ), Cycle-skipping<br>mode, VINA + PWR_VIN +<br>PWR1,2,5,6,7_VIN = 5 V                    |                   | 0.46 |      |      |

| I <sub>Q_TOTAL</sub>  | Quiescent current (Total)       | Typical Application: ACTIVE mode, all<br>VIN pins combined, DMD,<br>ILLUMINATION and PWR1,2 enabled,<br>PWR3,4,5,6,7 disabled.                                   |                   | 38   |      | mA   |

| INTERNAL S            | UPPLIES                         |                                                                                                                                                                  |                   |      |      |      |

| V <sub>SUP_5P0V</sub> | Internal supply, analog         |                                                                                                                                                                  |                   | 5    |      | V    |

| - 30F_3F0V            |                                 |                                                                                                                                                                  |                   |      |      |      |

(1) VIN must be higher than the UVLO voltage setting, including after accounting for AC noise on VIN, for the DLPA4000 device to fully operate. While 15.5 V is the min VIN voltage supported, TI recommends that the UVLO is never set below 16 V. 16 V gives margin above the minimum to protect against the case where someone suddenly removes VIN's power supply which causes the VIN voltage to drop rapidly. Failure to keep VIN above 16.0 V before the mirrors are parked and VOFS, VRST, and VBIAS supplies are properly shut down can result in permanent damage to the DMD. Because 16 V is 500 mV above 15.5 V, when UVLO trips there is time for the DLPA4000 device and DLPC343x to park the DMD mirrors and do a fast shut down of supplies VOFS, VRST, and VBIAS. Regardless of the UVLO setting, , include enough bulk capacitance on VIN inside the projector to maintain VIN above 15.5 V for at least 100 µs after VIN power supply is suddenly removed causing a UVLO fault.

Copyright © 2018, Texas Instruments Incorporated

## **Electrical Characteristics (continued)**

Over operating free-air temperature range.  $V_{IN} = 19.5 \text{ V}$ ,  $T_A = 0$  to +40°C, typical values are at  $T_A = 25^{\circ}$ C, Configuration according to *Typical Application* ( $V_{IN} = 19.5 \text{ V}$ ,  $I_{OUT} = 32 \text{ A}$ , LED, external MOSFETs ) (unless otherwise noted).

|                         | PARAMETER                                 | TEST CONDITIONS                                                                 | MIN | TYP  | MAX | UNIT |

|-------------------------|-------------------------------------------|---------------------------------------------------------------------------------|-----|------|-----|------|

| V <sub>DRST_VIN</sub>   |                                           |                                                                                 | 6   | 12   | 20  | V    |

| V <sub>DRST_5P5V</sub>  |                                           |                                                                                 |     | 5.5  |     | V    |

|                         |                                           | Rising                                                                          |     | 80%  |     |      |

| PGOOD                   | Power good DRST_5P5V                      | Faling                                                                          |     | 60%  |     |      |

| OVP                     | Overvoltage protection<br>DRST_5P5V       |                                                                                 |     | 7.2  |     | V    |

|                         | Regulator dropout                         | At 25 mA, VDRST_VIN= 5.5 V                                                      |     | 56   |     | mV   |

|                         | Regulator current limit <sup>(2)</sup>    |                                                                                 | 300 | 340  | 400 | mA   |

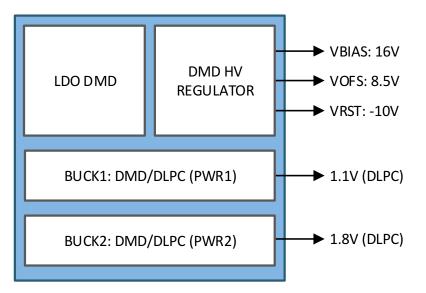

|                         |                                           | DMD - BUCK CONVERTERS                                                           |     |      |     |      |

| OUTPUT VOL              | TAGE                                      |                                                                                 |     |      |     |      |

| V <sub>PWR_1_VOUT</sub> | Output Voltage                            |                                                                                 |     | 1.1  |     | V    |

| V <sub>PWR_2_VOUT</sub> | Output Voltage                            |                                                                                 |     | 1.8  |     | V    |

|                         | DC output voltage accuracy                | I <sub>OUT</sub> = 0 mA                                                         | -3% |      | 3%  |      |

| MOSFET                  |                                           |                                                                                 |     |      |     |      |

| R <sub>ON,H</sub>       | High side switch resistance               | $25^{\circ}$ C, V <sub>PWR_1,2_Boost</sub> - V <sub>PWR1,2_SWITCH</sub> = 5.5 V |     | 150  |     | mΩ   |

| R <sub>ON,L</sub>       | Low side switch resistance <sup>(2)</sup> | 25°C                                                                            |     | 85   |     | mΩ   |

| LOAD CURRE              | NT                                        |                                                                                 |     |      |     |      |

|                         | Allowed Load Current.                     |                                                                                 |     |      | 3   | Α    |

| I <sub>OCL</sub>        | Current limit <sup>(2)</sup>              | L <sub>OUT</sub> = 3.3 μH                                                       | 3.2 | 3.6  | 4.2 | А    |

| ON-TIME TIME            | ER CONTROL                                |                                                                                 |     |      |     |      |

| t <sub>ON</sub>         | On time                                   | $V_{IN} = 12 V, V_O = 5 V$                                                      |     | 120  |     | ns   |

| t <sub>OFF(MIN)</sub>   | Minimum off time <sup>(2)</sup>           | $T_A = 25^{\circ}C, V_{FB} = 0 V$                                               |     | 270  |     | ns   |

| START-UP                |                                           |                                                                                 |     |      | ·   |      |

| PGOOD                   | Soft start                                |                                                                                 | 1   | 2.5  | 4   | ms   |

| Ratio <sub>OV</sub>     | Overvoltage protection                    |                                                                                 |     | 120% |     |      |

| Ratio <sub>PG</sub>     | Relative power good level                 | Low to High                                                                     |     | 72%  |     |      |

|                         |                                           | ILLUMINATION - LDO ILLUM                                                        |     |      |     |      |

| VILLUM_VIN              |                                           |                                                                                 | 6   | 12   | 20  | V    |

| VILLUM_5P5V             |                                           |                                                                                 |     | 5.5  |     | V    |

|                         |                                           | Rising                                                                          |     | 80%  |     |      |

| PGOOD                   | Power good ILLUM_5P5V                     | Falling                                                                         |     | 60%  |     |      |

| OVP                     | Overvoltage protection<br>ILLUM_5P5V      |                                                                                 |     | 7.2  |     | V    |

|                         | Regulator dropout                         | At 25 mA, V <sub>ILLUM_VIN</sub> = 5.5 V                                        |     | 53   |     | mV   |

|                         | Regulator current limit <sup>(2)</sup>    |                                                                                 | 300 | 340  | 400 | mA   |

|                         |                                           | ILLUMINATION - DRIVER A,B                                                       |     |      |     |      |

| VILLUM_A,B_IN           | Input supply voltage range                |                                                                                 | 6   | 12   | 20  | V    |

| PWM                     | ···· • •                                  |                                                                                 |     |      |     |      |

| fsw                     | Oscillator frequency                      | 3 V < V <sub>IN</sub> < 20 V                                                    |     | 600  |     | kHz  |

|                         | . ,                                       | HDRV off to LDRV on, TRDLY = 0                                                  |     | 28   |     |      |

| t <sub>DEAD</sub>       | Output driver dead time                   | HDRV off to LDRV on, TRDLY = 1                                                  |     | 40   |     | ns   |

|                         | •                                         | ,                                                                               |     | -    |     |      |

(2) Not production tested.

### **Electrical Characteristics (continued)**

Over operating free-air temperature range.  $V_{IN} = 19.5 \text{ V}$ ,  $T_A = 0$  to +40°C, typical values are at  $T_A = 25$ °C, Configuration according to *Typical Application* ( $V_{IN} = 19.5 \text{ V}$ ,  $I_{OUT} = 32 \text{ A}$ , LED, external MOSFETs ) (unless otherwise noted).

|                        | PARAMETER                                 | TEST CONDITIONS                                                                                                                                                        | MIN   | TYP  | MAX | UNIT |  |

|------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-----|------|--|

| R <sub>HDHI</sub>      | High-side driver pull-up resistance       | $\label{eq:Villum_a,b_boot} \begin{split} V_{\text{ILLUM}\_A, B\_BOOT} &- V_{\text{ILLUM}\_A, B\_SW} = 5 \text{ V}, \\ I_{\text{HDRV}} &= -100 \text{ mA} \end{split}$ |       | 4.9  |     | Ω    |  |

| R <sub>HDLO</sub>      | High-side driver pull-down<br>resistance  | $\label{eq:Villum_a,b_boot} \begin{split} V_{\text{ILLUM}\_A,B\_BOOT} &- V_{\text{ILLUM}\_A,B\_SW} = 5 \text{ V},\\ I_{\text{HDRV}} &= 100 \text{ mA} \end{split}$     |       | 3    |     | Ω    |  |

| R <sub>LDHI</sub>      | Low-side driver pull-up resistance        | $I_{LDRV} = -100 \text{ mA}$                                                                                                                                           |       | 3.1  |     | Ω    |  |

| R <sub>LDLO</sub>      | Low-side driver pull-down resistance      | I <sub>LDRV</sub> = 100 mA                                                                                                                                             |       | 2.4  |     | Ω    |  |

| t <sub>HRISE</sub>     | High-side driver rise time <sup>(2)</sup> | C <sub>LOAD</sub> = 5 nF                                                                                                                                               |       | 23   |     | ns   |  |

| t <sub>HFALL</sub>     | High-side driver fall time <sup>(2)</sup> | C <sub>LOAD</sub> = 5 nF                                                                                                                                               |       | 19   |     | ns   |  |

| t <sub>LRISE</sub>     | Low-side driver rise time <sup>(2)</sup>  | C <sub>LOAD</sub> = 5 nF                                                                                                                                               |       | 23   |     | ns   |  |

| t <sub>LFALL</sub>     | Low-side driver fall time <sup>(2)</sup>  | C <sub>LOAD</sub> = 5 nF                                                                                                                                               |       | 17   |     | ns   |  |

| OVERCURREN             | T PROTECTION                              |                                                                                                                                                                        |       |      |     |      |  |

| HSD OC                 | High-Side Drive Over Current threshold    | External switches, $V_{DS}$ threshold <sup>(2)</sup> .                                                                                                                 |       | 185  |     | mV   |  |

| BOOT DIODE             |                                           |                                                                                                                                                                        |       |      | ·   |      |  |

| V <sub>DFWD</sub>      | Bootstrap diode forward voltage           | I <sub>BOOT</sub> = 5 mA                                                                                                                                               |       | 0.75 |     | V    |  |

| PGOOD                  |                                           |                                                                                                                                                                        |       |      |     |      |  |

| RatioUV                | Undervoltage protection                   |                                                                                                                                                                        |       | 89%  |     |      |  |

| INTERNAL RGI           | B STROBE CONTROLLER SWITCH                | IES                                                                                                                                                                    |       |      | I   |      |  |

| R <sub>ON</sub>        | ON-resistance                             | CH1,2,3_SWITCH                                                                                                                                                         |       | 30   | 45  | mΩ   |  |

| ILEAK                  | OFF-state leakage current                 | V <sub>DS</sub> = 5.0 V                                                                                                                                                |       |      | 0.1 | μA   |  |

| I <sub>MAX</sub>       | Maximum current                           |                                                                                                                                                                        |       | 6    |     | A    |  |

|                        | ERNAL RGB STROBE CONTROLL                 | ER SWITCHES                                                                                                                                                            |       |      |     |      |  |

| CHx_GATE_C             |                                           | ILLUM_SW_ILIM_EN[2:0] = 7, register<br>0x02, I <sub>SINK</sub> = 400 μA                                                                                                |       | 4.35 |     | V    |  |

| NTR_HIGH               | Gate control high level                   | ILLUM_SW_ILIM_EN[2:0] = 0, register<br>0x02, I <sub>SINK</sub> = 400 μA                                                                                                |       | 5.25 |     |      |  |

| CHx_GATE_C             | <b>2</b> · · · · · · · · ·                | ILLUM_SW_ILIM_EN[2:0] = 7, register<br>0x02, I <sub>SINK</sub> = 400 μA                                                                                                |       | 55   |     |      |  |

| NTR_LOW                | Gate control low level                    | ILLUM_SW_ILIM_EN[2:0] = 0, register<br>0x02, I <sub>SINK</sub> = 400 μA                                                                                                |       | 55   |     | mV   |  |

| LED CURRENT            | CONTROL                                   |                                                                                                                                                                        |       |      | ·   |      |  |

| V <sub>LED_ANODE</sub> | LED Anode voltage <sup>(2)</sup>          | Ratio with respect to V <sub>ILLUM_A,B_VIN</sub> (Duty cycle limitation).                                                                                              | 0.85x |      |     |      |  |

|                        | -                                         |                                                                                                                                                                        |       |      | 8.6 | V    |  |

| I <sub>LED</sub>       | LED currents                              | $V_{ILLUM\_A,B\_VIN} \ge 8 V$ . See register SWx_IDAC[9:0] for settings.                                                                                               | 1     |      | 32  | А    |  |

|                        | DC current offset,<br>CH1,2,3_SWITCH      | $R_{LIM} = 4 m\Omega$                                                                                                                                                  | -150  | 0    | 150 | mA   |  |

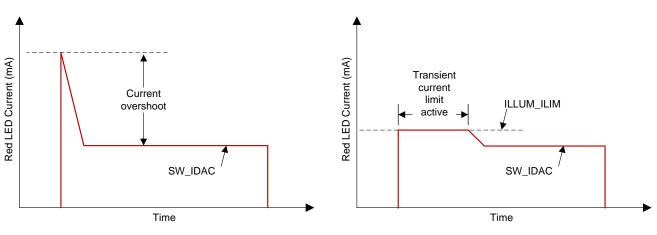

|                        | Transient LED current limit range         | 20% higher than $I_{LED}$ . Min-setting, $R_{LIM}$ = 4 m $\Omega$ .                                                                                                    |       | 11%  |     |      |  |

|                        | (programmable)                            | 20% higher than $I_{LED}$ . Max-setting, $R_{LIM}$ = 4 m $\Omega$ . Percentage of max current.                                                                         |       | 133% |     |      |  |

| t <sub>RISE</sub>      | Current rise time                         | $I_{LED}$ from 5% to 95%, $I_{LED}$ = 600 mA, transient current limit disabled <sup>(2)</sup> .                                                                        |       |      | 50  | μs   |  |

|                        | В                                         | UCK CONVERTERS - LDO_BUCKS                                                                                                                                             |       |      |     |      |  |

| V <sub>PWR_VIN</sub>   | Input voltage range<br>PWR1,2,5,6,7_VIN   |                                                                                                                                                                        | 16    | 19.5 | 20  | V    |  |

| V <sub>PWR_5P5V</sub>  | PWR_5P5V                                  |                                                                                                                                                                        |       | 5.5  |     | V    |  |

## **Electrical Characteristics (continued)**

Over operating free-air temperature range.  $V_{IN} = 19.5 \text{ V}$ ,  $T_A = 0$  to +40°C, typical values are at  $T_A = 25^{\circ}$ C, Configuration according to *Typical Application* ( $V_{IN} = 19.5 \text{ V}$ ,  $I_{OUT} = 32 \text{ A}$ , LED, external MOSFETs ) (unless otherwise noted).

|                                 | PARAMETER                                          | TEST CONDITIONS                                                             | MIN                   | ТҮР  | MAX  | UNIT |

|---------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------|-----------------------|------|------|------|

|                                 |                                                    | Rising                                                                      |                       | 80%  |      |      |

| PGOOD                           | Power good PWR_5P5V                                | Falling                                                                     |                       | 60%  |      |      |

| OVP                             | Overvoltage Protection<br>PWR_5P5V                 |                                                                             |                       | 7.2  |      | V    |

|                                 | Regulator dropout                                  | At 25 mA, V <sub>PWR_VIN</sub> = 5.5 V                                      |                       | 41   |      | mV   |

|                                 | Regulator current limit <sup>(2)</sup>             |                                                                             | 300                   | 340  | 400  | mA   |

|                                 | BUCK CONVERTE                                      | RS - GENERAL PURPOSE BUCK CONVE                                             | ERTERS <sup>(3)</sup> |      |      |      |

| OUTPUT VOLT                     | AGE                                                |                                                                             |                       |      |      |      |

| V <sub>PWR_5,6,7_VOU</sub><br>t | Output Voltage (General Purpose<br>Buck1,2,3)      | 8-bit programmable                                                          | 1                     |      | 5    | V    |

|                                 | DC output voltage accuracy                         | I <sub>OUT</sub> = 0 mA                                                     | -3.5%                 |      | 3.5% |      |

| MOSFET                          |                                                    |                                                                             |                       |      | ·    |      |

| R <sub>ON,H</sub>               | High-side switch resistance                        | 25°C, V <sub>PWR5,6,7_Boost</sub> – V <sub>PWR5,6,7_SWITCH</sub><br>= 5.5 V |                       | 150  |      | mΩ   |

| R <sub>ON,L</sub>               | Low-side switch resistance <sup>(2)</sup>          | 25°C                                                                        |                       | 85   |      | mΩ   |

| LOAD<br>CURRENT                 |                                                    |                                                                             |                       |      |      |      |

|                                 | Allowed load current PWR6.                         |                                                                             |                       | 2    |      | А    |

|                                 | Allowed load current PWR5, PWR7.                   | Buck converters should not be used.                                         |                       |      |      | А    |

| I <sub>OCL</sub>                | Current limit <sup>(2)</sup>                       | L <sub>OUT</sub> = 3.3 μH                                                   | 3.2                   | 3.6  | 4.2  | А    |

| ON-TIME<br>TIMER<br>CONTROL     |                                                    |                                                                             |                       |      |      |      |

| t <sub>ON</sub>                 | On time                                            | V <sub>IN</sub> = 12 V, V <sub>O</sub> = 5 V                                |                       | 120  |      | ns   |

| t <sub>OFF(min)</sub>           | Minimum off time <sup>(2)</sup>                    | T <sub>A</sub> = 25°C, V <sub>FB</sub> = 0 V                                |                       | 270  | 310  | ns   |

| START-UP                        |                                                    |                                                                             |                       |      | i    |      |

| t <sub>SS</sub>                 | Soft-start period                                  |                                                                             | 1                     | 2.5  | 4    | ms   |

| PGOOD                           |                                                    | •                                                                           |                       |      |      |      |

| Ratio <sub>OV</sub>             | Overvoltage protection                             |                                                                             |                       | 120% |      |      |

| Ratio <sub>PG</sub>             | Relative power good level                          | Low to High                                                                 |                       | 72%  |      |      |

|                                 |                                                    | AUXILIARY LDOs                                                              |                       |      |      |      |

| V <sub>PWR3,4_VIN</sub>         | Input voltage range                                | LDO1 (PWR4), LDO2 (PWR3)                                                    | 3.3                   | 12   | 20   | V    |

| PGOOD                           | Power good PWR3_VOUT,<br>PWR4_VOUT                 | PWR3_VOUT and PWR4_VOUT rising                                              |                       | 80%  |      |      |

|                                 |                                                    | PWR3_VOUT and PWR4_VOUT falling                                             |                       | 60%  |      |      |

| OVP                             | Overvoltage Protection<br>PWR3_VOUT, PWR4_VOUT     |                                                                             |                       | 7    |      | V    |

|                                 | DC output voltage accuracy<br>PWR3_VOUT, PWR4_VOUT | I <sub>OUT</sub> = 0 mA                                                     | -3%                   |      | 3%   |      |

|                                 | Regulator current limit <sup>(2)</sup>             |                                                                             | 300                   | 340  | 400  | mA   |

| t <sub>ON</sub>                 | Turn-on time                                       | to 80% of V <sub>OUT</sub> = PWR3 and PWR4, C = 1 $\mu$ F                   |                       | 40   |      | μs   |

| LDO2 (PWR3)                     |                                                    |                                                                             |                       |      |      |      |

| V <sub>PWR3_VOUT</sub>          | Output Voltage PWR3_VOUT                           |                                                                             |                       | 2.5  |      | V    |

|                                 | Load Current capability                            |                                                                             |                       | 200  |      | mA   |

|                                 | DC Load regulation PWR3_VOUT                       | V <sub>OUT</sub> = 2.5 V, 5 ≤ I <sub>OUT</sub> ≤ 200 mA                     |                       | -70  |      | mV/A |

(3) General Purpose Buck2 (PWR6) currently supported, others may be available in the future.

## **Electrical Characteristics (continued)**

Over operating free-air temperature range.  $V_{IN} = 19.5 \text{ V}$ ,  $T_A = 0$  to +40°C, typical values are at  $T_A = 25$ °C, Configuration according to *Typical Application* ( $V_{IN} = 19.5 \text{ V}$ ,  $I_{OUT} = 32 \text{ A}$ , LED, external MOSFETs ) (unless otherwise noted).

|                                   | PARAMETER                             | TEST CONDITIONS                                                             | MIN                       | TYP  | MAX                       | UNIT |

|-----------------------------------|---------------------------------------|-----------------------------------------------------------------------------|---------------------------|------|---------------------------|------|

|                                   | DC Line regulation PWR3_VOUT          | V <sub>OUT</sub> = 2.5 V, I <sub>OUT</sub> = 5 mA, 3.3 ≤<br>PWR3_VIN ≤ 20 V |                           | 30   |                           | μV/V |

| LDO1 (PWR4)                       |                                       |                                                                             |                           |      |                           |      |

| V <sub>PWR4_VOUT</sub>            | Output Voltage PWR4_VOUT              |                                                                             |                           | 3.3  |                           | V    |

|                                   | Load Current capability               |                                                                             |                           | 200  |                           | mA   |

|                                   | DC Load regulation PWR4_VOUT          | $V_{OUT}$ = 3.3 V, 5 ≤ $I_{OUT}$ ≤ 200 mA                                   |                           | -70  |                           | mV/A |

|                                   | DC Line regulation PWR4_VOUT          | $V_{OUT}$ = 3.3 V, $I_{OUT}$ = 5 mA, 4 ≤ PWR4_VIN ≤ 20 V                    |                           | 30   |                           | μV/V |

|                                   | Regulator dropout                     | $I_{OUT}$ = 25 mA, $V_{OUT}$ = 3.3 V, $V_{PWR4\_VIN}$ = 3.3 V               |                           | 48   |                           | mV   |

|                                   |                                       | MEASUREMENT SYSTEM                                                          |                           |      | i                         |      |

| AFE                               |                                       |                                                                             |                           |      |                           |      |

|                                   |                                       | AFE_GAIN[1:0] = 01                                                          |                           | 1    |                           |      |

| G                                 | Amplifier gain (PGA)                  | AFE_GAIN[1:0] = 10                                                          |                           | 9.5  |                           | V/V  |

|                                   |                                       | AFE_GAIN[1:0] = 11                                                          |                           | 18   |                           |      |

|                                   |                                       | PGA, AFE_CAL_DIS = $1^{(2)}$                                                | -1                        |      | 1                         |      |

| V <sub>OFS</sub>                  | Input referred offset voltage         | Comparator <sup>(2)</sup>                                                   | -1.5                      |      | +1.5                      | mV   |

|                                   |                                       | To 1% of final value <sup>(2)</sup> .                                       |                           | 46   | 67                        |      |

| τ <sub>RC</sub>                   | Settling time                         | To 0.1% of final value $^{(2)}$ .                                           |                           | 69   | 100                       | μs   |

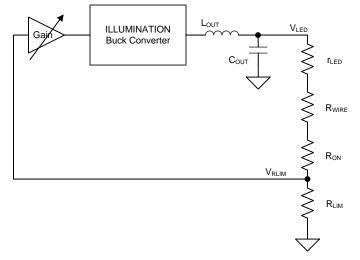

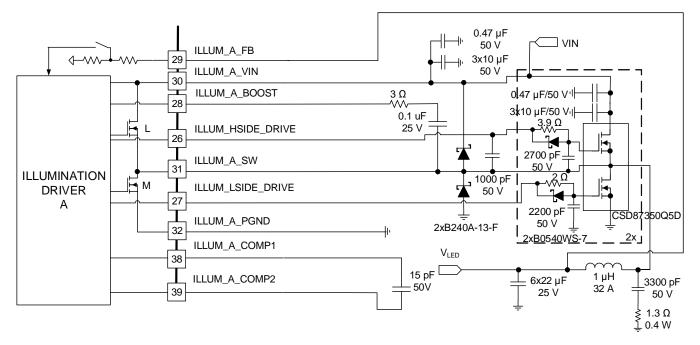

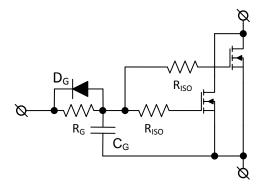

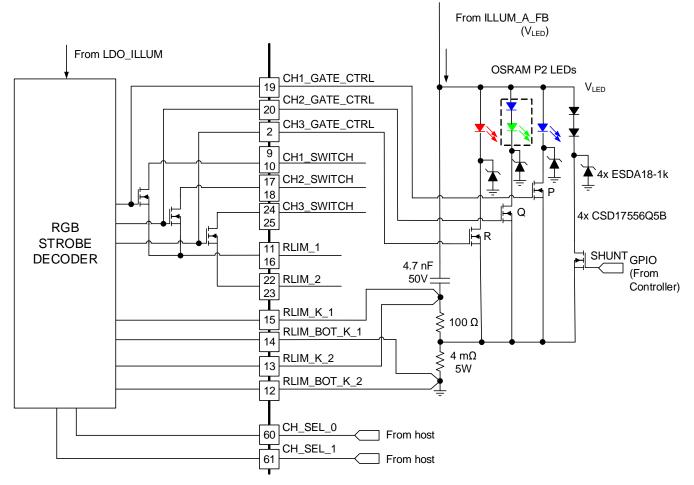

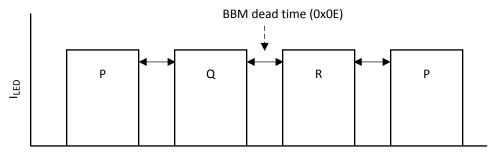

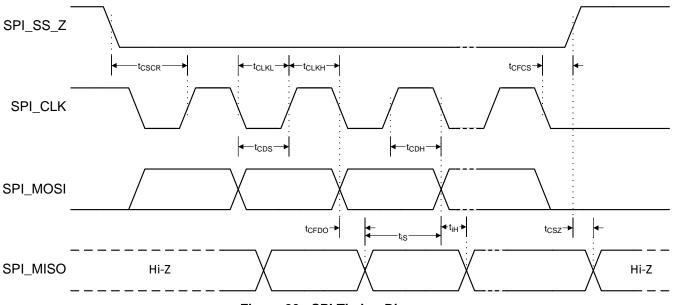

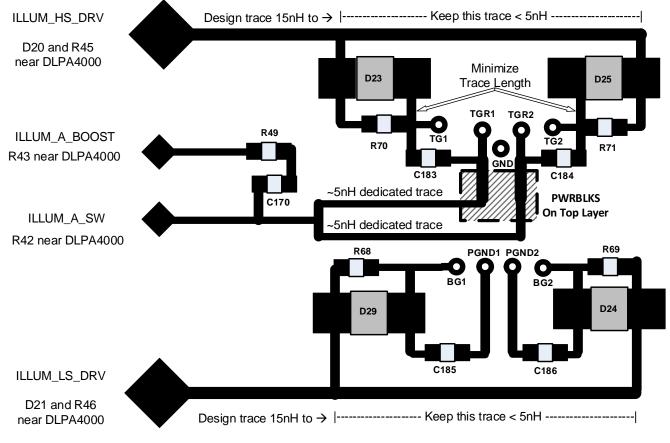

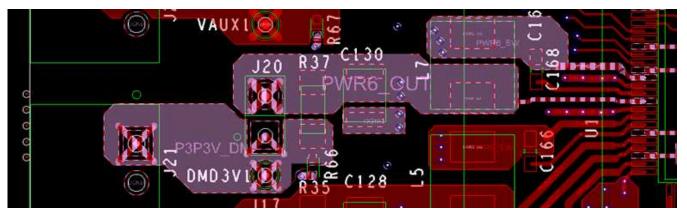

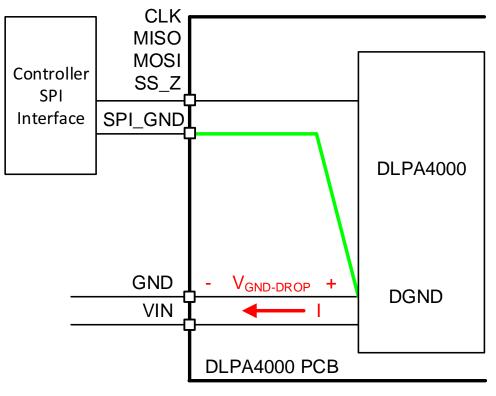

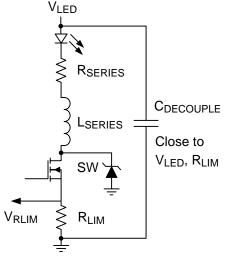

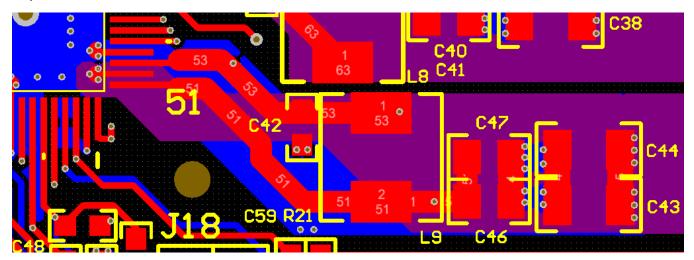

| V <sub>ACMPR_IN_1,2,3</sub>       | Input voltage Range<br>ACMPR_IN_1,2,3 |                                                                             | 0                         | 00   | 1.5                       | V    |