www.ti.com

SNAS354A -JUNE 2007-REVISED MAY 2013

# LM48821 Boomer® Audio Power Amplifier Series Direct Coupled, Ultra Low Noise, 52mW Differential Input Stereo Headphone Amplifier with I2C Volume Control

Check for Samples: LM48821, LM48821TLEVAL

#### **FEATURES**

- · Ground Referenced Outputs

- Differential Inputs

- I<sup>2</sup>C Volume and Mode Controls

- Available in Space-Saving DSBGA Package

- Ultra Low Current Shutdown Mode

- Advanced Output Transient Suppression Circuitry Eliminates Noises During Turn-On and Turn-Off Transitions

- 2.0V to 4.0V Operation (PV<sub>DD</sub> and SV<sub>DD</sub>)

- 1.8 to 4.0V Operation (I<sup>2</sup>CV<sub>DD</sub>)

- No Output Coupling Capacitors, Snubber Networks, Bootstrap Capacitors, or Gain-Setting Resistors Required

#### **APPLICATIONS**

- Notebook PCs

- Desktop PCs

- Mobile Phones

- PDAs

- Portable Electronic Devices

- MP3 Players

#### **KEY SPECIFICATIONS**

- Improved PSRR at 217Hz: 82dB (typ)

- Stereo Output Power at VDD = 3V, RL = 16Ω, THD+N = 1%: 52mW (typ)

- Mono Output Power at VDD = 3V, RL = 16Ω, THD+N = 1%: 93mW (typ)

- Shutdown current: 0.1µA (typ)

#### DESCRIPTION

With its directly-coupled output technology, the LM48821 is a variable gain audio power amplifier capable of delivering  $52 \text{mW}_{\text{RMS}}$  per channel into a  $16\Omega$  single-ended load with less than 1% THD+N from a 3V power supply. The I<sup>2</sup>C volume control has a range of -76 dB to 18 dB.

The LM48821's Tru-GND technology utilizes advanced charge pump technology to generate the LM48821's negative supply voltage. This eliminates the need for output-coupling capacitors typically used with single-ended loads.

Boomer audio power amplifiers were designed specifically to provide high quality output power with a minimal amount of external components. The LM48821 does not require output coupling capacitors or bootstrap capacitors, and therefore, is ideally suited for mobile phone and other low voltage applications where minimal power consumption is a primary requirement.

The LM48821 incorporates selectable low-power consumption shutdown and channel select modes.

The LM48821 contains advanced output transient suppression circuitry that eliminates noises which would otherwise occur during turn-on and turn-off transitions.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

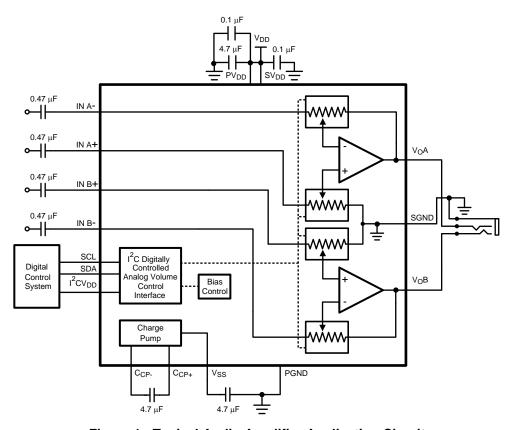

## **Typical Application**

Figure 1. Typical Audio Amplifier Application Circuit

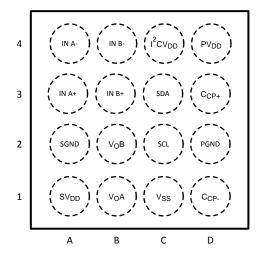

# **Connection Diagram**

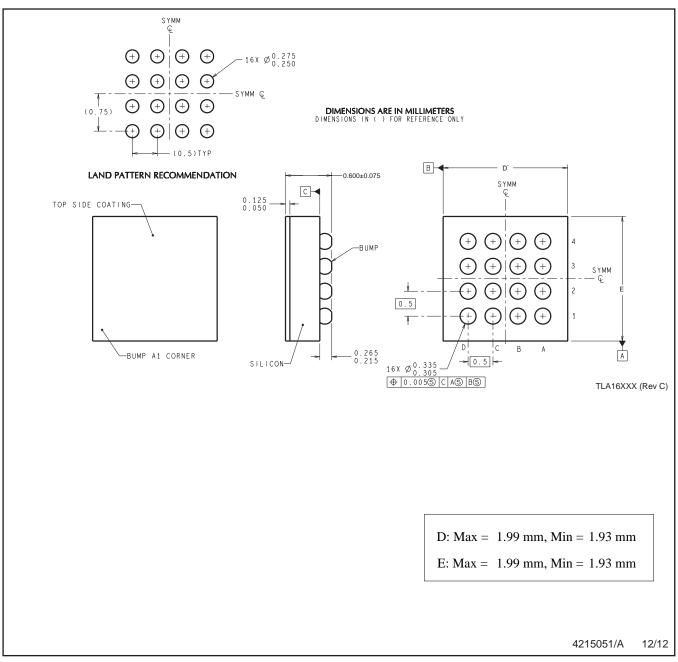

Figure 2. DSBGA - Top View See YZR0016 Package

www.ti.com

## **PIN DESCRIPTIONS**

| Pin Designator | Pin Name                        | Pin Function                                            |  |  |  |

|----------------|---------------------------------|---------------------------------------------------------|--|--|--|

| A1             | SV <sub>DD</sub>                | Signal power supply input                               |  |  |  |

| A2             | SGND                            | Signal ground                                           |  |  |  |

| A3             | IN A+                           | Left non-inverting input                                |  |  |  |

| A4             | IN A- Left inverting input      |                                                         |  |  |  |

| B1             | B1 V <sub>O</sub> A Left output |                                                         |  |  |  |

| B2             | Right output                    |                                                         |  |  |  |

| В3             | IN B+                           | Right non-inverting input                               |  |  |  |

| B4             | IN B-                           | Right inverting input                                   |  |  |  |

| C1             | V <sub>SS</sub>                 | DC to DC converter output                               |  |  |  |

| C2             | SCL                             | I <sup>2</sup> C serial clock input                     |  |  |  |

| C3             | SDA                             | I <sup>2</sup> C serial data input                      |  |  |  |

| C4             | I <sup>2</sup> CV <sub>DD</sub> | I <sup>2</sup> C supply voltage input                   |  |  |  |

| D1             | C <sub>CP</sub> -               | DC to DC converter flying capacitor inverting input     |  |  |  |

| D2             | D2 PGND Power ground            |                                                         |  |  |  |

| D3             | C <sub>CP+</sub>                | DC to DC converter flying capacitor non-inverting input |  |  |  |

| D4             | $PV_{DD}$                       | DC to DC converter power supply input                   |  |  |  |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **Absolute Maximum Ratings** (1)(2)(3)

| 4.5V                           |

|--------------------------------|

| −65°C to +150°C                |

| -0.3V to V <sub>DD</sub> +0.3V |

| Internally Limited             |

| 2000V                          |

| 200V                           |

| 150°C                          |

|                                |

| 105°C/W                        |

|                                |

- (1) All voltages are measured with respect to the GND pin unless otherwise specified.

- Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional but do not specify performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which ensure specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are for parameters where no limit is given, however, the typical value is a good indication of device performance.

- If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and

- (4) The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>JMAX</sub>, θ<sub>JA</sub>, and the ambient temperature,  $T_A$ . The maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A) / \theta_{JA}$  or the number given in Absolute Maximum Ratings, whichever is lower. For the LM48821, see power derating currents for more information.

- Human body model, 100pF discharged through a  $1.5k\Omega$  resistor.

- Machine Model, 220pF 240pF discharged through all pins.

## **Operating Ratings**

| Temperature Range                     |                                                          |

|---------------------------------------|----------------------------------------------------------|

| $T_{MIN} \le T_A \le T_{MAX}$         | -40°C ≤ T <sub>A</sub> ≤ +85°C                           |

| Supply Voltage                        |                                                          |

| PV <sub>DD</sub> and SV <sub>DD</sub> | $2.0 \text{V} \le \text{V}_{\text{DD}} \le 4.0 \text{V}$ |

| I <sup>2</sup> CV <sub>DD</sub>       | $1.8V \le I^2CV_{DD} \le 4.0V$                           |

# Audio Amplifier Electrical Characteristics $V_{DD} = 3V^{(1)}$

The following specifications apply for  $V_{DD} = 3V$ ,  $R_L = 16\Omega$ ,  $A_V = 0$ dB, unless otherwise specified. Limits apply for  $T_A = 25$ °C.

|                     |                                                |                                                                | L           | Units             |                      |  |

|---------------------|------------------------------------------------|----------------------------------------------------------------|-------------|-------------------|----------------------|--|

| Symbol              | Parameter                                      | Conditions                                                     | Typical (2) | Limits<br>(3) (4) | (Limits)             |  |

|                     |                                                | V <sub>IN</sub> = 0V, inputs terminated, both channels enabled | 3.0         | 4.5               | mA (max)             |  |

| 'DD                 | I <sub>DD</sub> Quiescent Power Supply Current | V <sub>IN</sub> = 0V, inputs terminated, one channel enabled   | 2.0         | 3.0               | mA                   |  |

| I <sub>SD</sub>     | Shutdown Current                               | Right and Left Enable bits set to 0                            | 0.1         | 1.2               | μA (max)             |  |

| Vos                 | Output Offset Voltage                          | $R_L = 32\Omega$                                               | 0.5         | 2.5               | mV (max)             |  |

| ^                   |                                                | [B0:B4] = 00000                                                | -76         |                   | dB                   |  |

| A <sub>V</sub>      | Volume Control Range                           | [B0:B4] = 11111                                                | +18         |                   | dB                   |  |

| $\Delta A_V$        | Channel-to-Channel Gain Match                  |                                                                | ±0.015      |                   | dB                   |  |

| A <sub>V-MUTE</sub> | Mute Gain                                      |                                                                | -76         |                   | dB                   |  |

| R <sub>IN</sub>     | Input Resistance                               | Gain = 18dB                                                    | 9           | 5<br>15           | kΩ (min)<br>kΩ (max) |  |

|                     |                                                | Gain = -76dB                                                   | 81          |                   | kΩ                   |  |

- All voltages are measured with respect to the GND pin unless otherwise specified.

- Typicals are measured at +25°C and represent the parametric norm.

- Limits are specified to AOQL (Average Outgoing Quality Level).

- Data sheet min and /max specification limits are specified by design, test, or statistical analysis. (4)

Submit Documentation Feedback

Copyright © 2007-2013, Texas Instruments Incorporated

# Audio Amplifier Electrical Characteristics $V_{DD} = 3V^{(1)}$ (continued)

The following specifications apply for  $V_{DD} = 3V$ ,  $R_L = 16\Omega$ ,  $A_V = 0$ dB, unless otherwise specified. Limits apply for  $T_A = 25$ °C.

|                                         |                                                                     |                                                                                            | LM             | 48821             | Units                |  |

|-----------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------|-------------------|----------------------|--|

| Symbol                                  | Parameter                                                           | Conditions                                                                                 | Typical (2)    | Limits<br>(3) (4) | (Limits)             |  |

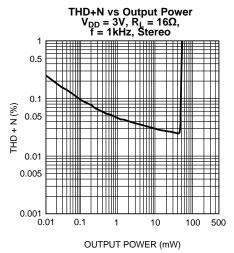

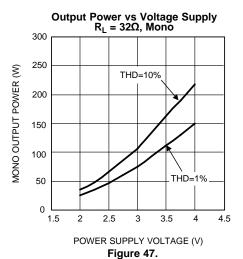

|                                         |                                                                     | THD+N = 1% (max); $f_{IN}$ = 1kHz,<br>R <sub>L</sub> = 16 $\Omega$ , per channel           | 52             | 43                | mW (min)             |  |

| D                                       | Output Pourer                                                       | THD+N = 1% (max); $f_{IN}$ = 1kHz, $R_L$ = 32 $\Omega$ , per channel                       | 53             | 45                | mW (min)             |  |

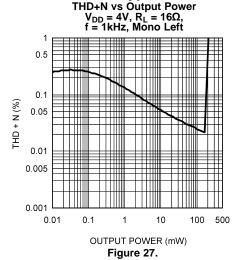

| P <sub>OUT</sub>                        | Output Power                                                        | THD+N = 1% (max); $f_{IN}$ = 1kHz,<br>R <sub>L</sub> = 16 $\Omega$ , single channel driven | 93             | 80                | mW (min)             |  |

|                                         |                                                                     | THD+N = 1% (max); $f_{IN}$ = 1kHz,<br>R <sub>L</sub> = 32 $\Omega$ , single channel driven | 79             |                   | mW                   |  |

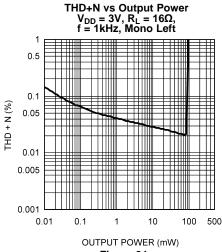

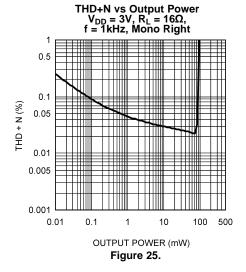

| THD+N Total Harmonic Distortion + Noise | $P_{OUT} = 50$ mW, $f = 1$ kHz<br>$R_L = 16\Omega$ , single channel | 0.022                                                                                      |                | %                 |                      |  |

|                                         | $P_{OUT} = 50$ mW, $f = 1$ kHz<br>$R_L = 32\Omega$ , single channel | 0.011                                                                                      |                | %                 |                      |  |

|                                         |                                                                     | V <sub>RIPPLE</sub> = 200mV <sub>P-P</sub> , input referred                                | ·              |                   |                      |  |

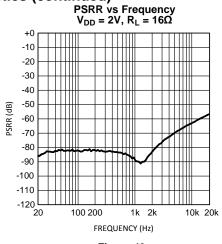

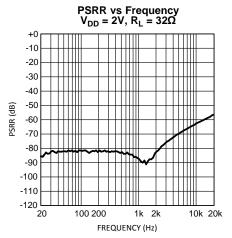

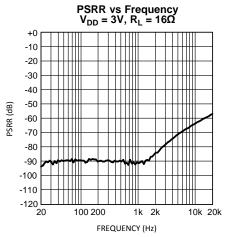

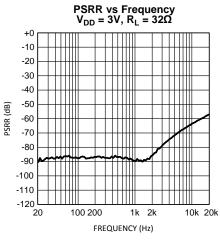

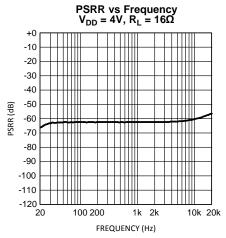

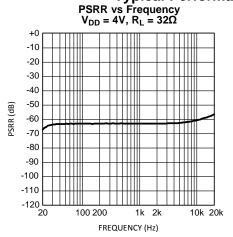

| PSRR                                    | Power Supply Rejection Ratio                                        | f = 217Hz<br>f = 1kHz<br>f = 20kHz                                                         | 82<br>80<br>55 | 65                | dB (min)<br>dB<br>dB |  |

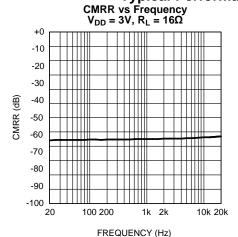

| CMRR                                    | Common Mode Rejection Ratio                                         | $V_{RIPPLE} = 200 \text{mV}_{p-p}$ , Input referred $f = 2 \text{kHz}$                     | 65             |                   | dB                   |  |

| SNR                                     | Signal-to-Noise-Ratio                                               | $R_L = 32\Omega$ , $P_{OUT} = 20$ mW,<br>f = 1kHz, BW = 20Hz to 22kHz                      | 100            |                   | dB                   |  |

| T <sub>WU</sub>                         | Charge Pump Wake-Up Time                                            |                                                                                            | 400            |                   | μs                   |  |

| X <sub>TALK</sub>                       | Crosstalk                                                           | $R_L = 16\Omega$ , $P_{OUT} = 1.6$ mW, $f = 1$ kHz, A-weighted filter                      | 82             |                   | dB                   |  |

| Z <sub>OUT</sub>                        | Output Impedance                                                    | Right and Left Enable bits set to 0                                                        | 41             |                   | kΩ                   |  |

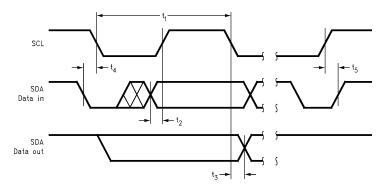

# Control Interface Electrical Characteristics (1)

The following specifications apply for  $1.8V \le l^2CV_{DD} \le 4.0V$ , unless otherwise specified. Limits apply for  $T_A = 25^{\circ}C$ . See Figure 56.

| Cumhal         | Doromotor                  | Conditions | L           | Units                                 |          |

|----------------|----------------------------|------------|-------------|---------------------------------------|----------|

| Symbol         | Parameter                  |            | Typical (2) | Limits (3) (4)                        | (Limits) |

| t <sub>1</sub> | SCL period                 |            |             | 2.5                                   | μs (min) |

| $t_2$          | SDA Setup Time             |            |             | 100                                   | ns (min) |

| $t_3$          | SDA Stable Time            |            |             | 0                                     | ns (min) |

| t <sub>4</sub> | Start Condition Time       |            |             | 100                                   | ns (min) |

| t <sub>5</sub> | Stop Condition Time        |            |             | 100                                   | ns (min) |

| $V_{IH}$       | Logic High Input Threshold |            |             | $0.7 \times I^2CV_{DD}$               | V (min)  |

| $V_{IL}$       | Logic Low Input Threshold  |            |             | 0.3 x I <sup>2</sup> CV <sub>DD</sub> | V (max)  |

- (1) All voltages are measured with respect to the GND pin unless otherwise specified.

(2) Typicals are measured at +25°C and represent the parametric norm.

- Limits are specified to AOQL (Average Outgoing Quality Level).

- Data sheet min and /max specification limits are specified by design, test, or statistical analysis.

Copyright © 2007-2013, Texas Instruments Incorporated

Submit Documentation Feedback

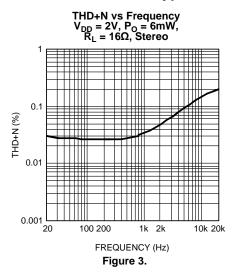

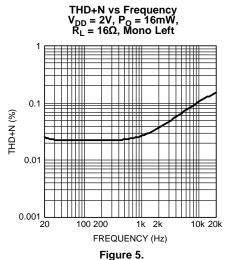

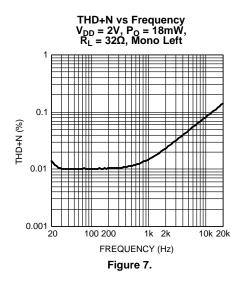

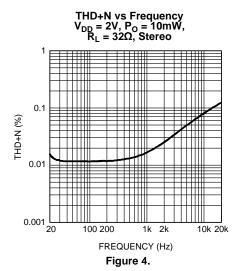

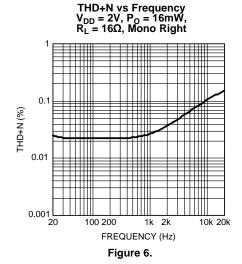

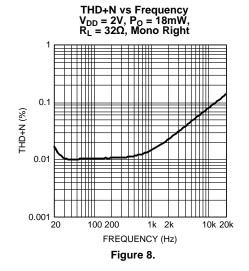

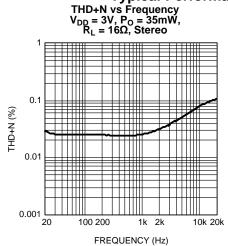

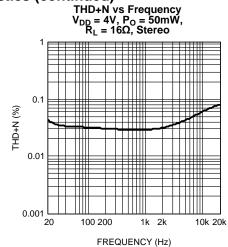

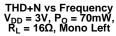

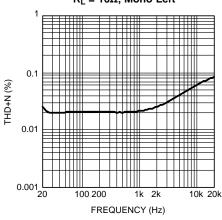

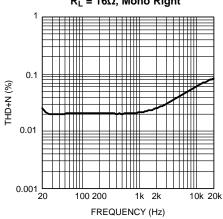

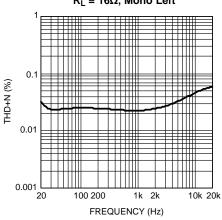

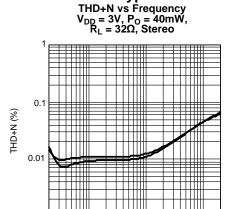

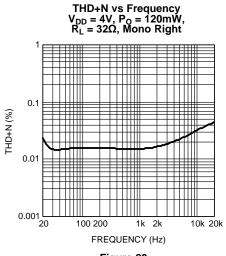

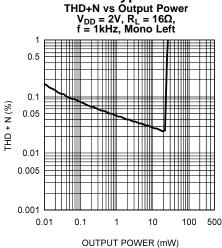

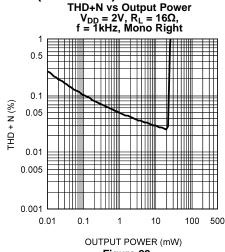

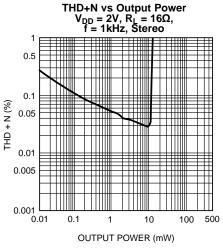

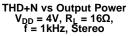

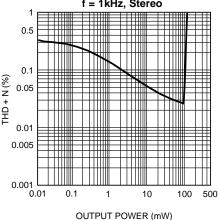

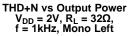

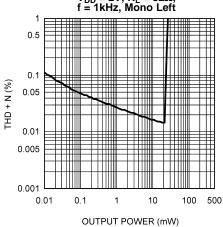

# **Typical Performance Characteristics**

Figure 9.

Figure 10.

Figure 11.

# THD+N vs Frequency $V_{DD}$ = 3V, $P_{O}$ = 70mW, $R_{L}$ = 16 $\Omega$ , Mono Right

Figure 12.

# THD+N vs Frequency $V_{DD}$ = 4V, $P_{O}$ = 160mW, $R_{L}$ = 16 $\Omega$ , Mono Left

Figure 13.

# THD+N vs Frequency $V_{DD}$ = 4V, $P_{O}$ = 160mW, $R_{L}$ = 16 $\Omega$ , Mono Right

Figure 14.

0.001

20

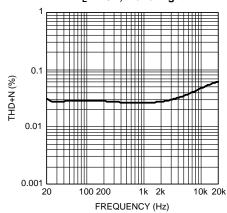

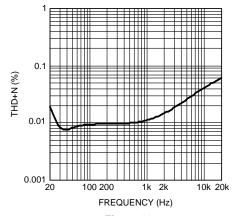

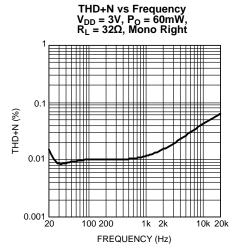

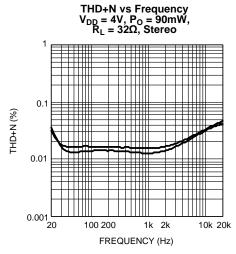

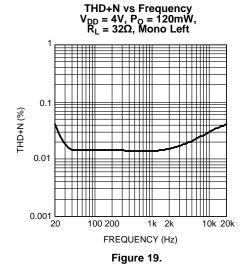

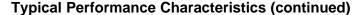

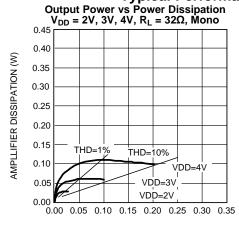

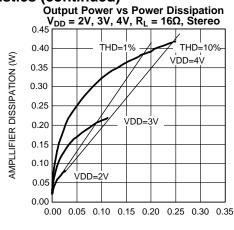

# **Typical Performance Characteristics (continued)**

FREQUENCY (Hz)

Figure 15.

1k 2k

10k 20k

100 200

THD+N vs Frequency  $V_{DD}$  = 3V,  $P_{O}$  = 60mW,  $R_{L}$  = 32 $\Omega$ , Mono Left

Figure 16.

Figure 17.

Figure 18.

Figure 20.

Figure 22.

Figure 23.

Figure 24.

Figure 26.

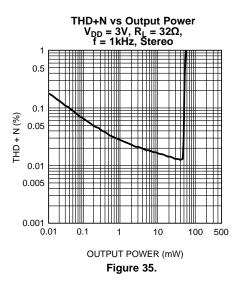

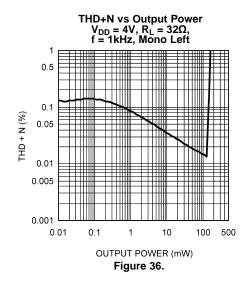

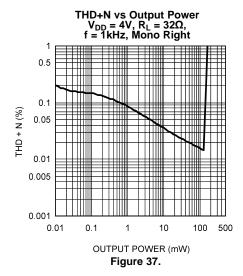

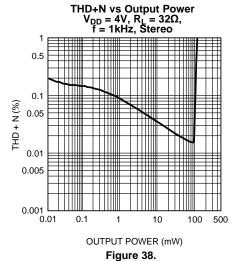

# Typical Performance Characteristics (continued) vs Output Power THD+N vs Output Power

V<sub>DD</sub> = 4V, R<sub>L</sub> = 16Ω, f = 1kHz, Mono Right 0.5 0.1 0.05 0.001 0.005

0.01

0.1

OUTPUT POWER (mW) Figure 28.

10

100 500

# Figure 29.

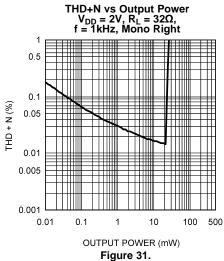

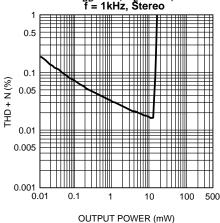

THD+N vs Output Power  $V_{DD}$  = 2V,  $R_L$  = 32 $\Omega$ , f = 1kHz, Stereo

Figure 30.

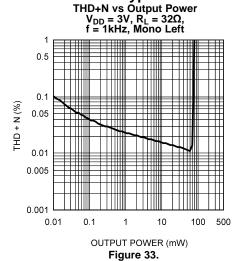

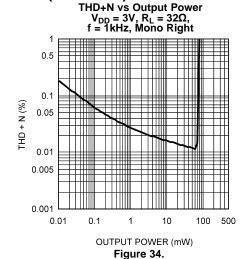

Figure 32.

Figure 39.

Figure 40.

Figure 41.

Figure 42.

Figure 44.

Figure 45.

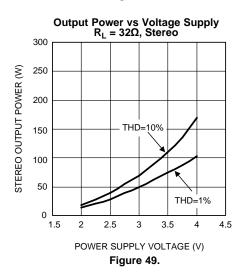

POWER SUPPLY VOLTAGE (V) Figure 46.

Figure 48.

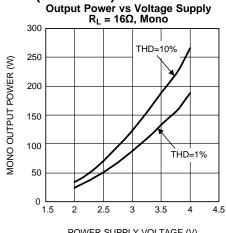

MONOPHONIC OUTPUT POWER (W) Figure 50.

MONOPHONIC OUTPUT POWER (W) Figure 51.

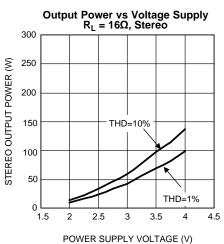

TOTAL STEREO OUTPUT POWER (W)

Figure 52.

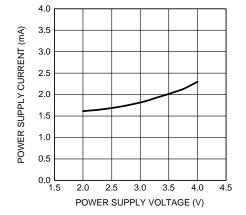

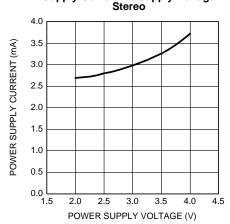

Supply Current vs Supply Voltage Mono

TOTAL STEREO OUTPUT POWER (W) Figure 53.

Figure 54.

# Supply Current vs Supply Voltage

Figure 55.

#### **APPLICATION INFORMATION**

Figure 56. I<sup>2</sup>C Timing Diagram

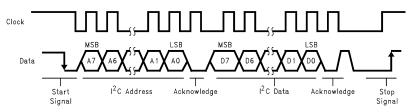

Figure 57. I<sup>2</sup>C Bus Format

## **Table 1. Chip Address**

|              | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|--------------|----|----|----|----|----|----|----|----|

| Chip Address | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 0  |

## **Table 2. Control Registers**

|                | D7  | D6  | D5  | D4  | D3  | D2   | D1           | D0           |

|----------------|-----|-----|-----|-----|-----|------|--------------|--------------|

| Volume Control | VD4 | VD3 | VD2 | VD1 | VD0 | MUTE | LF<br>ENABLE | RT<br>ENABLE |

# I<sup>2</sup>C VOLUME CONTROL

The LM48821 can be configured in 32 different gain steps by forcing I<sup>2</sup>C volume control bits to a desired gain according to Table 3.

Copyright © 2007–2013, Texas Instruments Incorporated

#### **Table 3. Volume Control**

| VD4 | VD3 | VD2 | VD1 | VD0 | Gain (dB)  |

|-----|-----|-----|-----|-----|------------|

| 0   | 0   | 0   | 0   | 0   | -76        |

| 0   | 0   | 0   | 0   | 1   | -62        |

| 0   | 0   | 0   | 1   | 0   | -52        |

| 0   | 0   | 0   | 1   | 1   | -32<br>-44 |

| 0   | 0   | 1   | 0   | 0   | -38        |

| 0   | 0   | 1   | 0   | 1   | -34        |

| 0   | 0   |     |     | 0   |            |

|     |     | 1   | 1   |     | -30        |

| 0   | 0   | 1   | 1   | 1   | -27        |

| 0   | 1   | 0   | 0   | 0   | -24        |

| 0   | 1   | 0   | 0   | 1   | -21        |

| 0   | 1   | 0   | 1   | 0   | -18        |

| 0   | 1   | 0   | 1   | 1   | -16        |

| 0   | 1   | 1   | 0   | 0   | -14        |

| 0   | 1   | 1   | 0   | 1   | -12        |

| 0   | 1   | 1   | 1   | 0   | -10        |

| 0   | 1   | 1   | 1   | 1   | -8         |

| 1   | 0   | 0   | 0   | 0   | -6         |

| 1   | 0   | 0   | 0   | 1   | -4         |

| 1   | 0   | 0   | 1   | 0   | -2         |

| 1   | 0   | 0   | 1   | 1   | 0          |

| 1   | 0   | 1   | 0   | 0   | 2          |

| 1   | 0   | 1   | 0   | 1   | 4          |

| 1   | 0   | 1   | 1   | 0   | 6          |

| 1   | 0   | 1   | 1   | 1   | 8          |

| 1   | 1   | 0   | 0   | 0   | 10         |

| 1   | 1   | 0   | 0   | 1   | 12         |

| 1   | 1   | 0   | 1   | 0   | 13         |

| 1   | 1   | 0   | 1   | 1   | 14         |

| 1   | 1   | 1   | 0   | 0   | 15         |

| 1   | 1   | 1   | 0   | 1   | 16         |

| 1   | 1   | 1   | 1   | 0   | 17         |

| 1   | 1   | 1   | 1   | 1   | 18         |

#### I<sup>2</sup>C COMPATIBLE INTERFACE

The LM48821 uses a serial data bus that conforms to the I<sup>2</sup>C protocol. Controlling the chip's functions is accomplished with two wires: serial clock (SCL) and serial data (SDA). The clock line is uni-directional. The data line is bi-directional (open-collector). The maximum clock frequency specified by the I<sup>2</sup>C standard is 400kHz. In this discussion, the master is the controlling microcontroller and the slave is the LM48821.

The bus format for the I<sup>2</sup>C interface is shown in Figure 57. The bus format diagram is broken up into six major sections: The Start Signal, the I<sup>2</sup>C Address, an Acknowledge bit, the I<sup>2</sup>C data, second Acknowledge bit, and the Stop Signal.

The start signal is generated by lowering the data signal while the clock signal is high. The start signal will alert all devices attached to the I<sup>2</sup>C bus to check the incoming address against their own address.

The 8-bit chip address is sent next, most significant bit first. The data is latched in on the rising edge of the clock. Each address bit must be stable while the clock level is high.

After the last bit of the address bit is sent, the master releases the data line high (through a pull-up resistor). Then the master sends an acknowledge clock pulse. If the LM48821 has received the address correctly, then it holds the data line low during the clock pulse. If the data line is not held low during the acknowledge clock pulse, then the master should abort the rest of the data transfer to the LM48821. The 8 bits of data are sent next, most significant bit first. Each data bit should be valid while the clock level is stable high.

After the data byte is sent, the master must check for another acknowledge to see if the LM48821 received the data.

If the master has more data bytes to send to the LM48821, then the master can repeat the previous two steps until all data bytes have been sent.

The stop signal ends the transfer. To signal stop, the data signal goes high while the clock signal is high. The data line should be held high when not in use.

The LM48821's I<sup>2</sup>C address is shown in Table 1. The I<sup>2</sup>C data register and its control bit names are shown in Table 2. The data values for the volume control are shown in Table 3.

# I<sup>2</sup>C INTERFACE POWER SUPPLY PIN (I<sup>2</sup>CV<sub>DD</sub>)

The LM48821's I<sup>2</sup>C interface is powered up through the I<sup>2</sup>CV<sub>DD</sub> pin. The LM48821's I<sup>2</sup>C interface operates at a voltage level set by the I<sup>2</sup>CV<sub>DD</sub> pin. This voltage can be independent from the main power supply pin (V<sub>DD</sub>). This is ideal whenever logic levels for the I<sup>2</sup>C interface are dictated by a microcontroller or microprocessor that is operating at a lower supply voltage than the main battery of a portable system.

#### **POWER SUPPLY BYPASSING**

As with any power amplifier, proper supply bypassing is critical for low noise performance and high power supply rejection. Applications that employ a 3.3V voltage regulator typically use a 10µF in parallel with a 0.1µF filter capacitors to stabilize the regulator's output, reduce noise on the regulated supply lines, and improve the regulator's transient response. However, their presence does not eliminate the need for a local 1.0µF tantalum bypass capacitance connected between the LM48821's supply pins and ground. Keep the length of leads and traces that connect capacitors between the LM48821's power supply pins and ground as short as possible.

#### **ELIMINATING THE OUTPUT COUPLING CAPACITOR**

The LM48821 features a low noise inverting charge pump that generates an internal negative supply voltage. This allows the LM48821 to reference its amplifier outputs to ground instead of a half-supply voltage, like traditional capacitivel-coupled headphone amplifiers. Because there is no DC bias voltage associated with either stereo output, the large DC blocking capacitors (typically 220µF) are not necessary. The coupling capacitors are replaced by two, small ceramic charge pump capacitors, saving board space and cost.

Eliminating the output coupling capacitors also improves low frequency response. In traditional headphone amplifiers, the headphone impedance and the output capacitor form a high pass filter that not only blocks the DC component of the output, but also attenuates low frequencies, impacting the bass response. Because the LM48821 does not require the output coupling capacitors, the low frequency response of the device is not degraded.

In addition to eliminating the output coupling capacitors, the ground referenced output nearly doubles the output voltage swing and available dynamic range of the LM48821 when compared to a traditional capacitively-coupled output headphone amplifier operating from the same supply voltage.

#### **OUTPUT TRANSIENT ELIMINATED**

The LM48821 contains advanced circuitry that virtually eliminates output transients ('clicks' and 'pops'). This circuitry attenuates output transients when the supply voltage is first applied or when the part resumes operation after using the shutdown mode.

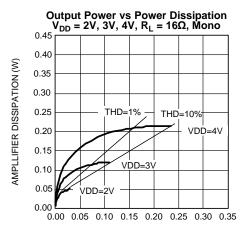

#### **POWER DISSIPATION**

Power dissipation is a major concern when using any power amplifier and must be thoroughly understood to ensure a successful design. Equation 1 states the maximum power dissipation point for a single-ended amplifier operating at a given supply voltage and driving a specified output load.

$$P_{DMAX} = (2V_{DD})^2 / (2\pi^2 R_L)$$

(1)

Since the LM48821 has two power amplifiers in one package, the maximum internal power dissipation point is twice that of the number which results from Equation 1. Even with large internal power dissipation, the LM48821 does not require heat sinking over a large range of ambient temperatures. The maximum power dissipation point obtained must not be greater than the power dissipation that results from Equation 2:

$$P_{DMAX} = (T_{JMAX} - T_A) / (\theta_{JA})$$

(2)

For the DSBGA package,  $\theta_{JA} = 105^{\circ}\text{C/W}$ .  $T_{JMAX} = 150^{\circ}\text{C}$  for the LM48821. Depending on the ambient temperature,  $T_A$ , of the system surroundings, Equation 2 can be used to find the maximum internal power dissipation supported by the IC packaging. If the result of Equation 1 is greater than that of Equation 2, then either the supply voltage must be decreased, the load impedance increased or  $T_A$  reduced. Power dissipation is a function of output power and thus, if typical operation is not around the maximum power dissipation point, the ambient temperature may be increased accordingly.

#### **SELECTING EXTERNAL COMPONENTS**

Optimizing the LM48821's performance requires properly selecting external components. Though the LM48821 operates well when using external components with wide tolerances, best performance is achieved by optimizing component values.

#### **Charge Pump Capacitor Selection**

Use low ESR (equivalent series resistance) ( $<100m\Omega$ ) ceramic capacitors with an X7R dielectric for best performance. Low ESR capacitors keep the charge pump output impedance to a minimum, extending the headroom on the negative supply. Higher ESR capacitors result in reduced output power from the audio amplifiers.

Charge pump load regulation and output impedance are affected by the value of the flying capacitor (connected between the  $C_{CP-}$  and  $C_{CP+}$  pins). A larger valued  $C_1$  (up to  $4.7\mu F$ ) improves load regulation and minimizes charge pump output resistance. Beyond  $4.7\mu F$ , the switchon-resistance dominates the output impedance.

The output ripple is affected by the value and ESR of the output capacitor (connected between the V<sub>SS</sub> and PGND pins). Larger capacitors reduce output ripple on the negative power supply. Lower ESR capacitors minimize the output ripple and reduce the output impedance of the charge pump.

The LM48821 charge pump design is optimized for 4.7µF, low ESR, ceramic, flying, and output capacitors.

#### **Power Supply Bypass Capacitor**

For good THD+N and low noise performance and to ensure correct power-on behavior at the maximum allowed power supply voltage, a local 4.7µF power supply bypass capacitor should be connected as physically closed as possible to the PV<sub>DD</sub> pin.

#### Input Capacitor Value Selection

Amplifying the lowest audio frequencies requires high value input coupling capacitors (the 0.47µF capacitors in Figure 1). A high value capacitor can be expensive and may compromise space efficiency in portable designs. In many cases, however, the speakers used in portable systems, whether internal or external, have little ability to reproduce signals below 150Hz. Applications using speakers with this limited frequency response reap little improvement by using high value input and output capacitors.

Besides affecting system cost and size, the input coupling capacitor value has an effect on the LM48821's click and pop performance. The magnitude of the pop is directly proportional to the input capacitor's size. Thus, pops can be minimized by selecting an input capacitor value that is no higher than necessary to meet the desired -3dB frequency.

The LM48821's nominal input resistance at full volume is  $10k\Omega$  and a minimum of  $5k\Omega$ . This input resistance and the input coupling capacitor value produce a -3dB high pass filter cutoff frequency that is found using Equation 3.

$$f_{-3dB} = 1/2\pi R_i C_i \tag{3}$$

#### **REVISION HISTORY**

| Rev | Date       | Description                                         |  |  |

|-----|------------|-----------------------------------------------------|--|--|

| 1.0 | 06/06/07   | Initial release.                                    |  |  |

| А   | 05/02/2013 | Changed layout of National Data Sheet to TI format. |  |  |

Submit Documentation Feedback

www.ti.com 11-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins   | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|------------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| LM48821TL/NOPB        | Active | Production    | DSBGA (YZR)   16 | 250   SMALL T&R       | Yes             | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 85    | G16              |

| LM48821TL/NOPB.A      | Active | Production    | DSBGA (YZR)   16 | 250   SMALL T&R       | Yes             | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 85    | G16              |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 26-Oct-2024

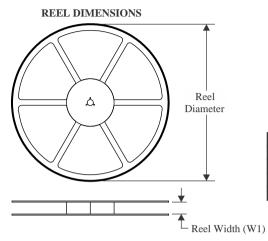

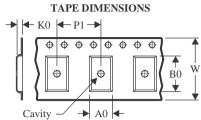

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

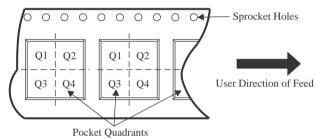

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing |    | SPQ | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|----|-----|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM48821TL/NOPB | DSBGA           | YZR                | 16 | 250 | 178.0                    | 8.4                      | 2.08       | 2.08       | 0.76       | 4.0        | 8.0       | Q1               |

# PACKAGE MATERIALS INFORMATION

www.ti.com 26-Oct-2024

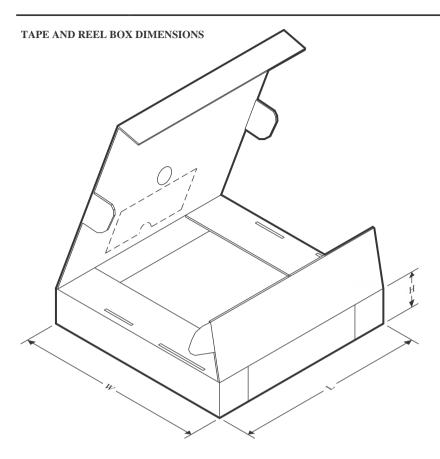

#### \*All dimensions are nominal

| Ì | Device         | Package Type | Package Drawing | Pins | SPQ | Length (mm) | Width (mm) | Height (mm) |  |

|---|----------------|--------------|-----------------|------|-----|-------------|------------|-------------|--|

| ı | LM48821TL/NOPB | DSBGA        | YZR             | 16   | 250 | 208.0       | 191.0      | 35.0        |  |

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

B. This drawing is subject to change without notice.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025