# LM49100 Boomer® Audio Power Amplifier Series Mono Class AB Audio Sub-System with a True-**Ground Headphone Amplifier**

Check for Samples: LM49100

#### **FEATURES**

- Mono and Stereo Inputs

- **Thermal Overload Protection**

- **True-Ground Headphone Drivers**

- I<sup>2</sup>C Control Interface

- **Input Mute Attenuation**

- 2nd Stage Headphone Attenuator

- 32-Step Digital Volume Control

- 10 Operating Modes

- **Minimum External Components**

- Click and Pop Suppression

- Micro-Power Shutdown

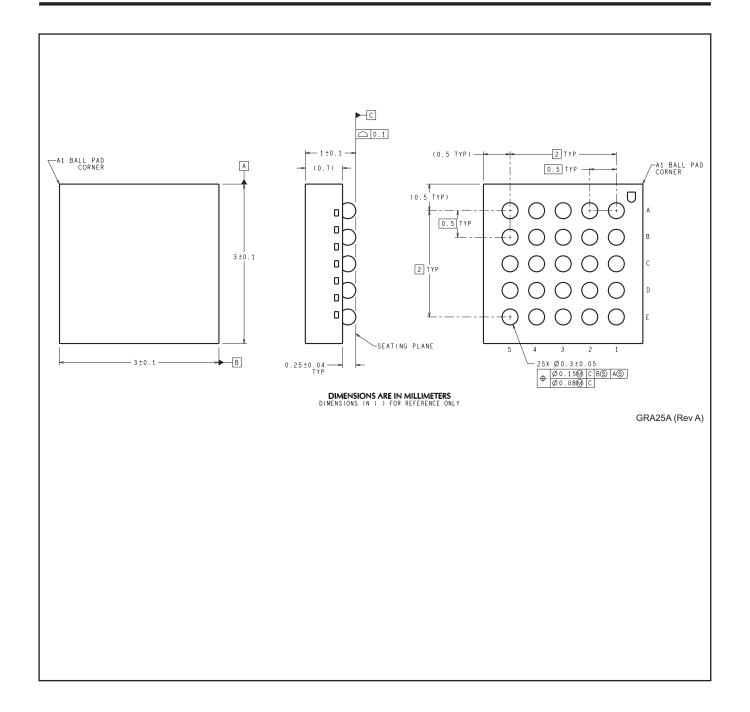

- Available in Space-Saving 3mm x 3mm 25-Bump csBGA Package

- **RF Suppression**

#### **KEY SPECIFICATIONS**

- Power Output at VDD = 5V:

- Loudspeaker (LS):

- RL = 8Ω, THD+N ≤: 1% 1.275W

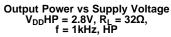

- Headphone (VDDHP = 2.8V):

- RL = 32Ω, THD+N ≤ 1%: 50mW

- Shutdown current 0.01µA

#### APPLICATIONS

- **Mobile Phones**

- **PDAs**

- **Laptops**

- Portable Electronics

#### DESCRIPTION

The LM49100 is a fully integrated audio subsystem capable of delivering 1.275W of continuous average power into a mono 8Ω bridged-tied load (BTL) with 1% THD+N and with a 5V power supply. The LM49100 also has a stereo true-ground headphone amplifier capable of 50mW per channel of continuous average power into a 32Ω single-ended (SE) loads with 1% THD+N.

The LM49100 has three input channels. One pair of SE inputs can be used with a stereo signal. The other input channel is fully differential and may be used with a mono input signal. The LM49100 features a 32-step digital volume control and ten distinct output modes. The mixer, volume control, and device mode select are controlled through an I<sup>2</sup>C compatible interface.

Thermal overload protection prevent the device from being damaged during fault conditions. Superior click and pop suppression eliminates audible transients on power-up/down and during shutdown.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

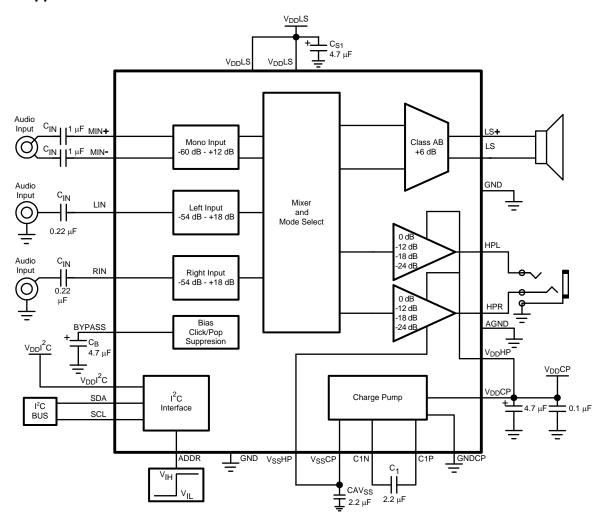

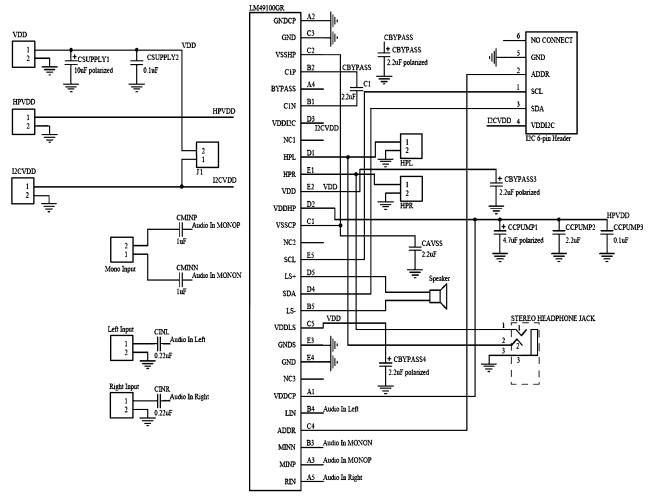

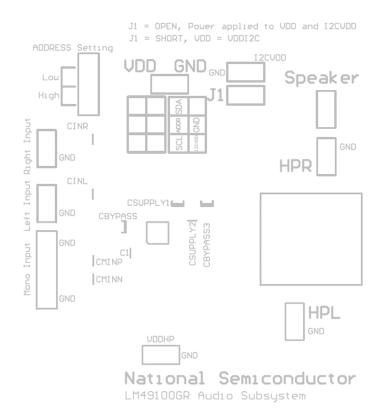

## **Typical Application**

Figure 1. Typical Audio Amplifier Application Circuit

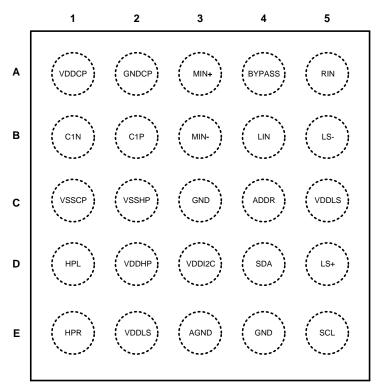

## **Connection Diagrams**

Figure 2. Top View 25-Bump csBGA 3mm × 3mm × 1mm See NYA0025A Package

#### **BUMP DESCRIPTIONS**

| Bump | Name                             | Description                                      |

|------|----------------------------------|--------------------------------------------------|

| A1   | V <sub>DD</sub> CP               | Positive Charge Pump Power Supply                |

| A2   | GNDCP                            | Charge Pump Ground                               |

| A3   | MIN+                             | Positive Mono Input                              |

| A4   | BYPASS                           | Half-Supply Bypass                               |

| A5   | RIN                              | Right Input                                      |

| B1   | C1N                              | Negative Terminal – Charge Pump Flying Capacitor |

| B2   | C1P                              | Positive Terminal – Charge Pump Flying Capacitor |

| B3   | MIN-                             | Negative Mono Input                              |

| B4   | LIN                              | Left Input                                       |

| B5   | LS-                              | Negative Loudspeaker Output                      |

| C1   | V <sub>SS</sub> CP               | Negative Charge Pump Power Supply                |

| C2   | V <sub>SS</sub> HP               | Negative Headphone Power Supply                  |

| C3   | GND                              | Ground                                           |

| C4   | ADDR                             | I <sup>2</sup> C Address Identification          |

| C5   | V <sub>DD</sub> LS               | Loudspeaker Power Supply                         |

| D1   | HPL                              | Left Headphone Output                            |

| D2   | V <sub>DD</sub> HP               | Positive Headphone Power Supply                  |

| D3   | V <sub>DD</sub> I <sup>2</sup> C | I <sup>2</sup> C Power Supply                    |

# **BUMP DESCRIPTIONS (continued)**

| Bump | Name               | Description                                                    |  |  |

|------|--------------------|----------------------------------------------------------------|--|--|

| D4   | SDA                | I <sup>2</sup> C Data                                          |  |  |

| D5   | LS+                | Loudspeaker Output Positive                                    |  |  |

| E1   | HPR                | Right Headphone Output                                         |  |  |

| E2   | V <sub>DD</sub> LS | Loudspeaker Power Supply                                       |  |  |

| E3   | AGND               | Headphone Signal Ground (See Application Information section). |  |  |

| E4   | GND                | Ground                                                         |  |  |

| E5   | SCL                | I <sup>2</sup> C Clock                                         |  |  |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings (1)(2)(3)

| 6V                              |

|---------------------------------|

| 3V                              |

| −65°C to +150°C                 |

| -0.3V to V <sub>DD</sub> + 0.3V |

| Internally Limited              |

| 2000V                           |

| 200V                            |

| 150°C                           |

|                                 |

| 50.2°C/W                        |

|                                 |

- (1) All voltages are measured with respect to the GND pin unless other wise specified.

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional but do not ensure specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which specify performance limits. This assumes that the device is within the Operating Ratings. Specifications are not for parameters where no limit is given, however, the typical value is a good indication of device performance.

- (3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (4) The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>JMAX</sub>, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation is P<sub>DMAX</sub> = (T<sub>JMAX</sub> T<sub>A</sub>)/ θ<sub>JA</sub> or the number given in Absolute Maximum Ratings, whichever is lower. For the LM49100, see power derating currents for more information.

- (5) Human body model, 100 pF discharged through a  $1.5k\Omega$  resistor.

- (6) Machine Model, 220pF 240pF discharged through all pins.

#### **Operating Ratings**

| Temperature Range                                            |                                                                                      |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------|

| $T_{MIN} \le T_A \le T_{MAX}$                                | -40°C ≤ T <sub>A</sub> ≤ +85°C                                                       |

| Supply Voltage V <sub>DD</sub> LS                            | $2.7V \le V_{DD}LS \le 5.5V$                                                         |

| Supply Voltage V <sub>DD</sub> HP                            | $2.4 \text{ V} \le \text{V}_{DD}\text{HP} \le 2.9 \text{V}$                          |

| I <sup>2</sup> C Voltage (V <sub>DD</sub> I <sup>2</sup> C ) | $1.7V \le V_{DD}I^{2}C \le 5.5V$ $V_{DD}HP \le V_{DD}LS$ $V_{DD}I^{2}C \le V_{DD}LS$ |

# Electrical Characteristics $V_{DD}LS = 3.6V$ , $V_{DD}HP = 2.8V$ <sup>(1)(2)</sup>

The following specifications apply for all programmable gain set to 0 dB,  $C_B = 4.7 \mu F$ ,  $R_{L~(SP)} = 8 \Omega$ ,  $R_{L(HP)} = 32 \Omega$ , f = 1~kHz unless otherwise specified. Limits apply for  $T_A = 25 ^{\circ}C$ .

|                  |                         |                                        | Conditions                                           |                                   |            | LM49100      |                   |  |

|------------------|-------------------------|----------------------------------------|------------------------------------------------------|-----------------------------------|------------|--------------|-------------------|--|

| Symbol           | Parameter               |                                        |                                                      |                                   |            | Limit<br>(4) | Units<br>(Limits) |  |

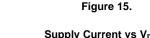

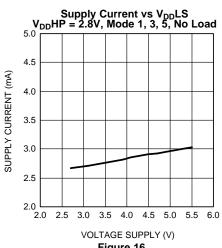

|                  |                         |                                        | Modes 1, 3, 5<br>V <sub>IN</sub> = 0V, No Lo         | ad                                | 2.9        |              | mA                |  |

|                  |                         | $V_{DD}LS = 3.0V$<br>$V_{DD}HP = 2.8V$ | Modes 2, 4, 6<br>V <sub>IN</sub> = 0V, No Lo         | ad                                | 3.4        |              | mA                |  |

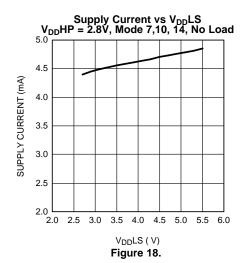

|                  |                         |                                        | Modes 7, 10, 14<br>V <sub>IN</sub> = 0V, No Lo       |                                   | 4.8        |              | mA                |  |

|                  |                         |                                        | Modes 1, 3, 5<br>V <sub>IN</sub> = 0V, No Lo         | ad                                | 2.9        | 4.3          | mA (max)          |  |

| I <sub>DD</sub>  | Supply Current          | $V_{DD}LS = 3.6V$<br>$V_{DD}HP = 2.8V$ | Modes 2, 4, 6<br>V <sub>IN</sub> = 0V, No Lo         | ad                                | 3.5        | 5.4          | mA (max)          |  |

|                  |                         |                                        | Modes 7, 10, 14<br>V <sub>IN</sub> = 0V, No Lo       |                                   | 4.8        | 7.4          | mA (max)          |  |

|                  |                         |                                        | Modes 1, 3, 5<br>V <sub>IN</sub> = 0V, No Lo         | ad                                | 3.1        |              | mA                |  |

|                  |                         | $V_{DD}LS = 5.0V$<br>$V_{DD}HP = 2.8V$ | Modes 2, 4, 6<br>V <sub>IN</sub> = 0V, No Load       |                                   | 3.6        |              | mA                |  |

|                  |                         |                                        | Modes 7, 10, 14<br>V <sub>IN</sub> = 0V, No Lo       |                                   | 5.0        |              | mA                |  |

| I <sub>SD</sub>  | Shutdown Supply Current | Mode 0                                 | Mode 0                                               |                                   |            |              | μA (max)          |  |

|                  |                         | V <sub>IN</sub> = 0V, Mode             | V <sub>IN</sub> = 0V, Mode 7, Mono                   |                                   |            | 25           | mV (max)          |  |

|                  |                         | V <sub>IN</sub> = 0V, Mode             | V <sub>IN</sub> = 0V, Mode 7, Headphone Gain = -24dB |                                   |            | 5.5          | mV                |  |

| Vos              | Output Offset Voltage   | V <sub>IN</sub> = 0V, Mode             | V <sub>IN</sub> = 0V, Mode 7, Headphone Gain = -18dB |                                   |            |              | mV (max)          |  |

|                  |                         | V <sub>IN</sub> = 0V, Mode             | V <sub>IN</sub> = 0V, Mode 7, Headphone Gain = -12dB |                                   |            |              | mV                |  |

|                  |                         | V <sub>IN</sub> = 0V, Mode             | V <sub>IN</sub> = 0V, Mode 7, Headphone Gain = 0dB   |                                   |            | 15           | mV (max)          |  |

|                  |                         |                                        | LS<br>f = 1kHz                                       | R <sub>L</sub> = 8Ω<br>1%<br>10%  | 425<br>525 |              | mW<br>mW          |  |

| P <sub>OUT</sub> | Output Power            | $V_{DD}LS = 3.0V$                      | HP<br>f = 1kHz                                       | R <sub>L</sub> = 16Ω<br>1%<br>10% | 49<br>69   |              | mW<br>mW          |  |

|                  |                         |                                        |                                                      | R <sub>L</sub> = 32Ω<br>1%<br>10% | 35<br>44   |              | mW<br>mW          |  |

| P <sub>OUT</sub> |                         |                                        | LS<br>f = 1kHz                                       | R <sub>L</sub> = 8Ω<br>1%<br>10%  | 640<br>790 | 600          | mW (min)<br>mW    |  |

|                  | Output Power            | $V_{DD}LS = 3.6V$                      | НР                                                   | R <sub>L</sub> = 16Ω<br>1%<br>10% | 49<br>72   |              | mW<br>mW          |  |

|                  |                         |                                        | f = 1kHz                                             | R <sub>L</sub> = 32Ω<br>1%<br>10% | 50<br>62   | 46           | mW (min)<br>mW    |  |

Product Folder Links: LM49100

<sup>(1)</sup> All voltages are measured with respect to the GND pin unless other wise specified.

<sup>(2)</sup> Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional but do not ensure specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which specify performance limits. This assumes that the device is within the Operating Ratings. Specifications are not for parameters where no limit is given, however, the typical value is a good indication of device performance.

<sup>(3)</sup> Typicals are measured at 25°C and represent the parametric norm.

<sup>(4)</sup> Limits are specified to AOQL (Average Outgoing Quality Level).

# Electrical Characteristics $V_{DD}LS = 3.6V$ , $V_{DD}HP = 2.8V$ (1)(2) (continued)

The following specifications apply for all programmable gain set to 0 dB,  $C_B = 4.7 \mu F$ ,  $R_{L~(SP)} = 8 \Omega$ ,  $R_{L(HP)} = 32 \Omega$ , f = 1~kHz unless otherwise specified. Limits apply for  $T_A = 25 ^{\circ}C$ .

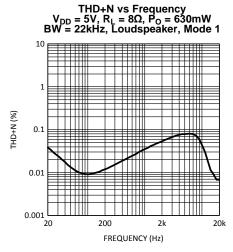

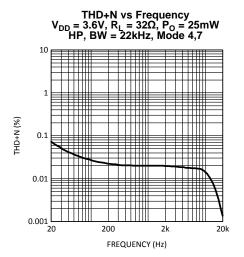

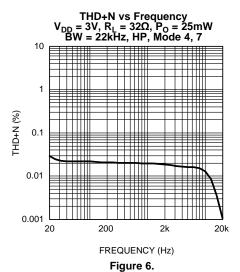

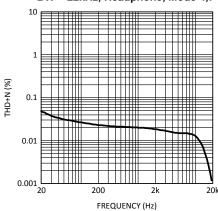

LM49100 Units **Parameter** Conditions **Symbol** Limit Typical (3) (Limits)  $R_L = 8\Omega$ LS 1275 mW f = 1kHz10% 1575 mW  $R_L = 16\Omega$ Pout **Output Power**  $V_{DD}LS = 5.0V$ 49 mW1% 10% 72 mWHP f = 1kHz $R_L = 32\Omega$ 53 mW1% 10% 62 mWLoudspeaker; Mode 1. 0.05 %  $R_L = 8\Omega$ ,  $P_{OUT} = 215$ mW Total Harmonic Distortion + THD+N  $V_{DD}LS = 3.0V$ f = 1kHzNoise Headphone: Mode 4, 0.02 %  $R_1 = 32\Omega$ ,  $P_{OUT} = 25 \text{mW}$ Loudspeaker; Mode 1, 0.05 %  $R_L = 8\Omega$ ,  $P_{OUT} = 320 \text{mW}$ Total Harmonic Distortion + THD+N  $V_{DD}LS = 3.6V$ f = 1kHzNoise Headphone; Mode 4, 0.02 %  $R_L = 32\Omega$ ,  $P_{OUT} = 25$ mW Loudspeaker; Mode 1, 0.035 %  $R_L = 8\Omega$ ,  $P_{OUT} = 630 \text{mW}$ Total Harmonic Distortion + THD+N  $V_{DD}LS = 5.0V$ f = 1kHzNoise Headphone: Mode 4, 0.02 %  $R_L = 32\Omega$ ,  $P_{OUT} = 25 \text{mW}$ Headphone Mode 2, 10 12 μV Mode 4, 7 13 μ۷ Mode 6, 14 μ۷ 16 A-weighted, 0 dB, inputs terminated to GND, output Noise  $e_N$ Loudspeaker referred Mode 1 14 μ۷ Mode 3, 7, 10, 23 μ۷ 14 Mode 5 27 μV

Product Folder Links: LM49100

Maximum gain setting

Maximum attenuation setting

10

15

130

26

12.5

110

ms

ms kΩ (min)

kΩ (max)

$k\Omega$  (min)

kΩ (max)

Turn-on Time

Turn-off Time

Input Impedance

$T_{ON}$

TOFF

$Z_{IN}$

# Electrical Characteristics $V_{DD}LS = 3.6V$ , $V_{DD}HP = 2.8V$ (1)(2) (continued)

The following specifications apply for all programmable gain set to 0 dB,  $C_B = 4.7 \mu F$ ,  $R_{L~(SP)} = 8 \Omega$ ,  $R_{L(HP)} = 32 \Omega$ , f = 1~kHz unless otherwise specified. Limits apply for  $T_A = 25 \,^{\circ}C$ .

|                         |                                |                                                                                                           |                                                 | LM49                   | Units        |                      |  |

|-------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------|--------------|----------------------|--|

| Symbol                  | Parameter                      |                                                                                                           | Conditions                                      | Typical <sup>(3)</sup> | Limit<br>(4) | (Limits)             |  |

|                         |                                | Stereo (Left                                                                                              | Input referred maximum attenuation              | -54                    | -52<br>-56   | dB (min)<br>dB (max) |  |

|                         | Valura Cantral                 | and Right<br>Channels)                                                                                    | Input referred maximum gain                     | 18                     | 17.5<br>18.5 | dB (min)<br>dB (max) |  |

| $A_V$                   | Volume Control                 | Mana                                                                                                      | Input referred maximum attenuation              | -60                    | -58<br>-62   | dB (min)<br>dB (max) |  |

|                         |                                | Mono                                                                                                      | Input referred maximum gain                     | 12                     | 11.5<br>12.5 | dB (min)<br>dB (max) |  |

| CMDD                    | Common Made Rejection Retio    | Headphone M $R_L = 32\Omega$                                                                              | ode 2, f = 217 Hz, $V_{CM} = 1 V_{PP}$ ,        | 64                     |              | dB                   |  |

| CMRR Common Mode Reject | Common Mode Rejection Ratio    | Loudspeaker Mode 1, f = 217 Hz, $V_{CM}$ = 1 $V_{PP}$ , $R_L$ = 8 $\Omega$                                |                                                 | 58                     |              | dB                   |  |

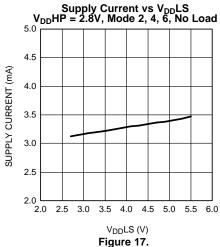

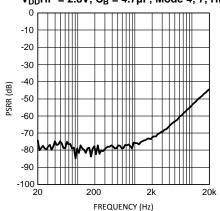

|                         |                                | V <sub>RIPPLE</sub> = 200mVpp on V <sub>DD</sub> LS, output referred, inputs terminated to GND, f = 217Hz |                                                 |                        |              |                      |  |

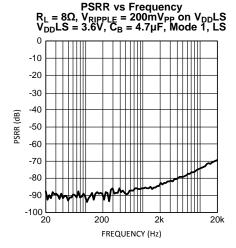

| PSRR                    | Davier Comply Delegation Datio | LS, Mode 1                                                                                                |                                                 | 90                     |              | dB                   |  |

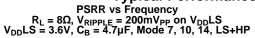

| PORK                    | Power Supply Rejection Ratio   | LS, Mode 3, 7                                                                                             | , 10, 14                                        | 78                     |              | dB                   |  |

|                         |                                | LS, Mode 5                                                                                                |                                                 | 77                     |              | dB                   |  |

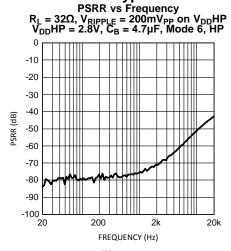

| DODD                    | Developed Defection Detic      | V <sub>RIPPLE</sub> = 200                                                                                 | mVpp on V <sub>DD</sub> HP, output referred, ir | puts terminate         | ed to GND, f | = 217Hz              |  |

| PSRR                    | Power Supply Rejection Ratio   | LS, Mode 7, 1                                                                                             | LS, Mode 7, 10, 14                              |                        |              | dB                   |  |

|                         |                                | V <sub>RIPPLE</sub> = 200                                                                                 | mVpp on V <sub>DD</sub> LS, output referred, in | puts terminate         | d to GND, f  | = 217Hz              |  |

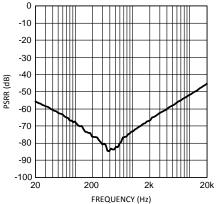

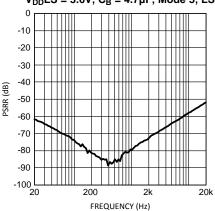

| DCDD                    | Davier Comply Delegation Datio | HP, Mode 2, 10                                                                                            |                                                 | 90                     |              | dB                   |  |

| PSRR                    | Power Supply Rejection Ratio   | HP, Mode 4, 7                                                                                             |                                                 | 88                     |              | dB                   |  |

|                         |                                | HP, Mode 6, 14                                                                                            |                                                 | 87                     |              | dB                   |  |

|                         |                                | V <sub>RIPPLE</sub> = 200mVpp on V <sub>DD</sub> HP, output referred, inputs terminated to GND, f = 217Hz |                                                 |                        |              |                      |  |

| DCDD                    | Dower Cumply Dejection Detic   | HP, Mode 2, 1                                                                                             | 0                                               | 83                     |              | dB                   |  |

| PSRR                    | Power Supply Rejection Ratio   | HP, Mode 4, 7                                                                                             |                                                 | 83                     |              | dB                   |  |

|                         |                                | HP, Mode 6, 1                                                                                             | 4                                               | 80                     |              | dB                   |  |

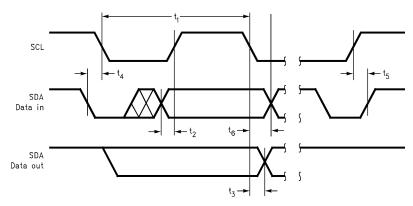

#### I<sup>2</sup>C (1)(2)

The following specifications apply for  $V_{DD} = 5.0V$  and 3.3V,  $T_A = 25^{\circ}C$ ,  $2.2V \le V_{DD}I^2C \le 5.5V$ , unless otherwise specified.

| Symbol          | Parameter                           | Conditions (3) | LN      | LM49100                              |          |  |

|-----------------|-------------------------------------|----------------|---------|--------------------------------------|----------|--|

|                 |                                     |                | Typical | Limits                               | (Limits) |  |

| t <sub>1</sub>  | I <sup>2</sup> C Clock Period       |                |         | 2.5                                  | μs (min) |  |

| t <sub>2</sub>  | I <sup>2</sup> C Data Setup Time    |                |         | 100                                  | ns (min) |  |

| t <sub>3</sub>  | I <sup>2</sup> C Data Stable Time   |                |         | 0                                    | ns (min) |  |

| t <sub>4</sub>  | Start Condition Time                |                |         | 100                                  | ns (min) |  |

| t <sub>5</sub>  | Stop Condition Time                 |                |         | 100                                  | ns (min) |  |

| <sup>1</sup> 6  | I <sup>2</sup> C Data Hold Time     |                |         | 100                                  | ns (min) |  |

| V <sub>IH</sub> | I <sup>2</sup> C Input Voltage High |                |         | 0.7xV <sub>DD</sub> I <sup>2</sup> C | V (min)  |  |

| V <sub>IL</sub> | I <sup>2</sup> C Input Voltage Low  |                |         | 0.3xV <sub>DD</sub> I <sup>2</sup> C | V (max)  |  |

<sup>(1)</sup> Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional but do not ensure specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which specify performance limits. This assumes that the device is within the Operating Ratings. Specifications are not for parameters where no limit is given, however, the typical value is a good indication of device performance.

- (2) Limits are specified to AOQL (Average Outgoing Quality Level).

- (3) Please refer to Figure 32 (I<sup>2</sup>C Timing Diagram).

- (4) Typicals are measured at 25°C and represent the parametric norm.

#### I<sup>2</sup>C (1)(2)

The following specifications apply for  $V_{DD} = 5.0V$  and 3.3V,  $T_A = 25^{\circ}C$ ,  $1.7V \le V_{DD}|^2C \le 2.2V$ , unless otherwise specified.

| Symbol          | Parameter                           | Conditions (3) | LN      | LM49100          |          |  |

|-----------------|-------------------------------------|----------------|---------|------------------|----------|--|

|                 |                                     |                | Typical | Limits           | (Limits) |  |

| t <sub>1</sub>  | I <sup>2</sup> C Clock Period       |                |         | 2.5              | μs (min) |  |

| t <sub>2</sub>  | I <sup>2</sup> C Data Setup Time    |                |         | 250              | ns (min) |  |

| t <sub>3</sub>  | I <sup>2</sup> C Data Stable Time   |                |         | 0                | ns (min) |  |

| t <sub>4</sub>  | Start Condition Time                |                |         | 250              | ns (min) |  |

| t <sub>5</sub>  | Stop Condition Time                 |                |         | 250              | ns (min) |  |

| <sup>t</sup> 6  | I <sup>2</sup> C Data Hold Time     |                |         | 250              | ns (min) |  |

| V <sub>IH</sub> | I <sup>2</sup> C Input Voltage High |                |         | $0.7xV_{DD}I^2C$ | V (min)  |  |

| V <sub>IL</sub> | I <sup>2</sup> C Input Voltage Low  |                |         | $0.3xV_{DD}I^2C$ | V (max)  |  |

<sup>(1)</sup> Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional but do not ensure specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which specify performance limits. This assumes that the device is within the Operating Ratings. Specifications are not for parameters where no limit is given, however, the typical value is a good indication of device performance.

Limits are specified to AOQL (Average Outgoing Quality Level). Please refer to Figure 32 (I<sup>2</sup>C Timing Diagram). Typicals are measured at 25°C and represent the parametric norm.

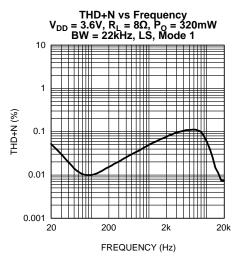

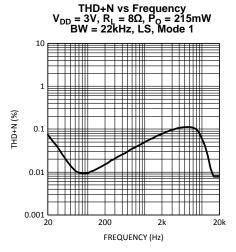

## **Typical Performance Characteristics**

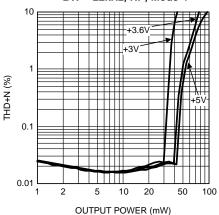

Figure 3.

Figure 5.

Figure 7.

Figure 4.

THD+N vs Frequency  $V_{DD}$  = 5V,  $R_L$  = 32 $\Omega$ ,  $P_O$  = 25mW BW = 22kHz, Headphone, Mode 4,7

Figure 8.

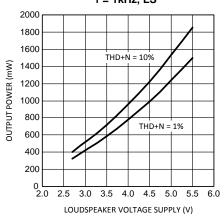

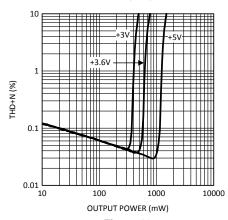

# **Typical Performance Characteristics (continued)**

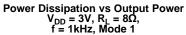

THD+N vs Output Power R<sub>L</sub> = 32Ω, f = 1kHz BW = 22kHz, HP, Mode 4

Figure 9.

Figure 11.

Figure 13.

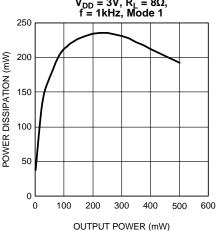

THD+N vs Output Power  $R_L = 8\Omega$ , f = 1kHzBW = 22kHz, LS, Mode 1

Figure 10.

LOUDSPEAKER VOLTAGE SUPPLY (V)

Figure 12.

Figure 14.

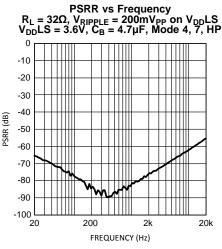

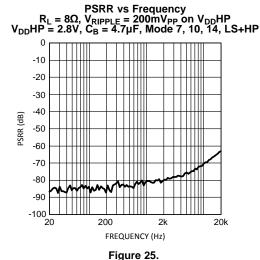

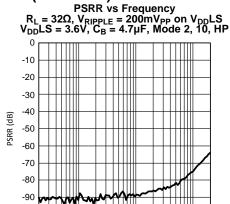

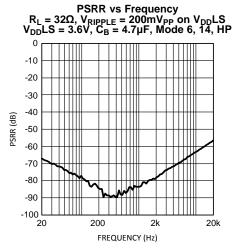

### Typical Performance Characteristics (continued)

PSRR vs Frequency  $R_L = 32\Omega, V_{RIPPLE} = 200 mV_{PP}$  on  $V_{DD}HP$   $V_{DD}HP = 2.8V, C_B = 4.7 \mu F$ , Mode 2, 10, HP

Figure 19.

Figure 16.

PSRR vs Frequency  $R_L = 32\Omega$ ,  $V_{RIPPLE} = 200 mV_{PP}$  on  $V_{DD}HP$   $V_{DD}HP = 2.8V$ ,  $C_B = 4.7 \mu F$ , Mode 4, 7, HP

Figure 20.

20k

#### **Typical Performance Characteristics (continued)**

Figure 21.

Figure 23.

FREQUENCY (Hz)

Figure 22.

200

-100

20

Figure 24.

Figure 26.

# **Typical Performance Characteristics (continued)**

Figure 27.

# PSRR vs Frequency $R_L = 8\Omega$ , $V_{RIPLE} = 200 mV_{PP}$ on $V_{DD} LS$ $V_{DD} LS = 3.6 V$ , $C_B = 4.7 \mu F$ , Mode 5, LS

Figure 29.

#

FREQUENCY (Hz) Figure 28.

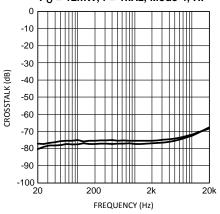

# Crosstalk vs Frequency P<sub>O</sub> = 12mW, f = 1kHz, Mode 4, HP

Figure 30.

#### LM49100 Control Tables

## Table 1. I<sup>2</sup>C Control Register Table<sup>(1)</sup>

|                                | D7 | D6 | D5             | D4  | D3  | D2     | D1    | D0    |

|--------------------------------|----|----|----------------|-----|-----|--------|-------|-------|

| <b>Modes Control</b>           | 0  | 0  | 1              | 1   | MC3 | MC2    | MC1   | MC0   |

| HP Volume (Gain)<br>Control    | 0  | 1  | INPUT_MU<br>TE | 0   | 0   | HPR_SD | HPVC1 | HPVC0 |

| Mono Volume Control            | 1  | 0  | 0              | MV4 | MV3 | MV2    | MV1   | MV0   |

| Left Volume (Gain)<br>Control  | 1  | 1  | 0              | LV4 | LV3 | LV2    | LV1   | LV0   |

| Right Volume (Gain)<br>Control | 1  | 1  | 1              | RV4 | RV3 | RV2    | RV1   | RV0   |

(1) The LM49100 is controlled through an  $I^2C$  compatible interface. The  $I^2C$  chip address is 0xF8 (ADR pin = 0) or 0xFAh (ADDR pin = 1).

# Table 2. Headphone Attenuation Control<sup>(1)</sup>

| Gain Select | HPVC1 | HPVC0 | Gain, dB |

|-------------|-------|-------|----------|

| 0           | 0     | 0     | 0        |

| 1           | 0     | 1     | -12      |

| 2           | 1     | 0     | -18      |

| 3           | 1     | 1     | -24      |

(1) The following bits have added for extra headphone output attenuation:

# Table 3. Output Mode Selection<sup>(1)</sup>

| Output<br>Mode<br>Number | мсз | MC2 | MC1 | MC0 | Handsfree Mono Output                                   | Right HP Output                               | Left HP Output                                |

|--------------------------|-----|-----|-----|-----|---------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|

| 0                        | 0   | 0   | 0   | 0   | SD                                                      | SD                                            | SD                                            |

| 1                        | 0   | 0   | 0   | 1   | $2 \times G_M \times M$                                 | SD                                            | SD                                            |

| 2                        | 0   | 0   | 1   | 0   | SD                                                      | $G_{HP} \times (G_M \times M)$                | $G_{HP} \times (G_M \times M)$                |

| 3                        | 0   | 0   | 1   | 1   | $2 \times (G_L \times L + G_R \times R)$                | SD                                            | SD                                            |

| 4                        | 0   | 1   | 0   | 0   | SD                                                      | $G_{HP} \times (G_R \times R)$                | $G_{HP} \times (G_L \times L)$                |

| 5                        | 0   | 1   | 0   | 1   | $2 \times (G_L \times L + G_R \times R + G_M \times M)$ | SD                                            | SD                                            |

| 6                        | 0   | 1   | 1   | 0   | SD                                                      | $G_{HP} \times (G_R \times R + G_M \times M)$ | $G_{HP} \times (G_L \times L + G_M \times M)$ |

| 7                        | 0   | 1   | 1   | 1   | $2 \times (G_L \times L + G_R \times R)$                | $G_{HP} \times (G_R \times R)$                | $G_{HP} \times (G_L \times L)$                |

| 10                       | 1   | 0   | 1   | 0   | $2 \times (G_L \times L + G_R \times R)$                | $G_{HP} \times (G_M \times M)$                | $G_{HP} \times (G_M \times M)$                |

| 14                       | 1   | 1   | 1   | 0   | $2 \times (G_L \times L + G_R \times R)$                | $G_{HP} \times (G_R \times R + G_M \times M)$ | $G_{HP} \times (G_L \times L + G_M \times M)$ |

M — Mono input signal

Table 4. Mono/Stereo Left/Stereo Right Input Gain Control

| Volume Step | MV4/LV4/RV4 | MV3/LV3/RV3 | MV2/LV2/RV2 | MV1/LV1/RV1 | MV0/LV0/RV0 | R/L Gain, dB | MonoGain, dB |

|-------------|-------------|-------------|-------------|-------------|-------------|--------------|--------------|

| 1           | 0           | 0           | 0           | 0           | 0           | -54          | -60          |

| 2           | 0           | 0           | 0           | 0           | 1           | -47          | -53          |

| 3           | 0           | 0           | 0           | 1           | 0           | -40.5        | -46.5        |

| 4           | 0           | 0           | 0           | 1           | 1           | -34.5        | -40.5        |

| 5           | 0           | 0           | 1           | 0           | 0           | -30.0        | -36          |

<sup>(1)</sup> G<sub>L</sub> — Left channel gain

G<sub>R</sub> — Right channel gain

G<sub>M</sub> — Mono channel gain

G<sub>HP</sub> — Headphone Amplifier gain

R — Right input signal

L — Left input signal

SD — Shutdown

Table 4. Mono/Stereo Left/Stereo Right Input Gain Control (continued)

| i dalo 4. inchescio a Lorgotoro Nigrit input dum control (continuo) |             |             |             |             |             |              |              |  |  |  |  |

|---------------------------------------------------------------------|-------------|-------------|-------------|-------------|-------------|--------------|--------------|--|--|--|--|

| Volume Step                                                         | MV4/LV4/RV4 | MV3/LV3/RV3 | MV2/LV2/RV2 | MV1/LV1/RV1 | MV0/LV0/RV0 | R/L Gain, dB | MonoGain, dB |  |  |  |  |

| 6                                                                   | 0           | 0           | 1           | 0           | 1           | -27          | -33          |  |  |  |  |

| 7                                                                   | 0           | 0           | 1           | 1           | 0           | -24          | -30          |  |  |  |  |

| 8                                                                   | 0           | 0           | 1           | 1           | 1           | -21          | -27          |  |  |  |  |

| 9                                                                   | 0           | 1           | 0           | 0           | 0           | -18          | -24          |  |  |  |  |

| 10                                                                  | 0           | 1           | 0           | 0           | 1           | <b>-</b> 15  | -21          |  |  |  |  |

| 11                                                                  | 0           | 1           | 0           | 1           | 0           | -13.5        | -19.5        |  |  |  |  |

| 12                                                                  | 0           | 1           | 0           | 1           | 1           | -12          | -18          |  |  |  |  |

| 13                                                                  | 0           | 1           | 1           | 0           | 0           | -10.5        | -16.5        |  |  |  |  |

| 14                                                                  | 0           | 1           | 1           | 0           | 1           | -9           | -15          |  |  |  |  |

| 15                                                                  | 0           | 1           | 1           | 1           | 0           | -7.5         | -13.5        |  |  |  |  |

| 16                                                                  | 0           | 1           | 1           | 1           | 1           | -6           | -12          |  |  |  |  |

| 17                                                                  | 1           | 0           | 0           | 0           | 0           | -4.5         | -10.5        |  |  |  |  |

| 18                                                                  | 1           | 0           | 0           | 0           | 1           | -3           | -9           |  |  |  |  |

| 19                                                                  | 1           | 0           | 0           | 1           | 0           | -1.5         | -7.5         |  |  |  |  |

| 20                                                                  | 1           | 0           | 0           | 1           | 1           | 0            | -6           |  |  |  |  |

| 21                                                                  | 1           | 0           | 1           | 0           | 0           | 1.5          | -4.5         |  |  |  |  |

| 22                                                                  | 1           | 0           | 1           | 0           | 1           | 3            | -3           |  |  |  |  |

| 23                                                                  | 1           | 0           | 1           | 1           | 0           | 4.5          | -1.5         |  |  |  |  |

| 24                                                                  | 1           | 0           | 1           | 1           | 1           | 6            | 0            |  |  |  |  |

| 25                                                                  | 1           | 1           | 0           | 0           | 0           | 7.5          | 1.5          |  |  |  |  |

| 26                                                                  | 1           | 1           | 0           | 0           | 1           | 9            | 3            |  |  |  |  |

| 27                                                                  | 1           | 1           | 0           | 1           | 0           | 10.5         | 4.5          |  |  |  |  |

| 28                                                                  | 1           | 1           | 0           | 1           | 1           | 12           | 6            |  |  |  |  |

| 29                                                                  | 1           | 1           | 1           | 0           | 0           | 13.5         | 7.5          |  |  |  |  |

| 30                                                                  | 1           | 1           | 1           | 0           | 1           | 15           | 9            |  |  |  |  |

| 31                                                                  | 1           | 1           | 1           | 1           | 0           | 16.5         | 10.5         |  |  |  |  |

| 32                                                                  | 1           | 1           | 1           | 1           | 1           | 18           | 12           |  |  |  |  |

#### APPLICATION INFORMATION

#### **MINIMIZING CLICK AND POP**

To minimize the audible click and pop heard through a headphone, maximize the input signal through the corresponding volume (gain) control registers and adjust the output amplifier gain accordingly to achieve the user's desired signal gain. For example, setting the output of the headphone amplifier to -24dB and setting the input volume control gain to 24dB will reduce the output offset from 7mV (typical) to 2.2mV (typical). This will reduce the audible click and pop noise significantly while maintaining a 0dB signal gain.

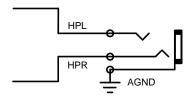

#### SIGNAL GROUND NOISE

The LM49100 has proprietary suppression circuitry, which provides an additional -50dB (typical) attenuation of the headphone ground noise and its incursion into the headphone. For optimum utilization of this feature the headphone jack ground should connect to the AGND (E3) bump.

www.ti.com

#### I<sup>2</sup>C PIN DESCRIPTION

**SDA:** This is the serial data input pin.

**SCL:** This is the clock input pin.

**ADDR:** This is the address select input pin.

#### I<sup>2</sup>C COMPATIBLE INTERFACE

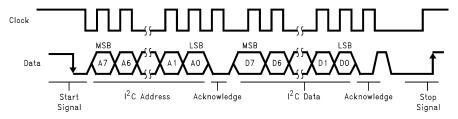

The LM49100 uses a serial bus which conforms to the I<sup>2</sup>C protocol to control the chip's functions with two wires: clock (SCL) and data (SDA). The clock line is uni-directional. The data line is bi-directional (open-collector). The LM49100's I<sup>2</sup>C compatible interface supports standard (100kHz) and fast (400kHz) I<sup>2</sup>C modes. In this discussion, the master is the controlling microcontroller and the slave is the LM49100.

The I<sup>2</sup>C address for the LM49100 is determined using the ADDR pin. The LM49100's two possible I<sup>2</sup>C chip addresses are of the form 111110 $X_1$ 0 (binary), where  $X_1 = 0$ , if ADDR pin is logic LOW; and  $X_1 = 1$ , if ADDR pin is logic HIGH. If the I<sup>2</sup>C interface is used to address a number of chips in a system, the LM49100's chip address can be changed to avoid any possible address conflicts.

The bus format for the I<sup>2</sup>C interface is shown in Figure 31. The bus format diagram is broken up into six major sections:

The "start" signal is generated by lowering the data signal while the clock signal is HIGH. The start signal will alert all devices attached to the I<sup>2</sup>C bus to check the incoming address against their own address.

The 8-bit chip address is sent next, most significant bit first. The data is latched in on the rising edge of the clock. Each address bit must be stable while the clock level is HIGH.

After the last bit of the address bit is sent, the master releases the data line HIGH (through a pull-up resistor). Then the master sends an acknowledge clock pulse. If the LM49100 has received the address correctly, then it holds the data line LOW during the clock pulse. If the data line is not held LOW during the acknowledge clock pulse, then the master should abort the rest of the data transfer to the LM49100.

The 8 bits of data are sent next, most significant bit first. Each data bit should be valid while the clock level is stable HIGH.

After the data byte is sent, the master must check for another acknowledge to see if the LM49100 received the data.

If the master has more data bytes to send to the LM49100, then the master can repeat the previous two steps until all data bytes have been sent.

The "stop" signal ends the transfer. To signal "stop", the data signal goes HIGH while the clock signal is HIGH. The data line should be held HIGH when not in use.

# I<sup>2</sup>C INTERFACE POWER SUPPLY PIN (V<sub>DD</sub>I<sup>2</sup>C)

The LM49100's  $I^2C$  interface is powered up through the  $V_{DD}$   $I^2C$  pin. The LM49100's  $I^2C$  interface operates at a voltage level set by the  $V_{DD}$   $I^2C$  pin which can be set independent to that of the main power supply pin  $V_{DD}$ . This is ideal whenever logic levels for the  $I^2C$  interface are dictated by a microcontroller or microprocessor that is operating at a lower supply voltage than the main battery of a portable system.

Figure 31. I<sup>2</sup>C Bus Format

Figure 32. I<sup>2</sup>C Timing Diagram

#### PCB LAYOUT AND SUPPLY REGULATION CONSIDERATIONS FOR DRIVING 8Ω LOAD

Power dissipated by a load is a function of the voltage swing across the load and the load's impedance. As load impedance decreases, load dissipation becomes increasingly dependent on the interconnect (PCB trace and wire) resistance between the amplifier output pins and the load's connections. Residual trace resistance causes a voltage drop, which results in power dissipated in the trace and not in the load as desired. For example,  $0.1\Omega$ trace resistance reduces the output power dissipated by an 8Ω load from 158.3mW to 156.4mW. The problem of decreased load dissipation is exacerbated as load impedance decreases. Therefore, to maintain the highest load dissipation and widest output voltage swing, PCB traces that connect the output pins to a load must be as wide as possible.

Poor power supply regulation adversely affects maximum output power. A poorly regulated supply's output voltage decreases with increasing load current. Reduced supply voltage causes decreased headroom, output signal clipping, and reduced output power. Even with tightly regulated supplies, trace resistance creates the same effects as poor supply regulation. Therefore, making the power supply traces as wide as possible helps maintain full output voltage swing.

#### **BRIDGE CONFIGURATION EXPLANATION**

The LM49100 drives a load, such as a loudspeaker, connected between outputs, LS+ and LS-.

This results in both amplifiers producing signals identical in magnitude, but 180° out of phase. Taking advantage of this phase difference, a load is placed between LS- and LS+ and driven differentially (commonly referred to as "bridge mode").

Bridge mode amplifiers are different from single-ended amplifiers that drive loads connected between a single amplifier's output and ground. For a given supply voltage, bridge mode has a distinct advantage over the singleended configuration: its differential output doubles the voltage swing across the load. Theoretically, this produces four times the output power when compared to a single-ended amplifier under the same conditions. This increase in attainable output power assumes that the amplifier is not current limited and that the output signal is not clipped.

Another advantage of the differential bridge output is no net DC voltage across the load. This is accomplished by biasing LS- and LS+ outputs at half-supply. This eliminates the coupling capacitor that single supply, singleended amplifiers require. Eliminating an output coupling capacitor in a typical single-ended configuration forces a single-supply amplifier's half-supply bias voltage across the load. This increases internal IC power dissipation and may permanently damage loads such as loudspeakers.

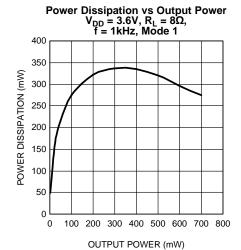

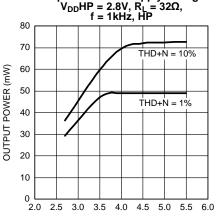

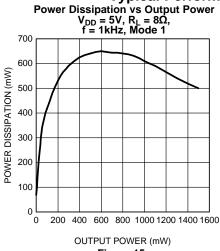

#### **POWER DISSIPATION**

Power dissipation is a major concern when designing a successful single-ended or bridged amplifier.

A direct consequence of the increased power delivered to the load by a bridge amplifier is higher internal power dissipation. The LM49100 has a pair of bridged-tied amplifiers driving a handsfree loudspeaker, LS. The maximum internal power dissipation operating in the bridge mode is twice that of a single-ended amplifier. From Equation 1, assuming a 5V power supply and an  $8\Omega$  load, the maximum MONO power dissipation is 634mW.

Submit Documentation Feedback Product Folder Links: LM49100

$$P_{DMAX-LS} = 4(V_{DD})^2 I (2\pi^2 R_L)$$

: Bridge Mode

(1)

The LM49100 also has a pair of single-ended amplifiers driving stereo headphones, HPR and HPL. The maximum internal power dissipation for HPR and HPL is given by Equation 2. Assuming a 2.8V power supply and a  $32\Omega$  load, the maximum power dissipation for  $L_{OUT}$  and  $R_{OUT}$  is 49mW, or 99mW total.

$$P_{DMAX-HPL} = 4(V_{DD}HP)^2 / (2\pi^2 R_1): Single-ended Mode$$

(2)

The maximum internal power dissipation of the LM49100 occurs when all three amplifiers pairs are simultaneously on; and is given by Equation 3.

$$P_{DMAX-TOTAL} = P_{DMAX-LS} + P_{DMAX-HPL} + P_{DMAX-HPR}$$

(3)

The maximum power dissipation point given by Equation 3 must not exceed the power dissipation given by Equation 4:

$$P_{DMAX} = (T_{JMAX} - T_A) / \theta_{JA}$$

(4)

The LM49100's  $T_{JMAX} = 150^{\circ}\text{C}$ . In the csBGA package, the LM49100's  $\theta_{JA}$  is  $50.2^{\circ}\text{C/W}$ . At any given ambient temperature  $T_A$ , use Equation 4 to find the maximum internal power dissipation supported by the IC packaging. Rearranging Equation 4 and substituting  $P_{DMAX-TOTAL}$  for  $P_{DMAX}$  results in Equation 5. This equation gives the maximum ambient temperature that still allows maximum stereo power dissipation without violating the LM49100's maximum junction temperature.

$$T_{A} = T_{\text{IMAX}} - P_{\text{DMAX-TOTAL}} \theta_{\text{IA}}$$

(5)

For a typical application with a 5V power supply and an  $8\Omega$  load, the maximum ambient temperature that allows maximum mono power dissipation without exceeding the maximum junction temperature is approximately 114°C for the csBGA package.

$$T_{\text{JMAX}} = P_{\text{DMAX-TOTAL}} \theta_{\text{JA}} + T_{\text{A}} \tag{6}$$

Equation 6 gives the maximum junction temperature  $T_{\text{JMAX}}$ . If the result violates the LM49100's 150°C, reduce the maximum junction temperature by reducing the power supply voltage or increasing the load resistance. Further allowance should be made for increased ambient temperatures.

The above examples assume that a device is a surface mount part operating around the maximum power dissipation point. Since internal power dissipation is a function of output power, higher ambient temperatures are allowed as output power or duty cycle decreases. If the result of Equation 3 is greater than that of Equation 4, then decrease the supply voltage, increase the load impedance, or reduce the ambient temperature. If these measures are insufficient, a heat sink can be added to reduce  $\theta_{JA}$ . The heat sink can be created using additional copper area around the package, with connections to the ground pin(s), supply pin and amplifier output pins.

#### **POWER SUPPLY BYPASSING**

As with any power amplifier, proper supply bypassing is critical for low noise performance and high power supply rejection. Applications that employ a 5V regulator typically use a 1µF in parallel with a 0.1µF filter capacitors to stabilize the regulator's output, reduce noise on the supply line, and improve the supply's transient response. However, their presence does not eliminate the need for a local 4.7µF tantalum bypass capacitor and a parallel 0.1µF ceramic capacitor connected between the LM49100's supply pin and ground. Keep the length of leads and traces that connect capacitors between the LM49100's power supply pin and ground as short as possible.

#### **SELECTING EXTERNAL COMPONENTS**

#### Input Capacitor Value Selection

Amplifying the lowest audio frequencies requires high value input coupling capacitor ( $C_{IN}$  in Figure 1). A high value capacitor can be expensive and may compromise space efficiency in portable designs. In many cases, however, the loudspeakers used in portable systems, whether internal or external, have little ability to reproduce signals below 150Hz. Applications using loudspeakers and headphones with this limited frequency response reap little improvement by using large input capacitor.

The internal input resistor ( $R_i$ ), typical 12.5k $\Omega$ , and the input capacitor ( $C_{IN}$ ) produce a high pass filter cutoff frequency that is found using Equation 7.

$$f_c = 1 / (2\pi R_i C_{IN})$$

(7)

#### **Bypass Capacitor Value Selection**

Besides minimizing the input capacitor size, careful consideration should be paid to value of  $C_B$ , the capacitor connected to the BYPASS pin. Since  $C_B$  determines how fast the LM49100 settles to quiescent operation, its value is critical when minimizing turn-on pops. Choosing  $C_B$  equal to 2.2 $\mu$ F along with a small value of  $C_i$  (in the range of 0.1 $\mu$ F to 0.33 $\mu$ F), produces a click-less and pop-less shutdown function. As discussed above, choosing  $C_{IN}$  no larger than necessary for the desired bandwidth helps minimize clicks and pops.  $C_B$ 's value should be in the range of 4 to 5 times the value of  $C_{IN}$ . This ensures that output transients are eliminated when power is first applied or the LM49100 resumes operation after shutdown.

#### **Demo Board Schematic**

Figure 33. Demo Board Schematic

Product Folder Links: *LM49100*

20

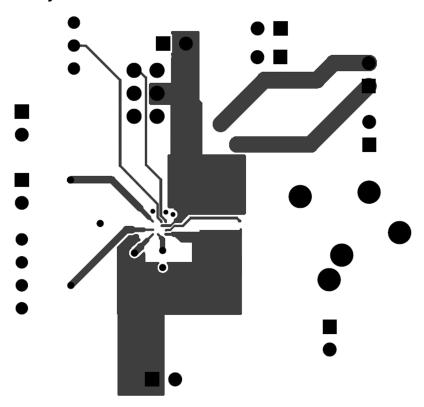

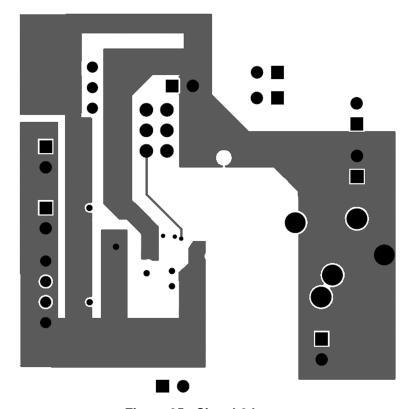

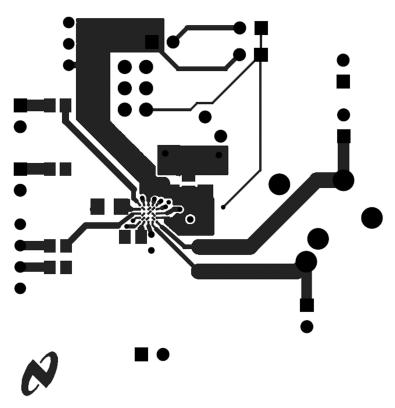

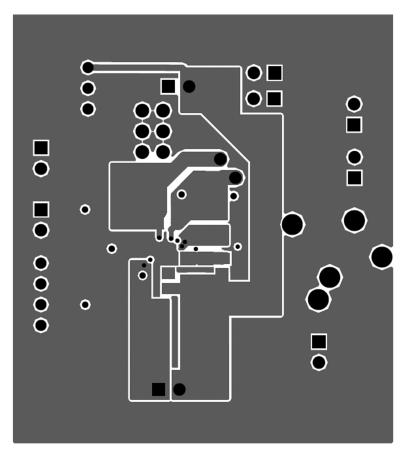

# **Demonstration Board Layout**

Figure 34. Signal 1 Layer

Figure 35. Signal 2 Layer

Copyright © 2007–2013, Texas Instruments Incorporated

Figure 36. Top Layer

Figure 37. Top Overlay

Figure 38. Bottom Layer

# 551013056-001 Rev. A

# Figure 39. Bottom Overlay

#### **REVISION HISTORY**

| Rev | Date       | Description                                                                                             |  |  |  |  |  |

|-----|------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1.0 | 06/21/07   | Initial release.                                                                                        |  |  |  |  |  |

| 1.1 | 06/28/07   | Changed the mktg outline from TLA25XXX to GRA25A.                                                       |  |  |  |  |  |

| 1.2 | 08/09/07   | Replaced some curves.                                                                                   |  |  |  |  |  |

| 1.3 | 08/13/07   | Changed the $f = 1 \text{kHz}$ into $f = 217 \text{Hz}$ (PSRR) in the Electrical Characteristics table. |  |  |  |  |  |

| 1.4 | 08/14/07   | Edited Table 1.                                                                                         |  |  |  |  |  |

| 1.5 | 09/18/07   | Edited the Schematic Diagram.                                                                           |  |  |  |  |  |

| F   | 05/02/2013 | Changed layout of National Data Sheet to TI format.                                                     |  |  |  |  |  |

## PACKAGE OPTION ADDENDUM

10-Dec-2020

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|----------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                    |              |                      |         |

| LM49100GR/NOPB   | ACTIVE | csBGA        | NYA                | 25   | 1000           | RoHS & Green | SNAGCU                        | Level-1-260C-UNLIM | -40 to 85    | GC9                  | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 5-Nov-2021

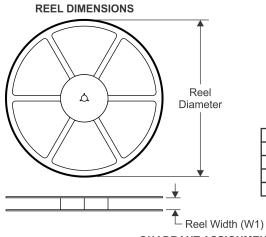

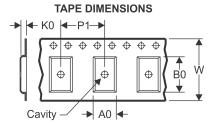

# TAPE AND REEL INFORMATION

| Α0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

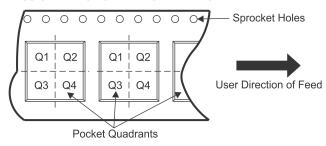

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM49100GR/NOPB | csBGA           | NYA                | 25 | 1000 | 178.0                    | 12.4                     | 3.3        | 3.3        | 1.6        | 8.0        | 12.0      | Q1               |

www.ti.com 5-Nov-2021

#### \*All dimensions are nominal

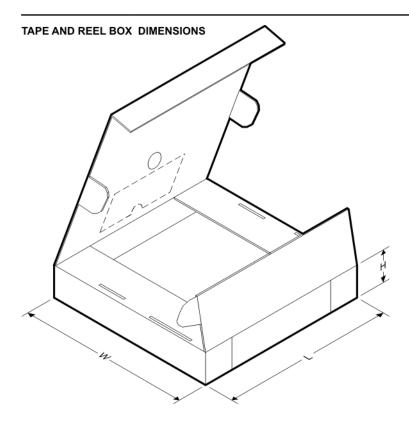

| Device         | Device Package Type |     | Pins SPQ |      | Length (mm) | Width (mm) | Height (mm) |  |

|----------------|---------------------|-----|----------|------|-------------|------------|-------------|--|

| LM49100GR/NOPB | csBGA               | NYA | 25       | 1000 | 208.0       | 191.0      | 35.0        |  |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated