www.ti.com

SNAS3810-NOVEMBER 2006-REVISED MARCH 2013

# LMK03000 Family Precision Clock Conditioner with Integrated VCO

Check for Samples: LMK03000, LMK03000C, LMK03000D, LMK03001, LMK03001C, LMK03001D, LMK03033, LMK03033C

#### **FEATURES**

- **Integrated VCO with Very Low Phase Noise**

- Integrated Integer-N PLL with Outstanding Normalized Phase Noise Contribution of -224 dBc/Hz

- VCO Divider Values of 2 to 8 (All Divides)

- Channel Divider Values of 1, 2 to 510 (even divides)

- LVDS and LVPECL Clock Outputs

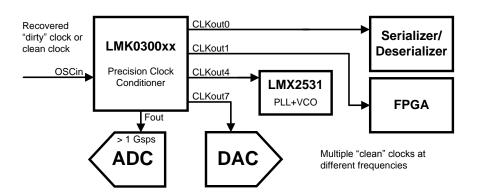

#### TARGET APPLICATIONS 1.1

- **Data Converter Clocking**

- Networking, SONET/SDH, DSLAM

- Wireless Infrastructure

- Medical

- **Test and Measurement**

- Military / Aerospace

- Partially Integrated Loop Filter

- **Dedicated Divider and Delay Blocks on Each Clock Output**

- . Pin Compatible Family of Clocking Devices

- 3.15 to 3.45 V Operation

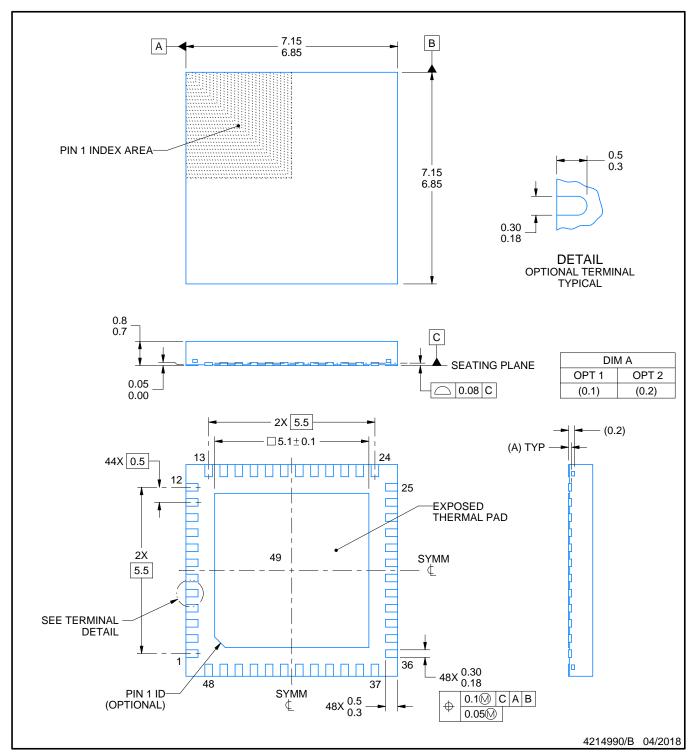

- Package: 48 Pin WQFN (7.0 x 7.0 x 0.8 mm)

- 200 fs RMS Clock Generator Performance (10 Hz to 20 MHz) with a Clean Input Clock

|           |          | VCC                   | )                  |

|-----------|----------|-----------------------|--------------------|

| Device    | Outputs  | Tuning Range<br>(MHz) | RMS Jitter<br>(fs) |

| LMK03000C |          |                       | 400                |

| LMK03000  |          | 1185 - 1296           | 800                |

| LMK03000D | 3 LVDS   |                       | 1200               |

| LMK03001C | 5 LVPECL |                       | 400                |

| LMK03001  |          | 1470 - 1570           | 800                |

| LMK03001D |          | 1200                  |                    |

| LMK03033C | 4 LVDS   | 1942 2460             | 500                |

| LMK03033  | 4 LVPECL | 1843 - 2160           | 800                |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

#### 1.2 DESCRIPTION

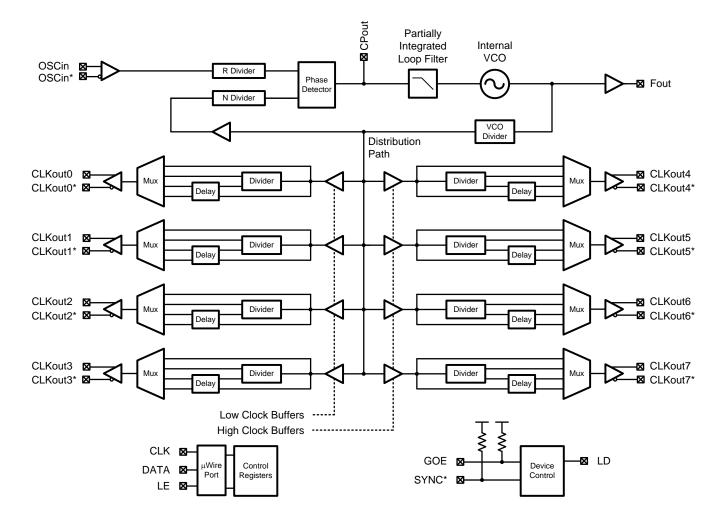

The LMK03000 family of precision clock conditioners combine the functions of jitter cleaning/reconditioning, multiplication, and distribution of a reference clock. The devices integrate a Voltage Controlled Oscillator (VCO), a high performance Integer-N Phase Locked Loop (PLL), a partially integrated loop filter, and up to eight outputs in various LVDS and LVPECL combinations.

The VCO output is optionally accessible on the Fout port. Internally, the VCO output goes through a VCO Divider to feed the various clock distribution blocks.

Each clock distribution block includes a programmable divider, a phase synchronization circuit, a programmable delay, a clock output mux, and an LVDS or LVPECL output buffer. This allows multiple integer-related and phase-adjusted copies of the reference to be distributed to eight system components.

The clock conditioners come in a 48-pin WQFN package and are footprint compatible with other clocking devices in the same family.

| 1 | FEA  | TURES <u>1</u>                                   |    | 6.10   | POWER ON RESET                       | 1        |

|---|------|--------------------------------------------------|----|--------|--------------------------------------|----------|

|   | 1.1  | TARGET APPLICATIONS 1                            |    | 6.11   | DIGITAL LOCK DETECT                  | 18       |

|   | 1.2  | DESCRIPTION 2                                    | 7  | Gene   | eral Programming Information         | 19       |

| 2 | Devi | ice Information 3                                |    | 7.1    | RECOMMENDED PROGRAMMING SEQUENCE .   | 19       |

|   | 2.1  | Functional Block Diagram 3                       |    | 7.2    | REGISTER R0 to R7                    | 2        |

|   | 2.2  | Connection Diagram 4                             |    | 7.3    | REGISTER R8                          | 2        |

| 3 | Elec | trical Specifications 6                          |    | 7.4    | REGISTER R9                          | 2        |

|   | 3.1  | Absolute Maximum Ratings 6                       |    | 7.5    | REGISTER R11                         | 24       |

|   | 3.2  | Recommended Operating Conditions 6               |    | 7.6    | REGISTER R13                         | 24       |

|   | 3.3  | Package Thermal Resistance 6                     |    | 7.7    | REGISTER R14                         | 2        |

|   | 3.4  | Electrical Characteristics 7                     |    | 7.8    | REGISTER R15                         | 2        |

|   | 3.5  | Serial Data Timing Diagram 11                    | 8  | Appl   | lication Information                 | 2        |

| 4 | Mea  | surement Definitions 12                          |    | 8.1    | SYSTEM LEVEL DIAGRAM                 | 2        |

|   | 4.1  | Charge Pump Current Specification Definitions 12 |    | 8.2    | BIAS PIN                             | 28       |

| 5 | Typi | cal Performance Characteristics 13               |    | 8.3    | LDO BYPASS                           | 28       |

| 6 | Fund | ctional Description 15                           |    | 8.4    | LOOP FILTER                          | 29       |

|   | 6.1  | BIAS PIN                                         |    | 8.5    | CURRENT CONSUMPTION / POWER          |          |

|   | 6.2  | LDO BYPASS <u>15</u>                             |    |        | DISSIPATION CALCULATIONS             | _        |

|   | 6.3  | OSCILLATOR INPUT PORT (OSCin, OSCin*) 15         |    | 8.6    | THERMAL MANAGEMENT                   | <u>3</u> |

|   | 6.4  | LOW NOISE, FULLY INTEGRATED VCO 15               |    | 8.7    | TERMINATION AND USE OF CLOCK OUTPUTS | 21       |

|   | 6.5  | CLKout DELAYS                                    |    | 8.8    | (DRIVERS)                            |          |

|   | 6.6  | LVDS/LVPECL OUTPUTS 16                           |    | 8.9    | MORE THAN EIGHT OUTPUTS WITH AN      | 30       |

|   | 6.7  | GLOBAL CLOCK OUTPUT SYNCHRONIZATION 16           |    | 0.5    | LMK03000 FAMILY DEVICE               | 3        |

|   | 6.8  | CLKout OUTPUT STATES                             | Re | vision | History                              |          |

|   | 6.9  | GLOBAL OUTPUT ENABLE AND LOCK DETECT 17          |    |        | -                                    |          |

|   |      |                                                  |    |        |                                      |          |

#### 2 Device Information

### 2.1 Functional Block Diagram

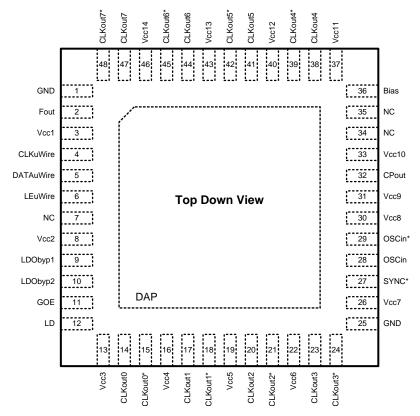

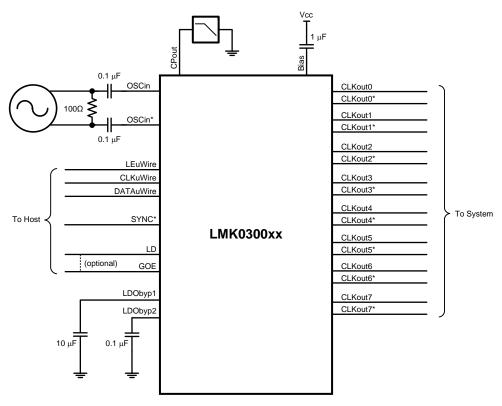

## 2.2 Connection Diagram

Figure 2-1. 48-Pin WQFN Package

#### **Table 2-1. PIN DESCRIPTIONS**

| Pin #                                                      | Pin Name                                                                                | I/O | Description                                                                   |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------|

| 1, 25                                                      | GND                                                                                     | -   | Ground                                                                        |

| 2                                                          | Fout                                                                                    | 0   | Internal VCO Frequency Output                                                 |

| 3, 8, 13, 16, 19, 22,<br>26, 30, 31, 33, 37,<br>40, 43, 46 | Vcc1, Vcc2, Vcc3, Vcc4, Vcc5, Vcc6, Vcc7, Vcc8, Vcc9, Vcc10, Vcc11, Vcc12, Vcc13, Vcc14 | -   | Power Supply                                                                  |

| 4                                                          | CLKuWire                                                                                | I   | MICROWIRE Clock Input                                                         |

| 5                                                          | DATAuWire                                                                               | I   | MICROWIRE Data Input                                                          |

| 6                                                          | LEuWire                                                                                 | I   | MICROWIRE Latch Enable Input                                                  |

| 7, 34, 35                                                  | NC                                                                                      | -   | No Connection to these pins                                                   |

| 9, 10                                                      | LDObyp1, LDObyp2                                                                        | -   | LDO Bypass                                                                    |

| 11                                                         | GOE                                                                                     | I   | Global Output Enable                                                          |

| 12                                                         | LD                                                                                      | 0   | Lock Detect and Test Output                                                   |

| 14, 15                                                     | CLKout0, CLKout0*                                                                       | 0   | LVDS Clock Output 0                                                           |

| 17, 18                                                     | CLKout1, CLKout1*                                                                       | 0   | LVDS Clock Output 1                                                           |

| 20, 21                                                     | CLKout2, CLKout2*                                                                       | 0   | LVDS Clock Output 2                                                           |

| 23, 24                                                     | CLKout3, CLKout3*                                                                       | 0   | Clock Output 3<br>(LVDS for LMK03033C/LMK03033<br>LVPECL for all other parts) |

| 27                                                         | SYNC*                                                                                   | I   | Global Clock Output Synchronization                                           |

| 28, 29                                                     | OSCin, OSCin*                                                                           | ı   | Oscillator Clock Input; Should be AC coupled                                  |

| 32                                                         | CPout                                                                                   | 0   | Charge Pump Output                                                            |

| 36                                                         | Bias                                                                                    | -1  | Bias Bypass                                                                   |

| 38, 39                                                     | CLKout4, CLKout4*                                                                       | 0   | LVPECL Clock Output 4                                                         |

| 41, 42                                                     | CLKout5, CLKout5*                                                                       | 0   | LVPECL Clock Output 5                                                         |

| 44, 45                                                     | CLKout6, CLKout6*                                                                       | 0   | LVPECL Clock Output 6                                                         |

| 47, 48                                                     | CLKout7, CLKout7*                                                                       | 0   | LVPECLClock Output 7                                                          |

| DAP                                                        | DAP                                                                                     | -   | Die Attach Pad is Ground                                                      |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# 3 Electrical Specifications

# 3.1 Absolute Maximum Ratings (1)(2)(3)

| Parameter                     | Symbol           | Ratings                         | Units |

|-------------------------------|------------------|---------------------------------|-------|

| Power Supply Voltage          | V <sub>cc</sub>  | -0.3 to 3.6                     | V     |

| Input Voltage                 | V <sub>IN</sub>  | -0.3 to (V <sub>CC</sub> + 0.3) | V     |

| Storage Temperature Range     | T <sub>STG</sub> | -65 to 150                      | °C    |

| Lead Temperature (solder 4 s) | T <sub>L</sub>   | +260                            | °C    |

| Junction Temperature          | T <sub>J</sub>   | 125                             | °C    |

<sup>(1) &</sup>quot;Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions.

### 3.2 Recommended Operating Conditions

| Parameter            | Symbol          | Min  | Тур | Max  | Units |

|----------------------|-----------------|------|-----|------|-------|

| Ambient Temperature  | T <sub>A</sub>  | -40  | 25  | 85   | °C    |

| Power Supply Voltage | V <sub>CC</sub> | 3.15 | 3.3 | 3.45 | V     |

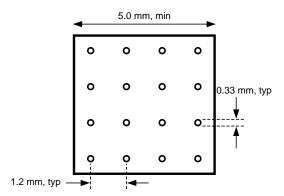

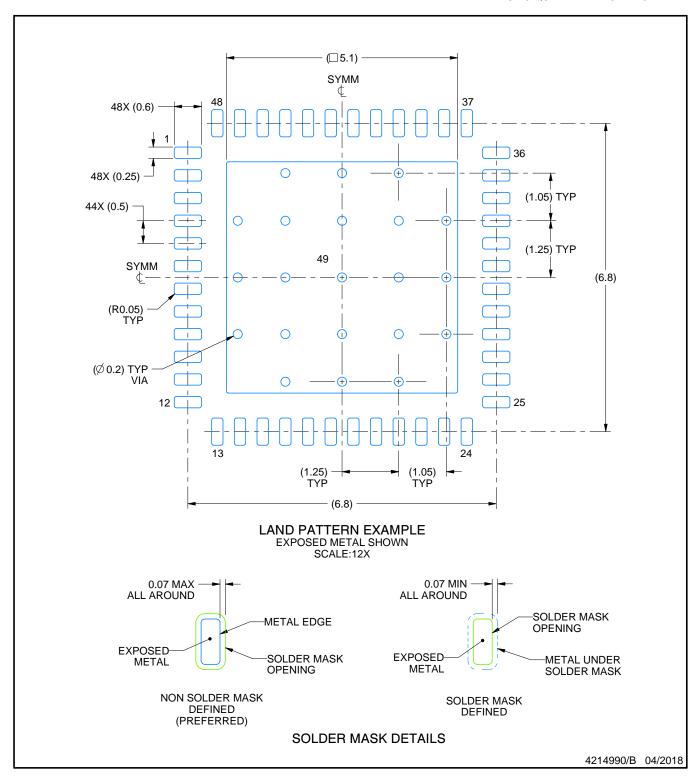

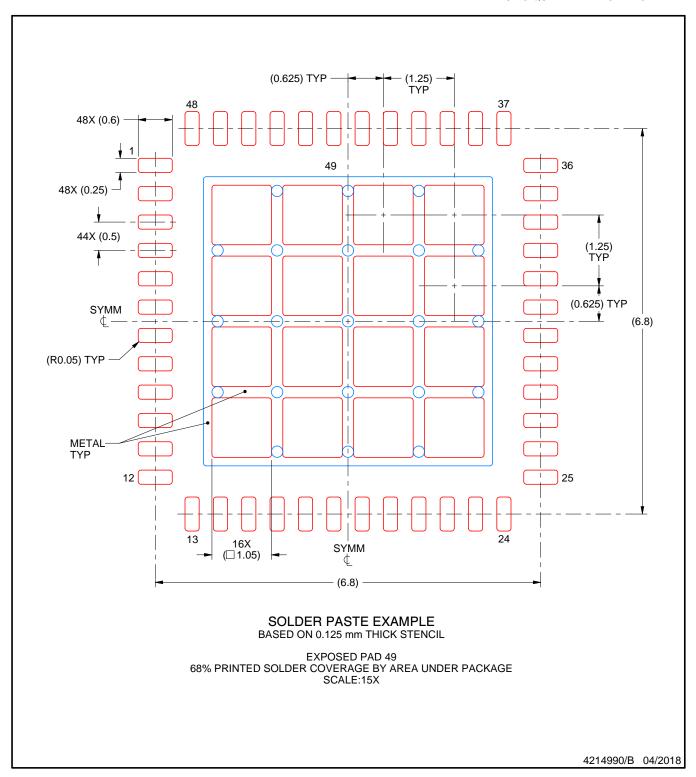

### 3.3 Package Thermal Resistance

| Package          | θ <sub>JA</sub> | θ <sub>J-PAD</sub> (Thermal Pad) |

|------------------|-----------------|----------------------------------|

| 48-Lead WQFN (1) | 27.4° C/W       | 5.8° C/W                         |

<sup>(1)</sup> Specification assumes 16 thermal vias connect the die attach pad to the embedded copper plane on the 4-layer JEDEC board. These vias play a key role in improving the thermal performance of the WQFN. It is recommended that the maximum number of vias be used in the board layout.

<sup>(2)</sup> This device is a high performance integrated circuit with ESD handling precautions. Handling of this device should only be done at ESD protected work stations. The device is rated to a HBM-ESD of > 2 kV, a MM-ESD of > 200 V, and a CDM-ESD of > 1.2 kV.

<sup>(3)</sup> If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

### 3.4 Electrical Characteristics (1)

$(3.15 \text{ V} \leq \text{Vcc} \leq 3.45 \text{ V}, -40 \text{ °C} \leq \text{T}_{\text{A}} \leq 85 \text{ °C}, \text{ Differential Inputs/Outputs; Vboost=0; except as specified. Typical values represent most likely parametric norms at Vcc = 3.3 V, T<sub>A</sub> = 25 °C, and at the Recommended Operation Conditions at the time of product characterization and are not ensured).$

| Symbol                    | Parameter                                                                  | Conditions                                                        | Min                            | Тур   | Max | Units  |  |

|---------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------|-------|-----|--------|--|

|                           | Curre                                                                      | ent Consumption                                                   |                                |       |     |        |  |

| I <sub>cc</sub>           | Entire device; one LVDS and one LVPECL clock enabled; no divide; no delay. |                                                                   |                                | 161.8 |     | mA     |  |

|                           |                                                                            | Entire device; All Outputs Off (no emitter resistors placed)      |                                | 86    |     |        |  |

| I <sub>CC</sub> PD        | Power Down Current                                                         | POWERDOWN = 1                                                     |                                | 1     |     | mA     |  |

|                           | Refe                                                                       | rence Oscillator                                                  |                                |       |     |        |  |

| f <sub>OSCin</sub> square | Reference Oscillator Input Frequency<br>Range for Square Wave              | AC assimilarly Differential (1/1)                                 | 1                              |       | 200 | MHz    |  |

| V <sub>OSCin</sub> square | Square Wave Input Voltage for OSCin and OSCin*                             | AC coupled; Differential (V <sub>OD</sub> )                       | 0.2                            |       | 1.6 | Vpp    |  |

|                           | •                                                                          | PLL                                                               |                                | •     |     | •      |  |

| f <sub>PD</sub>           | Phase Detector Frequency                                                   |                                                                   |                                |       | 40  | MHz    |  |

|                           |                                                                            | V <sub>CPout</sub> = Vcc/2, PLL_CP_GAIN = 1x                      | Pout = Vcc/2, PLL_CP_GAIN = 1x | 100   |     |        |  |

| OBest                     | Oharana Barrar Oharana Oharana                                             | V <sub>CPout</sub> = Vcc/2, PLL_CP_GAIN = 4x                      |                                | 400   |     | μA     |  |

| I <sub>SRCE</sub> CPout   | Charge Pump Source Current                                                 | V <sub>CPout</sub> = Vcc/2, PLL_CP_GAIN = 16x                     |                                | 1600  |     |        |  |

|                           |                                                                            | V <sub>CPout</sub> = Vcc/2, PLL_CP_GAIN = 32x                     |                                | 3200  |     |        |  |

|                           |                                                                            | V <sub>CPout</sub> = Vcc/2, PLL_CP_GAIN = 1x                      |                                | -100  |     |        |  |

| l CDt                     | Charge Burger Sigh Correct                                                 | V <sub>CPout</sub> = Vcc/2, PLL_CP_GAIN = 4x                      |                                | -400  |     |        |  |

| I <sub>SINK</sub> CPout   | Charge Pump Sink Current                                                   | V <sub>CPout</sub> = Vcc/2, PLL_CP_GAIN = 16x                     |                                | -1600 |     | μA     |  |

|                           |                                                                            | V <sub>CPout</sub> = Vcc/2, PLL_CP_GAIN = 32x                     |                                | -3200 |     |        |  |

| I <sub>CPout</sub> TRI    | Charge Pump TRI-STATE Current                                              | 0.5 V < V <sub>CPout</sub> < Vcc - 0.5 V                          |                                | 2     | 10  | nA     |  |

| I <sub>CPout</sub> %MIS   | Magnitude of Charge Pump<br>Sink vs. Source Current Mismatch               | V <sub>CPout</sub> = Vcc / 2<br>T <sub>A</sub> = 25°C             |                                | 3     |     | %      |  |

| I <sub>CPout</sub> VTUNE  | Magnitude of Charge Pump<br>Current vs. Charge Pump Voltage<br>Variation   | 0.5 V < V <sub>CPout</sub> < Vcc - 0.5 V<br>T <sub>A</sub> = 25°C |                                | 4     |     | %      |  |

| I <sub>CPout</sub> TEMP   | Magnitude of Charge Pump Current vs. Temperature Variation                 |                                                                   |                                | 4     |     | %      |  |

| DNI10kH-                  | PLL 1/f Noise at 10 kHz Offset (3)                                         | PLL_CP_GAIN = 1x                                                  |                                | -117  |     | dDa/U- |  |

| PN10kHz                   |                                                                            | PLL_CP_GAIN = 32x                                                 |                                | -122  |     | dBc/H  |  |

| DNALL-                    | Normalized Phase Noise Contribution                                        | PLL_CP_GAIN = 1x                                                  |                                | -219  |     | dDa/II |  |

| PN1Hz                     | (4)                                                                        | PLL_CP_GAIN = 32x                                                 |                                | -224  |     | dBc/Hz |  |

<sup>(1)</sup> The Electrical Characteristics table lists ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

(2) See Section 8.5 for more current consumption / power dissipation calculation information.

LMK03033C

<sup>(3)</sup> A specification in modeling PLL in-band phase noise is the 1/f flicker noise, L<sub>PLL\_flicker</sub>(f), which is dominant close to the carrier. Flicker noise has a 10 dB/decade slope. PN10kHz is normalized to a 10 kHz offset and a 1 GHz carrier frequency. PN10kHz = L<sub>PLL\_flicker</sub>(10 kHz) - 20log(Fout / 1 GHz), where L<sub>PLL\_flicker</sub>(f) is the single side band phase noise of only the flicker noise's contribution to total noise, L(f). To measure L<sub>PLL\_flicker</sub>(f) it is important to be on the 10 dB/decade slope close to the carrier. A high compare frequency and a clean crystal are important to isolating this noise source from the total phase noise, L(f). L<sub>PLL\_flicker</sub>(f) can be masked by the reference oscillator performance if a low power or noisy source is used. The total PLL inband phase noise performance is the sum of L<sub>PLL\_flicker</sub>(f) and L<sub>PLL flat</sub>(f).

<sup>(4)</sup> A specification in modeling PLL in-band phase noise is the Normalized Phase Noise Contribution, L<sub>PLL\_flat</sub>(f), of the PLL and is defined as PN1Hz = L<sub>PLL\_flat</sub>(f) – 20log(N) – 10log(f<sub>COMP</sub>). L<sub>PLL\_flat</sub>(f) is the single side band phase noise measured at an offset frequency, f, in a 1 Hz Bandwidth and f<sub>COMP</sub> is the phase detector frequency of the synthesizer. L<sub>PLL\_flat</sub>(f) contributes to the total noise, L(f). To measure L<sub>PLL\_flat</sub>(f) the offset frequency, f, must be chosen sufficiently smaller then the loop bandwidth of the PLL, and yet large enough to avoid a substantial noise contribution from the reference and flicker noise. L<sub>PLL\_flat</sub>(f) can be masked by the reference oscillator performance if a low power or noisy source is used.

$(3.15 \text{ V} \leq \text{Vcc} \leq 3.45 \text{ V}, -40 \text{ °C} \leq \text{T}_{\text{A}} \leq 85 \text{ °C}, \text{ Differential Inputs/Outputs; Vboost=0; except as specified. Typical values represent most likely parametric norms at Vcc = 3.3 V, T<sub>A</sub> = 25 °C, and at the Recommended Operation Conditions at the$ time of product characterization and are not ensured).

| Symbol                | Parameter                                                  | Conditions                                                                                                  | Min  | Тур         | Max  | Units      |  |

|-----------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------|-------------|------|------------|--|

|                       |                                                            | vco                                                                                                         | •    |             | •    |            |  |

|                       |                                                            | LMK03000C/LMK03000/LMK03000D                                                                                | 1185 |             | 1296 |            |  |

| f <sub>Fout</sub>     | VCO Tuning Range                                           | LMK03001C/LMK03001/LMK03001D                                                                                | 1470 |             | 1570 | MHz        |  |

|                       |                                                            | LMK03033C/LMK03033                                                                                          | 1843 |             | 2160 |            |  |

| ΔT <sub>CL</sub>      | Allowable Temperature Drift for Continuous Lock            | After programming R15 for lock, no changes to output configuration are permitted to ensure continuous lock. |      |             | 125  | °C         |  |

| PFout                 | Output Power to a 50 $\Omega$ load driven by Fout $^{(2)}$ | LMK03000C/LMK03000/LMK03000D;<br>T <sub>A</sub> = 25 °C                                                     |      | 3.3         |      |            |  |

|                       |                                                            | LMK03001C/LMK03001/LMK03001D;<br>T <sub>A</sub> = 25 °C                                                     |      | 2.7         |      | dBm        |  |

|                       |                                                            | LMK03033C/LMK03033;T <sub>A</sub> = 25 °C                                                                   |      | -5 to 0     |      |            |  |

|                       |                                                            | LMK03000C/LMK03000/LMK03000D                                                                                |      | 7 to 9      |      |            |  |

| K <sub>VCO</sub>      | Fine Tuning Sensitivity (3)                                | LMK03001C/LMK03001/LMK03001D                                                                                |      | 9 to 11     |      | MHz/V      |  |

| TV/CO                 | The running conditivity                                    | LMK03033C/LMK03033                                                                                          |      | 14 to<br>26 |      | 1011 127 0 |  |

|                       |                                                            | LMK03000C/LMK03001C                                                                                         |      | 400         |      |            |  |

| J <sub>RMS</sub> Fout |                                                            | LMK03000/LMK03001                                                                                           |      | 800         |      |            |  |

|                       | Fout RMS Period Jitter (12 kHz to 20 MHz bandwidth)        | LMK03000D/LMK03001D                                                                                         |      | 1200        |      | fs         |  |

|                       | (12 M IZ to Zo Wi IZ Ballawidil)                           | LMK03033C                                                                                                   |      | 500         |      |            |  |

|                       |                                                            | LMK03033                                                                                                    |      | 800         |      | 1          |  |

Allowable Temperature Drift for Continuous Lock is how far the temperature can drift in either direction and stay in lock from the ambient temperature and programmed state at which the device was when register R15 was programmed. The action of programming the R15 register, even to the same value, activates a frequency calibration routine. This implies that the device will work over the entire frequency range, but if the temperature drifts more than the maximum allowable drift for continuous lock, then it will be necessary to reprogram the R15 register to ensure that the device stays in lock. Regardless of what temperature the device was initially programmed at, the ambient temperature can never drift outside the range of -40 °C ≤ T<sub>A</sub> ≤ 85 °C without violating specifications. For this specification to be valid, the programmed state of the device must not change after R15 is programmed.

Output power varies as a function of frequency. When a range is shown, the higher output power applies to the lower frequency and the lower output power applies to the higher frequency.

The lower sensitivity indicates the typical sensitivity at the lower end of the tuning range, the higher sensitivity at the higher end of the

tuning range

$(3.15 \text{ V} \le \text{Vcc} \le 3.45 \text{ V}, -40 \text{ °C} \le \text{T}_{\text{A}} \le 85 \text{ °C}, \text{ Differential Inputs/Outputs; Vboost=0; except as specified. Typical values represent most likely parametric norms at Vcc = 3.3 V, T<sub>A</sub> = 25 °C, and at the Recommended Operation Conditions at the time of product characterization and are not ensured).$

| Symbol              | Parameter                         | Conditi                                                  | ons            | Min | Тур    | Max | Units  |

|---------------------|-----------------------------------|----------------------------------------------------------|----------------|-----|--------|-----|--------|

|                     | V                                 | CO (Continued)                                           |                |     | •      |     | •      |

|                     |                                   |                                                          | 10 kHz Offset  |     | -91.4  |     |        |

|                     |                                   | LMK03000C                                                | 100 kHz Offset |     | -116.8 |     |        |

|                     |                                   | $f_{Fout} = 1296 \text{ MHz}^{(1)}$                      | 1 MHz Offset   |     | -137.8 |     |        |

|                     |                                   |                                                          | 10 MHz Offset  |     | -156.9 |     |        |

|                     |                                   |                                                          | 10 kHz Offset  |     | -93.5  |     |        |

|                     |                                   | LMK03000C                                                | 100 kHz Offset |     | -118.5 |     |        |

|                     |                                   | $f_{Fout} = 1185 \text{ MHz}^{(1)}$                      | 1 MHz Offset   |     | -139.4 |     |        |

|                     |                                   |                                                          | 10 MHz Offset  |     | -158.4 |     | dBc/Hz |

|                     | Fout Cingle Cide Dand Dhace Naise | LMK03001C<br>f <sub>Fout</sub> = 1570 MHz <sup>(1)</sup> | 10 kHz Offset  |     | -89.6  |     |        |

|                     |                                   |                                                          | 100 kHz Offset |     | -115.2 |     |        |

|                     |                                   |                                                          | 1 MHz Offset   |     | -136.5 |     |        |

| <b>(4)</b>          |                                   |                                                          | 10 MHz Offset  |     | -156.0 |     |        |

| (f) <sub>Fout</sub> | Fout Single Side Band Phase Noise |                                                          | 10 kHz Offset  |     | -91.6  |     |        |

|                     |                                   | LMK03001C<br>f <sub>Fout</sub> = 1470 MHz <sup>(1)</sup> | 100 kHz Offset |     | -116.0 |     |        |

|                     |                                   |                                                          | 1 MHz Offset   |     | -137.9 |     |        |

|                     |                                   |                                                          | 10 MHz Offset  |     | -156.2 |     |        |

|                     |                                   |                                                          | 10 kHz Offset  |     | -83    |     |        |

|                     |                                   | LMK03033C                                                | 100 kHz Offset |     | -109   |     |        |

|                     |                                   | $f_{Fout} = 2160 \text{ MHz}^{(1)}$                      | 1 MHz Offset   |     | -131   |     |        |

|                     |                                   |                                                          | 10 MHz Offset  |     | -152   |     |        |

|                     |                                   |                                                          | 10 kHz Offset  |     | -86    |     |        |

|                     |                                   | LMK03033C                                                | 100 kHz Offset |     | -111   |     |        |

|                     |                                   | $f_{Fout} = 1843 \text{ MHz}^{(1)}$                      | 1 MHz Offset   |     | -134   |     |        |

|                     |                                   |                                                          | 10 MHz Offset  |     | -153   |     |        |

<sup>(1)</sup> VCO phase noise is measured assuming the VCO is the dominant noise source due to a 75 Hz loop bandwidth. Over frequency, the phase noise typically varies by 1 to 2 dB, with the worst case performance typically occurring at the highest frequency. Over temperature, the phase noise typically varies by 1 to 2 dB, assuming the device is not reprogrammed. Reprogramming R15 will run the frequency calibration routine for optimum phase noise.

$(3.15 \text{ V} \leq \text{Vcc} \leq 3.45 \text{ V}, -40 \text{ °C} \leq \text{T}_{\text{A}} \leq 85 \text{ °C}, \text{ Differential Inputs/Outputs; Vboost=0; except as specified. Typical values represent most likely parametric norms at Vcc = 3.3 V, T<sub>A</sub> = 25 °C, and at the Recommended Operation Conditions at the time of product characterization and are not ensured).$

| Symbol                             | Parameter                                                              | Condit                                                   | Conditions                                                   |               |               | Max   | Units |

|------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------|---------------|---------------|-------|-------|

|                                    | Clock Distribution S                                                   | Section (1) (2) - LVDS CI                                | ock Outputs                                                  | !             |               | '     |       |

|                                    |                                                                        | R <sub>L</sub> = 100 Ω<br>Distribution Path =            |                                                              |               | 20            |       |       |

| Jitter <sub>ADD</sub> Additive RMS | Additive RMS Jitter (1)                                                | 765 MHz<br>Bandwidth =<br>12 kHz to 20 MHz               | CLKoutX_MUX<br>= Divided (no<br>delay)<br>CLKoutX_DIV<br>= 4 |               | 75            |       | fs    |

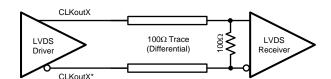

| t <sub>SKEW</sub>                  | CLKoutX to CLKoutY (3)                                                 | Equal loading and ic configuration $R_L = 100 \Omega$    | lentical clock                                               | -30           | ±4            | 30    | ps    |

| V <sub>OD</sub>                    | Differential Output Voltage                                            | $R_L = 100 \Omega$                                       |                                                              | 250           | 350           | 450   | mV    |

| ΔV <sub>OD</sub>                   | Change in magnitude of V <sub>OD</sub> for complementary output states | R <sub>L</sub> = 100 Ω                                   |                                                              | -50           |               | 50    | mV    |

| V <sub>OS</sub>                    | Output Offset Voltage                                                  | $R_L = 100 \Omega$                                       |                                                              | 1.070         | 1.25          | 1.370 | V     |

| $\Delta V_{OS}$                    | Change in magnitude of V <sub>OS</sub> for complementary output states | $R_L = 100 \Omega$                                       |                                                              | -35           |               | 35    | mV    |

| I <sub>SA</sub><br>I <sub>SB</sub> | Clock Output Short Circuit Current single-ended                        | Single-ended output                                      | s shorted to GND                                             | -24           |               | 24    | mA    |

| I <sub>SAB</sub>                   | Clock Output Short Circuit Current differential                        | Complementary outp                                       | outs tied together                                           | -12           |               | 12    | mA    |

|                                    | Clock Distribution Se                                                  | ection <sup>(1) (2)</sup> - LVPECL C                     | Clock Outputs                                                |               |               |       |       |

|                                    |                                                                        | $R_L = 100 \Omega$                                       | CLKoutX_MUX<br>= Bypass (no<br>divide or delay)              |               | 20            |       |       |

| Jitter <sub>ADD</sub>              | Additive RMS Jitter (1)                                                | Distribution Path = 765 MHz Bandwidth = 12 kHz to 20 MHz | CLKoutX_MUX<br>= Divided (no<br>delay)<br>CLKoutX_DIV<br>= 4 |               | 75            |       | fs    |

| t <sub>SKEW</sub>                  | CLKoutX to CLKoutY (3)                                                 | Equal loading and ic configuration Termination = 50 Ω    |                                                              | -30           | ±3            | 30    | ps    |

| V <sub>OH</sub>                    | Output High Voltage                                                    | Termination = 50 Ω                                       | to Vcc - 2 V                                                 |               | Vcc -<br>0.98 |       | V     |

| V <sub>OL</sub>                    | Output Low Voltage                                                     | 757777740077 = 50 12                                     |                                                              |               | Vcc -<br>1.8  |       | V     |

| V <sub>OD</sub>                    | Differential Output Voltage                                            | $R_L = 100 \Omega$                                       |                                                              |               | 810           | 965   | mV    |

|                                    | T                                                                      | I LVTTL Interfaces (4)                                   |                                                              | 1             |               |       |       |

| V <sub>IH</sub>                    | High-Level Input Voltage                                               |                                                          |                                                              | 2.0           |               | Vcc   | V     |

| V <sub>IL</sub>                    | Low-Level Input Voltage                                                |                                                          |                                                              |               |               | 8.0   | V     |

| I <sub>IH</sub>                    | High-Level Input Current                                               | V <sub>IH</sub> = Vcc                                    |                                                              | -5.0<br>-40.0 |               | 5.0   | μA    |

| I <sub>IL</sub>                    | Low-Level Input Current                                                | $V_{IL} = 0$                                             | V <sub>IL</sub> = 0                                          |               |               | 5.0   | μΑ    |

| V <sub>OH</sub>                    | High-Level Output Voltage                                              | I <sub>OH</sub> = +500 μA                                |                                                              | Vcc -<br>0.4  |               |       | V     |

| $V_{OL}$                           | Low-Level Output Voltage                                               | $I_{OL} = -500  \mu A$                                   |                                                              |               |               | 0.4   | V     |

<sup>(1)</sup> The Clock Distribution Section includes all parts of the device except the PLL and VCO sections. Typical Additive Jitter specifications apply to the clock distribution section only and this adds in an RMS fashion to the shaped jitter of the PLL and the VCO.

<sup>(2)</sup> For CLKout frequencies above 1 GHz, the delay should be limited to one half of a period. For 1 GHz and below, the maximum delay can be used.

<sup>(3)</sup> Specification is ensured by characterization and is not tested in production.

<sup>(4)</sup> Applies to GOE, LD, and SYNC\*.

$(3.15 \text{ V} \leq \text{Vcc} \leq 3.45 \text{ V}, -40 \text{ °C} \leq \text{T}_{A} \leq 85 \text{ °C}, \text{ Differential Inputs/Outputs; Vboost=0; except as specified. Typical values represent most likely parametric norms at Vcc = 3.3 V, T<sub>A</sub> = 25 °C, and at the Recommended Operation Conditions at the time of product characterization and are not ensured).$

| Symbol           | Parameter                   | Conditions                 | Min  | Тур | Max | Units |

|------------------|-----------------------------|----------------------------|------|-----|-----|-------|

|                  | Digital                     | I MICROWIRE Interfaces (1) |      | !   |     |       |

| V <sub>IH</sub>  | High-Level Input Voltage    |                            | 1.6  |     | Vcc | V     |

| V <sub>IL</sub>  | Low-Level Input Voltage     |                            |      |     | 0.4 | V     |

| I <sub>IH</sub>  | High-Level Input Current    | V <sub>IH</sub> = Vcc      | -5.0 |     | 5.0 | μΑ    |

| I <sub>IL</sub>  | Low-Level Input Current     | V <sub>IL</sub> = 0        | -5.0 |     | 5.0 | μΑ    |

|                  | •                           | MICROWIRE Timing           | •    |     |     | •     |

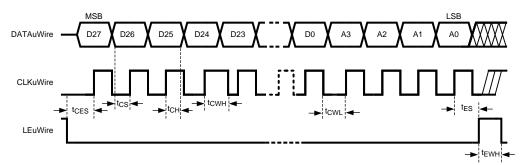

| t <sub>CS</sub>  | Data to Clock Set Up Time   | See Data Input Timing      | 25   |     |     | ns    |

| t <sub>CH</sub>  | Data to Clock Hold Time     | See Data Input Timing      | 8    |     |     | ns    |

| t <sub>CWH</sub> | Clock Pulse Width High      | See Data Input Timing      | 25   |     |     | ns    |

| t <sub>CWL</sub> | Clock Pulse Width Low       | See Data Input Timing      | 25   |     |     | ns    |

| t <sub>ES</sub>  | Clock to Enable Set Up Time | See Data Input Timing      | 25   |     |     | ns    |

| t <sub>CES</sub> | Enable to Clock Set Up Time | See Data Input Timing      | 25   |     |     | ns    |

| t <sub>EWH</sub> | Enable Pulse Width High     | See Data Input Timing      | 25   |     |     | ns    |

<sup>(1)</sup> Applies to CLKuWire, DATAuWire, and LEuWire.

### 3.5 Serial Data Timing Diagram

Data bits set on the DATAuWire signal are clocked into a shift register, MSB first, on each rising edge of the CLKuWire signal. On the rising edge of the LEuWire signal, the data is sent from the shift register to the addressed register determined by the LSB bits. After the programming is complete the CLKuWire, DATAuWire, and LEuWire signals should be returned to a low state. It is recommended that the slew rate of CLKuWire, DATAuWire, and LEuWire should be at least 30 V/µs.

#### 4 Measurement Definitions

# 4.1 Charge Pump Current Specification Definitions

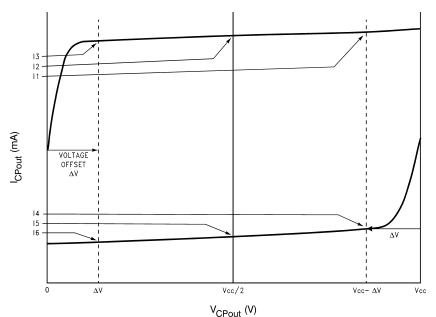

I1 = Charge Pump Sink Current at  $V_{CPout} = Vcc - \Delta V$

I2 = Charge Pump Sink Current at V<sub>CPout</sub> = Vcc/2

I3 = Charge Pump Sink Current at  $V_{CPout} = \Delta V$

I4 = Charge Pump Source Current at  $V_{CPout} = Vcc - \Delta V$

15 = Charge Pump Source Current at V<sub>CPout</sub> = Vcc/2

16 = Charge Pump Source Current at  $V_{CPout} = \Delta V$

$\Delta V = Voltage$  offset from the positive and negative supply rails. Defined to be 0.5 V for this device.

# 4.1.1 Charge Pump Output Current Magnitude Variation vs. Charge Pump Output Voltage

$$I_{CPout} Vs V_{CPout} = \frac{|I1| - |I3|}{|I1| + |I3|} \times 100\%$$

$$= \frac{|I4| - |I6|}{|I4| + |I6|} \times 100\%$$

### 4.1.2 Charge Pump Sink Current vs. Charge Pump Output Source Current Mismatch

$$I_{CPout}$$

Sink Vs  $I_{CPout}$  Source =

$$\frac{||2| - ||5||}{||2| + ||5||} \times 100\%$$

### 4.1.3 Charge Pump Output Current Magnitude Variation vs. Temperature

$$I_{CPout} \text{ Vs } T_{A} = \frac{|I_{2}||_{T_{A}} - |I_{2}||_{T_{A} = 25^{\circ}C}}{|I_{2}||_{T_{A} = 25^{\circ}C}} \times 100\%$$

$$= \frac{|I_{S}||_{T_{A}} - |I_{S}||_{T_{A} = 25^{\circ}C}}{|I_{S}||_{T_{A} = 25^{\circ}C}} \times 100\%$$

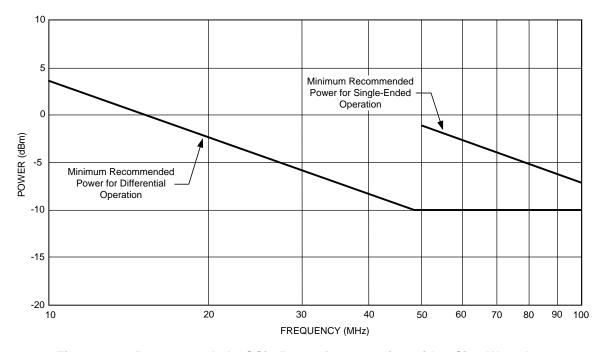

# 5 Typical Performance Characteristics

#### NOTE

These plots show performance at frequencies beyond what the part is ensured to operate at to give the user an idea of the capabilities of the part, but they do not imply any sort of ensured specification.

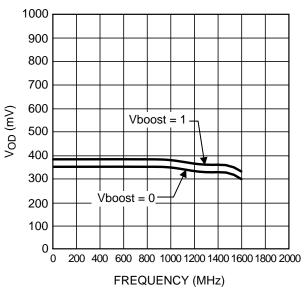

Figure 5-1. LVDS Differential Output Voltage (VoD)

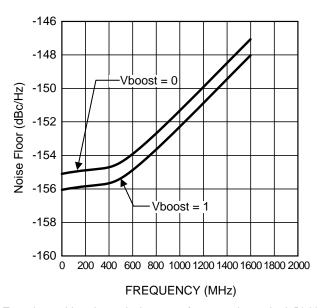

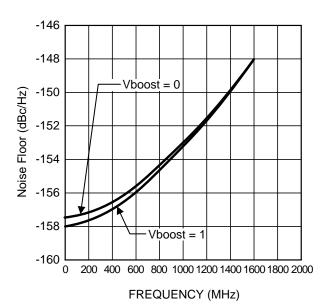

To estimate this noise, only the output frequency is required. Divide value and input frequency are not integral.

Figure 5-3. LVDS Output Buffer Noise Floor

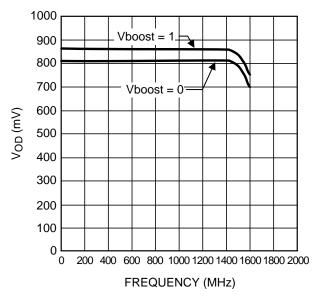

Figure 5-2. LVPECL Differential Output Voltage (V<sub>OD</sub>)

To estimate this noise, only the output frequency is required. Divide value and input frequency are not integral.

Figure 5-4. LVPECL Output Buffer Noise Floor

LMK03033C

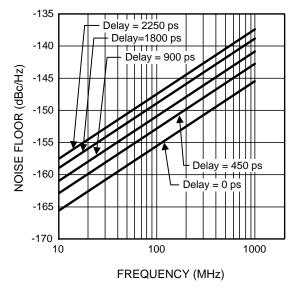

To estimate this noise, only the output frequency is required. Divide value and input frequency are not integral.

The noise of the delay block is independent of output type and only applies if the delay is enabled. The noise floor due to the distribution section accounting for the delay nise can be calculated as: Total Output Noise = 10 × log(10<sup>Output Buffer Noise/10</sup> + 10<sup>Delay Noise Floor/10</sup>).

Figure 5-5. Delay Noise Floor (Adds to Output Noise Floor)

### **6 Functional Description**

The LMK03000 family of precision clock conditioners combine the functions of jitter cleaning/reconditioning, multiplication, and distribution of a reference clock. The devices integrate a Voltage Controlled Oscillator (VCO), a high performance Integer-N Phase Locked Loop (PLL), a partially integrated loop filter, three LVDS, and five LVPECL clock output distribution blocks.

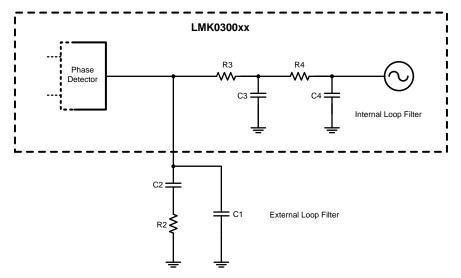

The devices include internal 3rd and 4th order poles to simplify loop filter design and improve spurious performance. The 1st and 2nd order poles are off-chip to provide flexibility for the design of various loop filter bandwidths.

The LMK03000 family has multiple options for VCO frequencies. The VCO output is optionally accessible on the Fout port. Internally, the VCO output goes through an VCO Divider to feed the various clock distribution blocks.

Each clock distribution block includes a programmable divider, a phase synchronization circuit, a programmable delay, a clock output mux, and an LVDS or LVPECL output buffer. This allows multiple integer-related and phase-adjusted copies of the reference to be distributed to eight system components.

The clock conditioners come in a 48-pin WQFN package and are footprint compatible with other clocking devices in the same family.

#### 6.1 BIAS PIN

To properly use the device, bypass Bias (pin 36) with a low leakage 1 µF capacitor connected to Vcc. This is important for low noise performance.

#### 6.2 LDO BYPASS

To properly use the device, bypass LDObyp1 (pin 9) with a 10  $\mu$ F capacitor and LDObyp2 (pin 10) with a 0.1  $\mu$ F capacitor.

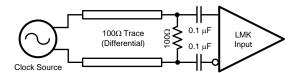

### 6.3 OSCILLATOR INPUT PORT (OSCin, OSCin\*)

The purpose of OSCin is to provide the PLL with a reference signal. Due to an internal DC bias the OSCin port should be AC coupled, refer to the Section 8.1 in the Section 8 section. The OSCin port may be driven single-endedly by AC grounding OSCin\* with a 0.1 µF capacitor.

#### 6.4 LOW NOISE, FULLY INTEGRATED VCO

The LMK03000 family of devices contain a fully integrated VCO. In order for proper operation the VCO uses a frequency calibration algorithm. The frequency calibration algorithm is activated any time that the R15 register is programmed. Once R15 is programmed the temperature may not drift more than the maximum allowable drift for continuous lock,  $\Delta T_{CL}$ , or else the VCO is not ensured to stay in lock.

For the frequency calibration algorithm to work properly OSCin must be driven by a valid signal when R15 is programmed.

#### 6.5 CLKout DELAYS

Each individual clock output includes a delay adjustment. Clock output delay registers (CLKoutX\_DLY) support a 150 ps step size and range from 0 to 2250 ps of total delay.

#### 6.6 LVDS/LVPECL OUTPUTS

By default all the clock outputs are disabled until programmed.

Each LVDS or LVPECL output may be disabled individually by programming the CLKoutX\_EN bits. All the outputs may be disabled simultaneously by pulling the GOE pin low or programming EN\_CLKout\_Global to 0.

The duty cycle of the LVDS and LVPECL clock outputs are shown in the table below.

| VCO_DIV    | CLKoutX_MUX                     | Duty Cycle |

|------------|---------------------------------|------------|

| Any        | Divided, or Divided and Delayed | 50%        |

| 2, 4, 6, 8 | Any                             | 50%        |

| 3          | Bypassed, or Delayed            | 33%        |

| 5          | Bypassed, or Delayed            | 40%        |

| 7          | Bypassed, or Delayed            | 43%        |

#### 6.7 GLOBAL CLOCK OUTPUT SYNCHRONIZATION

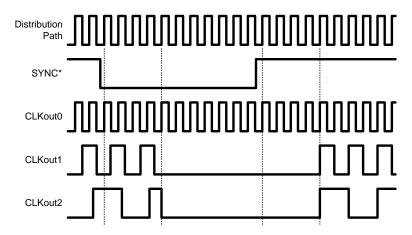

The SYNC\* pin synchronizes the clock outputs. When the SYNC\* pin is held in a logic low state, the divided outputs are also held in a logic low state. The bypassed outputs will continue to operate normally. Shortly after the SYNC\* pin goes high, the divided clock outputs are activated and will all transition to a high state simultaneously. All the outputs, divided and bypassed, will now be synchronized. Clocks in the bypassed state are not affected by SYNC\* and are always synchronized with the divided outputs.

The SYNC\* pin must be held low for greater than one clock cycle of the output of the VCO Divider, also known as the distribution path. Once this low event has been registered, the outputs will not reflect the low state for four more cycles. This means that the outputs will be low on the fifth rising edge of the distribution path. Similarly once the SYNC\* pin becomes high, the outputs will not simultaneously transition high until four more distribution path clock cycles have passed, which is the fifth rising edge of the distribution path. See the timing diagram in Figure 6-1 for further detail. The clocks are programmed as CLKout0\_MUX = Bypassed, CLKout1\_MUX = Divided, CLKout1\_DIV = 2, CLKout2\_MUX = Divided, and CLKout2\_DIV = 4. To synchronize the outputs, after the low SYNC\* event has been registered, it is not required to wait for the outputs to go low before SYNC\* is set high.

Figure 6-1. SYNC\* Timing Diagram

The SYNC\* pin provides an internal pull-up resistor as shown on the functional block diagram. If the SYNC\* pin is not terminated externally the clock outputs will operate normally. If the SYNC\* function is not used, clock output synchronization is not ensured.

#### 6.8 CLKout OUTPUT STATES

Each clock output may be individually enabled with the CLKoutX\_EN bits. Each individual output enable control bit is gated with the Global Output Enable input pin (GOE) and the Global Output Enable bit (EN\_CLKout\_Global).

All clock outputs can be disabled simultaneously if the GOE pin is pulled low by an external signal or EN CLKout Global is set to 0.

| CLKoutX_EN bit | EN_CLKout_Global bit | GOE pin           | CLKoutX Output State |

|----------------|----------------------|-------------------|----------------------|

| 1              | 1                    | Low               | Low                  |

| Don't care     | 0                    | Don't care        | Off                  |

| 0              | Don't care           | Don't care        | Off                  |

| 1              | 1                    | High / No Connect | Enabled              |

When an LVDS output is in the Off state, the outputs are at a voltage of approximately 1.5 volts. When an LVPECL output is in the Off state, the outputs are at a voltage of approximately 1 volt.

#### 6.9 GLOBAL OUTPUT ENABLE AND LOCK DETECT

The GOE pin provides an internal pull-up resistor as shown on the functional block diagram. If it is not terminated externally, the clock output states are determined by the Clock Output Enable bits (CLKoutX EN) and the EN CLKout Global bit.

By programming the PLL\_MUX register to Digital Lock Detect Active High, the Lock Detect (LD) pin can be connected to the GOE pin in which case all outputs are set low automatically if the synthesizer is not locked.

#### 6.10 POWER ON RESET

When supply voltage to the device increases monotonically from ground to Vcc, the power on reset circuit sets all registers to their default values, see the Section 7 section for more information on default register values. Voltage should be applied to all Vcc pins simultaneously.

#### 6.11 DIGITAL LOCK DETECT

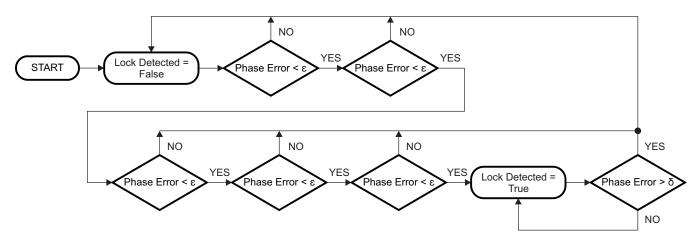

The PLL digital lock detect circuitry compares the difference between the phase of the inputs of the phase detector to a RC generated delay of  $\epsilon$ . To indicate a locked state the phase error must be less than the  $\epsilon$  RC delay for 5 consecutive reference cycles. Once in lock, the RC delay is changed to approximately  $\delta$ . To indicate an out of lock state, the phase error must become greater  $\delta$ . The values of  $\epsilon$  and  $\delta$  are shown in the table below:

| ε     | δ     |

|-------|-------|

| 10 ns | 20 ns |

To utilize the digital lock detect feature, PLL\_MUX must be programmed for "Digital Lock Detect (Active High)" or "Digital Lock Detect (Active Low)." When one of these modes is programmed the state of the LD pin will be set high or low as determined by the description above as shown in Figure 6-2.

When the device is in power down mode and the LD pin is programmed for a digital lock detect function, LD will show a "no lock detected" condition which is low or high given active high or active low circuitry respectively.

The accuracy of this circuit degrades at higher comparison frequencies. To compensate for this, the DIV4 word should be set to one if the comparison frequency exceeds 20 MHz. The function of this word is to divide the comparison frequency presented to the lock detect circuit by 4.

Figure 6-2. Digital Lock Detect Flowchart

### 7 General Programming Information

The LMK03000 family of devices are programmed using several 32-bit registers which control the device's operation. The registers consist of a data field and an address field. The last 4 register bits, ADDR[3:0] form the address field. The remaining 28 bits form the data field DATA[27:0].

During programming, LEuWire is low and serial data is clocked in on the rising edge of CLKuWire (MSB first). When LE goes high, data is transferred to the register bank selected by the address field. Only registers R0 to R7, R11, and R13 to R15 need to be programmed for proper device operation.

For the frequency calibration algorithm to work properly OSCin must be driven by a valid signal when R15 is programmed. Any changes to the PLL R divider or OSCin require R15 to be programmed again to activate the frequency calibration routine.

#### 7.1 RECOMMENDED PROGRAMMING SEQUENCE

The recommended programming sequence involves programming R0 with the reset bit set (RESET = 1) to ensure the device is in a default state. It is not necessary to program R0 again, but if R0 is programmed again, the reset bit is programmed clear (RESET = 0). Registers are programmed in order with R15 being the last register programmed. An example programming sequence is shown below.

- Program R0 with the reset bit set (RESET = 1). This ensures the device is in a default state. When the reset bit is set in R0, the other R0 bits are ignored.

- If R0 is programmed again, the reset bit is programmed clear (RESET = 0).

- Program R0 to R7 as necessary with desired clocks with appropriate enable, mux, divider, and delay settings.

- Program R8 for optimum phase noise performance.

- Program R9 with Vboost setting if necessary. Optional, only needed to set Vboost = 1.

- Program R11 with DIV4 setting if necessary.

- Program R13 with oscillator input frequency and internal loop filter values

- Program R14 with Fout enable bit, global clock output bit, power down setting, PLL mux setting, and PLL R divider.

- Program R15 with PLL charge pump gain, VCO divider, and PLL N divider. Also starts frequency calibration routine.

www.ti.com

### **Table 7-1. REGISTER MAP**

|          | I     | ı  |    |    |    |    |    |    |    |    |    |    |      |                          |            |    |    | 1  | 1           | 1               |    |   |   | I  |              |              | 1  | 1  |    |    |    |

|----------|-------|----|----|----|----|----|----|----|----|----|----|----|------|--------------------------|------------|----|----|----|-------------|-----------------|----|---|---|----|--------------|--------------|----|----|----|----|----|

| Register | 31    | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19   | 18 17                    | 7 16       | 15 | 14 | 13 | 12          | 11              | 10 | 9 | 8 | 7  | 6            | 5            | 4  | 3  | 2  | 1  | 0  |

|          |       |    | I  | ı  | 1  |    |    |    |    |    |    |    | Data | [27:0]                   |            |    | 1  |    | 1           |                 | 1  |   |   |    | I            |              |    | А3 | A2 | A1 | A0 |

| R0       | RESET | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | CLKout0<br>_MUX<br>[1:0] | CLKout0_EN |    |    |    | CLKoi<br>[7 | ut0_DI\<br>7:0] | ,  |   |   | CI | -Kout        | t0_DL<br>:0] | LY | 0  | 0  | 0  | 0  |

| R1       | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | CLKout1<br>_MUX<br>[1:0] | CLKout1_EN |    |    |    | CLKoi<br>[7 | ut1_DIV<br>7:0] | ,  |   |   | CI | _Kout<br>[3: | t1_DL<br>:0] | LY | 0  | 0  | 0  | 1  |

| R2       | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | CLKout2<br>_MUX<br>[1:0] | CLKout2_EN |    |    |    | CLKoi<br>[7 | ut2_DIV<br>7:0] | ,  |   |   | CI | -Kout        | t2_DL<br>:0] | LY | 0  | 0  | 1  | 0  |

| R3       | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | CLKout3<br>_MUX<br>[1:0] | CLKout3_EN |    |    |    |             | ut3_DI\<br>7:0] | ,  |   |   | CI | _Kout<br>[3: | :3_DL        | LY | 0  | 0  | 1  | 1  |

| R4       | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | CLKout4<br>_MUX<br>[1:0] | CLKout4_EN |    |    |    | CLKoi<br>[7 | ut4_DIV<br>7:0] | ,  |   |   | CI | _Kout<br>[3: | t4_Dl<br>:0] | LY | 0  | 1  | 0  | 0  |

| R5       | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | CLKout5<br>_MUX<br>[1:0] | CLKout5_EN |    |    |    |             | ut5_DIV<br>7:0] | ,  |   |   | Cl | _Kout        | t5_DL<br>:0] | LY | 0  | 1  | 0  | 1  |

| R6       | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | CLKout6<br>_MUX<br>[1:0] | CLKout6_EN |    |    |    | CLKoi<br>[7 | ut6_DI\<br>7:0] | ,  |   |   | Cl | _Kout<br>[3: | t6_Dl<br>:0] | LY | 0  | 1  | 1  | 0  |

| R7       | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | CLKout7<br>_MUX<br>[1:0] | CLKout7_EN |    |    |    | CLKoi<br>[7 | ut7_DIV<br>7:0] | ,  |   |   | Cl | -Kout        | t7_DL<br>:0] | LY | 0  | 1  | 1  | 1  |

| R8       | 0     | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0 0                      | 0          | 0  | 0  | 0  | 0           | 1               | 0  | 0 | 1 | 0  | 0            | 0            | 0  | 1  | 0  | 0  | 0  |

SNAS3810 - NOVEMBER 2006 - REVISED MARCH 2013

## **Table 7-1. REGISTER MAP (continued)**

| Register | 31                           | 30 | 29 | 28      | 27               | 26        | 25 | 24 | 23 | 22          | 21 | 20 | 19 | 18          | 17           | 16        | 15   | 14         | 13          | 12                     | 11 | 10 | 9                      | 8 | 7 | 6                 | 5    | 4 | 3 | 2 | 1 | 0 |

|----------|------------------------------|----|----|---------|------------------|-----------|----|----|----|-------------|----|----|----|-------------|--------------|-----------|------|------------|-------------|------------------------|----|----|------------------------|---|---|-------------------|------|---|---|---|---|---|

| R9       | 1                            | 0  | 1  | 0       | 0                | 0         | 0  | 0  | 0  | 0           | 0  | 0  | 0  | 0           | 1            | Vboost    | 0    | 0          | 1           | 0                      | 1  | 0  | 1                      | 0 | 0 | 0                 | 0    | 0 | 1 | 0 | 0 | 1 |

| R11      | 0                            | 0  | 0  | 0       | 0                | 0         | 0  | 0  | 1  | 0           | 0  | 0  | 0  | 0           | 1            | 0         | DIV4 | 0          | 0           | 0                      | 0  | 0  | 0                      | 0 | 0 | 0                 | 0    | 0 | 1 | 0 | 1 | 1 |

| R13      | 0                            | 0  | 0  | 0       | 0                | 0         | 1  | 0  | 1  | 0           |    |    |    | OSCin<br>[7 | _FREQ<br>:0] |           |      |            |             | VCO_<br>R4_LF<br>[2:0] |    |    | VCO_<br>R3_LF<br>[2:0] |   | ( | VC<br>C3_C<br>[3: | 4_LF | = | 1 | 1 | 0 | 1 |

| R14      | 0                            | 0  | 0  | EN_Fout | EN_CLKout_Global | POWERDOWN | 0  | 0  |    | PLL_<br>[3: |    |    |    |             |              |           |      | PLI<br>[11 | L_R<br>1:0] |                        |    |    |                        |   | 0 | 0                 | 0    | 0 | 1 | 1 | 1 | 0 |

| R15      | PLL_<br>CP_<br>GAIN<br>[1:0] | I  |    | VCO     | _DIV<br>:0]      |           |    |    |    |             |    |    |    |             | PLI<br>[17   | N<br>':0] |      |            |             |                        |    |    |                        |   | 0 | 0                 | 0    | 0 | 1 | 1 | 1 | 1 |

#### 7.2 REGISTER R0 to R7

Registers R0 through R7 control the eight clock outputs. Register R0 controls CLKout0, Register R1 controls CLKout1, and so on. There is one additional bit in register R0 called RESET. Aside from this, the functions of these bits are identical. The X in CLKoutX\_MUX, CLKoutX\_DIV, CLKoutX\_DLY, and CLKoutX\_EN denote the actual clock output which may be from 0 to 7.

Table 7-2. Default Register Settings after Power on Reset

| Bit Name         | Default<br>Bit Value | Bit State                  | Bit Description                       | Register | Bit<br>Location |

|------------------|----------------------|----------------------------|---------------------------------------|----------|-----------------|

| RESET            | 0                    | No reset, normal operation | Reset to power on defaults            | R0       | 31              |

| CLKoutX_MUX      | 0                    | Bypassed                   | CLKoutX mux mode                      |          | 18:17           |

| CLKoutX_EN       | 0                    | Disabled                   | CLKoutX enable                        | D0 to D7 | 16              |

| CLKoutX_DIV      | 1                    | Divide by 2                | CLKoutX clock divide                  | R0 to R7 | 15:8            |

| CLKoutX_DLY      | 0                    | 0 ps                       | CLKoutX clock delay                   |          | 7:4             |

| Vboost           | 0                    | Normal Mode                | Output Power Control                  | R9       | 16              |

| DIV4             | 0                    | PDF ≤ 20 MHz               | Phase Detector Frequency              | R11      | 15              |

| OSCin_FREQ       | 10                   | 10 MHz OSCin               | OSCin Frequency in MHz                |          | 21:14           |

| VCO_R4_LF        | 0                    | Low (~200 Ω)               | R4 internal loop filter values        | R13      | 13:11           |

| VCO_R3_LF        | 0                    | Low (~600 Ω)               | R3 internal loop filter values        | K13      | 10:8            |

| VCO_C3_C4_LF     | 0                    | C3 = 0 pF, C4 = 10 pF      | C3 and C4 internal loop filter values |          | 7:4             |

| EN_Fout          | 0                    | Fout disabled              | Fout enable                           |          | 28              |

| EN_CLKout_Global | 1                    | Normal - CLKouts normal    | Global clock output enable            |          | 27              |

| POWERDOWN        | 0                    | Normal - Device active     | Device power down                     | R14      | 26              |

| PLL_MUX          | 0                    | Disabled                   | Multiplexer control for LD pin        |          | 23:20           |

| PLL_R            | 10                   | R divider = 10             | PLL R divide value                    |          | 19:8            |

| PLL_CP_GAIN      | 0                    | 100 μΑ                     | Charge pump current                   |          | 31:30           |

| VCO_DIV          | 2                    | Divide by 2                | VCO divide value                      | R15      | 29:26           |

| PLL_N 760        |                      | N divider = 760            | PLL N divide value                    |          | 25:8            |

### 7.2.1 RESET bit -- R0 only

This bit is only in register R0. The use of this bit is optional and it should be set to '0' if not used. Setting this bit to a '1' forces all registers to their power on reset condition and therefore automatically clears this bit. If this bit is set, all other R0 bits are ignored and R0 needs to be programmed again if used with its proper values and RESET = 0.

### 7.2.2 CLKoutX\_MUX[1:0] -- Clock Output Multiplexers

These bits control the Clock Output Multiplexer for each clock output. Changing between the different modes changes the blocks in the signal path and therefore incurs a delay relative to the bypass mode. The different MUX modes and associated delays are listed below.

| CLKoutX_MUX[1:0] | Mode                | Added Delay Relative to Bypass Mode             |

|------------------|---------------------|-------------------------------------------------|

| 0                | Bypassed (default)  | 0 ps                                            |

| 1                | Divided             | 100 ps                                          |

| 2                | Delayed             | 400 ps<br>(In addition to the programmed delay) |

| 3                | Divided and Delayed | 500 ps<br>(In addition to the programmed delay) |

### 7.2.3 CLKoutX\_DIV[7:0] -- Clock Output Dividers

These bits control the clock output divider value. In order for these dividers to be active, the respective CLKoutX\_MUX bit must be set to either "Divided" or "Divided and Delayed" mode. After all the dividers are programed, the SYNC\* pin must be used to ensure that all edges of the clock outputs are aligned. The Clock Output Dividers follow the VCO Divider so the final clock divide for an output is VCO Divider × Clock Output Divider. By adding the divider block to the output path a fixed delay of approximately 100 ps is incurred.

The actual Clock Output Divide value is twice the binary value programmed as listed in the table below.

|   |   |   | CLKoutX | _DIV[7:0] |   |   |   | Clock Output Divider value |

|---|---|---|---------|-----------|---|---|---|----------------------------|

| 0 | 0 | 0 | 0       | 0         | 0 | 0 | 0 | Invalid                    |

| 0 | 0 | 0 | 0       | 0         | 0 | 0 | 1 | 2 (default)                |

| 0 | 0 | 0 | 0       | 0         | 0 | 1 | 0 | 4                          |

| 0 | 0 | 0 | 0       | 0         | 0 | 1 | 1 | 6                          |

| 0 | 0 | 0 | 0       | 0         | 1 | 0 | 0 | 8                          |

| 0 | 0 | 0 | 0       | 0         | 1 | 0 | 1 | 10                         |

|   |   |   |         |           |   |   |   |                            |

| 1 | 1 | 1 | 1       | 1         | 1 | 1 | 1 | 510                        |

#### 7.2.4 CLKoutX DLY[3:0] -- Clock Output Delays

These bits control the delay stages for each clock output. In order for these delays to be active, the respective CLKoutX\_MUX (See Section 7.2.2) bit must be set to either "Delayed" or "Divided and Delayed" mode. By adding the delay block to the output path a fixed delay of approximately 400 ps is incurred in addition to the delay shown in the table below.

| CLKoutX_DLY[3:0] | Delay (ps)  |

|------------------|-------------|

| 0                | 0 (default) |

| 1                | 150         |

| 2                | 300         |

| 3                | 450         |

| 4                | 600         |

| 5                | 750         |

| 6                | 900         |

| 7                | 1050        |

| 8                | 1200        |

| 9                | 1350        |

| 10               | 1500        |

| 11               | 1650        |

| 12               | 1800        |

| 13               | 1950        |

| 14               | 2100        |

| 15               | 2250        |

### 7.2.5 CLKoutX\_EN bit -- Clock Output Enables

These bits control whether an individual clock output is enabled or not. If the EN\_CLKout\_Global bit (See Section 7.7.4) is set to zero or if GOE pin is held low, all CLKoutX\_EN bit states will be ignored and all clock outputs will be disabled.

| CLKoutX_EN bit | Conditions                  | CLKoutX State      |

|----------------|-----------------------------|--------------------|

| 0              | EN_CLKout_Global bit = 1    | Disabled (default) |

| 1              | GOE pin = High / No Connect | Enabled            |

#### 7.3 REGISTER R8

The programming of register R8 provides optimum phase noise performance.

#### 7.4 REGISTER R9

The programming of register R9 is optional. If it is not programmed the bit Vboost will be defaulted to 0, which is the test condition for all electrical characteristics.

### 7.4.1 Vboost -- Voltage Boost

By enabling this bit, the voltage output levels for all clock outputs is increased. Also, the noise floor is improved

| Vboost | Typical LVDS Voltage Output (mV) | Typical LVPECL Voltage Output (mV) |

|--------|----------------------------------|------------------------------------|

| 0      | 350                              | 810                                |

| 1      | 390                              | 865                                |

#### 7.5 REGISTER R11

This register only has one bit and only needs to be programmed in the case that the phase detector frequency is greater than 20 MHz and digital lock detect is used. Otherwise, it is automatically defaulted to the correct values.

### 7.5.1 DIV4 -- High Phase Detector Frequencies and Lock Detect

This bit divides the frequency presented to the digital lock detect circuitry by 4. It is necessary to get a reliable output from the digital lock detect output in the case of a phase detector frequency frequency greater than 20 MHz.

| DIV4 | Digital Lock Detect Circuitry Mode                      |

|------|---------------------------------------------------------|

| 0    | Not divided Phase Detector Frequency ≤ 20 MHz (default) |

| 1    | Divided by 4 Phase Detector Frequency > 20 MHz          |

#### 7.6 REGISTER R13

#### 7.6.1 VCO\_C3\_C4\_LF[3:0] -- Value for Internal Loop Filter Capacitors C3 and C4

These bits control the capacitor values for C3 and C4 in the internal loop filter.

|                   | Loop Filter | Capacitors   |

|-------------------|-------------|--------------|

| VCO_C3_C4_LF[3:0] | C3 (pF)     | C4 (pF)      |

| 0                 | 0 (default) | 10 (default) |

| 1                 | 0           | 60           |

| 2                 | 50          | 10           |

| 3                 | 0           | 110          |

| 4                 | 50          | 110          |

| 5                 | 100         | 110          |

| 6                 | 0           | 160          |

| 7                 | 50          | 160          |

| 8                 | 100         | 10           |

| 9                 | 100         | 60           |

| 10                | 150         | 110          |

| 11                | 150         | 60           |

| 12 to 15          | Inv         | valid        |

### 7.6.2 VCO\_R3\_LF[2:0] -- Value for Internal Loop Filter Resistor R3

These bits control the R3 resistor value in the internal loop filter. The recommended setting for

VCO\_R3\_LF[2:0] = 0 for optimum phase noise and jitter.

| VCO_R3_LF[2:0] | R3 Value (kΩ)          |  |  |  |  |

|----------------|------------------------|--|--|--|--|

| 0              | Low (~600 Ω) (default) |  |  |  |  |

| 1              | 10                     |  |  |  |  |

| 2              | 20                     |  |  |  |  |

| 3              | 30                     |  |  |  |  |

| 4              | 40                     |  |  |  |  |

| 5 to 7         | Invalid                |  |  |  |  |

### 7.6.3 VCO\_R4\_LF[2:0] -- Value for Internal Loop Filter Resistor R4

These bits control the R4 resistor value in the internal loop filter. The recommended setting for

VCO R4 LF[2:0] = 0 for optimum phase noise and jitter.

| VCO_R4_LF[2:0] | R4 Value (kΩ)          |

|----------------|------------------------|

| 0              | Low (~200 Ω) (default) |

| 1              | 10                     |

| 2              | 20                     |

| 3              | 30                     |

| 4              | 40                     |

| 5 to 7         | Invalid                |

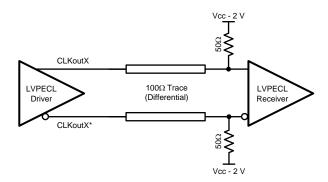

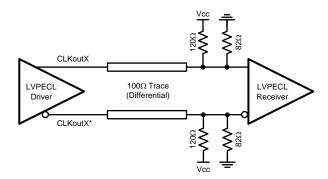

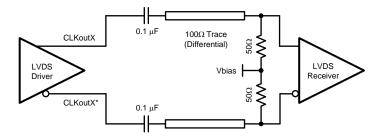

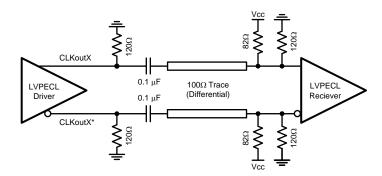

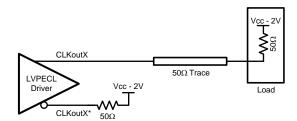

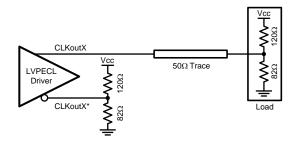

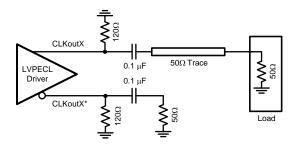

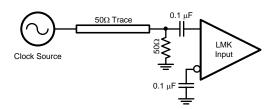

### 7.6.4 OSCin FREQ[7:0] -- Oscillator Input Calibration Adjustment