- Military Temperature Range - -55°C to 125°C

- 100-ns or 80-ns Instruction Cycle Times

- 544 Words of Programmable On-Chip Data

- 4K Words of On-Chip Program ROM

- 128K Words of Data/Program Space

- 16 Input and 16 Output Channels

- 16-Bit Parallel Interface

- **Directly Accessible External Data Memory** Space

- Global Data Memory Interface

- 16-Bit Instruction and Data Words

- 16 × 16-Bit Multiplier With a 32-Bit Product

- 32-Bit ALU and Accumulator

- Single-Cycle Multiply/Accumulate Instructions

- 0 to 16-Bit Scaling Shifter

- **Bit Manipulation and Logical Instructions**

- **Instruction Set Support for Floating-Point** Operations, Adaptive Filtering, and **Extended-Precision Arithmetic**

- **Block Moves for Data/Program** Management

- Repeat Instructions for Efficient Use of **Program Space**

- **Eight Auxiliary Registers and Dedicated** Arithmetic Unit for Indirect Addressing

- Serial Port for Direct Code Interface

- **Synchronization Input for Synchronous Multiprocessor Configurations**

- Wait States for Communication to Slow-Off-Chip Memories/Peripherals

- **On-Chip Timer for Control Operations**

- **Three External Maskable User Interrupts**

- Input Pin Polled by Software Branch Instruction

- 1.6-µm CMOS Technology

- **Programmable Output Pin for Signaling External Devices**

- Single 5-V Supply

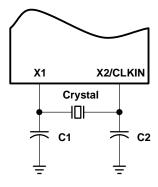

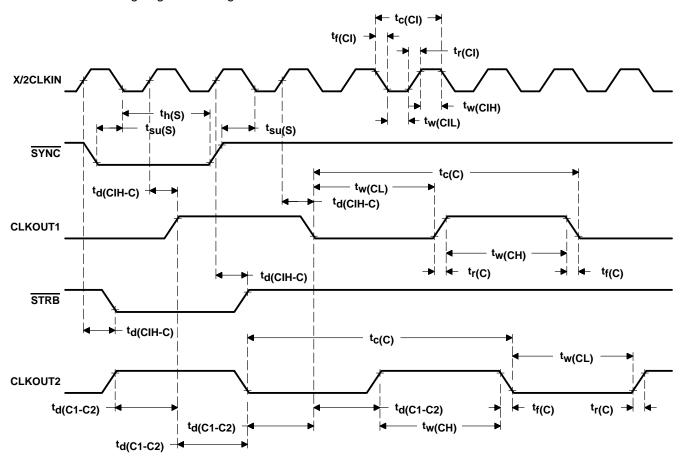

- **On-Chip Clock Generator**

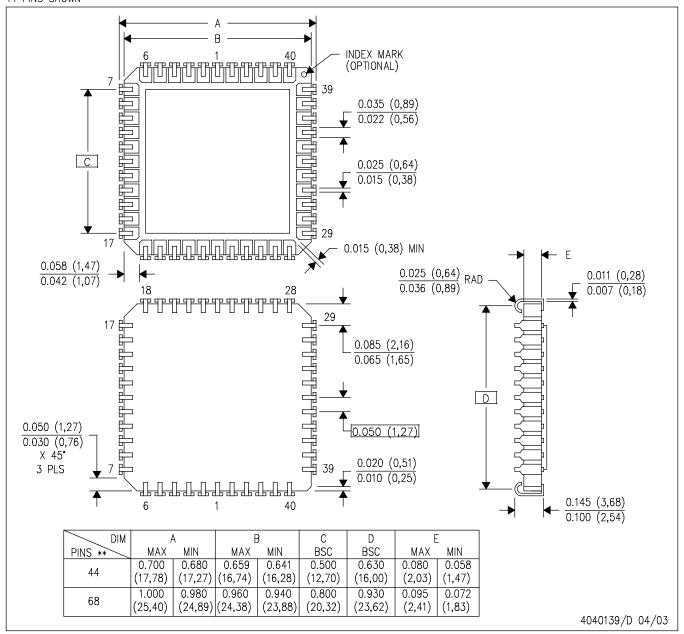

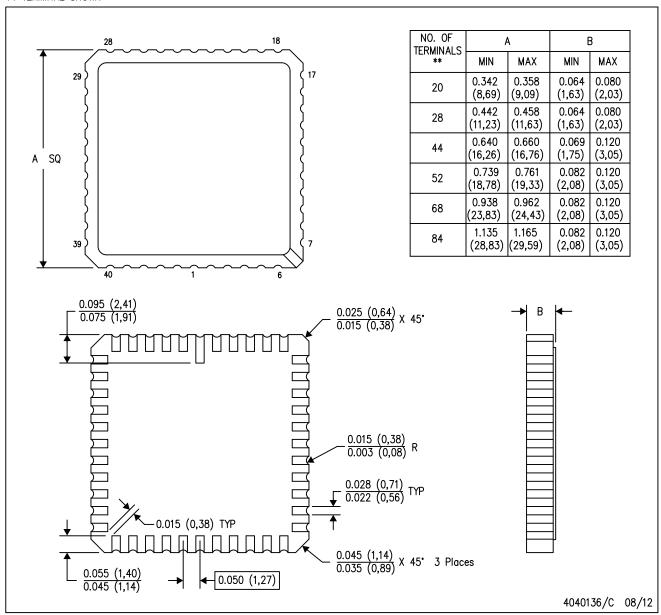

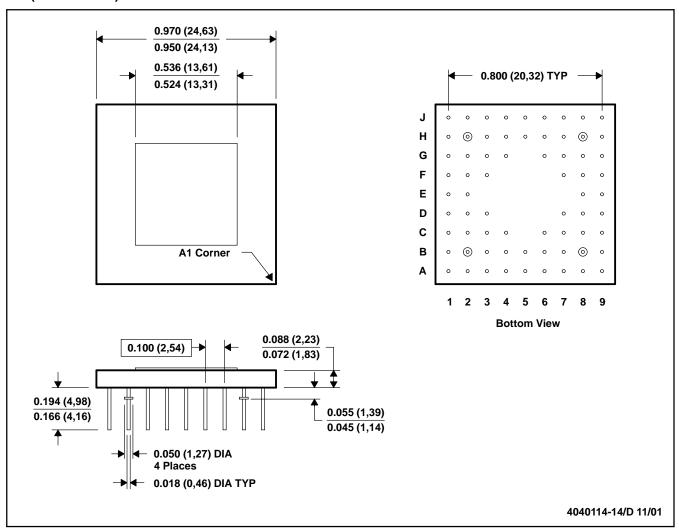

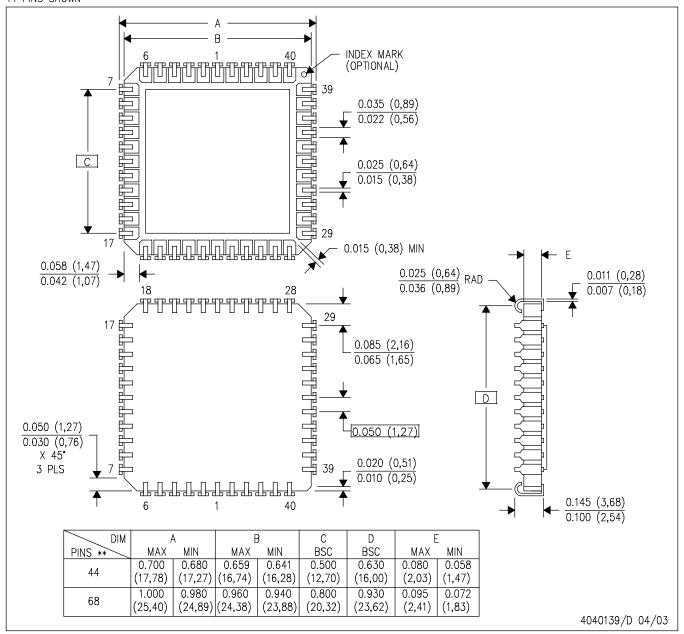

- Packaging:

- 68-Pin Leaded Ceramic Chip Carrier (FJ Suffix)

- 68-Pin Ceramic Grid Array (GB Suffix)

- 68-Pin Leadless Ceramic Chip Carrier (FD Suffix)

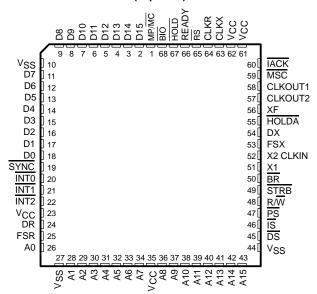

#### 68-Pin FJ and FD Packages (Top View)

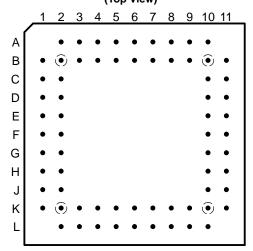

#### 68-Pin GB Package (Top View)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

### description

This data sheet provides design documentation for the SMJ320C25 and the SMJ320C25-50 digital signal processor (DSP) devices in the SMJ320™ family of VLSI digital signal processors and peripherals. The SMJ320 family supports a wide range of digital signal processing applications such as tactical communications, guidance, military modems, speech processing, spectrum analysis, audio processing, digital filtering, high-speed control, graphics, and other computation-intensive applications.

Differences between the SMJ320C25 and the SMJ320C25-50 are specifically identified, as in the following paragraph and in the parameter tables on pages 18 through 24 of this data sheet. When not specifically differentiated, the term SMJ320C25 is used to describe both devices.

The SMJ320C25 has a 100-ns instruction cycle time. The SMJ320C25-50 has an 80-ns instruction cycle time. With these fast instruction cycle times and their innovative memory configurations, these devices perform operations necessary for many real-time digital signal processing algorithms. Since most instructions require only one cycle, the SMJ320C25 is capable of executing 12.5 million instructions per second. On-chip data RAM of 544 16-bit words, on-chip program ROM of 4K words, direct addressing of up to 64K words of external data memory space and 64K words of external program memory space, and multiprocessor interface features for sharing global memory minimize unnecessary data transfers to take full advantage of the capabilities of the instruction set.

**FUNCTION FUNCTION FUNCTION FUNCTION FUNCTION** PIN PIN **FUNCTION** PIN PIN PIN PIN Α0 K1/26 A12 K8/40 D2 E1/16 D14 A5/3 INT2 H1/22 H2/23 Vcc Α1 K2/28 A13 L9/41 D3 D2/15 D15 B6/2 IS J11/46 L6/35 Vcc A2 L3/29 A14 K9/42 D4 D1/14 DR J1/24 MP/MC A6/1 Vss B1/10 C2/13 MSC A15 L10/43 D5 DS K10/45 K11/44 АЗ K3/30 C10/59 ٧ss PS L4/31 BI0 C1/12 DX E11/54 J10/47 L2/27 A4 B7/68 D6 ۷ss A5 K4/32 BR G11/50 D7 B2/11 FSR J2/25 READY B8/66 XF D11/56 RS A6 L5/33 CLKOUT1 C11/58 D8 A2/9 FSX F10/53 A8/65 X1 G10/51 HOLD R/W X2/CLKIN Α7 K5/34 CLKOUT2 D10/57 B3/8 A7/67 H11/48 F11/52 D9 A۸ K6/36 CLKR B9/64 D10 A3/7 HOLDA E10/55 STRB H10/49 SYNC Α9 L7/37 CLKX A9/63 D11 B4/6 IACK B11/60 F2/19 A10 K7/38 D0 F1/18 D12 A4/5 INT0 G1/20 Vcc A10/61 A11 18/39 D1 E2/17 D13 85/4 INT1 G2/21 Vcc B10/62

Table 1. PGA/CLCC/LCCC Pin Assignments

SMJ320 is a trademark of Texas Instruments Incorporated

## **Terminal Functions**

| SIGNALS   | I/O/Z† | DEFINITION                                                                                                                               |

|-----------|--------|------------------------------------------------------------------------------------------------------------------------------------------|

| VCC       | I      | 5-V supply pins                                                                                                                          |

| VSS       | I      | Ground pins                                                                                                                              |

| X1        | 0      | Output from internal oscillator for crystal                                                                                              |

| X2/CLKIN  | I      | Input to internal oscillator from crystal or external clock                                                                              |

| CLKOUT1   | 0      | Master clock output (crystal or CLKIN frequency/4)                                                                                       |

| CLKOUT2   | 0      | A second clock output signal                                                                                                             |

| D15-D0    | I/O/Z  | 16-bit data bus D15 (MSB) through D0 (LSB). Multiplexed between program, data, and I/0 spaces.                                           |

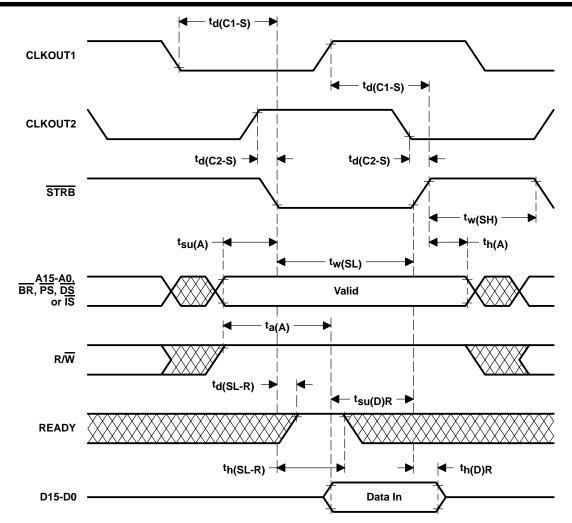

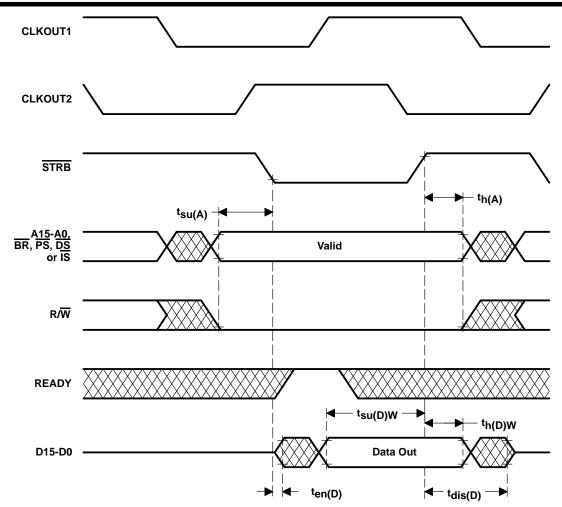

| A15-A0    | O/Z    | 16-bit address bus A15 (MSB) through A0 (LSB)                                                                                            |

| PS,DS,IS  | O/Z    | Program, data, and I/O space select signals                                                                                              |

| R/W       | O/Z    | Read / write signal                                                                                                                      |

| STRB      | O/Z    | Strobe signal                                                                                                                            |

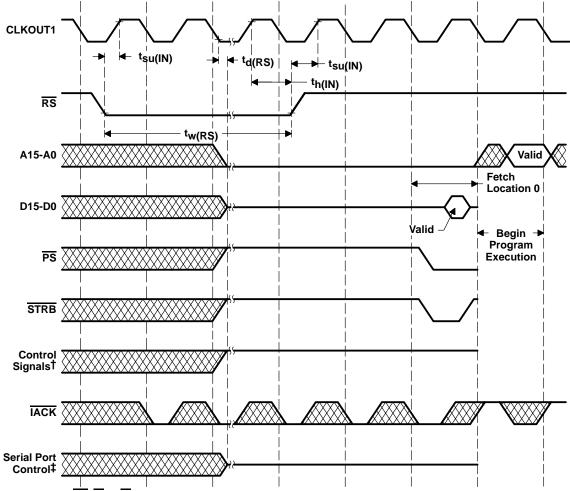

| RS        | I      | Reset input                                                                                                                              |

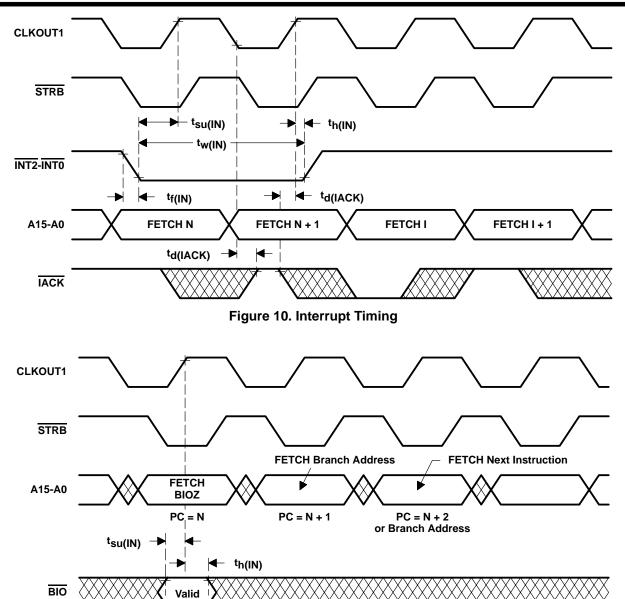

| INT2-INT0 | I      | External user interrupt inputs                                                                                                           |

| MP/MC     | I      | Microprocessor/microcomputer mode select pin                                                                                             |

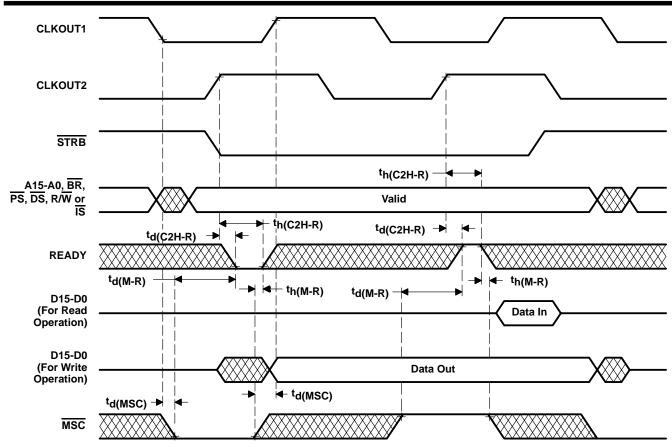

| MSC       | 0      | Microstate complete signal                                                                                                               |

| IACK      | 0      | Interrupt acknowledge signal                                                                                                             |

| READY     | 1      | Data ready input. Asserted by external logic when using slower devices to indicate that the current bus transaction is complete.         |

| BR        | 0      | Bus request signal. Asserted when the SMJ320C25 requires access to an external global data memory space.                                 |

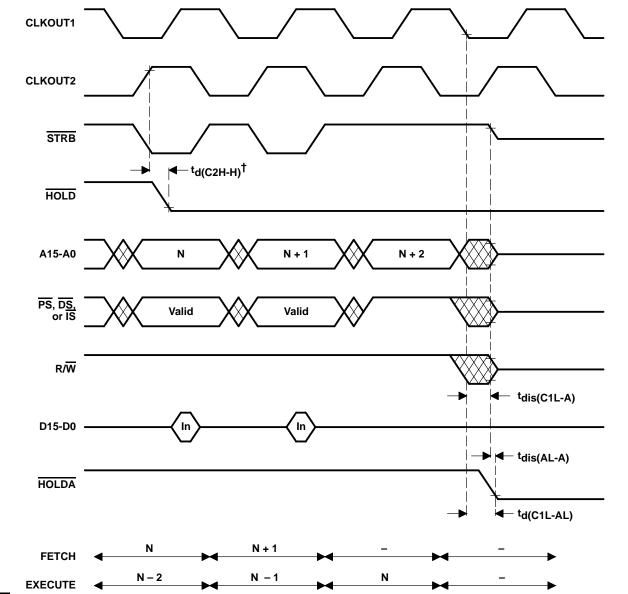

| XF        | 0      | External flag output (latched software-programmable signal)                                                                              |

| HOLD      | 1      | Hold input. When asserted, SMJ320C25 goes into an idle mode and places the data, address, and control lines in the high-impedance state. |

| HOLDA     | 0      | Hold acknowledge signal                                                                                                                  |

| SYNC      | I      | Synchronization input                                                                                                                    |

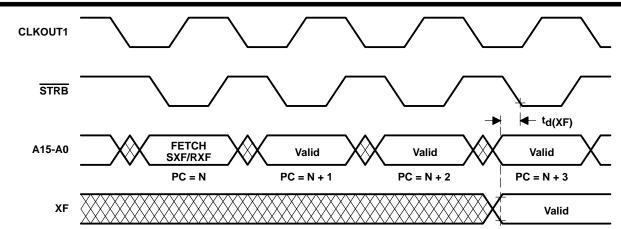

| BIO       | ļ      | Branch control input. Polled by BIOZ instruction                                                                                         |

| DR        | ļ      | Serial data receive input                                                                                                                |

| CLKR      | ı      | Clock for receive input for serial port                                                                                                  |

| FSR       | I      | Frame synchronization pulse for receive input                                                                                            |

| DX        | O/Z    | Serial data transmit output                                                                                                              |

| CLKX      | I      | Clock for transmit output for serial port                                                                                                |

| FSX       | I/O/Z  | Frame synchronization pulse for transmit. Configurable as either an input or an output.                                                  |

<sup>†</sup> I/O/Z denotes input/output/high-impedance state.

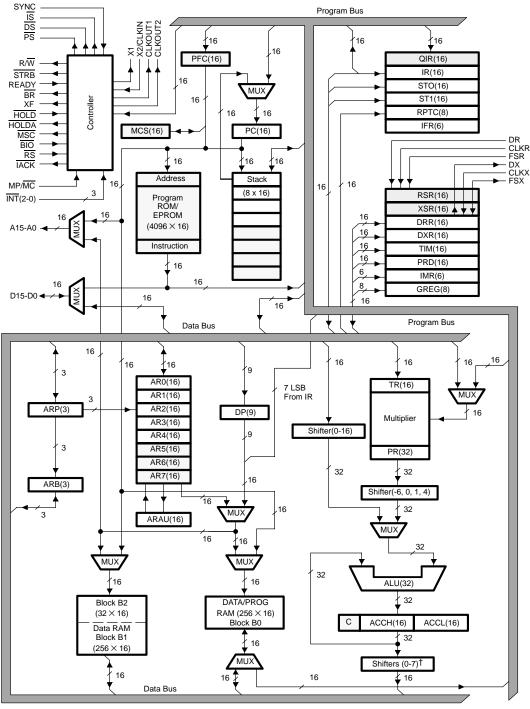

## block diagram

LEGEND:

ACCH = Accumulator high ACCL Accumulator low Arithmetic logic unit Auxiliary register arithmetic unit ALU ARAU

ARB Auxiliary register pointer buffer ARP DP Auxiliary register pointer Data memory page pointer Serial port data receive register

DRR Serial port data transmit register

Interrupt flag register IMR Interrupt mask register

IR Instruction register MCS Microcall stack QIR Queue instruction register PR PRD Product register Period register for timer

Temporary register

Program counter Prefetch counter

PFC RPTC Repeat instruction counter GREG Global memory allocation register RSR Serial port receive shift register XSR AR0-AR7 Serial port transmit shift register

Auxiliary registers Status registers ST0, ST1

#### architecture

The SMJ320C25 increases performance of DSP algorithms through innovative additions to the SMJ320 architecture. Increased throughput on the SMJ320C25 for many DSP applications is accomplished by means of single-cycle multiply/accumulate instructions with a data move option, eight auxiliary registers with a dedicated arithmetic unit, and faster I/O necessary for data-intensive signal processing.

The architectural design of the SMJ320C25 emphasizes overall speed, communication, and flexibility in processor configuration. Control signals and instructions provide floating-point support, block-memory transfers, communication to slower off-chip devices, and multiprocessing implementations.

Two large on-chip RAM blocks, configurable either as separate program and data spaces or as two contiguous data blocks, provide increased flexibility in system design. Programs of up to 4K words can be masked into the internal program ROM. The remainder of the 64K-word program memory space is located externally. Large programs can execute at full speed from this memory space. Programs can also be downloaded from slow external memory to high-speed on-chip RAM. A total of 64K data memory address space is included to facilitate implementation of DSP algorithms. The VLSI implementation of the SMJ320C25 incorporates all of these features as well as many others, such as a hardware timer, serial port, and block data transfer capabilities.

#### 32-bit ALU/accumulator

The SMJ320C25 32-bit arithmetic logic unit (ALU) and accumulator perform a wide range of arithmetic and logical instructions, the majority of which execute in a single clock cycle. The ALU executes a variety of branch instructions dependent on the status of the ALU or a single bit in a word. These instruction provide the following capabilities:

- Branch to an address specified by the accumulator

- Normalize fixed-point numbers contained in the accumulator

- Test a specified bit of a word in data memory.

One input to the ALU is always provided from the accumulator, and the other input can be provided from the product register (PA) of the multiplier or the input scaling shifter which has fetched data from the RAM on the data bus. After the ALU has performed the arithmetic or logical operations, the result is stored in the accumulator.

The 32-bit accumulator is split into two 16-bit segments for storage in data memory. Additional shifters at the output of the accumulator perform shifts while the data is being transferred to the data bus for storage. The contents of the accumulator remain unchanged.

#### scaling shifter

The SMJ320C25 scaling shifter has a 16-bit input connected to the data bus and a 32-bit output connected to the ALU. The scaling shifter produces a left shift of 0 to 16 bits on the input data, as programmed in the instruction. The LSBs of the output are filled with zeroes, and the MSBs can be either filled with zeroes or sign-extended, depending upon the status programmed into the SXM (sign-extension mode) bit of status register ST1.

#### 16 X 16-bit parallel multiplier

The SMJ320C25 has a 16 x 16-bit hardware multiplier, which is capable of computing a signed or unsigned 32-bit product in a single machine cycle. The multiplier has the following two associated registers:

- A 16-bit temporary register (TR) that holds one of the operands for the multiplier, and

- A 32-bit product register (PR) that holds the product.

Incorporated into the SMJ320C25 instruction set are single-cycle multiply/accumulate instruction that allow both operands to be processed simultaneously. The data for these operations can reside anywhere in internal or external memory and can be transferred to the multiplier each cycle via the program and data buses.

## SMJ320C25, SMJ320C25-50 DIGITAL SIGNAL PROCESSOR

SGUS007D - AUGUST 1988 - REVISED OCTOBER 2001

### 16 X 16-bit parallel multiplier (continued)

Four product shift modes are available at the product register (PR) output that are useful when performing multiply/accumulate operations, fractional arithmetic, or justifying fractional products.

#### timer

The SMJ320C25 provides a memory-mapped 16-bit timer for control operations. The on-chip timer (TIM) register is a down counter that is continuously clocked by CLKOUT1. A timer interrupt (TINT) is generated every time the timer decrements to zero. The timer is reloaded with the value contained in the period (PRD) register within the next cycle after it reaches zero so that interrupts can be programmed to occur at regular intervals of PRD + 1 cycles of CLKOUT1.

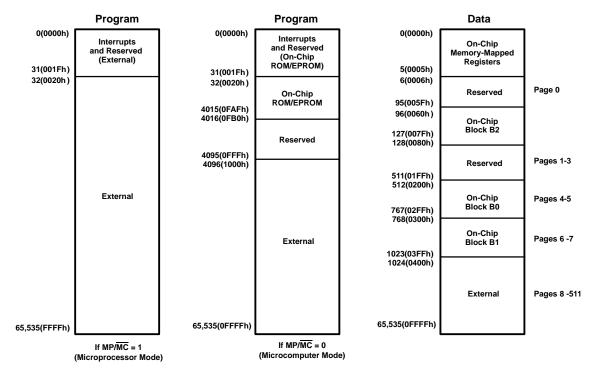

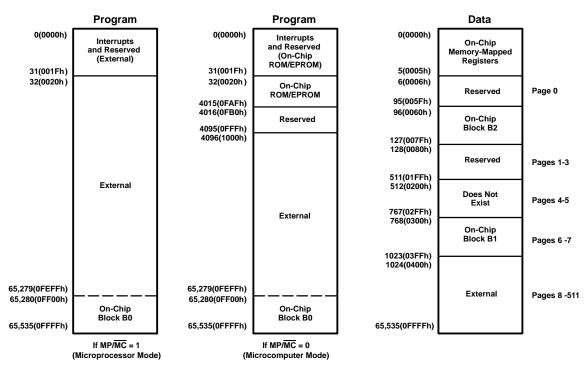

#### memory control

The SMJ320C25 provides a total of 544 16-bit words of on-chip data RAM, divided into three separate blocks (B0, B1, and B2). Of the 544 words, 288 words (blocks B1 and B2) are always data memory, and 256 words (block B0) are programmable as either data or program memory. A data memory size of 544 words allows the SMJ320C25 to handle a data array of 512 words (256 words if on-chip RAM is used for program memory), while still leaving 32 locations for intermediate storage. When using block B0 as program memory, instructions can be downloaded from external program memory into on-chip RAM and then executed.

When using on-chip program RAM, ROM, or high-speed external program memory, the SMJ320C25 runs at full speed without wait states. However, the READY line can be used to interface the SMJ320C25 to slower, less-expensive external memory. Downloading programs from slow off-chip memory to on-chip program RAM speeds processing while cutting system costs.

The SMJ320C25 provides three separate address states for program memory, data memory, and I/O. The on-chip memory is mapped into either the 64K-word data memory or program memory space, depending upon the memory configuration. The CNF0 (configure block B0 as data memory) and CNFP (configure block B0 as program memory) instruction allow dynamic configuration of the memory maps through software. Regardless of the configuration, the user can still execute from external program memory.

The SMJ320C25 has six registers which are mapped into the data memory space: a serial port data receive register, serial port data transmit register, timer register, period register, interrupt mask register, and global memory allocation register.

### memory control (continued)

#### (a) Memory Maps After a CNFD Instruction

(b) Memory Maps After a CNFP Instruction

Figure 1. Memory Maps

## SMJ320C25, SMJ320C25-50 DIGITAL SIGNAL PROCESSOR

SGUS007D - AUGUST 1988 - REVISED OCTOBER 2001

### interrupts and subroutines

The SMJ320C25 has three external maskable user interrupts  $\overline{\text{INT2}}-\overline{\text{INT0}}$ , available for external devices that interrupt the processor. Internal interrupts are generated by the serial port (RINT and XINT), by the timer (TINT), and by the software interrupt (TRAP) instruction. Interrupts are prioritized with reset (RS) having the highest priority and the serial port transmit interrupt (XINT) having the lowest priority. All interrupt locations are on two-word boundaries so that branch instruction can be accommodated in those locations if desired.

A built-in mechanism protects multicycle instructions from interrupts. If an interrupt occurs during a multicycle instruction, the interrupt is not processed until the instruction is completed. This mechanism applies both to instructions that are repeated or become multicycle due to the READY signal.

#### external interface

The SMJ320C25 supports a wide range of system interfacing requirements. Program, data, and I/O address spaces provide interface to memory and I/O. thus maximizing system throughout. I/O design is simplified by having I/O treated the same way as memory. I/O devices are mapped into the I/O address space using the processor's external address and data buses in the same manner as memory-mapped devices. Interface to memory and I/O devices of varying speeds is accomplished by using the READY line. When transitions are made with slower devices, the SMJ320C25 processor waits until the other device completes its function and signals the processor via the READY line. Then, the SMJ320C25 continues execution.

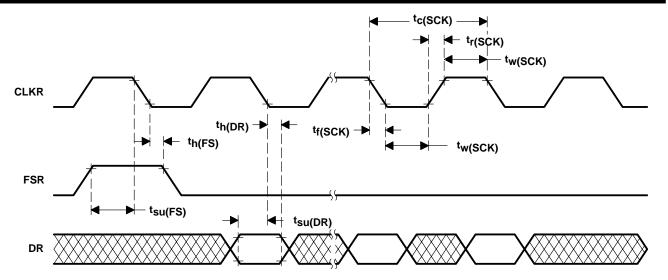

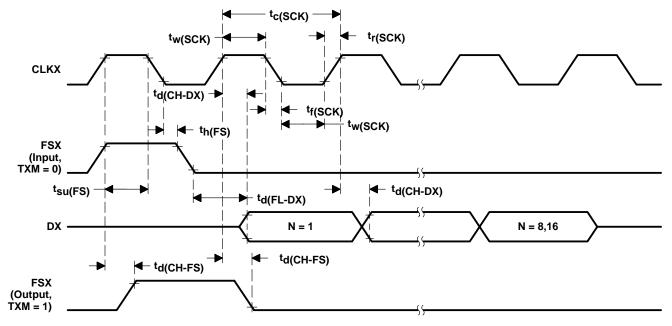

A full-duplex serial port provides communication with serial devices, such as codecs, serial A/D converters, and other serial systems. The interface signals are compatible with codecs and many other serial devices with a minimum of external hardware. The serial port can also be used for intercommunication between processors in multiprocessing applications.

The serial port has two memory-mapped registers: the data transmit register (DXR) and the data receive register (DRR). Both registers operate in either the byte mode or 16-bit word mode, any can be accessed in the same manner as any other data *memory* location. Each register has an external clock, a framing synchronization pulse, and associated shift registers. One method of multiprocessing can be implemented by programming one device to transmit while the others are in the receive mode.

### multiprocessing

The flexibility of the SMJ320C25 allows configurations to satisfy a wide range of system requirements. The SMJ320C25 can be used as follows:

- A standalone processor

- A multiprocessor with devices in parallel

- A slave/host multiprocessor with global memory space

- A peripheral processor interfaced via processor-controlled signals to another device.

For multiprocessing applications, the SMJ320C25 has the capability of allocating global data memory space and communicating with that space via the  $\overline{BR}$  (bus request) and READY control signals. Global memory is data memory shared by more than one processor. Global data memory access must be arbitrated. The 8-bit memory-mapped GREG (global memory allocation register) specifies part of the SMJ320C25s data memory as global external memory. The contents of the register determine the size of the global memory space. If the current instruction addresses an operand within that space,  $\overline{BR}$  is asserted to request control of the bus. The length of the memory cycle is controlled by the READY line.

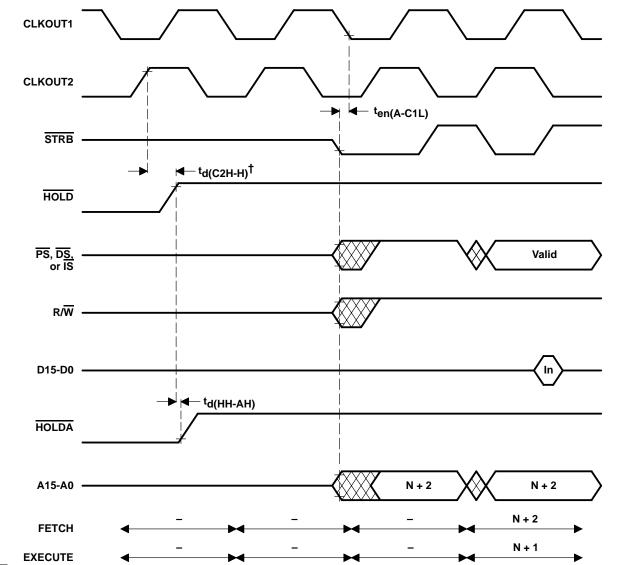

The SMJ320C25 supports DMA (direct memory access) to its external program/data memory using the HOLD and HOLDA signals. Another processor can take complete control of the SMJ320C25s external memory by asserting HOLD low. This causes the SMJ320C25 to place its address, data, and control lines in a high-impedance state, and assert HOLDA. Program execution from on-chip memory can proceed concurrently while the device is in the hold mode.

#### instruction set

The SMJ320C25 microprocessor implements a comprehensive instruction set that supports both numeric-intensive signal processing operations as well as general-purpose applications, such as multiprocessing and high-speed control.

For maximum throughput, the next instruction is prefetched while the current one is being executed. Since the same data lines are used to communicate to external data/program or I/O space, the number of cycles may vary depending upon whether the next data operand fetch is from internal or external program memory. Highest throughput is achieved by maintaining data memory on-chip and using either internal or fast external program memory.

#### addressing modes

The SMJ320C25 instruction set provides three memory addressing modes: direct, indirect, and immediate addressing.

Both direct and indirect addressing can be used to access data memory. In direct addressing, seven bits of the instruction word are concatenated with the nine bits of the data memory page pointer to form the 16-bit data memory address. Indirect addressing accesses data memory through the eight auxiliary registers. In immediate addressing, the data is based on a portion of the instruction word(s).

In direct memory addressing, the instruction word contains the lower seven bits of the data memory address. This field is concatenated with the nine bits of the data memory page pointer to form the full 16-bit address. Thus, memory is paged in the direct addressing mode with a total of 512 pages, each page containing 128 words.

Eight auxiliary register (AR0–AR7) provide flexible and powerful indirect addressing. To select a specific auxiliary register, the Auxiliary Register Pointer (ARP) is loaded with a value from 0 through 7 for AR0–AR7, respectively.

There are seven types of indirect addressing: auto-increment or auto-decrement, post-indexing by either adding or subtracting the contents of ARO, or single indirect addressing with no increment or decrement and bit-reversal addressing (used in FFTs) with increment or decrement. All operations are performed on the current auxiliary register in the same cycle as the original instruction, followed by anew ARP value being loaded.

### repeat feature

A repeat feature, used with instructions such as multiply/accumulates, block moves, I/O transfers, and table read/writes, allows a single instruction to be performed up to 256 times. The repeat counter (RPTC) is loaded with either a data memory value (RPT instruction) or an immediate value (RPTK instruction) .The value of this operand is one less than the number of times that the next instruction is executed. Those instructions that are normally multicycle are pipelined when using the repeat feature, and effectively become single-cycle instructions.

#### instruction set summary

Table 1 lists the symbols and abbreviations used in Table 1, the instruction set summary, Table 2 consists primarily of single-cycle, single-word instructions. Infrequently used branch, I/O, and CALL instructions are multicycle. The instruction set summary is arranged according to function and alphabetized within each functional grouping.

# SMJ320C25, SMJ320C25-50 DIGITAL SIGNAL PROCESSOR

SGUS007D - AUGUST 1988 - REVISED OCTOBER 2001

# instruction set summary (continued)

# **Table 1. Instruction Symbols**

| SYMBOL | MEANING                                                                                      |

|--------|----------------------------------------------------------------------------------------------|

| В      | 4-bit field specifying a bit code                                                            |

| СМ     | 2-bit field specifying compare mode                                                          |

| D      | Data memory address field                                                                    |

| F0     | Format status bit                                                                            |

| M      | Addressing mode bit                                                                          |

| К      | Immediate operand field                                                                      |

| PA     | Port address (PA0–PA15 are predefined assembler symbols equal to 0 through 15, respectively) |

| PM     | 2-bit field specifying P register output shift code                                          |

| R      | 3-bit operand field specifying auxiliary register                                            |

| S      | 4-bit left-shift code                                                                        |

| X      | 3-bit accumulator left-shift field                                                           |

Table 2. SMJ320C25 Instruction Set Summary

|                   | ACCUMULATOR MI                                               | MORY RE | FER | ENC | E IN | STRU | JCTI | ONS | ;    |            |     |     |    |                |            |   |   |          |

|-------------------|--------------------------------------------------------------|---------|-----|-----|------|------|------|-----|------|------------|-----|-----|----|----------------|------------|---|---|----------|

| MNEMONIC          | DESCRIPTION                                                  | NO.     |     |     |      |      | INS  | TRU | JCTI | ON         | ВІТ | COI | DΕ |                |            |   |   |          |

|                   |                                                              | WORDS   | 15  | 14  | 13   | 12   | 11   | 10  | 9    | 8          | 7   | 6   | 5  | 4              | 3          | 2 | 1 | 0        |

| ABS               | Absolute value of accumulator                                | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 1    | 0          | 0   | 0   | 0  | 1              | 1          | 0 | 1 | 1        |

| ADD               | Add to accumulator with shift                                | 1       | 0   | 0   | 0    | 0    | •    |     | s—   | <b>-</b> ▶ | М   | •   |    |                | - D        |   |   | <b>→</b> |

| ADDC‡             | Add to accumulator with carry                                | 1       | 0   | 1   | 0    | 0    | 0    | 0   | 1    | 1          | М   | •   |    |                | - D        |   |   | <b>→</b> |

| ADDH              | Add to high accumulator                                      | 1       | 0   | 1   | 0    | 0    | 1    | 0   | 0    | 0          | М   | 4   |    |                | - D        |   |   | <b>→</b> |

| ADDK‡             | Add to accumulator short immediate                           | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 0    | 0          | •   |     |    | — k            | <b>(</b> — |   |   | <b>→</b> |

| ADDS              | Add to low accumulator with sign extension suppressed        | 1       | 0   | 1   | 0    | 0    | 1    | 0   | 0    | 1          | M   | •   |    |                | - D        |   |   | <b>→</b> |

| ADDT              | Add to accumulator with shift specified by T register        | 1       | 0   | 1   | 0    | 0    | 1    | 0   | 1    | 0          | M   | 4   |    |                | - D        |   |   | <b>→</b> |

| ADLK <sup>†</sup> | Add to accumulator long immediate with shift                 | 2       | 1   | 1   | 0    | 1    | •    |     | s—   | <b>-</b> ▶ | 0   | 0   | 0  | 0              | 0          | 0 | 1 | 0        |

| AND               | AND with accumulator                                         | 1       | 0   | 1   | 0    | 0    | 1    | 1   | 1    | 0          | М   | 4   |    |                | - D        |   |   | <b>→</b> |

| ANDK†             | AND immediate with accumulator with shift                    | 2       | 1   | 1   | 0    | 1    | •    |     | s—   | <b>-</b> ▶ | 0   | 0   | 0  | 0              | 0          | 1 | 0 | 0        |

| CMPL†             | Complement accumulator                                       | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 1    | 0          | 0   | 0   | 1  | 0              | 0          | 1 | 1 | 1        |

| LAC               | Load accumulator with shift                                  | 1       | 0   | 0   | 1    | 0    | •    |     | s—   | <b>-</b> ▶ | М   | 4   |    |                | - D        |   |   | <b>-</b> |

| LACK              | Load accumulator immediate short                             | 1       | 1   | 1   | 0    | 0    | 1    | 0   | 1    | 0          | •   |     |    | — k            | <b>(</b> — |   |   | <b>→</b> |

| LACT†             | Load accumulator with shift specified by T register          | 1       | 0   | 1   | 0    | 0    | 0    | 0   | 1    | 0          | М   | 4   |    |                | - D        |   |   | <b>→</b> |

| LALK <sup>†</sup> | Load accumulator long immediate with shift                   | 2       | 1   | 1   | 0    | 1    | •    |     | s—   | <b>-</b>   | 0   | 0   | 0  | 0              | 0          | 0 | 0 | 1        |

| NEG <sup>†</sup>  | Negate accumulator                                           | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 1    | 0          | 0   | 0   | 1  | 0              | 0          | 0 | 1 | 1        |

| NORM†             | Normalize contents of accumulator                            | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 1    | 0          | 1   | 4   |    |                | - D        |   |   | <b>→</b> |

| OR                | OR with accumulator                                          | 1       | 0   | 1   | 0    | 0    | 1    | 1   | 0    | 1          | М   | 4   |    |                | - D        |   |   | <b>→</b> |

| ORK†              | OR immediate with accumulator with shift                     | 2       | 1   | 1   | 0    | 1    | •    |     | s—   | <b>-</b> ▶ | 0   | 0   | 0  | 0              | 0          | 1 | 0 | 1        |

| ROL <sup>‡</sup>  | Rotate accumulator left                                      | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 1    | 0          | 0   | 0   | 1  | 1              | 0          | 1 | 0 | 0        |

| ROR <sup>‡</sup>  | Rotate accumulator right                                     | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 1    | 0          | 0   | 0   | 1  | 1              | 0          | 1 | 0 | 1        |

| SACH              | Store high accumulator with shift                            | 1       | 0   | 1   | 1    | 0    | 1    | •   | — х  | <b>-</b> ▶ | М   | 4   |    |                | - D        |   |   | <b>→</b> |

| SACL              | Store low-order accumulator with shift                       | 1       | 0   | 1   | 1    | 0    | 0    | •   | - x  | <b>-</b> ▶ | М   | 4   |    |                | - D        |   |   | <b>→</b> |

| SBLK†             | Subtract from accumulator long immediate with shift          | 2       | 1   | 1   | 0    | 1    | •    |     | s—   | <b>-</b> ▶ | 0   | 0   | 0  | 0              | 0          | 0 | 1 | 1        |

| SFL <sup>†</sup>  | Shift accumulator left                                       | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 1    | 0          | 0   | 0   | 0  | 1              | 1          | 0 | 0 | 0        |

| SFR†              | Shift accumulator right                                      | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 1    | 0          | 0   | 0   | 0  | 1              | 1          | 0 | 0 | 1        |

| SUB               | Subtract from accumulator with shift                         | 1       | 0   | 0   | 0    | 1    | •    |     | s—   | <b>-</b>   | М   | 4   |    |                | - D        |   |   | <b>→</b> |

| SUBB‡             | Subtract from accumulator with borrow                        | 1       | 0   | 1   | 0    | 0    | 1    | 1   | 1    | 1          | М   | 4   |    |                | - D        |   |   | <b>→</b> |

| SUBC              | Conditional subtract                                         | 1       | 0   | 1   | 0    | 0    | 0    | 1   | 1    | 1          | М   | 4   |    |                | - D        |   |   | <b>→</b> |

| SUBH              | Subtract from high accumulator                               | 1       | 0   | 1   | 0    | 0    | 0    | 1   | 0    | 0          | М   | 4   |    |                | - D        |   |   | <b>→</b> |

| SUBK <sup>‡</sup> | Subtract from accumulator short immediate                    | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 0    | 1          | •   |     |    | — <sub>k</sub> | <b>(</b> — |   |   | <b>→</b> |

| SUBS              | Subtract from low accumulator with sign extension suppressed | 1       | 0   | 1   | 0    | 0    | 0    | 1   | 0    | 1          | М   | 4   |    |                | - D        |   |   | <b>→</b> |

$<sup>\</sup>dagger$  These instructions are not included in the TMS320C1x instruction set.

<sup>&</sup>lt;sup>‡</sup> These instructions are not included in the TMS32020 instruction set.

Table 2. SMJ320C25 Instruction Set Summary (continued)

|                                          | ACCUMULATOR ME                                                                                                                                                                                                                                                                                                       | MORY RE                               | FER                                                 | ENC                             | E IN                            | STRU                            | JCTI                                  | ONS          |                                           |          |                       |      |          |        |                                                       |     |            |                                         |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------------|--------------|-------------------------------------------|----------|-----------------------|------|----------|--------|-------------------------------------------------------|-----|------------|-----------------------------------------|

| MNEMO                                    | NIC DESCRIPTION                                                                                                                                                                                                                                                                                                      | NO.<br>WORDS                          |                                                     |                                 |                                 |                                 | IN                                    | ISTR         | UC                                        | TION     | I BI                  | тс   | ODE      |        |                                                       |     |            |                                         |

|                                          |                                                                                                                                                                                                                                                                                                                      | HOMEO                                 | 15                                                  | 14                              | 13                              | 12                              | 11                                    | 10           | 9                                         | 8        | 7                     | 6    | 5        | 4      | 3                                                     | 2   | 1          | 0                                       |

| SUBT†                                    | Subtract from accumulator with shift specified by T register                                                                                                                                                                                                                                                         | 1                                     | 0                                                   | 1                               | 0                               | 0                               | 0                                     | 1            | 1                                         | 0        | М                     | •    |          |        | - D                                                   |     |            | <b>-</b>                                |

| XOR                                      | Exclusive-OR with accumulator                                                                                                                                                                                                                                                                                        | 1                                     | 0                                                   | 1                               | 0                               | 0                               | 1                                     | 1            | 0                                         | 0        | М                     | •    |          |        | - D                                                   |     |            | -                                       |

| XORK†                                    | Exclusive-OR immediate with accumulator with shift                                                                                                                                                                                                                                                                   | 2                                     | 1                                                   | 1                               | 0                               | 1                               | •                                     | — ;          | s –                                       | <b>-</b> | 0                     | 0    | 0        | 0      | 0                                                     | 1   | 1          | 0                                       |

| ZAC                                      | Zero accumulator                                                                                                                                                                                                                                                                                                     | 1                                     | 1                                                   | 1                               | 0                               | 0                               | 1                                     | 0            | 1                                         | 0        | 0                     | 0    | 0        | 0      | 0                                                     | 0   | 0          | 0                                       |

| ZALH                                     | Zero low accumulator and load high accumulator                                                                                                                                                                                                                                                                       | 1                                     | 0                                                   | 1                               | 0                               | 0                               | 0                                     | 0            | 0                                         | 0        | М                     | •    |          |        | - D                                                   |     |            | -                                       |

| ZALR‡                                    | Zero low accumulator and load high accumulator with rounding                                                                                                                                                                                                                                                         | 1                                     | 0                                                   | 1                               | 1                               | 1                               | 1                                     | 0            | 1                                         | 1        | М                     | •    |          |        | - D                                                   |     |            | <b>→</b>                                |

| ZALS                                     | Zero accumulator and load low accumulator with sign extension suppressed                                                                                                                                                                                                                                             | 1                                     | 0                                                   | 1                               | 0                               | 0                               | 0                                     | 0            | 0                                         | 1        | М                     | •    |          |        | - D                                                   |     |            | <b>→</b>                                |

|                                          | AUXILIARY REGISTERS A                                                                                                                                                                                                                                                                                                | ND DATA                               | PAG                                                 | E P                             | TNIC                            | ER II                           | NSTF                                  | RUCT         | 101                                       | IS       |                       |      |          |        |                                                       |     |            |                                         |

|                                          |                                                                                                                                                                                                                                                                                                                      |                                       | ATA PAGE POINTER INSTRUCTIONS  INSTRUCTION BIT CODE |                                 |                                 |                                 |                                       |              |                                           |          |                       |      |          |        |                                                       |     |            |                                         |

| MNEMO                                    | NIC DESCRIPTION                                                                                                                                                                                                                                                                                                      | NO.<br>WORDS                          |                                                     |                                 |                                 |                                 | IN                                    | ISTR         | UC                                        | TION     | I BI                  | ТС   | ODE      |        |                                                       |     |            |                                         |

| MNEMO                                    | ONIC DESCRIPTION                                                                                                                                                                                                                                                                                                     | NO.<br>WORDS                          | 15                                                  | 14                              | 13                              | 12                              | 11                                    | ISTR<br>10   | UC <sup>-</sup>                           | 10N<br>8 | 1 BI <sup>*</sup>     | T C( | ODE<br>5 | 4      | 3                                                     | 2   | 1          | 0                                       |

| MNEMO<br>ADRK‡                           | Add to auxiliary register short immediate                                                                                                                                                                                                                                                                            |                                       |                                                     | <b>14</b>                       | <b>13</b>                       | <b>12</b>                       |                                       |              |                                           |          |                       |      |          |        | <b>3</b><br>K -                                       | 2   | 1          | 0                                       |

|                                          |                                                                                                                                                                                                                                                                                                                      | WORDS                                 | 15                                                  |                                 |                                 |                                 | 11                                    |              |                                           | 8        |                       |      |          |        | <b>3</b> K -                                          |     |            | 0<br>→                                  |

| ADRK‡                                    | Add to auxiliary register short immediate  Compare auxiliary register with auxiliary                                                                                                                                                                                                                                 | WORDS<br>1                            | <b>15</b>                                           | 1                               | 1                               | 1                               | 11                                    |              |                                           | <b>8</b> | 7                     |      | 5        | 4      | K -                                                   | 0 • |            | <u>→</u>                                |

| ADRK‡                                    | Add to auxiliary register short immediate  Compare auxiliary register with auxiliary register AR0                                                                                                                                                                                                                    | WORDS  1                              | 0<br>1                                              | 1                               | 1 0                             | 1 0                             | <b>11</b> 1                           |              |                                           | <b>8</b> | 7                     |      | 5        | 4      | К -<br>0                                              | 0 • |            | <u>→</u>                                |

| ADRK‡ CMPR† LAR                          | Add to auxiliary register short immediate  Compare auxiliary register with auxiliary register AR0  Load auxiliary register                                                                                                                                                                                           | 1<br>1<br>1                           | 15<br>0<br>1<br>0                                   | 1<br>1<br>0                     | 1<br>0<br>1                     | 1 0 1                           | <b>11</b> 1                           |              |                                           | <b>8</b> | 7                     |      | 5        | 4      | К -<br>0                                              | 0 • |            | <u>→</u>                                |

| ADRK‡ CMPR† LAR LARK                     | Add to auxiliary register short immediate  Compare auxiliary register with auxiliary register AR0  Load auxiliary register  Load auxiliary register short immediate                                                                                                                                                  | 1<br>1<br>1<br>1                      | 15<br>0<br>1<br>0<br>1                              | 1<br>1<br>0<br>1                | 1<br>0<br>1<br>0                | 1<br>0<br>1<br>0                | 11<br>1<br>1<br>0                     |              | 9<br>1<br>1<br>R<br>R                     | <b>8</b> | 7                     | 1    | 0        | 1      | К -<br>0                                              | 0 • | <b>←</b> C | <u>→</u>                                |

| ADRK‡ CMPR† LAR LARK LARK                | Add to auxiliary register short immediate  Compare auxiliary register with auxiliary register AR0  Load auxiliary register  Load auxiliary register short immediate  Load auxiliary register pointer                                                                                                                 | 1 1 1 1 1 1 1                         | 15<br>0<br>1<br>0<br>1<br>0                         | 1<br>1<br>0<br>1                | 1<br>0<br>1<br>0                | 1<br>0<br>1<br>0                | 11<br>1<br>1<br>0<br>0                | 10<br>1<br>1 | 9<br>1<br>1<br>R<br>R                     | <b>8</b> | 7                     | 1    | 0        | 1      | K - 0 - D - K 1 - D                                   | 0 • | <b>←</b> C | <u>→</u>                                |

| ADRK‡ CMPR† LAR LARK LARK LARP           | Add to auxiliary register short immediate  Compare auxiliary register with auxiliary register AR0  Load auxiliary register  Load auxiliary register short immediate  Load auxiliary register pointer  Load data memory page pointer                                                                                  | 1 1 1 1 1 1 1 1                       | 15<br>0<br>1<br>0<br>1<br>0<br>0                    | 1<br>1<br>0<br>1<br>1           | 1<br>0<br>1<br>0<br>0           | 1<br>0<br>1<br>0<br>1           | 11<br>1<br>0<br>0<br>0                | 10<br>1<br>1 | 9<br>1<br>1<br>R<br>R                     | <b>8</b> | 7                     | 1    | 0        | 1 0    | K - 0 - D - K 1 - D                                   | 0 • | <b>←</b> C | <u>→</u>                                |

| ADRK‡ CMPR† LAR LARK LARP LDP            | Add to auxiliary register short immediate  Compare auxiliary register with auxiliary register AR0  Load auxiliary register  Load auxiliary register short immediate  Load auxiliary register pointer  Load data memory page pointer  Load data memory page pointer immediate                                         | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 15<br>0<br>1<br>0<br>1<br>0<br>0<br>1               | 1<br>1<br>0<br>1<br>1<br>1      | 1<br>0<br>1<br>0<br>0<br>0      | 1<br>0<br>1<br>0<br>1<br>1      | 11<br>1<br>0<br>0<br>0                | 10<br>1<br>1 | 9<br>1<br>1<br>R<br>R                     | <b>8</b> | 7                     | 1 0  | 0        | 1<br>0 | K - 0 - D - K 1 - D                                   | 0   | <b>←</b> C | → M → → → → → → → → → → → → → → → → → → |

| ADRK‡ CMPR† LAR LARK LARP LDP LDPK LRLK† | Add to auxiliary register short immediate  Compare auxiliary register with auxiliary register AR0  Load auxiliary register  Load auxiliary register short immediate  Load auxiliary register pointer  Load data memory page pointer  Load data memory page pointer immediate  Load auxiliary register long immediate | 1 1 1 1 1 1 1 2                       | 15<br>0<br>1<br>0<br>1<br>0<br>0<br>1<br>1          | 1<br>1<br>0<br>1<br>1<br>1<br>1 | 1<br>0<br>1<br>0<br>0<br>0<br>0 | 1<br>0<br>1<br>0<br>1<br>1<br>0 | 11<br>1<br>1<br>0<br>0<br>0<br>0<br>1 | 10<br>1<br>1 | 9<br>1<br>1<br>R<br>R<br>0<br>1<br>0<br>R | <b>8</b> | 7<br>0<br>M<br>1<br>M | 1 0  | 0        | 1<br>0 | K - 0 - D - K - 1 - D - D - D - D - D - D - D - D - D | 0   | <b>←</b> C | → M → → → → → → → → → → → → → → → → → → |

<sup>&</sup>lt;sup>†</sup> These instructions are not included in the TMS320C1x instruction set.

<sup>&</sup>lt;sup>‡</sup>These instructions are not included in the TMS32020 instruction set.

## Table 2. SMJ320C25 Instruction Set Summary (continued)

|                  | T REGISTER, P REGI                                          | STER, AN     | D MU | JLTIF | PLY I | NSTF | RUCT | TION: | s   |     |     |     |    |   |     |     |             |          |

|------------------|-------------------------------------------------------------|--------------|------|-------|-------|------|------|-------|-----|-----|-----|-----|----|---|-----|-----|-------------|----------|

| MNEMO            | NIC DESCRIPTION                                             | NO.<br>WORDS |      |       |       |      |      | STR   | UCT | ION | ВІТ | co  | DE |   |     |     |             |          |

|                  |                                                             |              | 15   | 14    | 13    | 12   | 11   | 10    | 9   | 8   | 7   | 6   | 5  | 4 | 3   | 2   | 1           | 0        |

| APAC             | Add P register to accumulator                               | 1            | 1    | 1     | 0     | 0    | 1    | 1     | 1   | 0   | 0   | 0   | 0  | 1 | 0   | 1   | 0           | 1        |

| LPH <sup>†</sup> | Load high P register                                        | 1            | 0    | 1     | 0     | 1    | 0    | 0     | 1   | 1   | M   | •   |    |   | - D |     |             | <b>→</b> |

| LT               | Load T register                                             | 1            | 0    | 0     | 1     | 1    | 1    | 1     | 0   | 0   | M   | •   |    |   | - D |     |             | <b>→</b> |

| LTA              | Load T register and accumulate previous product             | 1            | 0    | 0     | 1     | 1    | 1    | 1     | 0   | 1   | М   | •   |    |   | - D |     |             | <b>→</b> |

| LTD              | Load T register, accumulate previous product, and move data | 1            | 0    | 0     | 1     | 1    | 1    | 1     | 1   | 1   | M   | •   |    |   | - D |     | —           | <b>→</b> |

| LTP†             | Load T register and store P register in accumulator         | 1            | 0    | 0     | 1     | 1    | 1    | 1     | 1   | 0   | M   | •   |    |   | - D |     |             | <b>-</b> |

| LTS <sup>†</sup> | Load T register and subtract previous product               | 1            | 0    | 1     | 0     | 1    | 1    | 0     | 1   | 1   | М   | 4   |    |   | - D |     |             | <b>→</b> |

| MAC†             | Multiply and accumulate                                     | 2            | 0    | 1     | 0     | 1    | 1    | 1     | 0   | 1   | М   | 4   |    |   | - D |     |             | <b>→</b> |

| MACD†            | Multiply and accumulate with data move                      | 2            | 0    | 1     | 0     | 1    | 1    | 1     | 0   | 0   | М   | 4   |    |   | - D |     |             | <b>→</b> |

| MPY              | Multiply (with T register, store product in P register)     | 1            | 0    | 0     | 1     | 1    | 1    | 0     | 0   | 0   | М   | •   |    |   | - D |     |             | <b>-</b> |

| MPYA‡            | Multiply and accumulate previous product                    | 1            | 0    | 0     | 1     | 1    | 1    | 0     | 1   | 0   | М   | 4   |    |   | - D |     |             | <b>→</b> |

| MPYK             | Multiply immediate                                          | 1            | 1    | 0     | 1     | •    |      |       |     |     | — 1 | κ – |    |   |     |     |             | <b>→</b> |

| MPYS‡            | Multiply and subtract previous product                      | 1            | 0    | 0     | 1     | 1    | 1    | 0     | 1   | 1   | М   | 4   |    |   | - D |     |             | <b>→</b> |

| MPYU‡            | Multiply unsigned                                           | 1            | 1    | 1     | 0     | 0    | 1    | 1     | 1   | 1   | М   | 4   |    |   | - D |     |             | <b>→</b> |

| PAC              | Load accumulator with P register                            | 1            | 1    | 1     | 0     | 0    | 1    | 1     | 1   | 0   | 0   | 0   | 0  | 1 | 0   | 1   | 0           | 0        |

| SPAC             | Subtract P register from accumulator                        | 1            | 1    | 1     | 0     | 0    | 1    | 1     | 1   | 0   | 0   | 0   | 0  | 1 | 0   | 1   | 1           | 0        |

| SPH <sup>‡</sup> | Store high P register                                       | 1            | 0    | 1     | 1     | 1    | 1    | 1     | 0   | 1   | М   | 4   |    |   | - D |     |             | <b>-</b> |

| SPL <sup>‡</sup> | Store low P register                                        | 1            | 0    | 1     | 1     | 1    | 1    | 1     | 0   | 0   | М   | •   |    |   | - D |     |             | <b>→</b> |

| SPM <sup>†</sup> | Set P register output shift mode                            | 1            | 1    | 1     | 0     | 0    | 1    | 1     | 1   | 0   | 0   | 0   | 0  | 0 | 1   | 0 • | <b>◆</b> PI | M        |

| SQRA†            | Square and accumulate                                       | 1            | 0    | 0     | 1     | 1    | 1    | 0     | 0   | 1   | М   | 4   |    |   | - D |     |             | <b>-</b> |

| sqrs†            | Square and subtract previous product                        | 1            | 0    | 1     | 0     | 1    | 1    | 0     | 1   | 0   | М   | •   |    |   | - D |     |             | <u> </u> |

<sup>&</sup>lt;sup>†</sup> These instructions are not included in the TMS320C1x instruction set.

<sup>‡</sup> These instructions are not included in the TMS32020 instruction set.

Table 2. SMJ320C25 Instruction Set Summary (continued)

|                   | BRAN                                         | ICH/CALL     | INS  | TRUC      | CTIO      | NS        |          |      |          |               |      |      |             |          |     |   |   |          |

|-------------------|----------------------------------------------|--------------|------|-----------|-----------|-----------|----------|------|----------|---------------|------|------|-------------|----------|-----|---|---|----------|

| MNEMO             | NIC DESCRIPTION                              | NO.<br>WORDS |      |           |           |           | II       | NSTR | UC       | TIOI          | N BI | IT C | ODE         | <b>=</b> |     |   |   |          |

|                   |                                              |              | 15   | 14        | 13        | 12        | 11       | 10   | 9        | 8             | 7    | 6    | 5           | 4        |     | 2 | 1 | 0        |

| В                 | Branch unconditionally                       | 2            | 1    | 1         | 1         | 1         | 1        | 1    | 1        | 1             | 1    | •    | -           |          | – D |   |   | <b>→</b> |

| BACCT             | Branch to address specified by accumulator   | 1            | 1    | 1         | 0         | 0         | 1        | 1    | 1        | 0             | 0    | 0    | 1           | 0        | 0   | 1 | 0 | 1        |

| BANZ              | Branch on auxiliary register not zero        | 2            | 1    | 1         | 1         | 1         | 1        | 0    | 1        | 1             | 1    | •    | -           |          | – D |   |   | <b>→</b> |

| BBNZ†             | Branch if TC bit ≠ 0                         | 2            | 1    | 1         | 1         | 1         | 1        | 0    | 0        | 1             | 1    | •    | -           |          | – D |   |   | <b>→</b> |

| BBZ†              | Branch if TC bit = 0                         | 2            | 1    | 1         | 1         | 1         | 1        | 0    | 0        | 0             | 1    | •    | -           |          | – D |   |   | <b>→</b> |

| BC‡               | Branch on carry                              | 2            | 0    | 1         | 0         | 1         | 1        | 1    | 1        | 0             | 1    | •    | —           |          | – D |   |   | <b>→</b> |

| BGEZ              | Branch if accumulator $\geq 0$               | 2            | 1    | 1         | 1         | 1         | 0        | 1    | 0        | 0             | 1    | ◀    | -           |          | – D |   |   | <b>-</b> |

| BGZ               | Branch if accumulator > 0                    | 2            | 1    | 1         | 1         | 1         | 0        | 0    | 0        | 1             | 1    | •    | <del></del> |          | – D |   |   | <b>→</b> |

| BIOZ              | Branch on I/O status = 0                     | 2            | 1    | 1         | 1         | 1         | 1        | 0    | 1        | 0             | 1    | •    | <del></del> |          | – D |   |   | <b>→</b> |

| BLEZ              | Branch if accumulator ≤ 0                    | 2            | 1    | 1         | 1         | 1         | 0        | 0    | 1        | 0             | 1    | •    | -           |          | – D |   |   | <b>→</b> |

| BLZ               | Branch if accumulator < 0                    | 2            | 1    | 1         | 1         | 1         | 0        | 0    | 1        | 1             | 1    | •    | <del></del> |          | - D |   |   | <b>-</b> |

| BNC‡              | Branch on no carry                           | 2            | 0    | 1         | 0         | 1         | 1        | 1    | 1        | 1             | 1    | •    | -           |          | - D |   |   | <b>-</b> |

| BNV†              | Branch if no overflow                        | 2            | 1    | 1         | 1         | 1         | 0        | 1    | 1        | 1             | 1    | •    | -           |          | – D |   |   | <b>-</b> |

| BNZ               | Branch if accumulator ≠ 0                    | 2            | 1    | 1         | 1         | 1         | 0        | 1    | 0        | 1             | 1    | •    | <b>—</b>    |          | – D |   |   | <b>-</b> |

| BV                | Branch on overflow                           | 2            | 1    | 1         | 1         | 1         | 0        | 0    | 0        | 0             | 1    | •    | -           |          | – D |   |   | <b>-</b> |

| BZ                | Branch if accumulator = 0                    | 2            | 1    | 1         | 1         | 1         | 0        | 1    | 1        | 0             | 1    | •    | —           |          | – D |   |   | <b>-</b> |

| CALA              | Call subroutine indirect                     | 1            | 1    | 1         | 0         | 0         | 1        | 1    | 1        | 0             | 0    | 0    | 1           | 0        | 0   | 1 | 0 | 0        |

| CALL              | Call subroutine                              | 2            | 1    | 1         | 1         | 1         | 1        | 1    | 1        | 0             | 1    | •    | <u> </u>    |          | – D |   |   | <b>→</b> |

| RET               | Return from subroutine                       | 1            | 1    | 1         | 0         | 0         | 1        | 1    | 1        | 0             | 0    | 0    | 1           | 0        | 0   | 1 | 1 | 0        |

|                   | I/O AND                                      | DATA MEN     | /IOR | Y OP      | ERA       | ΓΙΟΝ      | s        |      |          |               |      |      |             |          |     |   |   |          |

|                   |                                              | NO.          |      |           |           |           | II       | NSTR | :UC      | TIOI          | N BI | T C  | ODE         | =        |     |   |   |          |

| MNEMO             | NIC DESCRIPTION                              | WORDS        | 15   | 11        | 12        | 12        |          | 10   |          |               | 7    | 6    | 5           |          | 3   | _ | 4 | _        |

| BLKD†             | Block move from data memory to data memory   | 2            | 1    | <b>14</b> | <b>13</b> | <b>12</b> | 11       | 1    | <b>9</b> | <b>8</b><br>1 | M    | •    | <u> </u>    | 4        |     | _ | 1 | 0        |

| BLKP†             | Block move from program memory to data       | 2            | 1    | 1         | 1         | 1         | 1        | 1    | 0        | 0             | M    | •    | '<br>       |          | - D |   |   | <b>→</b> |

| DMOV              | memory  Data move in data memory             | 1            | 0    | 1         | 0         | 1         | 0        | 1    | 1        | 0             | М    | _    |             |          | _   |   |   |          |

| FORT†             | Format serial port registers                 | 1            | 1    | 1         | 0         | 0         | 1        | 1    |          | 0             |      | 0    | _           | 0        | – D |   | 1 | FC       |

|                   |                                              | '            | l .  | •         | ·         | ·         | '<br>'   | •    | •        | •             |      | 0    |             | U        |     |   | ' |          |

| IN                | Input data from port                         | 1            | 1    | 0         | 0         | 0         | <b>T</b> | — F  |          |               | M    | •    |             |          | – D |   |   | <b>→</b> |

| OUT               | Output data to port                          | 1            | 1    | 1         | 1         | 0         | <b>4</b> |      | Α -      |               | · M  |      | _           |          | – D |   | _ |          |

| RFSM‡             | Reset serial port frame synchronization mode | 1            | 1    | 1         | 0         | 0         | 1        | 1    | 1        | 0             | 0    | 0    | 1           | 1        | 0   | 1 | 1 | 0        |

| RTXM <sup>†</sup> | Reset serial port transmit mode              | 1            | 1    | 1         | 0         | 0         | 1        | 1    | 1        | 0             | 0    | 0    | 1           | 0        | 0   | 0 | 0 | 0        |

| RXF <sup>†</sup>  | Reset external flag                          | 1            | 1    | 1         | 0         | 0         | 1        | 1    | 1        | 0             | 0    | 0    | 0           | 0        | 1   | 1 | 0 | 0        |

| SFSM <sup>‡</sup> | Set serial port frame synchronization mode   | 1            | 1    | 1         | 0         | 0         | 1        | 1    | 1        | 0             | 0    | 0    | 1           | 1        | 0   | 1 | 1 | 1        |

| STXM <sup>†</sup> | Set serial port transmit mode                | 1            | 1    | 1         | 0         | 0         | 1        | 1    | 1        | 0             | 0    | 0    | 1           | 0        | 0   | 0 | 0 | 1        |

| SXF†              | Set external flag                            | 1            | 1    | 1         | 0         | 0         | 1        | 1    | 1        | 0             | 0    | 0    | 0           | 0        | 1   | 1 | 0 | 1        |

| TBLR              | Table read                                   | 1            | 0    | 1         | 0         | 1         | 1        | 0    | 0        | 0             | M    | •    | -           |          | – D |   |   | <b>→</b> |

| TBLW              | Table write                                  | 1            | 0    | 1         | 0         | 1         | 1        | 0    | 0        | 1             | Μ    | •    | -           |          | – D |   |   | <b>-</b> |

<sup>†</sup> These instructions are not included in the TMS320C1x instruction set.

<sup>&</sup>lt;sup>‡</sup> These instructions are not included in the TMS32020 instruction set.

Table 2. SMJ320C25 Instruction Set Summary (concluded)

|                   |                                                      | TROL INS     |    |    |    |    |    |     |     |            |     |    |    |     |      |   |   |          |

|-------------------|------------------------------------------------------|--------------|----|----|----|----|----|-----|-----|------------|-----|----|----|-----|------|---|---|----------|

| MNEMONIC          | DESCRIPTION                                          | NO.<br>WORDS |    |    |    |    | IN | STR | JCT | ION        | BIT | CC | DE |     |      |   |   |          |

|                   |                                                      | WORDO        | 15 | 14 | 13 | 12 | 11 | 10  | 9   | 8          | 7   | 6  | 5  | 4   | 3    | 2 | 1 | 0        |

| віт†              | Test bit                                             | 1            | 1  | 0  | 0  | 1  | •  | — Е | 3 — | <b>-</b> ▶ | М   | •  |    |     | D -  |   |   | <b>→</b> |

| BITT <sup>†</sup> | Test bit specified by T register                     | 1            | 0  | 1  | 0  | 1  | 0  | 1   | 1   | 1          | М   | •  |    |     | D -  |   |   | •        |

| CNFD†             | Configure block as data memory                       | 1            | 1  | 1  | 0  | 0  | 1  | 1   | 1   | 0          | 0   | 0  | 0  | 0   | 0    | 1 | 0 | 0        |

| CNFP <sup>†</sup> | Configure block as program memory                    | 1            | 1  | 1  | 0  | 0  | 1  | 1   | 1   | 0          | 0   | 0  | 0  | 0   | 0    | 1 | 0 | 1        |

| DINT              | Disable interrupt                                    | 1            | 1  | 1  | 0  | 0  | 1  | 1   | 1   | 0          | 0   | 0  | 0  | 0   | 0    | 0 | 0 | 1        |

| EINT              | Enable interrupt                                     | 1            | 1  | 1  | 0  | 0  | 1  | 1   | 1   | 0          | 0   | 0  | 0  | 0   | 0    | 0 | 0 | 0        |

| IDLE†             | Idle until interrupt                                 | 1            | 1  | 1  | 0  | 0  | 1  | 1   | 1   | 0          | 0   | 0  | 0  | 1   | 1    | 1 | 1 | 1        |

| LST               | Load status register STO                             | 1            | 0  | 1  | 0  | 1  | 0  | 0   | 0   | 0          | М   | •  |    |     | D-   |   |   | •        |

| LST1 <sup>†</sup> | Load status register ST1                             | 1            | 0  | 1  | 0  | 1  | 0  | 0   | 0   | 1          | М   | •  |    |     | - D- |   |   | <b>→</b> |

| NOP               | No operation                                         | 1            | 0  | 1  | 0  | 1  | 0  | 1   | 0   | 1          | 0   | 0  | 0  | 0   | 0    | 0 | 0 | 0        |

| POP               | Pop top of stack to low accumulator                  | 1            | 1  | 1  | 0  | 0  | 1  | 1   | 1   | 0          | 0   | 0  | 0  | 1   | 1    | 1 | 0 | 1        |

| POPD†             | Pop top of stack to data memory                      | 1            | 0  | 1  | 1  | 1  | 1  | 0   | 1   | 0          | М   | •  |    |     | D-   |   |   | <b>→</b> |

| PSHD†             | Push data memory value onto stack                    | 1            | 0  | 1  | 0  | 1  | 0  | 1   | 0   | 0          | М   | •  |    |     | D-   |   |   | •        |

| PUSH              | Push low accumulator onto stack                      | 1            | 1  | 1  | 0  | 0  | 1  | 1   | 1   | 0          | 0   | 0  | 0  | 1   | 1    | 1 | 0 | 0        |

| RC <sup>‡</sup>   | Reset carry bit                                      | 1            | 1  | 1  | 0  | 0  | 1  | 1   | 1   | 0          | 0   | 0  | 1  | 1   | 0    | 0 | 0 | 0        |

| RHM <sup>‡</sup>  | Reset hold mode                                      | 1            | 1  | 1  | 0  | 0  | 1  | 1   | 1   | 0          | 0   | 0  | 1  | 1   | 1    | 0 | 0 | 0        |

| ROVM              | Reset overflow mode                                  | 1            | 1  | 1  | 0  | 0  | 1  | 1   | 1   | 0          | 0   | 0  | 0  | 0   | 0    | 0 | 1 | 0        |

| RPT <sup>†</sup>  | Repeat instruction as specified by data memory value | 1            | 0  | 1  | 0  | 0  | 1  | 0   | 1   | 1          | М   | •  |    |     | D-   |   |   | <b>→</b> |

| RPTK <sup>†</sup> | Repeat instruction as specified by immediate value   | 1            | 1  | 1  | 0  | 0  | 1  | 0   | 1   | 1          | •   |    |    | – к | (    |   |   | <b>→</b> |

| RSXM <sup>†</sup> | Reset sign-extension mode                            | 1            | 1  | 1  | 0  | 0  | 1  | 1   | 1   | 0          | 0   | 0  | 0  | 0   | 0    | 1 | 1 | 0        |

| RTC <sup>‡</sup>  | Reset test/control flag                              | 1            | 1  | 1  | 0  | 0  | 1  | 1   | 1   | 0          | 0   | 0  | 1  | 1   | 0    | 0 | 1 | 0        |

| sc‡               | Set carry bit                                        | 1            | 1  | 1  | 0  | 0  | 1  | 1   | 1   | 0          | 0   | 0  | 1  | 1   | 0    | 0 | 0 | 1        |

| SHM‡              | Set hold mode                                        | 1            | 1  | 1  | 0  | 0  | 1  | 1   | 1   | 0          | 0   | 0  | 1  | 1   | 1    | 0 | 0 | 1        |

| SOVM              | Set overflow mode                                    | 1            | 1  | 1  | 0  | 0  | 1  | 1   | 1   | 0          | 0   | 0  | 0  | 0   | 0    | 0 | 1 | 1        |

| SST               | Store status register ST0                            | 1            | 0  | 1  | 1  | 1  | 1  | 0   | 0   | 0          | М   | 4  |    |     | - D- |   |   | →        |

| SST1 <sup>†</sup> | Store status register ST1                            | 1            | 0  | 1  | 1  | 1  | 1  | 0   | 0   | 1          | М   | •  |    |     | - D- |   |   | <b>→</b> |

| ssxm†             | Set sign-extension mode                              | 1            | 1  | 1  | 0  | 0  | 1  | 1   | 1   | 0          | 0   | 0  | 0  | 0   | 0    | 1 | 1 | 1        |

| STC <sup>‡</sup>  | Set test/control flag                                | 1            | 1  | 1  | 0  | 0  | 1  | 1   | 1   | 0          | 0   | 0  | 1  | 1   | 0    | 0 | 1 | 1        |

| TRAP†             | Software interrupt                                   | 1            | 1  | 1  | 0  | 0  | 1  | 1   | 1   | 0          | 0   | 0  | 0  | 1   | 1    | 1 | 1 | 0        |

$<sup>\</sup>dagger$  These instructions are not included in the TMS320C1x instruction set.

$<sup>\</sup>mbox{\ensuremath{\mbox{\footnote{1}}}}$  These instructions are not included in the TMS32020 instruction set.

### development systems and software support

Texas Instruments offers concentrated development support and complete documentation for designing an SMJ320C25-based microprocessor system. When developing an application, tools are provided to evaluate the performance of the processor, to develop the algorithm implementation, and to fully integrate the design's software and hardware modules. When questions arise, additional support can be obtained by calling the nearest Texas Instruments Regional Technology Center (RTC).

Sophisticated development operations are performed with the SMJ320C25 Macro Assembler/linker, Simulator, and Emulator (XDS). The macro assembler and linker are used to translate program modules into object code and link them together. This puts the program modules into a form which can be loaded into the SMJ320C25 Simulator or Emulator. The simulator provides a quick means for initially debugging SMJ320C25 software while the emulator provides the real-time in-circuit emulation necessary to perform system level debug efficiently.

Table 3 gives a complete list of SMJ320C25 software and hardware development tools.

Table 3. SMJ/SMJ320C25 Software and Hardware Support

|               | MACRO ASSEMBLERS/LINKERS |               |

|---------------|--------------------------|---------------|

| Host Computer | Operating System         | Part Number   |

| DECVAX        | VMS                      | TMDS324210-08 |