TLC59116F

SCLS714C -MARCH 2009-REVISED SEPTEMBER 2015

# TLC59116F 16-Channel Fast-Mode Plus I<sup>2</sup>C Bus LED Driver

#### **Features**

- 16 LED Drivers (Each Output Programmable at OFF, ON, LED Brightness, and Group Dimming/Blinking Mixed With Individual LED Brightness)

- 16 Open-Drain Output Channels

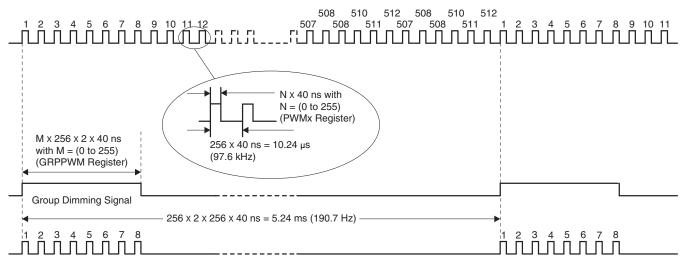

- 256-Step (8-Bit) Linear Programmable Brightness Per LED Output Varying From Fully OFF (Default) to Maximum Brightness Using a 97-kHz PWM Signal

- 256-Step Group Brightness Control Allows General Dimming (Using a 190-Hz PWM Signal From Fully OFF to Maximum Brightness (Default)

- 256-Step Group Blinking With Frequency Programmable From 24 Hz to 10.73 s and Duty Cycle from 0% to 99.6%

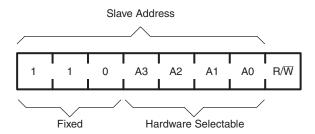

- Four Hardware Address Pins Allow 14 TLC59116F Devices to be Connected to the Same I<sup>2</sup>C Bus

- Four Software-Programmable I<sup>2</sup>C Bus Addresses (One LED Group Call Address and Three LED Sub-Call Addresses) Allow Groups of Devices to be Addressed Simultaneously in Any Combination (For example, One Register Used for 'All Call' So All the TLC59116Fs on the I2C Bus Can be Addressed at the Same Time and the Second Register Used for Three Different Addresses So That 1/3 of all Devices on the Bus Can Be Addressed at the Same Time in a Group). Software Enable and Disable for I<sup>2</sup>C Bus Address.

- Software Reset Feature (SWRST Call) Allows the Device to be Reset Through the I<sup>2</sup>C Bus

- Up to 14 Possible Hardware Adjustable Individual I<sup>2</sup>C Bus Addresses Per Device so That Each Device Can be Programmed

- Output State Change Programmable on the Acknowledge or the STOP Command to Update Outputs Byte-by-Byte or All at the Same Time (Default to Change on STOP).

- 120-mA Maximum Output Current

- 17-V Maximum Output Voltage

- 25-MHz Internal Oscillator Requires No External Components

- 1-MHz Fast-Mode Plus (FM+) Compatible I<sup>2</sup>C Bus Interface With 30 mA High Drive Capability on SDA Output for Driving High Capacity Buses

- Internal Power-On Reset

- Noise Filter on SCL/SDA Inputs

- No Glitch on Power Up

- Active-Low Reset

- Supports Hot Insertion

- Low Standby Current

- 3.3-V or 5-V Supply Voltage

- 5.5-V Tolerant Inputs

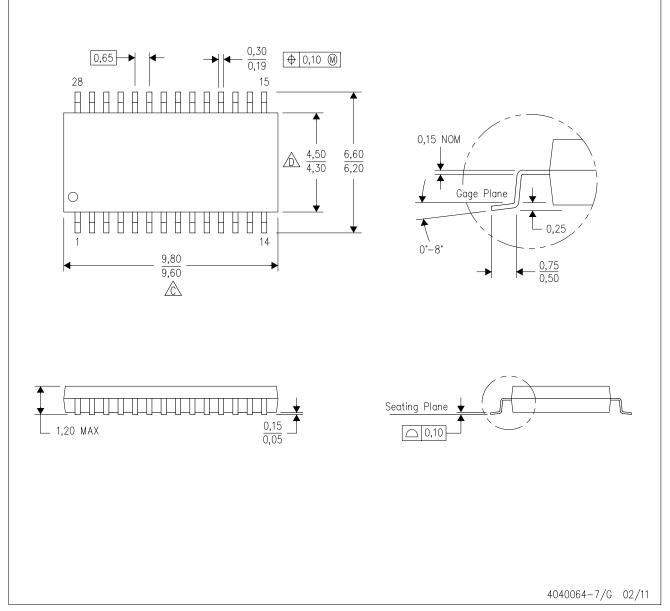

- 28-Pin TSSOP (PW)

- -40°C to 85°C Operation

### 2 Applications

- Gaming

- Small Signage

- Industrial Equipment

### 3 Description

The TLC59116F is an I<sup>2</sup>C-bus controlled 16-channel LED driver optimized for red/green/blue/amber (RGBA) color mixing applications. Each LED output has its own 8-bit resolution (256 steps) fixed frequency individual PWM controller that operates at 97 kHz with a duty cycle that is adjustable from 0% to 99.6% to allow the LED to be set to a specific brightness value. An additional 8-bit resolution (256 steps) group PWM controller has both a fixed frequency of 190 Hz and an adjustable frequency between 24 Hz to once every 10.73 seconds with a duty cycle that is adjustable from 0% to 99.6% that is used to either dim or blink all LEDs with the same value.

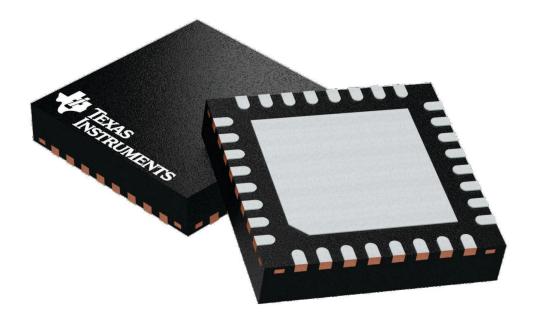

### Device Information (1)

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |  |

|-------------|------------|-------------------|--|

| TI 050446F  | TSSOP (28) | 9.70 mm × 4.40 mm |  |

| TLC59116F   | VQFN (32)  | 5.00 mm × 5.00 mm |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

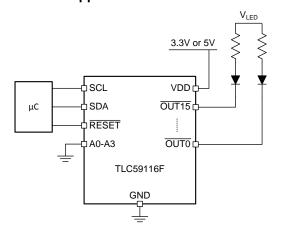

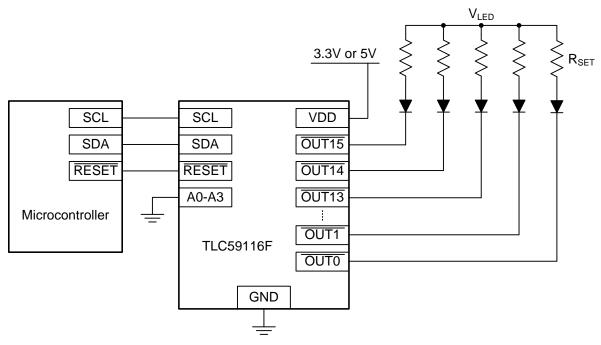

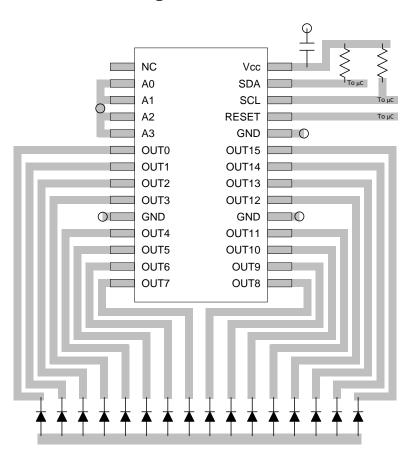

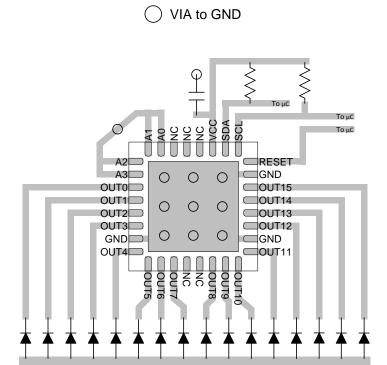

### **Application Schematic**

## **Table of Contents**

| Features 1                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8.3 Feature Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications 1               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8.4 Device Functional Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8.5 Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8.6 Register Maps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <del>-</del>                 | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Application and Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| _                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9.1 Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <mark>2</mark> :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| -                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9.2 Typical Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5                            | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Power Supply Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| •                            | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ·                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11.1 Layout Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11.2 Layout Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>2</u> 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Device and Documentation Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12.1 Community Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <mark>2</mark>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12.2 Trademarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12.3 Electrostatic Discharge Caution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12.4 Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8.2 Functional Block Diagram | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Mechanical, Packaging, and Orderable Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                              | Applications         1           Description         1           Revision History         2           Pin Configuration and Functions         3           Specifications         4           6.1 Absolute Maximum Ratings         4           6.2 ESD Ratings         4           6.3 Recommended Operating Conditions         4           6.4 Thermal Information         4           6.5 Electrical Characteristics         5           6.6 I <sup>2</sup> C Interface Bus Timing Requirements         6           6.7 Typical Characteristics         7           Parameter Measurement Information         7           Detailed Description         9           8.1 Overview         9 | Applications       1         Description       1         Revision History       2         Pin Configuration and Functions       3         Specifications       4         6.1 Absolute Maximum Ratings       4         6.2 ESD Ratings       4         6.3 Recommended Operating Conditions       4         6.4 Thermal Information       4         6.5 Electrical Characteristics       5         6.6 I²C Interface Bus Timing Requirements       6         6.7 Typical Characteristics       7         Parameter Measurement Information       7         Detailed Description       9         8.1 Overview       9 | Applications 1 8.4 Device Functional Modes.  Description 1 8.5 Programming.  Revision History 2 8.6 Register Maps.  Pin Configuration and Functions 3 9 Application and Implementation 9.1 Application Information.  6.1 Absolute Maximum Ratings 4 9.2 Typical Application 1.2 Device and Documentation 9.1 Layout Examples.  6.3 Recommended Operating Conditions 4 11 Layout Examples.  6.4 Thermal Information 4 11.1 Layout Guidelines 11.2 Layout Examples.  6.6 I²C Interface Bus Timing Requirements 6 12 Device and Documentation Support 12.1 Community Resources.  Parameter Measurement Information 7 12.2 Trademarks 12.3 Electrostatic Discharge Caution 12.4 Glossary 12.4 Glossary 12.4 Glossary 13 Mechanical, Packaging, and Orderable |

### 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Cr | nanges from Revision B (July 2011) to Revision C                                                                                                                                                                                                                                                                             | Page |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section | 1    |

| •  | Removed Thermal Impedence table from Specifications                                                                                                                                                                                                                                                                          | 5    |

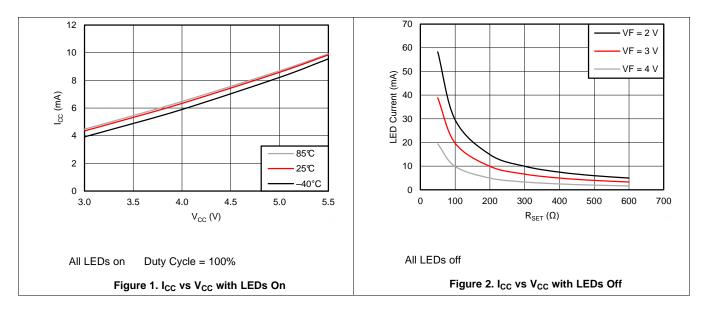

| •  | Added Figure 1 and Figure 2 to Typical Characteristics                                                                                                                                                                                                                                                                       | 6    |

| •  | Removed Figure 9 from Control Register.                                                                                                                                                                                                                                                                                      | 16   |

| •  | Added Figure 22 and Figure 23 to Layout Examples                                                                                                                                                                                                                                                                             | 26   |

|    |                                                                                                                                                                                                                                                                                                                              |      |

| Ch | nanges from Revision A (June 2010) to Revision B                                                                                                                                                                                                                                                                             | Page |

Submit Documentation Feedback

Copyright © 2009–2015, Texas Instruments Incorporated

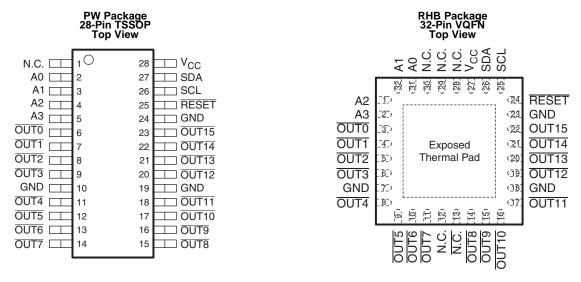

## 5 Pin Configuration and Functions

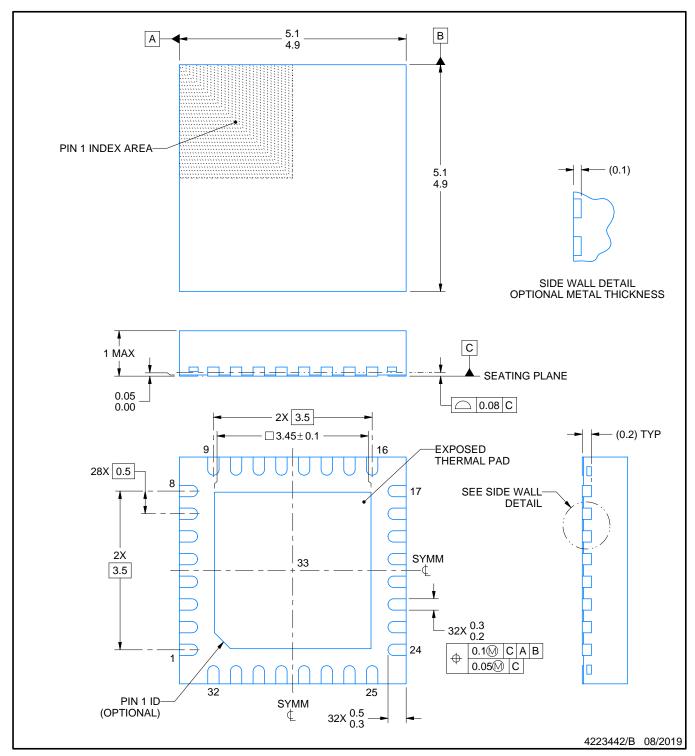

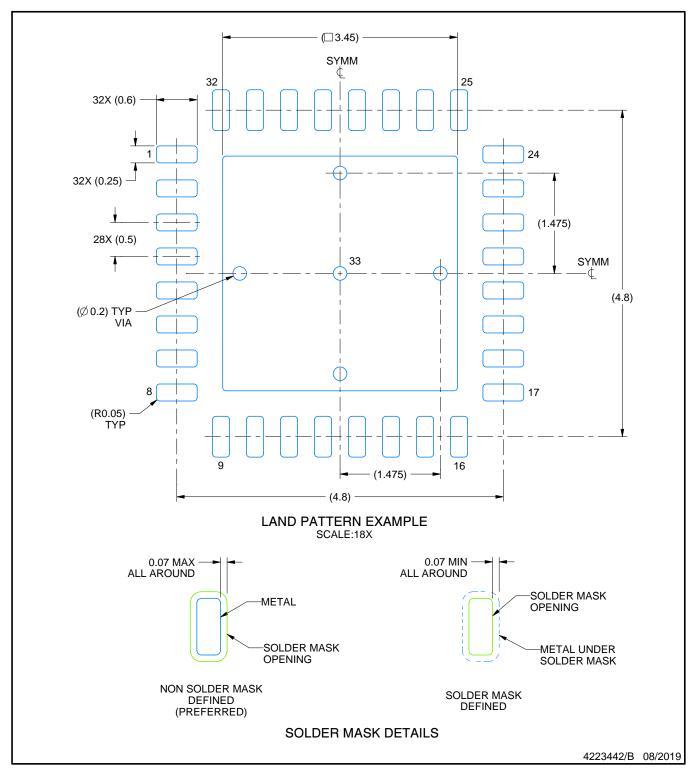

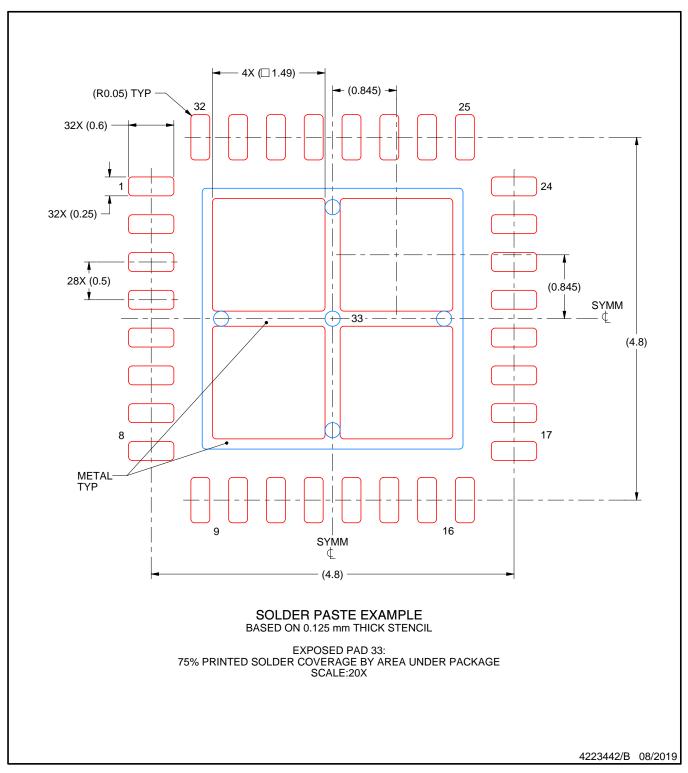

If used, the exposed thermal pad must be connected as a secondary ground. N.C. – No internal connection

#### **Pin Functions**

| PIN             |                    |            |     | PEOGRAPHICA                               |

|-----------------|--------------------|------------|-----|-------------------------------------------|

| NAME            | QFN (RHB)          | TSSOP (PW) | I/O | DESCRIPTION                               |

| A0              | 31                 | 2          | I   | Address input 0                           |

| A1              | 32                 | 3          | I   | Address input 1                           |

| A2              | 1                  | 4          | I   | Address input 2                           |

| A3              | 2                  | 5          | I   | Address input 3                           |

| GND             | 7, 18, 23          | 10, 19, 24 | _   | Power ground                              |

| N.C.            | 12, 13, 28, 29, 30 | 1          | -   | No internal connection                    |

| OUT0            |                    |            |     |                                           |

| OUT1            | 3–6                | 6–9        | 0   | On an ideal autout 0 to 2 LED ON at law   |

| OUT2            | 3-6                | 0–9        |     | Open-drain output 0 to 3, LED ON at low   |

| OUT3            |                    |            |     |                                           |

| OUT4            |                    |            |     |                                           |

| OUT5            | 8–11               | 11–14      | 0   | Open drain autout 4 to 7 LED ON at law    |

| OUT6            | 0-11               | 11-14      |     | Open-drain output 4 to 7, LED ON at low   |

| OUT7            |                    |            |     |                                           |

| OUT8            |                    |            |     |                                           |

| OUT9            | 14–17              | 15–18      | 0   | Open drain output 9 to 11 LED ON at low   |

| OUT10           | 14-17              | 10-10      |     | Open-drain output 8 to 11, LED ON at low  |

| OUT11           |                    |            |     |                                           |

| OUT12           |                    |            |     |                                           |

| OUT13           | 19–22              | 20–23      | 0   | Open drain output 12 to 15 LED ON at law  |

| OUT14           | 19–22              | 20–23      | 0   | Open-drain output 12 to 15, LED ON at low |

| OUT15           |                    |            |     |                                           |

| RESET           | 24                 | 25         | I   | Active-low reset input                    |

| SCL             | 25                 | 26         | I   | Serial clock input                        |

| SDA             | 26                 | 27         | I/O | Serial data input/output                  |

| V <sub>CC</sub> | 27                 | 28         | -   | Power supply                              |

### 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (see (1))

|                  |                                                      |            | MIN  | MAX | UNIT |

|------------------|------------------------------------------------------|------------|------|-----|------|

| $V_{CC}$         | Supply voltage                                       |            | 0    | 7   | ٧    |

| VI               | Input voltage                                        |            | -0.4 | 7   | V    |

| Vo               | Output voltage                                       |            | -0.5 | 20  | V    |

| Io               | Continuous output current per channel                |            |      | 120 | mA   |

| P <sub>D</sub>   | Power dissipation (T <sub>A</sub> = 25°C, JESD 51-7) | PW package |      | 1.6 | W    |

| TJ               | Junction temperature                                 |            | -40  | 150 | °C   |

| T <sub>stg</sub> | Storage temperature                                  |            | -55  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                                            |                                                        |                                                                     | VALUE | UNIT     |

|--------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------|-------|----------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1) | ±1500                                                               | .,    |          |

|                                            | discharge                                              | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | <b>v</b> |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted) (see (1))

|                                          |                                |                    |                                 | MIN                   | MAX                 | UNIT       |

|------------------------------------------|--------------------------------|--------------------|---------------------------------|-----------------------|---------------------|------------|

| V <sub>CC</sub>                          | Supply voltage                 |                    |                                 | 3                     | 5.5                 | V          |

| $V_{IH}$                                 | High-level input voltage       | SCL, SDA, RESET, A | 0, A1, A2, A3                   | V <sub>CC</sub> × 0.7 | V <sub>CC</sub>     | V          |

| $V_{IL}$                                 | Low-level input voltage        | SCL, SDA, RESET, A | SCL, SDA, RESET, A0, A1, A2, A3 |                       | $V_{CC} \times 0.3$ | V          |

| $V_{O}$                                  | Output voltage                 | OUT0-OUT15         | OUT0-OUT15                      |                       | 17                  | V          |

|                                          | Low level output ourrent       | SDA                | $V_{CC} = 3 V$                  |                       | 20                  | <b>~</b> ∧ |

| I <sub>OL</sub> Low-level output current |                                | SDA                | $V_{CC} = 5 V$                  |                       | 30                  | mA         |

| lo                                       | Output current per channel     | OUT0-OUT15         |                                 |                       | 120                 | mA         |

| T <sub>A</sub>                           | Operating free-air temperature |                    |                                 | -40                   | 85                  | °C         |

<sup>(1)</sup> All unused inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation.

#### 6.4 Thermal Information

|                      |                                              | TLC5       | TLC59116F  |      |  |  |

|----------------------|----------------------------------------------|------------|------------|------|--|--|

|                      | THERMAL METRIC (1)                           | PW (TSSOP) | RHB (VQFN) | UNIT |  |  |

|                      |                                              | 28 PINS    | 32 PINS    |      |  |  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 78         | 34.4       | °C/W |  |  |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 18.8       | 26.3       | °C/W |  |  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 36         | 8.3        | °C/W |  |  |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | 0.5        | 0.4        | °C/W |  |  |

| ΨЈВ                  | Junction-to-board characterization parameter | 35.5       | 8.2        | °C/W |  |  |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | _          | 3.3        | °C/W |  |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.5 Electrical Characteristics

$V_{CC} = 3 \text{ V to } 5.5 \text{ V}, T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C} \text{ (unless otherwise noted)}$

|                  | PARA                         | METER                                 | TEST CONDITIONS                                   | MIN | TYP (1) | MAX  | UNIT |

|------------------|------------------------------|---------------------------------------|---------------------------------------------------|-----|---------|------|------|

| IL               | Input/output leakage current | SCL, SDA,<br>A0, A1, A2, A3,<br>RESET | V <sub>I</sub> = V <sub>CC</sub> or GND           |     |         | ±0.3 | μΑ   |

|                  | Output leakage current       | OUT0-OUT15                            | $V_O = 17 \text{ V}, T_J = 25^{\circ}\text{C}$    |     |         | 0.5  | μΑ   |

| V <sub>POR</sub> | Power-on reset voltage       |                                       |                                                   |     | 2.5     |      | V    |

|                  | Low-level output             | CDA                                   | V <sub>CC</sub> = 3 V, V <sub>OL</sub> = 0.4 V    | 20  |         |      | A    |

| l <sub>OL</sub>  | current                      | SDA                                   | $V_{CC} = 5 \text{ V}, V_{OL} = 0.4 \text{ V}$    | 30  |         |      | mA   |

| V                | Low-level output             | OUT0-OUT15                            | $V_{CC} = 3 \text{ V}, I_{OL} = 120 \text{ mA}$   |     | 200     | 450  | mV   |

| $V_{OL}$         | voltage                      | 0010-00115                            | $V_{CC} = 4.5 \text{ V}, I_{OL} = 120 \text{ mA}$ |     | 175     | 400  | mv   |

| _                | On registeres                | OUT0-OUT15                            | V <sub>CC</sub> = 3 V, I <sub>OL</sub> = 120 mA   |     | 1.67    | 3.75 | 0    |

| r <sub>ON</sub>  | On resistance                | 0010-00115                            | $V_{CC} = 4.5 \text{ V}, I_{OL} = 120 \text{ mA}$ |     | 1.46    | 3.3  | Ω    |

| T <sub>SD</sub>  | Overtemperature shutdo       | wn <sup>(2)</sup>                     |                                                   | 150 | 175     | 200  | °C   |

| T <sub>HYS</sub> | Restart hysteresis           |                                       |                                                   |     | 15      |      | °C   |

| Ci               | Input capacitance            | SCL, A0, A1, A2, A3, RESET            | V <sub>I</sub> = V <sub>CC</sub> or GND           |     | 5       |      | pF   |

| C <sub>io</sub>  | Input/output capacitance     | SDA                                   | V <sub>I</sub> = V <sub>CC</sub> or GND           |     | 8       |      | pF   |

| I <sub>CC</sub>  | Supply current               | OUT0-OUT15 = OFF                      | V <sub>CC</sub> = 5.5 V                           |     |         | 13   | mA   |

<sup>(1)</sup> All typical values are at T<sub>J</sub> = 25°C.

(2) Specified by design; not production tested.

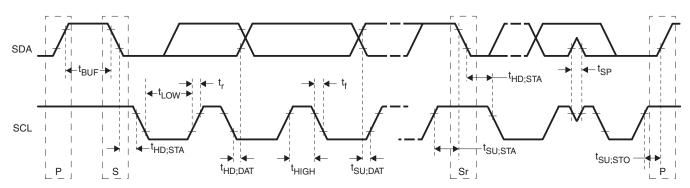

### 6.6 I<sup>2</sup>C Interface Bus Timing Requirements

$T_{\Lambda} = -40^{\circ}\text{C}$  to 85°C

| PARAMETER              |                                                                                  | STANDARD<br>I <sup>2</sup> C BU |      | FAST-MODE<br>I <sup>2</sup> C BUS     |     | FAST-MODE PLUS<br>I <sup>2</sup> C BUS |      | UNIT |

|------------------------|----------------------------------------------------------------------------------|---------------------------------|------|---------------------------------------|-----|----------------------------------------|------|------|

|                        |                                                                                  |                                 | MAX  | MIN                                   | MAX | MIN                                    | MAX  |      |

| I <sup>2</sup> C Inter | face                                                                             |                                 | •    |                                       | ٠   |                                        |      |      |

| f <sub>SCL</sub>       | SCL clock frequency                                                              | 0                               | 100  | 0                                     | 400 | 0                                      | 1000 | kHz  |

| t <sub>BUF</sub>       | Bus free time between a STOP and START condition                                 | 4.7                             |      | 1.3                                   |     | 0.5                                    |      | μs   |

| t <sub>HD;STA</sub>    | Hold time (repeated) START condition                                             | 4                               |      | 0.6                                   |     | 0.26                                   |      | μs   |

| t <sub>SU;STA</sub>    | Set-up time for a (repeated) START condition                                     | 1.7                             |      | 0.6                                   |     | 0.26                                   |      | μs   |

| t <sub>SU;STO</sub>    | Set-up time for STOP condition                                                   | 4                               |      | 0.6                                   |     | 0.26                                   |      | μs   |

| t <sub>HD;DAT</sub>    | Data hold time                                                                   | 0                               |      | 0                                     |     | 0                                      |      | ns   |

| t <sub>VD;ACK</sub>    | Data valid acknowledge time (1)                                                  | 0.3                             | 3.45 | 0.1                                   | 0.9 | 0.05                                   | 0.45 | μs   |

| t <sub>VD;DAT</sub>    | Data valid time (2)                                                              | 0.3                             | 3.45 | 0.1                                   | 0.9 | 0.05                                   | 0.45 | μs   |

| t <sub>SU;DAT</sub>    | Data set-up time                                                                 | 250                             |      | 100                                   |     | 50                                     |      | ns   |

| $t_{LOW}$              | Low period of the SCL clock                                                      | 4.7                             |      | 1.3                                   |     | 0.5                                    |      | μs   |

| t <sub>HIGH</sub>      | High period of the SCL clock                                                     | 4                               |      | 0.6                                   |     | 0.26                                   |      | μs   |

| t <sub>f</sub>         | Fall times of both SDA and SCL signals (3) (4)                                   |                                 | 300  | 20 + 0.1C <sub>b</sub> <sup>(5)</sup> | 300 |                                        | 120  | ns   |

| t <sub>r</sub>         | Rise time of both SDA and SCL signals                                            |                                 | 1000 | 20 + 0.1C <sub>b</sub> <sup>(5)</sup> | 300 |                                        | 120  | ns   |

| t <sub>SP</sub>        | Pulse width of spikes that must be suppressed by the input filter <sup>(6)</sup> |                                 | 50   |                                       | 50  |                                        | 50   | ns   |

| Reset                  |                                                                                  | •                               | *    |                                       | *   |                                        | *    |      |

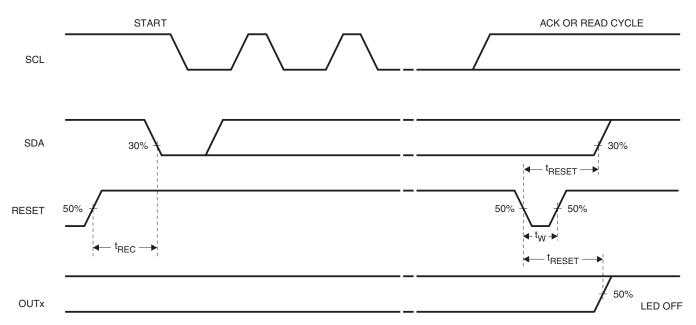

| t <sub>W</sub>         | Reset pulse width                                                                | 10                              |      | 10                                    |     | 10                                     |      | ns   |

| t <sub>REC</sub>       | Reset recovery time                                                              | 0                               |      | 0                                     |     | 0                                      |      | ns   |

| t <sub>RESET</sub>     | Time to reset (7) (8)                                                            | 400                             |      | 400                                   |     | 400                                    |      | ns   |

- (1)  $t_{VD;ACK}$  = time for acknowledgment signal from SCL low to SDA (out) low.

- (2)  $t_{VD;DAT}$  = minimum time for SDA data out to be valid following SCL low.

- (3) A master device must internally provide a hold time of at least 300 ns for the SDA signal (refer to the V<sub>IL</sub> of the SCL signal) in order to bridge the undefined region of SCL's falling edge.

- (4) The maximum t<sub>f</sub> for the SDA and SCL bus lines is specified at 300 ns. The maximum fall time (t<sub>f</sub>) for the SDA output stage is specified at 250 ns. This allows series protection resistors to be connected between the SDA and the SCL pins and the SDA/SCL bus lines without exceeding the maximum specified t<sub>f</sub>.

- (5) C<sub>b</sub> = total capacitance of one bus line in pF.

- (6) Input filters on the SDA and SCL inputs suppress noise spikes less than 50 ns.

- (7) Resetting the device while actively communicating on the bus may cause glitches or errant STOP conditions.

- (8) Upon reset, the full delay will be the sum of t<sub>RESET</sub> and the RC time constant of the SDA bus.

Submit Documentation Feedback

Copyright © 2009–2015, Texas Instruments Incorporated

## 6.7 Typical Characteristics

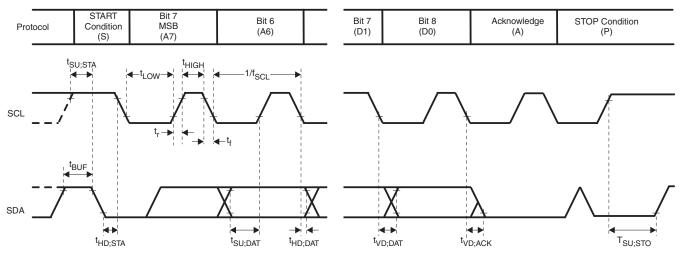

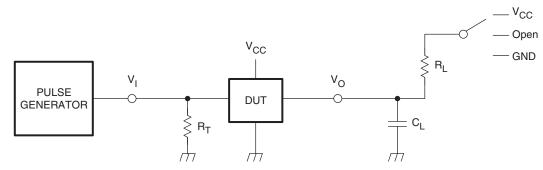

### 7 Parameter Measurement Information

Figure 3. Definition of RESET Timing

### **Parameter Measurement Information (continued)**

Figure 4. Definition of Timing

A. Rise and fall times refer to  $V_{IL}$  and  $V_{IH}$ .

Figure 5. I<sup>2</sup>C Bus Timing

- A. Load resistor,  $R_L$ , for SDA and SCL > 1 k $\Omega$  (3 mA or less current)

- B. Load capacitance, C<sub>L</sub>, includes jig and probe capacitance

- C. Termination resistance,  $R_T$ , should be equal to the output impedance  $Z_0$  of the pulse generators.

Figure 6. Test Circuit for Switching Characteristics

Submit Documentation Feedback

### 8 Detailed Description

#### 8.1 Overview

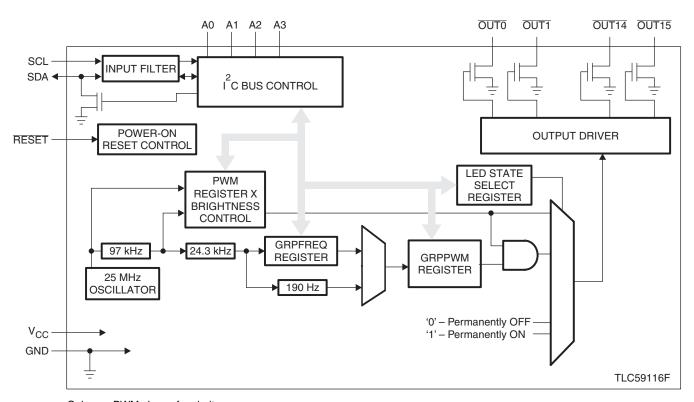

The TLC59116F is an I<sup>2</sup>C-bus controlled 16-channel LED driver optimized for red/green/blue/amber (RGBA) color mixing applications. Each LED output has its own 8-bit resolution (256 steps) fixed frequency individual PWM controller that operates at 97 kHz with a duty cycle that is adjustable from 0% to 99.6% to allow the LED to be set to a specific brightness value. An additional 8-bit resolution (256 steps) group PWM controller has both a fixed frequency of 190 Hz and an adjustable frequency between 24 Hz to once every 10.73 seconds with a duty cycle that is adjustable from 0% to 99.6% that is used to either dim or blink all LEDs with the same value.

Each LED output can be off, on (no PWM control), set at its individual PWM controller value or at both individual and group PWM controller values. The TLC59116F operates with a supply voltage range of 3 V to 5.5 V and the outputs are 17-V tolerant. LEDs can be directly connected to the TLC59116F device outputs.

Software programmable LED group and three sub call I<sup>2</sup>C bus addresses allow all or defined groups of TLC59116F devices to respond to a common I<sup>2</sup>C bus address, which allows, for example, all the same color LEDs to be turned on or off at the same time or marguee chasing effect, thus minimizing I<sup>2</sup>C bus commands.

Four hardware address pins allow up to 14 devices on the same bus.

The software reset (SWRST) call allows the master to perform a reset of the TLC59116F through the I<sup>2</sup>C bus, identical to the power-on reset (POR) that initializes the registers to their default state causing the outputs to be set high (LED off). This allows an easy and guick way to reconfigure all device registers to the same condition.

#### 8.2 Functional Block Diagram

Only one PWM shown for clarity.

#### 8.3 Feature Description

### 8.3.1 Power-On Reset (POR)

When power is applied to  $V_{CC}$ , an internal power-on reset holds the TLC59116F in a reset condition until  $V_{CC}$  reaches  $V_{POR}$ . At this point, the reset condition is released and the TLC59116F registers and  $I^2C$  bus state machine are initialized to their default states causing all the channels to be deselected. Thereafter,  $V_{CC}$  must be lowered below 0.2 V to reset the device.

#### 8.3.2 External Reset

A reset can be accomplished by holding the  $\overline{RESET}$  pin low for a minimum of  $t_W$ . The TLC59116F registers and  $I^2C$  state machine will be held in their default state until the  $\overline{RESET}$  input is once again high.

This input requires a pullup resistor to V<sub>CC</sub> if no active connection is used.

#### 8.3.3 Software Reset

The software reset call (SWRST Call) allows all the devices in the I<sup>2</sup>C bus to be reset to the power-up state value through a specific formatted I<sup>2</sup>C bus command. To be performed correctly, it implies that the I<sup>2</sup>C bus is functional and that there is no device hanging the bus.

The SWRST Call function is defined as the following:

- A START command is sent by the I<sup>2</sup>C bus master.

- The reserved SWRST I<sup>2</sup>C bus address '1101 011' with the R/W bit set to '0' (write) is sent by the I<sup>2</sup>C bus master.

- The TLC59116F device(s) acknowledge(s) after seeing the SWRST Call address '1101 0110' (D6h) only. If the R/W bit is set to '1' (read), no acknowledge is returned to the I<sup>2</sup>C bus master.

- Once the SWRST Call address has been sent and acknowledged, the master sends 2 bytes with 2 specific values (SWRST data byte 1 and byte 2):

- a. Byte1 = A5h: the TLC59116F acknowledges this value only. If byte 1 is not equal to A5h, the TLC59116F does not acknowledge it.

- b. Byte 2 = 5Ah: the TLC59116F acknowledges this value only. If byte 2 is not equal to 5Ah, the TLC59116F does not acknowledge it.

If more than 2 bytes of data are sent, the TLC59116F does not acknowledge any more.

Once the right 2 bytes (SWRST data byte 1 and byte 2 only) have been sent and correctly acknowledged, the

master sends a STOP command to end the SWRST Call: the TLC59116F then resets to the default value

(power-up value) and is ready to be addressed again within the specified bus free time (t<sub>BUF</sub>).

The I<sup>2</sup>C bus master must interpret a non-acknowledge from the TLC59116F (at any time) as a *SWRST Call Abort*. The TLC59116F does not initiate a reset of its registers. This happens only when the format of the START Call sequence is not correct.

#### 8.3.4 Individual Brightness Control With Group Dimming/Blinking

A 97-kHz fixed frequency signal with programmable duty cycle (8 bits, 256 steps) is used to control individually the brightness for each LED.

On top of this signal, one of the following signals can be superimposed (this signal can be applied to the 4 LED outputs):

- A lower 190-Hz fixed frequency signal with programmable duty cycle (8 bits, 256 steps) is used to provide a global brightness control.

- A programmable frequency signal from 24 Hz to 1/10.73 s (8 bits, 256 steps) is used to provide a global blinking control.

### **Feature Description (continued)**

Resulting Brightness + Group Dimming Signal

- A. Minimum pulse width for LEDn brightness control is 40 ns.

- B. Minimum pulse width for group dimming is 20.48 μs.

- C. When M = 1 (GRPPWM register value), the resulting LEDn brightness control and group dimming signal will have two pulses of the LED brightness control signal (pulse width = N x 40 ns, with N defined in the PWMx register).

- D. The resulting brightness plus group dimming signal shown above demonstrate a resulting control signal with M = 4 (8 pulses).

Figure 7. Brightness and Group Dimming Signals

#### 8.4 Device Functional Modes

#### **8.4.1** Active

Active mode occurs when one or more of the output channels is enabled.

#### 8.4.2 Standby

Standby mode occurs when all output channels are disabled. Standby mode may be entered either through I<sup>2</sup>C command or by pulling the RESET pin low.

### 8.5 Programming

#### 8.5.1 Device Address

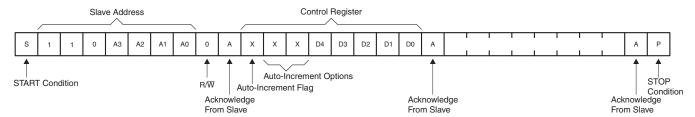

Following a START condition, the bus master outputs the address of the slave it is accessing.

#### 8.5.2 Regular I<sup>2</sup>C Bus Slave Address

The I<sup>2</sup>C bus slave address of the TLC59116F is shown in Figure 8. To conserve power, no internal pullup resistors are incorporated on the hardware-selectable address pins, and they must be pulled high or low.

For buffer management purpose, a set of sector information data should be stored in a certain buffer.

Figure 8. Slave Address

The last bit of the address byte defines the operation to be performed. When set to logic 1, a read is selected; a logic 0 selects a write operation.

### 8.5.3 LED All-Call I<sup>2</sup>C Bus Address

- Default power-up value (ALLCALLADR register): D0h or 1101 000

- Programmable through I<sup>2</sup>C bus (volatile programming)

- At power-up, LED All Call I<sup>2</sup>C bus address is enabled. TLC59116F sends an ACK when D0h ( $R/\overline{W} = 0$ ) or D1h ( $R/\overline{W} = 1$ ) is sent by the master.

See Register Descriptions for more details.

#### NOTE

The default LED all-call I<sup>2</sup>C bus address (D0h or 1101 000) must not be used as a regular I<sup>2</sup>C bus slave address since this address is enabled at power-up. All the TLC59116Fs on the I<sup>2</sup>C bus will acknowledge the address if sent by the I<sup>2</sup>C bus master.

### 8.5.4 LED Sub-Call I<sup>2</sup>C Bus Address

- Three different I<sup>2</sup>C bus addresses can be used.

- Default power-up values:

- SUBADR1 register: D2h or 1101 001

- SUBADR2 register: D4h or 1101 010

- SUBADR3 register: D8h or 1101 100

- Programmable through I<sup>2</sup>C bus (volatile programming)

- At power-up, sub-call I<sup>2</sup>C <u>bus</u> address is disabled. TLC59116<u>F</u> does not send an ACK when D2h (R/W = 0) or D3h (R/W = 1) or D4h (R/W = 0) or D5h (R/W = 1) or D8h (R/W = 0) or D9h (R/W = 1) is sent by the master.

See Register Descriptions for more details.

#### NOTE

The default LED Sub Call I<sup>2</sup>C bus address may be used as a regular I<sup>2</sup>C bus slave address as long as the Sub Call addresses are disabled in MODE1 (default).

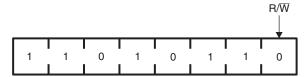

### 8.5.5 Software Reset I<sup>2</sup>C Bus Address

The address shown in Figure 9 is used when a reset of the TLC59116F needs to be performed by the master. The Software Reset address (SWRST Call) must be used with R/W = 0. If R/W = 1, the TLC59116F does not acknowledge the SWRST. See *Register Descriptions* for more details.

The software reset I<sup>2</sup>C bus address is reserved address and cannot be use as regular I<sup>2</sup>C bus slave address or as an LED All-Call or LED Sub-Call address.

Figure 9. Software Reset Address

#### 8.5.6 Characteristics of the I<sup>2</sup>C Bus

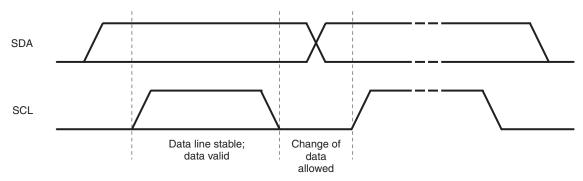

The I<sup>2</sup>C bus is for two-way, two-line communication between different ICs or modules. The two lines are a serial data line (SDA) and a serial clock line (SCL). Both lines must be connected to a positive supply through a pullup resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

#### 8.5.6.1 Bit Transfer

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the high period of the clock pulse as changes in the data line at this time will be interpreted as control signals (see Figure 10).

Figure 10. Bit Transfer

#### 8.5.6.2 START and STOP Conditions

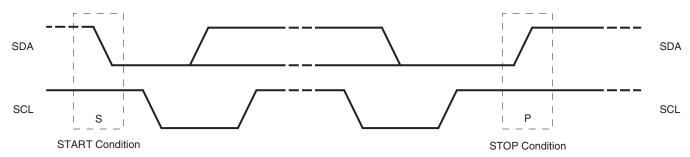

Both data and clock lines remain high when the bus is not busy. A high-to-low transition of the data line while the clock is high is defined as the START condition (S). A low-to-high transition of the data line while the clock is high is defined as the STOP condition (P) (see Figure 11).

Figure 11. Definition of START and STOP Conditions

Copyright © 2009–2015, Texas Instruments Incorporated

#### 8.5.6.3 System Configuration

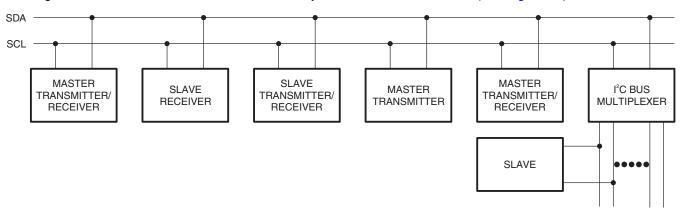

A device generating a message is a transmitter; a device receiving is the receiver. The device that controls the message is the master and the devices controlled by the master are the slaves (see Figure 12).

Figure 12. System Configuration

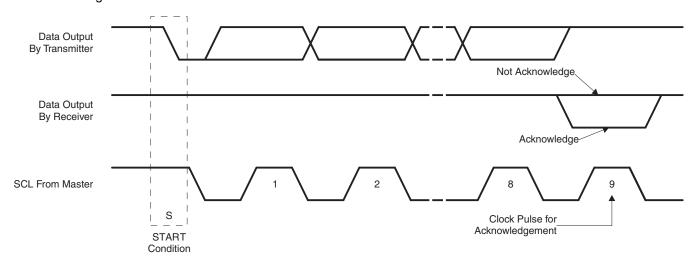

### 8.5.6.4 Acknowledge

The number of data bytes transferred between the START and the STOP conditions from transmitter to receiver is not limited. Each byte of eight bits is followed by one acknowledge bit. The acknowledge bit is a high level put on the bus by the transmitter, whereas the master generates an extra acknowledge related clock pulse.

A slave receiver which is addressed must generate an acknowledge after the reception of each byte. Also a master must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse, so that the SDA line is stable low during the high period of the acknowledge related clock pulse; set-up time and hold time must be taken into account.

A master receiver must signal an end of data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event, the transmitter must leave the data line high to enable the master to generate a STOP condition.

Figure 13. Acknowledge on the I<sup>2</sup>C Bus

Submit Documentation Feedback

Figure 14. Write to a Specific Register

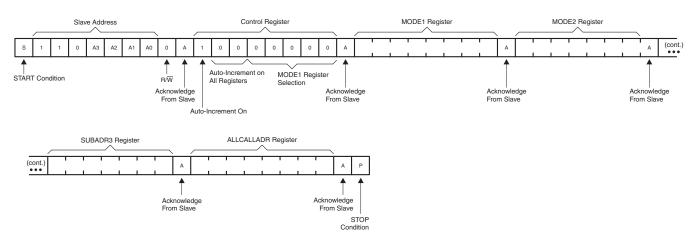

Figure 15. Write to All Registers Using the Auto-Increment Feature

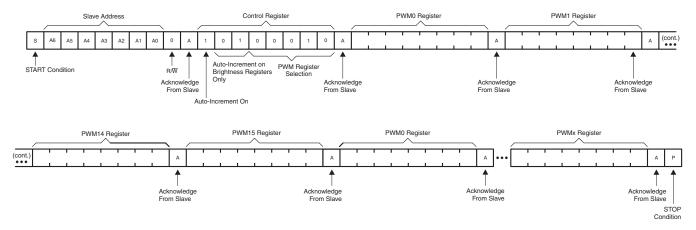

Figure 16. Multiple Writes to Individual Brightness Registers Only Using the Auto-Increment Feature

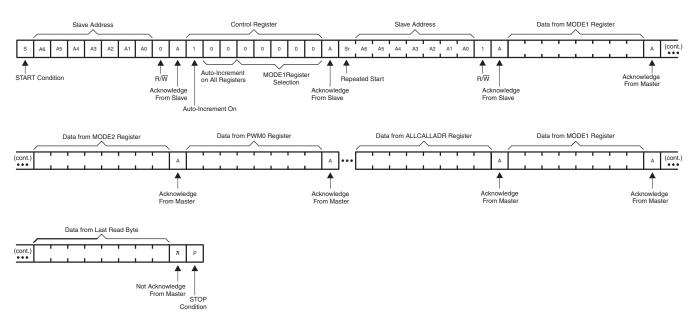

Figure 17. Read All Registers With the Auto-Increment Feature

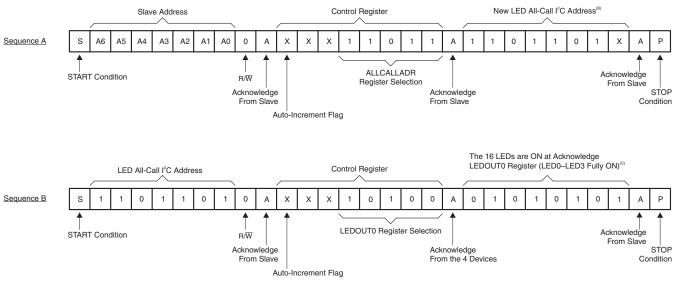

- A. In this example, four TLC59116Fs are used with the same sequence sent to each.

- B. ALLCALL bit in MODE1 register is equal to 1 for this example.

- C. OCH bit in MODE2 register is equal to 1 for this example.

Figure 18. LED All-Call I<sup>2</sup>C Bus Address Programming and LED All-Call Sequence Example

### 8.6 Register Maps

### 8.6.1 Control Register

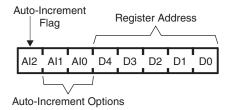

Following the successful acknowledgment of the slave address, LED All Call address or LED Sub Call address, the bus master will send a byte to the TLC59116F, which will be stored in the Control register. The lowest 5 bits are used as a pointer to determine which register will be accessed (D[4:0]). The highest three bits are used as Auto-Increment flag and Auto-Increment options (Al[2:0]).

### **Register Maps (continued)**

Figure 19. Control Register

When the Auto-Increment flag is set (AI2 = logic 1), the five low order bits of the Control register are automatically incremented after a read or write. This allows the user to program the registers sequentially. Four different types of Auto-Increment are possible, depending on AI1 and AI0 values.

**PIN DESCRIPTION** AI2 AI1 AI0 0 0 0 No auto-increment Auto-increment for all registers. D[4:0] roll over to 0 0000 after the last 1 0 0 register (1 1011) is accessed. Auto-increment for individual brightness registers only. D[4:0] roll over 1 0 1 to 0 0010 after the last register (1 0001) is accessed. Auto-increment for global control registers only. D[4:0] roll over to 1 1 1 n 0010 after the last register (1 0011) is accessed. Auto-increment for individual and global control registers only. D[4:0] 1 1 roll over to 0 0010 after the last register (1 0011) is accessed.

Table 1. Auto-Increment Options (1)