Sample &

Buv

TPS65400-Q1

SLVSCQ2-JULY 2015

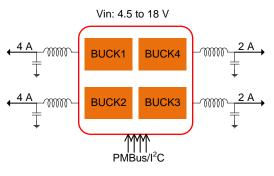

# TPS65400-Q1 4.5- to 18-V Input Flexible Power Management Unit With PMBus/I<sup>2</sup>C Interface

Technical

Documents

#### 1 Features

- **Qualified for Automotive Applications**

- AEC-Q100 Qualified With the Following Results:

- Device Temperature Grade 1: -40°C to 125°C Ambient Operating Temperature Range

- Device HBM ESD Classification Level H2

- Device CDM ESD Classification Level C4B

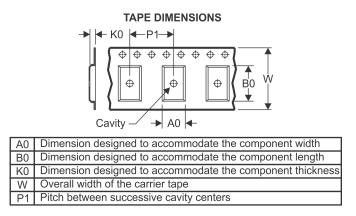

- Efficiency up to 95% for Each Switching Regulator

- Switching Regulator Specifications:

- Input Voltage Range: 4.5 to 18 V

- Vout Range: 0.6 V-90%Vin

- SW1, SW2 lout: 4-A Max

- SW3, SW4 lout: 2-A Max

- Pre-Bias Startup Algorithm Minimizes Voltage Dip **During Startup**

- Internal Undervoltage Lockout (UVLO), Overcurrent Protection (OCP), Overvoltage Protection (OVP), and Overtemperature Protection (OTP)

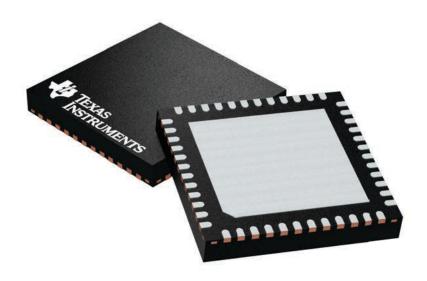

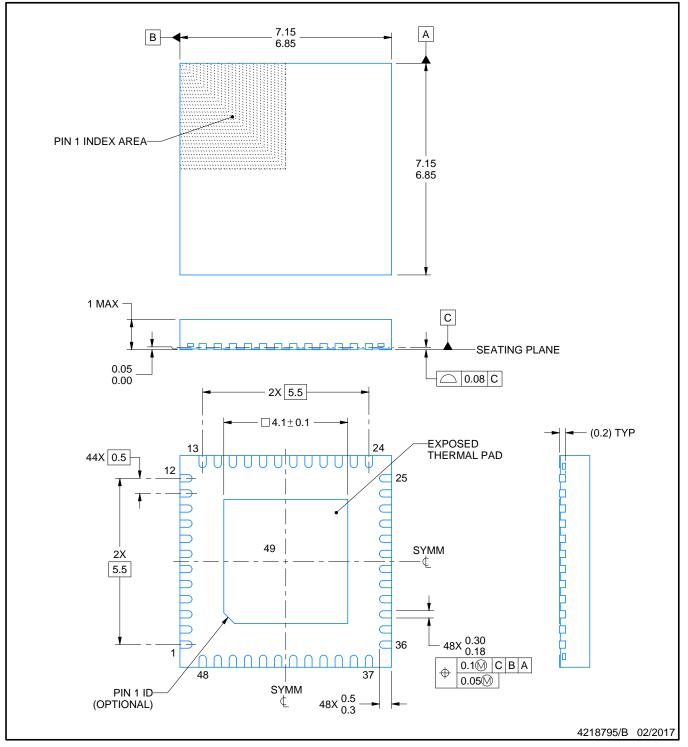

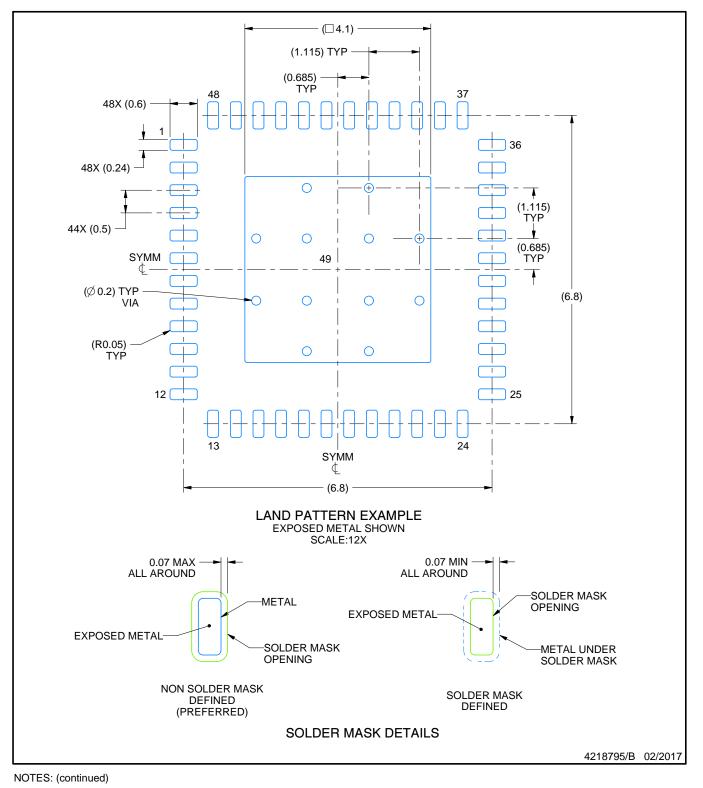

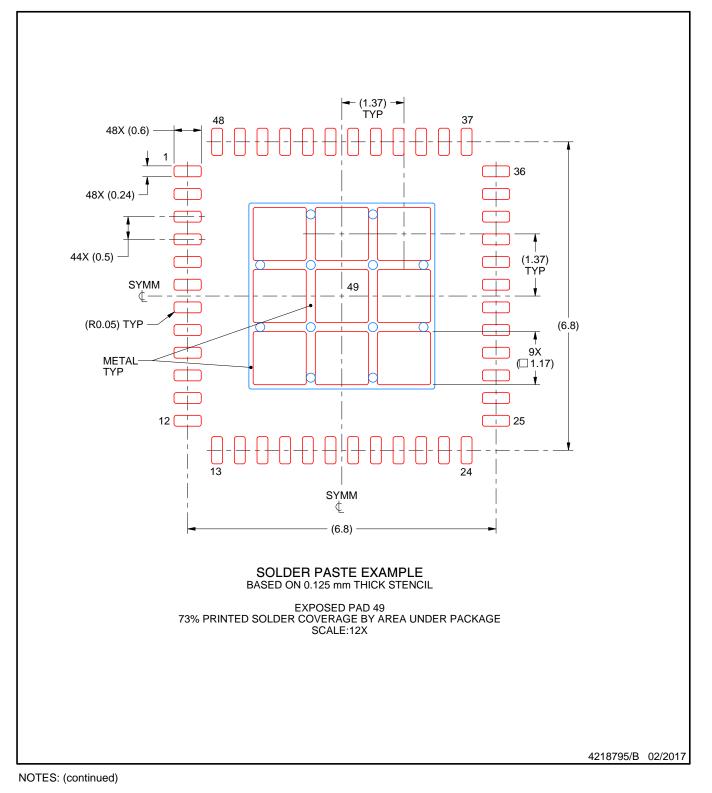

- Thermally-Enhanced 7-mm × 7-mm 48-Pin, 0.5mm Pitch VQFN Package

- Pin Accessible Features:

- Adjustable VOUT With External Feedback Resistors

- Sequencing Control Through Precision Enable Pins for Each Switcher

- Resistor Adjustable PWM Switching Frequency \_ from 275 kHz to 2.2 MHz

- Clock Sync Input and Clock Output

- Soft-Start Delay Through External Capacitor

- Current Sharing Between SW1 and SW2 and Between SW3 and SW4 Allows Support of Higher Current Needs if Required

- **PMBus Runtime Control and Status**

- Runtime Voltage Positioning Through Adjustment of VRFF

- Enable and Disable of Each Switcher

- Fault and Status Monitoring

- User-Configurable PMBus / I<sup>2</sup>C Options, Saved in EEPROM

- Power Supply Turn-On and Turn-Off Sequencing

- Sequencing can be Based on Fixed Time **Delays or PGOOD Dependence**

- Initial Voltage Positioning Through VREF Configuration

PWM Frequency Adjustment for Each Switcher

Support &

Community

20

- Individual PWM Phase Alignment for Each Switcher to Minimize Ripple and Capacitor Size

- Adjustable Current Limit on Each Regulator Enables Size and Cost Optimization of Inductors

- Soft-Start Time

Tools &

Software

# 2 Applications

- **Qualified for Automotive Applications** ٠

- Small Cellular Base Stations (BTS) (for Example: Picocells and Microcells); Macro BTS (Using Multiple PMUs)

- Power over Ethernet (PoE) Powered **Communications Infrastructure Equipment**

- Powering DSP and MCUs

- Industrial and Factory Automation

- Systems Requiring Small Form Factor, High-Efficiency, High-Ambient Operating Temperature, and Flexible Power Management

# 3 Description

The TPS65400-Q1 is an integrated PMU optimized for applications requiring small form factor and high power conversion efficiency, enabling small spaceconstrained equipment with high ambient operating temperature without cooling. It provides high-power efficiency at a system level by enabling a single stage conversion from an intermediate distribution bus with an optimized combination of regulators.

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |

|-------------|-----------|-------------------|--|

| TPS65400-Q1 | VQFN (48) | 7.00 mm × 7.00 mm |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

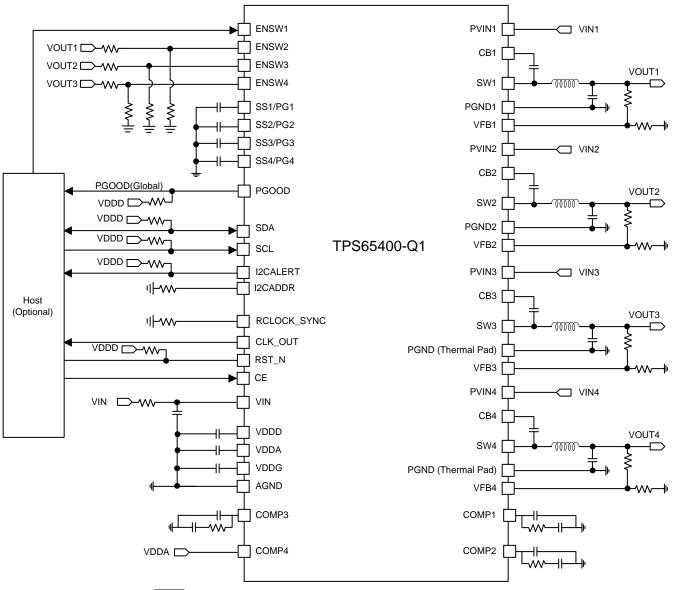

## **Simplified Schematic**

# **Table of Contents**

| 1 | Feat | tures                                      | 1    |

|---|------|--------------------------------------------|------|

| 2 | Арр  | lications                                  | 1    |

| 3 | Des  | cription                                   | 1    |

| 4 | Rev  | ision History                              | 2    |

| 5 | Des  | cription (continued)                       | 3    |

| 6 | Pin  | Configuration and Functions                | 3    |

| 7 | Spe  | cifications                                | 5    |

|   | 7.1  | Absolute Maximum Ratings                   | 5    |

|   | 7.2  | ESD Ratings                                | 5    |

|   | 7.3  | Recommended Operating Conditions           | 5    |

|   | 7.4  | Thermal Information                        | 6    |

|   | 7.5  | Electrical Characteristics                 | 7    |

|   | 7.6  | System Characteristics                     | 9    |

|   | 7.7  | Operational Parameters                     | 9    |

|   | 7.8  | Package Dissipation Ratings                | 9    |

|   | 7.9  | Typical Characteristics: System Efficiency | . 10 |

| 8 | Deta | ailed Description                          |      |

|   | 8.1  | Overview                                   | . 11 |

|   |      |                                            |      |

|    | 8.2  | Functional Block Diagrams         | 12              |

|----|------|-----------------------------------|-----------------|

|    | 8.3  | Feature Description               | 13              |

|    | 8.4  | Device Functional Modes           | 27              |

|    | 8.5  | Register Maps                     | 29              |

| 9  | App  | lication and Implementation       | 54              |

|    | 9.1  | Application Information           | 54              |

|    | 9.2  | Typical Applications              | 55              |

| 10 | Pow  | er Supply Recommendations         | <mark>66</mark> |

| 11 | Lay  | out                               | <mark>66</mark> |

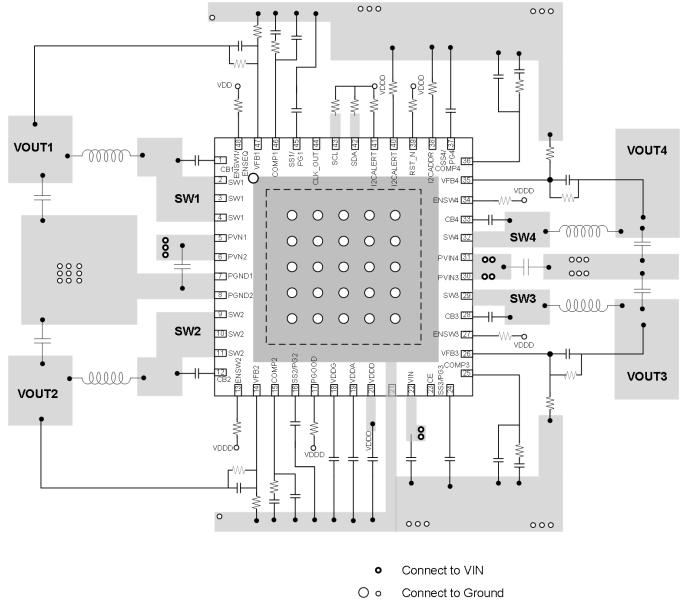

|    | 11.1 | Layout Guidelines                 | 66              |

|    | 11.2 | Layout Example                    | 67              |

| 12 | Dev  | ice and Documentation Support     | <mark>68</mark> |

|    | 12.1 | Documentation Support             | 68              |

|    | 12.2 | Community Resources               | 68              |

|    | 12.3 | Trademarks                        | 68              |

|    | 12.4 | Electrostatic Discharge Caution   | <mark>68</mark> |

|    | 12.5 | Glossary                          | 68              |

| 13 | Мес  | hanical, Packaging, and Orderable |                 |

|    |      | mation                            | <mark>68</mark> |

|    |      |                                   |                 |

# 4 Revision History

| DATE      | REVISION | NOTES            |

|-----------|----------|------------------|

| July 2015 | *        | Initial release. |

## **5** Description (continued)

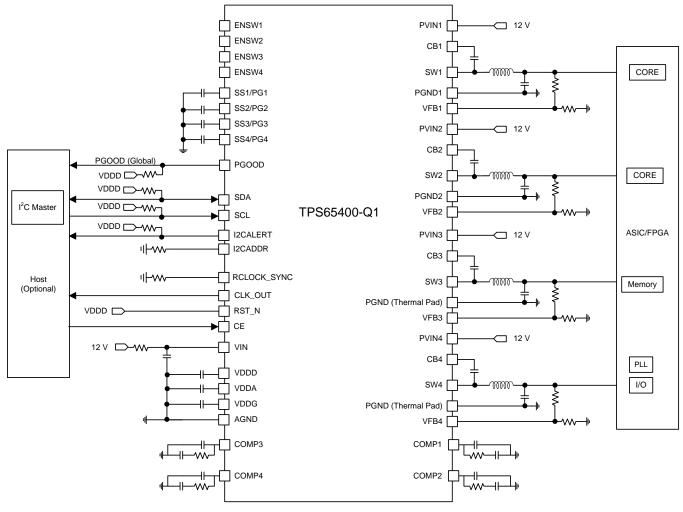

TPS65400-Q1 implements a PMBus-I<sup>2</sup>C-compatible digital interface. It helps Core Chip optimize system performance by runtime changing regulated voltage, power sequence, phase interleaving, operating frequency, read back operating status, and so forth.

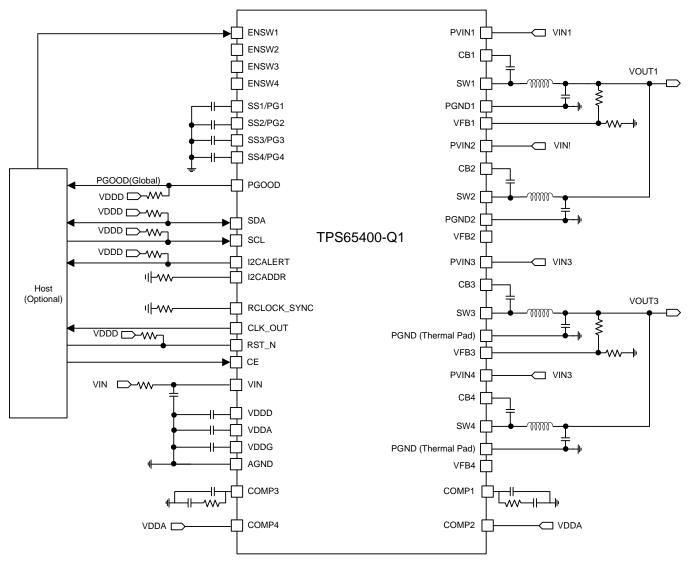

The TPS65400-Q1 consists of four high-current buck switching regulators (SW1, SW2, SW3, and SW4) with integrated FETs. The switching power supplies are intended for powering high-current digital circuits such as the processor, FPGA, ASIC, memory, and digital I/Os. SW1 and SW2 support 4 A each, and SW3 and SW4 support 2 A each. Each regulator's switching frequency is independently adjustable up to 2.2 MHz.

Current limit programmability on each switcher enables optimization of inductor ratings for a particular application configuration not requiring the maximum current capability.

The TPS65400-Q1 can be powered from a single-input voltage rail between 4.5 and 18 V, making it suitable for applications running off a 5- or 12-V intermediate power distribution bus.

Sequencing requirements can be met using the individual enable terminals or by programming the sequence through the  $I^2C$  bus into the onboard EEPROM. Output voltages can be set through external resistor networks and VREF can be programmed from 0.6 to 1.87 V in 10-mV steps. All control and status info can be accessed through a PMBus-compatible  $I^2C$  bus.

The TPS65400-Q1 provides a high level of flexibility for monitoring and control through the  $l^2C$  bus while providing the option of programmability through the use of external components and voltage levels for systems not using  $l^2C$ .

## 6 Pin Configuration and Functions

A. Thermal pad must be soldered to PCB as SW3 and SW4 power ground

**TPS65400-Q1** SLVSCQ2 – JULY 2015

Texas Instruments

## **Pin Functions**

| PIN         |     |                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|-------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME        | NO. | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| CB1         | 1   | Bootstrap pin for high-side MOSFET gate drive for SW1                                                                                                                                                                                                                                                                                                                                    |  |  |

|             | 2   |                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| SW1         | 3   | Switch pin for SW1                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|             | 4   |                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| PVIN1       | 5   | Power input for buck switching regulator SW1                                                                                                                                                                                                                                                                                                                                             |  |  |

| PVIN2       | 6   | Power input for SW2                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| PGND1       | 7   | Power ground for buck converters                                                                                                                                                                                                                                                                                                                                                         |  |  |

| PGND2       | 8   | Power ground for buck converters                                                                                                                                                                                                                                                                                                                                                         |  |  |

|             | 9   |                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| SW2         | 10  | Switch pin for SW2                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|             | 11  |                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| CB2         | 12  | Bootstrap pin for SW2 high-side MOSFET gate drive                                                                                                                                                                                                                                                                                                                                        |  |  |

| ENSW2       | 13  | Enable input pin for SW2. Active high. 2-µA internal pullup current is inside.                                                                                                                                                                                                                                                                                                           |  |  |

| VFB2        | 14  | Feedback input pin for SW2                                                                                                                                                                                                                                                                                                                                                               |  |  |

| COMP2       | 15  | Compensation pin for external compensation network for SW2. Pulling this line high to VDDD configures the SW1 controller to control both SW1 and SW2.                                                                                                                                                                                                                                    |  |  |

| SS2/PG2     | 16  | Soft-start for SW2 (default). A capacitor is used to set the startup time. This pin can also be reconfigured through I <sup>2</sup> C to display the PGOOD2 signal instead.                                                                                                                                                                                                              |  |  |

| PGOOD       | 17  | Default PGOOD signal is for all switchers. It can be changed according to ( <i>D2h</i> ) <i>PIN_CONFIG_00</i> . If all switchers are disabled, PGOOD is low.                                                                                                                                                                                                                             |  |  |

| VDDG        | 18  | Supply for gate drives. Bypass locally to PGND.                                                                                                                                                                                                                                                                                                                                          |  |  |

| VDDA        | 19  | Output of internal regulator for analog controls.                                                                                                                                                                                                                                                                                                                                        |  |  |

| VDDD        | 20  | 3.3-V output of internal regulator digital controls                                                                                                                                                                                                                                                                                                                                      |  |  |

| AGND        | 21  | Ground connection for analog controls                                                                                                                                                                                                                                                                                                                                                    |  |  |

| VIN         | 22  | Analog V <sub>IN</sub> . Power input pin for VDDD, VDDA, and VGATE subregulator power                                                                                                                                                                                                                                                                                                    |  |  |

| CE          | 23  | Chip enables. Internal pull-up current will default to high if the pin is left floating. Connect to an open-drain output to pull low to disable. Driving with a push-pull output is not recommended. When low, internal regulators are shutdown to minimize power, and functions are disabled. Configuration is reloaded from EEPROM as part of the power-up sequence when CE goes high. |  |  |

| SS3/PG3     | 24  | Soft-start for SW3 (default). A capacitor is used to set the startup time. This pin can also be reconfigured through I <sup>2</sup> C to display the PGOOD3 signal instead.                                                                                                                                                                                                              |  |  |

| COMP3       | 25  | Compensation pin for external compensation network for SW3                                                                                                                                                                                                                                                                                                                               |  |  |

| VFB3        | 26  | Feedback input pin for SW3                                                                                                                                                                                                                                                                                                                                                               |  |  |

| ENSW3       | 27  | Enable input pin for SW3. Active high. 2-µA internal pullup current is inside.                                                                                                                                                                                                                                                                                                           |  |  |

| CB3         | 28  | Bootstrap pin for SW3 high-side MOSFET gate drive                                                                                                                                                                                                                                                                                                                                        |  |  |

| SW3         | 29  | Switch pin for SW3. Max rated output current is 2 A.                                                                                                                                                                                                                                                                                                                                     |  |  |

| PVIN3       | 30  | Power input for buck switching regulator SW3                                                                                                                                                                                                                                                                                                                                             |  |  |

| PVIN4       | 31  | Power input for SW4                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| SW4         | 32  | Switch pin for SW4. Max rated output current is 2 A.                                                                                                                                                                                                                                                                                                                                     |  |  |

| CB4         | 33  | Bootstrap pin for SW4 high-side MOSFET gate drive                                                                                                                                                                                                                                                                                                                                        |  |  |

| ENSW4       | 34  | Enable input pin for SW4. Active high. 2-µA internal pullup current is inside.                                                                                                                                                                                                                                                                                                           |  |  |

| VFB4        | 35  | Feedback input pin for SW4                                                                                                                                                                                                                                                                                                                                                               |  |  |

| COMP4       | 36  | Compensation pin for external compensation network for SW4. Pulling this line high to VDDD configures the SW3 controller to control both SW3 and SW4.                                                                                                                                                                                                                                    |  |  |

| SS4/PG4     | 37  | Soft-start for SW4 (default). A capacitor is used to set the startup time. This pin can also be reconfigured through $I^2C$ to display the PGOOD4 signal instead                                                                                                                                                                                                                         |  |  |

| I2CADDR     | 38  | Select I <sup>2</sup> C address with resistor to AGND                                                                                                                                                                                                                                                                                                                                    |  |  |

| RST_N       | 39  | Reset of digital logic. When low, all switchers are disabled. Configuration is reloaded from EEPROM when RESET_N is deasserted.                                                                                                                                                                                                                                                          |  |  |

| RCLOCK_SYNC | 40  | Resistor for setting master clock frequency from 275 kHz to 2.2 MHz or for clock sync                                                                                                                                                                                                                                                                                                    |  |  |

#### **Pin Functions (continued)**

| PIN         |     | DECONIDION                                                                                                                                                                  |

|-------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO. | DESCRIPTION                                                                                                                                                                 |

| I2CALERT    | 41  | Open-drain output that is pulled low for 200 $\mu$ s when a timeout condition is detected by the I <sup>2</sup> C watchdog on either SDA or SCL.                            |

| SDA         | 42  | Data input/output pin for I <sup>2</sup> C bus                                                                                                                              |

| SCL         | 43  | Clock input pin for I <sup>2</sup> C bus                                                                                                                                    |

| CLK_OUT     | 44  | Clock output signal. Open-collector output, requires pull up.                                                                                                               |

| SS1/PG1     | 45  | Soft-start for SW1 (default). A capacitor is used to set the startup time. This pin can also be reconfigured through I <sup>2</sup> C to display the PGOOD1 signal instead. |

| COMP1       | 46  | Compensation pin for external compensation network for SW1                                                                                                                  |

| VFB1        | 47  | Feedback input pin for SW1                                                                                                                                                  |

| ENSW1/ENSEQ | 48  | Enable input pin for SW1. Active high. 2-µA internal pullup current is inside.                                                                                              |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature (unless otherwise noted) <sup>(1)</sup>

|                     |                                                                                                                                                 | MIN  | MAX         | UNIT  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|-------|

|                     | RS1_N, SCL, SDA, I2CALER1, CLK_OUT, I2CADDR, RCLOCK_SYNC     -1     20       SW1, SW2, SW3, SW4     -1     20       VDDA, VDDG     -0.3     7.5 | 20   |             |       |

|                     | CB1, CB2, CB3, CB4 referenced to SWx                                                                                                            | -0.3 | 7.5         |       |

|                     |                                                                                                                                                 | -0.3 | VDDD or 3.6 |       |

| Input<br>voltage    | SW1, SW2, SW3, SW4                                                                                                                              | -1   | 20          | V     |

| vollago             | VDDA, VDDG                                                                                                                                      | -0.3 | 7.5         | 3.6 V |

|                     | PGOOD, SS1/PG1, SS2/PG2, SS3/PG3, SS4/PG4, COMP1, COMP2, COMP3, COMP4, CE                                                                       | -0.3 | VDDA or 7.5 |       |

|                     | VDDD                                                                                                                                            | -0.3 | 3.6         |       |

| T <sub>J(max)</sub> | Junction temperature                                                                                                                            |      | 150         | °C    |

|                     | Maximum lead temperature (soldering, 10 s)                                                                                                      |      | 260         | °C    |

| T <sub>stg</sub>    | Storage temperature                                                                                                                             | -65  | 150         | °C    |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |                            |                                 |                                                 | VALUE | UNIT |

|--------------------|----------------------------|---------------------------------|-------------------------------------------------|-------|------|

|                    |                            | Human-body model (HBM), per AEC | C Q100-002 <sup>(1)</sup>                       | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic<br>discharge | Charged-device model (CDM), per | All pins                                        | ±500  | V    |

|                    | alconargo                  | AEC Q100-011                    | Corner pins (1, 12, 13, 24, 25, 36, 37, and 48) | ±750  |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                       |                            | MIN | MAX  | UNIT |

|---------------------------------------|----------------------------|-----|------|------|

| VIN1, VIN2, VIN3, VIN4                | Input voltage range        | 4.5 | 18   | V    |

| I <sub>OUT1</sub> , I <sub>OUT2</sub> | Load current               | 0   | 4    | А    |

| I <sub>OUT3</sub> , I <sub>OUT4</sub> | Load current               | 0   | 2    | А    |

| $V_{FB1}, V_{FB2}, V_{FB3}, V_{FB4}$  | Voltage feedback           | 0.6 | 1.87 | V    |

| TJ                                    | Junction temperature range | -40 | 125  | °C   |

#### **TPS65400-Q1** SLVSCQ2 – JULY 2015

www.ti.com

NSTRUMENTS

**FEXAS**

# 7.4 Thermal Information

|                       |                                              | TPS65400-Q1 |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RGZ (VQFN)  | UNIT |

|                       |                                              | 48 PINS     |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 29.8        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 14.9        | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 6.3         | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.2         | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 6.3         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.8         | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

6 Submit Documentation Feedback

# 7.5 Electrical Characteristics

$V_{IN}$  = 12 V,  $F_{SW}$  = 500 kHz,  $T_J$  = -40°C to 125°C, typical values are at  $T_J$  = 25°C, unless otherwise noted

|                                         | PARAMETER                                                                                | TEST CONDITIONS                                   | MIN  | TYP                   | MAX  | UNIT |

|-----------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------|------|-----------------------|------|------|

| SWITCHER 1 A                            | ND SWITCHER 2                                                                            |                                                   |      |                       |      |      |

| limit1, I <sub>limit2</sub>             | SW1, SW2 high-side current limit<br>adjustment range                                     |                                                   | 2    |                       | 6    | А    |

| limit-accuracy                          | Accuracy to nominal current limit value                                                  | I <sub>limit</sub> = 4 A, 5 A, 6 A                | -25% |                       | 25%  |      |

| Rdson HS                                | SW1, SW2 HS Rds(on)                                                                      |                                                   |      | 66                    |      | mΩ   |

| Rdson LS                                | SW1, SW2 LS Rds(on)                                                                      |                                                   |      | 42                    |      | mΩ   |

| SWITCHER 3 A                            | ND SWITCHER 4                                                                            |                                                   |      |                       |      |      |

| <sub>limit3</sub> , I <sub>limit4</sub> | SW3 and SW4 current limit                                                                |                                                   | 0.5  |                       | 3    | Α    |

| limit accuracy                          | Accuracy to nominal current limit value                                                  | I <sub>limit</sub> = 1 A, 2 A, 3 A                | -25% |                       | 25%  |      |

| Rdson HS                                | SW3 and SW4 HS Rds(on)                                                                   |                                                   |      | 120                   |      | mΩ   |

| Rdson LS                                | SW3/4 LS Rds(on)                                                                         |                                                   |      | 90                    |      | mΩ   |

| FEEDBACK AN                             | ID ERROR AMPLIFIERS FOR SW1 – SW                                                         | 14                                                |      |                       |      |      |

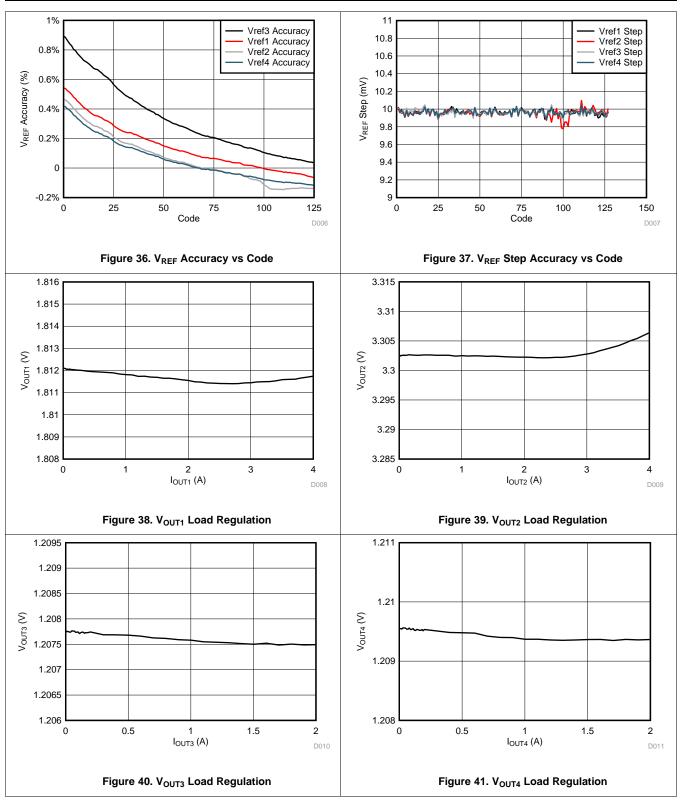

| /FB                                     | Accuracy                                                                                 | V <sub>REF</sub> = 1 V                            | -1%  |                       | 1%   |      |

| V <sub>REFn</sub>                       | Error amplifier reference voltage                                                        | Default value                                     |      | 800                   |      | mV   |

| V <sub>REF_STEP</sub>                   | I <sup>2</sup> C programmable V <sub>REF</sub> step size                                 |                                                   |      | 10                    |      | mV   |

| Gm                                      | Error amplifier transconductance                                                         |                                                   | 95   | 133                   | 165  | μS   |

| sink                                    | Sink                                                                                     |                                                   |      | 12                    |      | μA   |

| source                                  | Source                                                                                   |                                                   |      | 12                    |      | μA   |

| PWM SWITCHI                             | NG CHARACTERISTICS                                                                       | · · · · · · · · · · · · · · · · · · ·             |      |                       |      |      |

| Phase_err12 <sup>(1)</sup>              | Phase error between SW1 and SW2                                                          | F <sub>sw</sub> = 1.1 MHz                         |      | 5°                    |      |      |

| Phase_err34 <sup>(1)</sup>              | Phase error between SW3 and SW4                                                          | F <sub>sw</sub> = 1.1 MHz                         |      | 5°                    |      |      |

| sw                                      | Resistor-configurable PWM switching configuration                                        |                                                   | 275  |                       | 2200 | kHz  |

| F <sub>sw-accuracy</sub>                | PWM switching frequency accuracy                                                         | $R_{OSC}$ = 165 kΩ<br>(F <sub>sw</sub> = 1.1 MHz) | -10% |                       | 10%  |      |

| V <sub>rclock_sync</sub>                | Voltage reference for RCLOCK_SYNC                                                        |                                                   |      | 0.8                   |      | V    |

| ON_min                                  | Lower duty cycle limit                                                                   |                                                   |      | 80                    | 150  | ns   |

| OFF_min                                 | Minimum off-time limit (constrains the maximum achievable duty cycle)                    |                                                   |      | 150                   |      | ns   |

| CLOCK SYNC                              |                                                                                          |                                                   |      |                       |      |      |

| V_H <sub>SYNC</sub>                     | High signal threshold                                                                    |                                                   | 2.6  |                       |      | V    |

| V_L <sub>SYNC</sub>                     | Low signal threshold                                                                     |                                                   |      |                       | 1    | V    |

| CLKOUT                                  | Max current sink/source for CLK_OUT                                                      |                                                   |      | 2                     |      | mA   |

| min_SYNC                                | Minimum detectable time for sync pulse                                                   |                                                   |      |                       | 150  | ns   |

|                                         | Frequency synchronization range                                                          |                                                   | 275  |                       | 2200 | kHz  |

| T <sub>SYNC_DELAY</sub>                 | Delay between input pulse to<br>RCLOCK_SYNC and rising edge of<br>CLK OUT and PWM output |                                                   |      | 20                    |      | ns   |

| TIMING CHAR                             | —                                                                                        |                                                   |      |                       |      |      |

|                                         | Delay for restart during repeated OCP                                                    |                                                   |      |                       |      |      |

| restart                                 | condition                                                                                |                                                   |      | 20                    |      | ms   |

| NTERNAL REC                             | GULATORS AND UVLO                                                                        |                                                   |      |                       |      |      |

| V <sub>DDA</sub>                        | Internal subregulator output                                                             | V <sub>in</sub> > 6.6 V                           |      | 6.1                   |      | V    |

|                                         | <u> </u>                                                                                 | 4.5 V < V <sub>in</sub> 6.6 V                     |      | V <sub>in</sub> – 0.1 |      |      |

| V <sub>DDD</sub>                        | Output of internal subregulator                                                          |                                                   |      | 3.2                   |      | V    |

| V <sub>DDG</sub>                        | Output of Internal regulator for gate                                                    | V <sub>in</sub> > 6.6 V                           |      | 6.1                   |      | V    |

| • DDG                                   | drivers                                                                                  | 4.5 V < V <sub>in</sub> 6.6 V                     |      | V <sub>in</sub> – 0.1 |      | v    |

(1) Specified by design.

Copyright © 2015, Texas Instruments Incorporated

TPS65400-Q1

# **Electrical Characteristics (continued)**

$V_{IN}$  = 12 V,  $F_{SW}$  = 500 kHz,  $T_J$  = -40°C to 125°C, typical values are at  $T_J$  = 25°C, unless otherwise noted

|                                          | PARAMETER                                                           | TEST CONDITIONS                                                  | MIN  | TYP  | MAX  | UNIT                     |

|------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------|------|------|------|--------------------------|

| I <sub>VIN</sub>                         | Quiescent non-switching, no load<br>current                         | CE high, V <sub>FB</sub> >> V <sub>REF</sub> , (no<br>switching) |      | 8    |      | mA                       |

| SD                                       | Quiescent shutdown current                                          | CE low                                                           |      | 12   | 27   | μA                       |

| V <sub>IN_UVLO</sub>                     | Input voltage UVLO                                                  | Rising                                                           |      | 4.25 | 4.48 | V                        |

| VIN_UVLO                                 | Input voltage UVLO                                                  | Falling                                                          | 3.4  | 3.75 |      | V                        |

|                                          | Vx, RST_N, SSx, PG                                                  | · · · · · · · · · · · · · · · · · · ·                            |      |      |      |                          |

| R_L <sub>PGOOD</sub>                     | Resistance of PGOOD outputs when low                                |                                                                  |      | 500  |      | Ω                        |

| V_OL <sub>PGOOD</sub>                    | Logic output low voltage                                            | I_OL = 100 μA                                                    |      |      | 0.1  | V                        |

| ss                                       | Soft-start current                                                  |                                                                  | 4.1  | 5.6  | 7.3  | μA                       |

| V <sub>EN_H</sub>                        | Enable logic high threshold (for ENSW1, ENSW2, ENSW3, ENSW4)        | V <sub>EN</sub> rising                                           | 1.12 | 1.20 | 1.28 | V                        |

| V <sub>EN_L</sub>                        | Enable logic low threshold (for ENSW1, ENSW2, ENSW3, ENSW4)         | V <sub>EN</sub> falling                                          | 0.97 | 1.07 |      | V                        |

| V <sub>EN_HYS</sub>                      | Enable hysteresis (for ENSW1, ENSW2, ENSW3, ENSW4)                  |                                                                  |      | 130  |      | mV                       |

| I <sub>EN</sub>                          | ENSWx pin pullup current                                            | V <sub>EN</sub> = 0                                              |      | 2    |      | μA                       |

| CE                                       | CE pin pullup current                                               | $V_{CE} = 0$                                                     |      | 2    |      | μA                       |

| V <sub>IH_CE</sub>                       | Logic input high for CE                                             |                                                                  | 1.3  |      |      | V                        |

| V <sub>IL_CE</sub>                       | Logic input low CE                                                  |                                                                  |      |      | 0.4  | V                        |

| V <sub>IH_RSTN</sub>                     | Logic input high RST_N                                              |                                                                  | 1.3  |      |      | V                        |

| V <sub>IL_RSTN</sub>                     | Logic input low RST_N                                               |                                                                  |      |      | 0.4  | V                        |

|                                          | SDA, SCL, I2CALERT, I2CADDR)                                        | + +                                                              |      |      |      |                          |

| V_IL <sub>I2C</sub>                      | Logic input low SCL, SDA                                            |                                                                  |      |      | 0.8  | V                        |

| V_IH <sub>I2C</sub>                      | Logic input high for SCL, SDA                                       |                                                                  | 2.1  |      |      | V                        |

| R_L <sub>I2C</sub>                       | ON resistance of I <sup>2</sup> C pins<br>(SDA,SCL,I2CALERT) to GND | I2CALERT = 1                                                     |      | 85   |      | Ω                        |

| V_OL <sub>I2C</sub>                      | Logic output low voltage for<br>SCL,SDA,I2CALERT pins               | I_OL = 350 μA                                                    |      |      | 0.1  | V                        |

| LEAK                                     | Input leakage current                                               | SDA, SCL = 3.3 V                                                 |      |      | 1    | μA                       |

| I2CADDR                                  | Source current of I2CADDR pin                                       | VDDD = 3.3 V, VIN > 4.5 V                                        |      | 20   |      | uA                       |

|                                          | Timeout detection on SDA or SCL low                                 |                                                                  |      | 30   |      | ms                       |

| TIMEOUT_PULSE                            | Duration of timeout pulse on I2CALERT                               |                                                                  |      | 200  |      | μs                       |

| FAULTS                                   |                                                                     |                                                                  |      |      |      |                          |

| T <sub>TSD</sub> <sup>(2)</sup>          | Thermal shutdown threshold                                          |                                                                  |      | 160  |      | °C                       |

| T <sub>TSD_</sub> restart <sup>(2)</sup> | Thermal shutdown hysteresis                                         |                                                                  |      | 20   |      | °C                       |

|                                          | OVP threshold rising (fault latched, PGOOD asserted)                | 0.6V < V <sub>REF</sub> < 1.87 V                                 |      | 111  |      | % of<br>V <sub>REF</sub> |

| V <sub>FB_OVP</sub>                      | OVP threshold falling (fault cleared, PGOOD deasserted)             | 0.6 V < V <sub>REF</sub> < 1.87 V                                |      | 104  |      | % of<br>V <sub>REF</sub> |

| OVPSDOWN                                 | Time after OVP before protection activation and PGOOD fall          |                                                                  |      | 55   | 95   | μs                       |

| <br>                                     | Undervoltage threshold (PGOOD deasserted)                           | 0.6 V < V <sub>REF</sub> < 1.87 V                                |      | 92   |      | % of<br>V <sub>REF</sub> |

| V <sub>FB UVP</sub>                      | Undervoltage Threshold (PGOOD asserted)                             | 0.6 V < V <sub>REF</sub> < 1.87 V                                |      | 83   |      | % of<br>V <sub>REF</sub> |

| t <sub>UVPSDOWN</sub>                    | Time after UVP before PGOOD fall                                    |                                                                  |      | 55   | 95   | μs                       |

(2) Specified by lab validation.

## 7.6 System Characteristics

The following specification table entries are specified by the design (component values provided in the typical application circuit are used). These parameters are not specified by production testing. Minimum and Max values apply over the full operating ambient temperature range ( $-40^{\circ}C \le T_{J} \le 125^{\circ}C$ ), over the V<sub>IN</sub> range = 5 to 12 V, and I<sub>OUT</sub> range unless otherwise specified. L = 3.3 µH, DCR = 10.4 m $\Omega$ , V<sub>OUT</sub> = 1.2 V, 1% FB resistor.

|                                   | PARAMETER                                                                            | TEST CONDITIONS                                                  | MIN  | TYP | MAX | UNIT |

|-----------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------|------|-----|-----|------|

| V <sub>LINEREG</sub>              | Line regulation                                                                      |                                                                  |      | 0.1 |     | %/V  |

| V <sub>LOADREG</sub>              | Load regulation                                                                      |                                                                  |      | 0.1 |     | %/A  |

| t <sub>r</sub>                    | VOUT step duration (t <sub>r</sub> )                                                 | For 50-mV step                                                   |      | 30  |     | μs   |

| t <sub>s</sub>                    | VOUT step settling time (t <sub>s</sub> )                                            | For 50-mV step                                                   |      | 30  |     | μs   |

| V <sub>OVUV</sub>                 | VOUT step overshoot/undershoot                                                       | For 50-mV step                                                   |      | 6   |     | mV   |

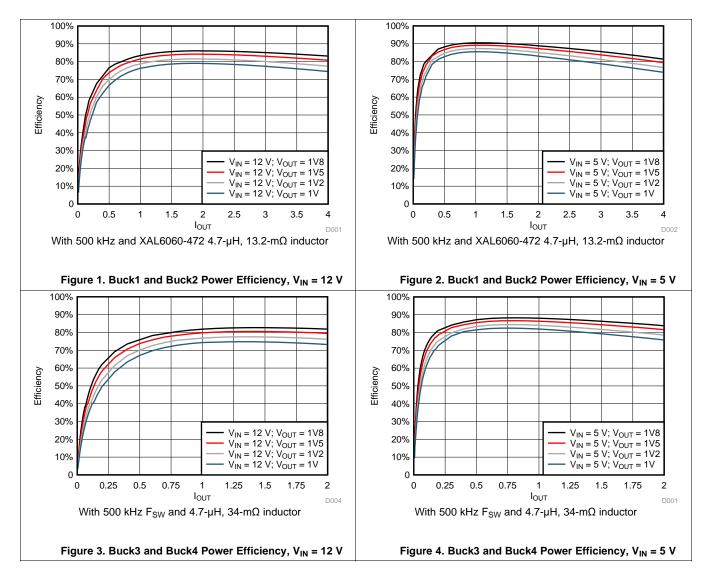

|                                   | Efficiency (SM(4 and SM(2))                                                          | Vin = 5 V, Vo = 1.2 V, lout = 4 A,<br>$f_{sw} = 500 \text{ kHz}$ |      | 77% |     |      |

|                                   | Efficiency (SW1 and SW2)                                                             | Vin = 12 V, Vo = 1.2 V lout = 4 A,<br>$f_{sw} = 500 \text{ kHz}$ |      | 76% |     |      |

|                                   | Efficiency (SW3 and SW4)                                                             | Vin = 5 V, Vo = 1.2 V, lout = 2 A,<br>$f_{sw}$ = 500 kHz         |      | 77% |     |      |

|                                   | Efficiency (SW3 and SW4)                                                             | Vin = 12 V, Vo = 1.2 V lout = 2 A,<br>$f_{sw} = 500 \text{ kHz}$ |      | 74% |     |      |

| IOUT <sub>match</sub>             | Average ( <sup>(1)</sup> ) current sharing<br>accuracy (SW1 and SW2, SW3 and<br>SW4) | I <sub>load</sub> = I <sub>OUTmax</sub>                          |      | 20% |     |      |

| IPK <sub>match</sub>              | Peak current ( <sup>(2)</sup> ) sharing accuracy (SW1 and SW2, SW3 and SW4)          | I <sub>load</sub> = I <sub>OUTmax</sub>                          |      |     | 20% |      |

| t <sub>acc</sub>                  | Timing accuracy for delays and restarts                                              |                                                                  | -10% |     | 10% |      |

| t <sub>reset_delay</sub>          | Time after RSTn or CE is released for power sequence to begin                        | Default value                                                    |      | 1   |     | ms   |

| t <sub>reset_delay_max</sub><br>0 | Minimum delay after reset is<br>released for power sequence to<br>begin              | t <sub>reset_delay</sub> set to 0 ms                             |      |     | 1.1 | ms   |

(1) Average current sharing accuracy is highly dependent on the matching of the inductor and capacitor.

(2) Peak current sharing accuracy refers to the max inductor current in each phase.

# 7.7 Operational Parameters

Values recommended that ensure proper system behavior

|                            | PARAMETER                                       | MIN | TYP MAX    | UNIT |

|----------------------------|-------------------------------------------------|-----|------------|------|

| C <sub>A</sub>             | Stabilization capacitor to be connected to VDDA |     | 4.7        | μF   |

| C <sub>D</sub>             | Stabilization capacitor to be connected to VDDD |     | 3.3        | μF   |

| C <sub>G</sub>             | Stabilization capacitor to be connected to VDDG |     | 10         | μF   |

| Vin1, Vin2, Vin3, Vin4     | SW1 to SW4 input voltage                        | 4.5 | 18         | V    |

| Vout1, Vout2, Vout3, Vout4 | SW1 to SW4 output voltage                       | 0.6 | 90% of Vin | V    |

## 7.8 Package Dissipation Ratings<sup>(1)</sup>

| PACKAGE | R <sub>θJA</sub> (°C/W) | T <sub>A</sub> = 25°C | T <sub>A</sub> = 55°C | T <sub>A</sub> = 85°C |

|---------|-------------------------|-----------------------|-----------------------|-----------------------|

| RGZ     | 29.8                    | 4.5 W                 | 3.14 W                | 1.77 W                |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

**TPS65400-Q1** SLVSCQ2 – JULY 2015

# 7.9 Typical Characteristics: System Efficiency

# 8 Detailed Description

#### 8.1 Overview

The TPS65400-Q1 is an integrated PMU optimized for applications that require small form factor and high-power conversion efficiency enabling small space-constrained equipment with high-ambient operating temperature without cooling. It provides high-power efficiency at a system level by enabling a single-stage conversion from an intermediate distribution bus with an optimized combination of regulators.

The TPS65400-Q1 consists of four high-current buck-switching regulators (SW1, SW2, SW3, and SW4) with integrated FETs. The switching power supplies are intended for powering high-current digital circuits such as the processor, FPGA, ASIC, memory, and digital I/Os. SW1 and SW2 support 4 A each, and SW3 and SW4 support 2 A each. Each regulator's switching frequency is independently adjustable up to 2.2 MHz.

Current limit programmability on each switcher enables optimization of inductor ratings for a particular application configuration not requiring the maximum current capability.

The TPS65400-Q1 can be powered from a single-input voltage rail between 4.5 and 18 V, making it suitable for applications running off a 5- or 12-V intermediate power distribution bus.

Sequencing requirements can be met using the individual enable pins or by programming the sequence through the  $I^2C$  bus into the onboard EEPROM. Output voltages can be set through external resistor networks and VREF can be programmed from 0.6 to 1.87 V in 10-mV steps. All control and status info can be accessed through a PMBus-compatible  $I^2C$  bus.

The TPS65400-Q1 provides a high level of flexibility for monitoring and control through the  $I^2C$  bus while providing the option of programmability through the use of external components and voltage levels for systems not using  $I^2C$ .

**TPS65400-Q1** SLVSCQ2 – JULY 2015 TEXAS INSTRUMENTS

www.ti.com

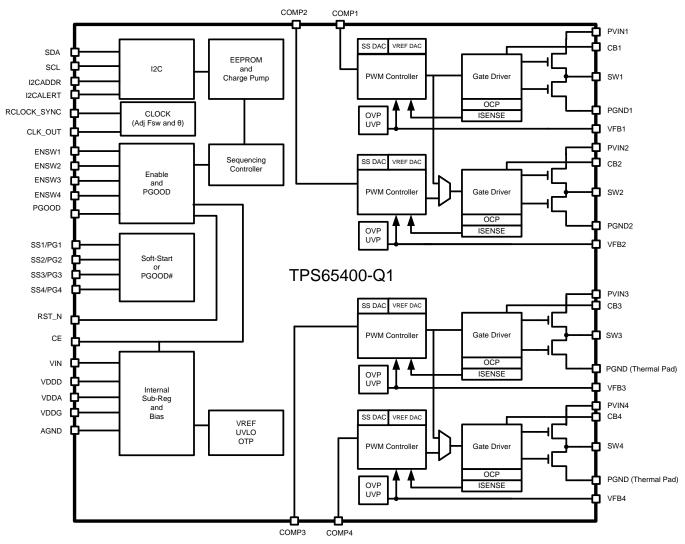

# 8.2 Functional Block Diagrams

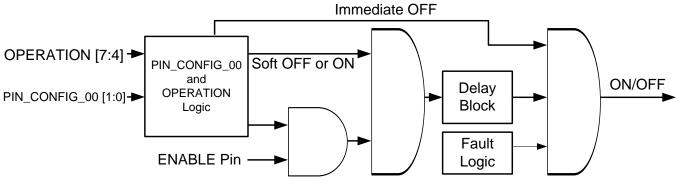

Figure 5. TPS65400-Q1 Functional Block Diagram

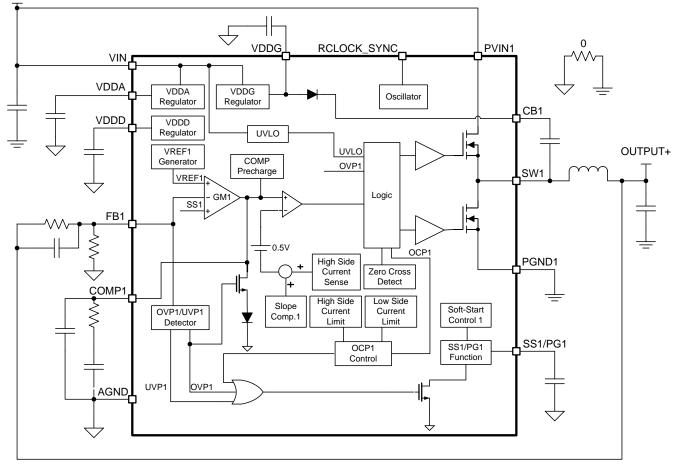

## **Functional Block Diagrams (continued)**

A. All other switchers follow the same pattern

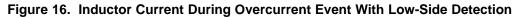

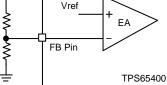

#### Figure 6. Simplified Control Block Diagram for Switcher1

## 8.3 Feature Description

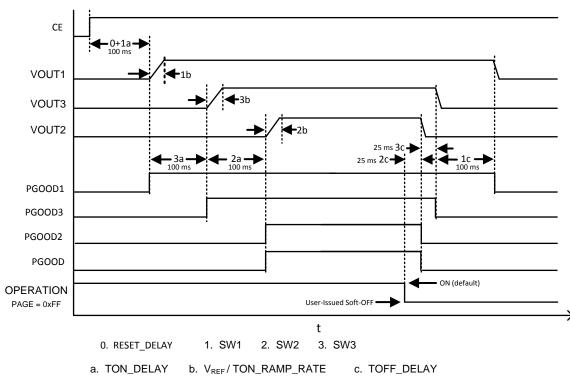

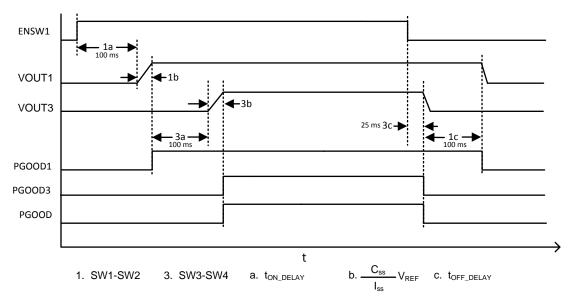

#### 8.3.1 Startup Timing and Power Sequencing

#### 8.3.1.1 Startup Timing

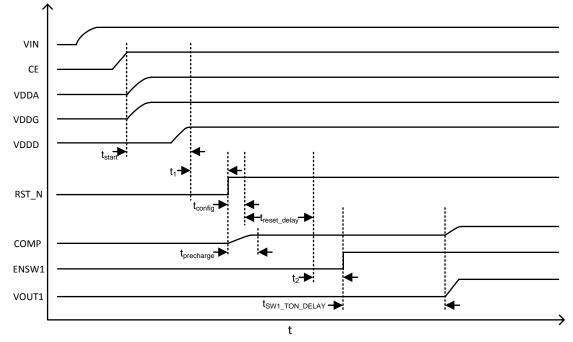

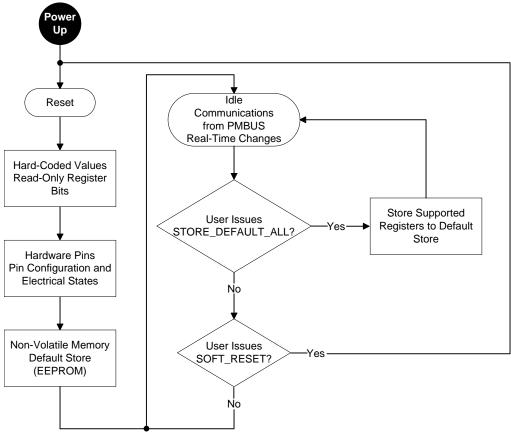

Figure 7 shows the startup timing of the TPS65400-Q1. Upon power-up or the rising edge of CE, the internal power rails VDDA, VDDG, and VDDD startup during the time labeled  $t_{start}$ . Following  $t_{start}$ , a delay of  $t_1$  follows (which is defined by the user through the timing of RST\_N). During time  $t_{start}$  and  $t_1$ , the COMP terminal is internally discharged through a 1-k $\Omega$  resistor. At the rising edge of RST\_N, the TPS65400-Q1 begins two actions:

- 1. The TPS65400-Q1 begins its precharge of the COMP terminal (indicated by t<sub>precharge</sub>). The length of t<sub>precharge</sub> needed to precharge the COMP terminal depends on the time constant of the R and C components. The internal precharge voltage source remains on even during normal operation, preventing the COMP terminal from falling below 0.6 V except during faults (OVP, OCP, and so forth).

- 2. The TPS65400-Q1 begins its configuration sequence (indicated by t<sub>config</sub>), and loads parameters from the EEPROM. Parameters to be set include Vout, switching frequency, soft-start timing, and current limit.

#### Feature Description (continued)

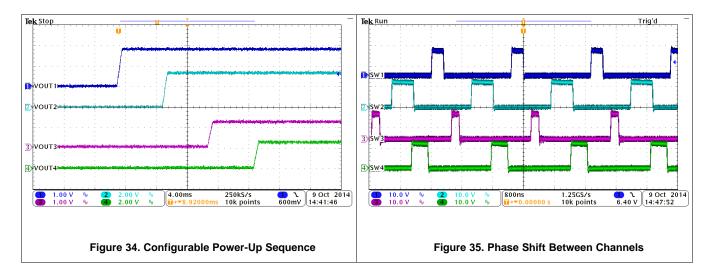

After  $t_{config}$  is complete,  $t_{reset\_delay}$  begins. The length of  $t_{reset\_delay}$  is user-configurable through PMBus register DCh. After  $t_{reset\_delay}$  is complete, the TPS65400-Q1 begins its startup sequence. The startup sequence is EEPROM-configurable, so any of the four switchers could be the first to startup with a configurable delay. In this particular example, SW1 is configured to startup first after a delay of  $t_{SW1\_TON\_DELAY}$ , which is configurable through PMBus register *(DDh) TON\\_TOFF\\_DELAY*.

A. PGOOD1 and ENSW2 are tied together externally, and t<sub>ON\_DELAY1</sub> and t<sub>ON\_DELAY2</sub> are configured through PMBus.

Figure 7. Timing Showing Startup from CE

To summarize, the length of time from rising edge of CE to soft-start of the first switcher in the sequence is:

$t_{CE_{to}SS} = t_{start} + t_1 + t_{config} + t_{reset_{delay}} + t_2 + t_{SW1_{on_{DELAY}}}$

(1)

The delays,  $t_{reset\_delay}$  and  $t_{SW1\_ON\_DELAY}$ , are both configurable through PMBus. The delay,  $t_{config}$ , is typically 1.1 ms. The delays,  $t_1$  and  $t_2$ , are determined by the user-defined timing of RST\_N and ENSW1. They can both be set to 0 by pulling RST\_N high before the end of  $t_{start}$  and ENSW1 high before the end of  $t_{reset\_delay}$ . One simple way to do this would be to tie both signals to VDDD.

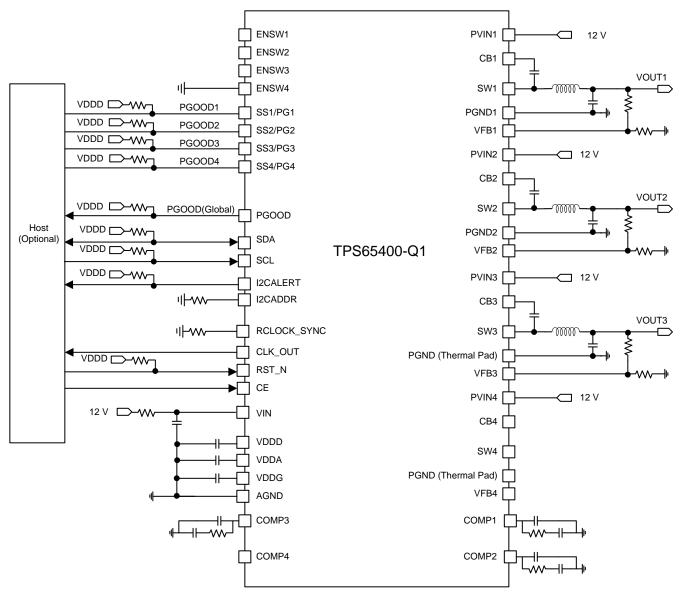

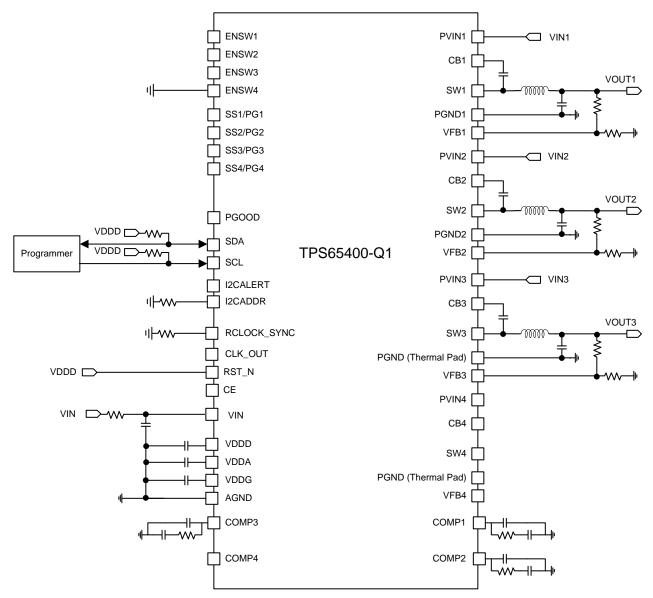

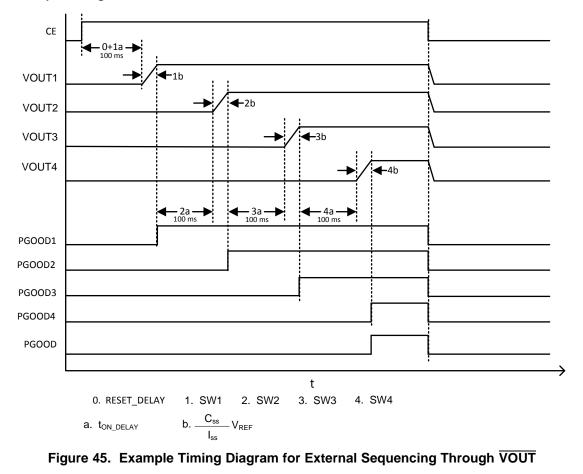

#### 8.3.1.2 External Sequencing

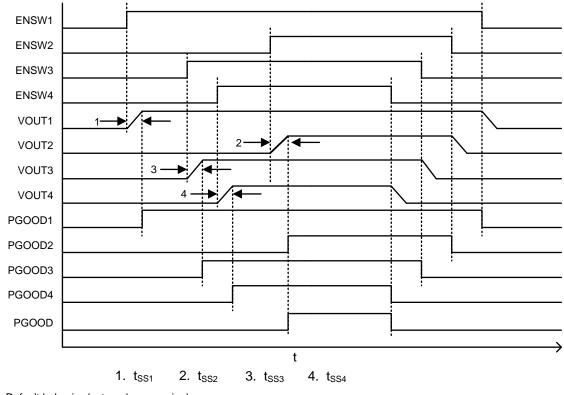

To use external sequencing, either connect all the enable pins (ENSW1, ENSW2, ENSW3, and ENSW4) to an external sequencing controller, or connect them to PGOOD outputs as shown in Figure 8. By default,  $t_{ON\_DELAY}$  and  $t_{OFF\_DELAY}$  are both set to 5 ms. This allows the user complete flexibility of sequencing order and timing with the ENSWx pins without modifying any of the default settings in the TPS65400-Q1.

#### **Feature Description (continued)**

A. Default behavior (external sequencing)

#### Figure 8. Example of Sequencing Where Timing is Controlled by an External Sequencer With ENSWx Pins

#### 8.3.1.3 Internal Sequencing

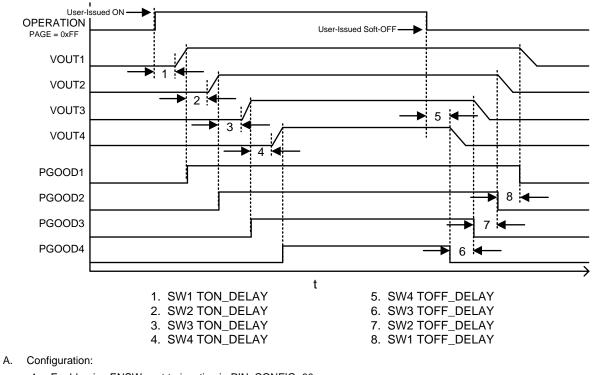

The default settings for SEQUENCE\_ORDER (see *(D5h)* SEQUENCE\_ORDER) effectively disable sequencing by setting all switchers to start at the same time. Therefore, to use internal sequencing, the default values for SEQUENCE\_ORDER must be changed to the desired sequence. In addition, the user can configure the start or stop sequence to have a dependence on the PGOOD output of the previous switcher, or to wait for a set delay. If configured to have a dependence on PGOOD, the soft-start for the next switcher begins after PGOOD of the previous goes high and the wait time determined by  $t_{ON_DELAY}$  is complete. If configured to wait for a set delay, the wait time determined by  $t_{ON_DELAY}$  begins immediately upon the enabling of the previous switcher.

In addition, each supply can be disabled such that it is bypassed in the power-up sequence. For example, if the sequence is SW1-SW2-SW3-SW4, and SW2 is disabled, then SW3 will be powered up after SW1. The initial configuration of the TPS65400-Q1 (for first-time power-up) needs to be done using one of the methods described in *Initial Configuration*.

#### 8.3.2 UVLO and Precision Enables

The TPS65400-Q1 implements a UVLO function that prevents startup when the voltage at VIN (terminal 22) is below 4 V. In most applications, VIN and all of the power rails (PVIN1, PVIN2, PVIN3, and PVIN4) are tied to the same source and this single UVLO function is sufficient. However, in some applications, the power rails may be tied to different input voltages, and there is the possibility that the TPS65400-Q1 may attempt to startup a switcher even when its associated PVINx rail has not reached a high-enough voltage. In these cases, the precision enable threshold on each ENSWx can be used to precisely set the startup threshold for each individual switcher with a simple resistor divider to PVINx.

Copyright © 2015, Texas Instruments Incorporated

#### **Feature Description (continued)**

In cases where a single UVLO threshold is needed for all four switchers, but at a different level than 4 V, the TPS65400-Q1 can be configured for single-terminal enable (PMBus register D2h, bits 0:1 = 10) where the ENSW1/ENSEQ terminal is used as a sequence enable terminal. Then, a resistor divider to the appropriate PVINx rail can be used to set a precise UVLO threshold that applies to all four switchers.

#### 8.3.3 Soft-Start and Prebiased Startup

The TPS65400-Q1 implements a soft-start function that minimizes discharge of the output when starting up in a prebiased condition. Soft-start time,  $t_{SS}$ , is set by  $t_{ON\_TRANSITION\_RATE}$  (digital soft-start) or by a capacitor connected to the corresponding SSx pin (analog soft-start). In this setup, the SSx pin sources a 5-µA current charging the capacitor, and the voltage at the SSx pin limits the reference voltage at the input of the error amplifier.

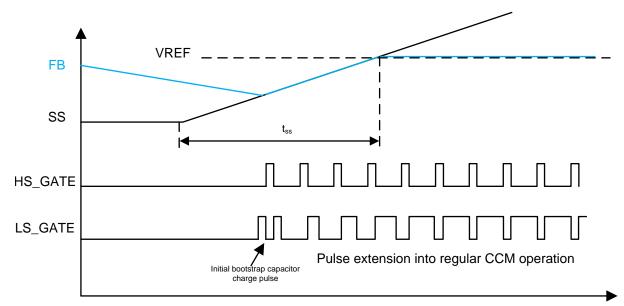

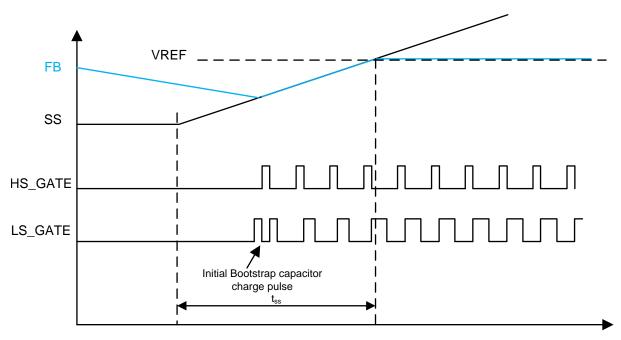

At the beginning of the soft-start, the soft-start input to the error amplifier is set to 0. The SSx input is raised gradually and reaches its target value during the time  $t_{ss}$ . If  $V_{FB} > V_{SS}$ , then no switching occurs. After the Soft-Start signal crosses VFB, the switching begins. The first switching pulse is on the low-side FET, which charges the high-side bootstrap capacitor. The unit runs in discontinuous conduction mode (DCM) with the zero-cross detector enabled on the low side (diode emulation). The high-side FET is pulsed according to the error amplifier output on the COMP pin. If the IC is configured for continuous conduction mode (CCM) operation (default), the low-side FET pulses gradually transition to normal CCM operation; at each successive switching cycle, the low-side gate pulse is gradually ramped until full synchronous switching occurs. At this point, the switcher enters normal CCM operation.

Figure 9. Soft-Start Under Prebiased Condition and CCM Mode Programmed

## **Feature Description (continued)**

Figure 10. Soft-Start Under Prebiased Condition and DCM Mode Programmed

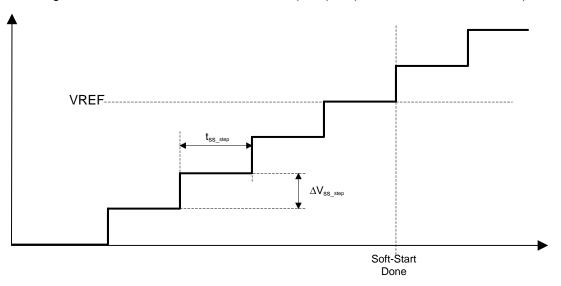

#### 8.3.3.1 Analog Soft-Start (Default) and Digital Soft-Start

The TPS65400-Q1 has the ability to use an analog-based soft-start ramp based on external capacitors (one input for each switcher) or to use internal signals based on digital logics and DACs to perform the soft-start function.

When using external soft-start configuration (default configuration), the SSx pins are connected to the soft-start input of the error amplifier.

When using the internal digital soft-start signal, the soft-start input to the error amplifier increases step-by-step at a rate set according to the value set in TON\_RAMP\_RATE (see (DEh) TON\_TRANSITION\_RATE).

$\Delta VSS\_$ step is 10 mV. Tss\_step depends on the soft-start time option selected. See (*DEh*) TON\_TRANSITION\_RATE for more details.

(3)

#### Feature Description (continued)

#### 8.3.3.2 Soft-Start Capacitor Selection

When using external soft-start capacitor to set the soft-start time, use Equation 2.

$$t_{ss} = \frac{Css}{lss} \times Vref$$

(2)

Css is the value of the capacitor connected between the SSx pin and AGND. VREF is the value of the reference voltage (default is 0.8 V). I<sub>SS</sub> is the current sourced by the SS1/PG1 pin during soft-start.

#### 8.3.4 PWM Switching Frequency Selection

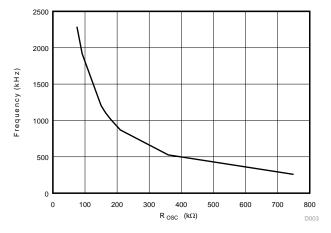

The master clock frequency,  $F_{OSC}$ , can be set by external resistor on the RCLOCK\_SYNC terminal, or by synchronizing with an external clock. To set using an external resistor, use this formula.

$F_{SW}$  (kHz) = 138664  $R_{OSC}$  (k $\Omega$ )<sup>-0.948</sup>

Figure 12. Frequency vs R<sub>osc</sub>

To sync to an external source, an AC-coupled signal should be applied to the terminal. A fixed resistor should still be connected to set a minimum frequency. The frequency of the input signal to synchronize with should always be higher than the minimum frequency. If the internal PLL cannot synchronize, the switchers will fall back to the minimum frequency set by the resistor. The CLK\_OUT terminal outputs the master clock F<sub>OSC</sub>.

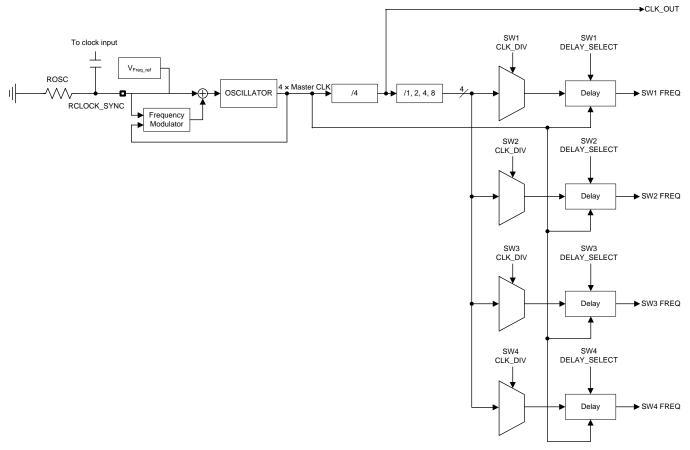

The PWM frequency of each switcher is determined by this master clock frequency and an I<sup>2</sup>C-programmable choice of 4 divider ratios (1, 2, 4, or 8) by setting CLK\_DIV (see (*D7h*) FREQUENCY\_PHASE).

#### Feature Description (continued)

A. The frequency modulator is used for external clock synchronization.

#### Figure 13. Diagram of PWM Clock Generation

The intent of the individual divider ratios is to allow users to set the frequency of each switcher independently. For example, with a master clock F<sub>OSC</sub> of 1.1 MHz, SW1 and SW2 have a divider ratio of 4 for a 275-kHz PWM, and SW3 and SW4 have a divider ratio of 1 for a PWM frequency of 1.1 MHz. Select the divider ratio so that the PWM frequency stays within the range of 275 kHz to 2.2 MHz for whichever master clock frequency is set.

In addition to selecting the frequency, each switcher can have its PWM frequency delayed. This enables the designer to minimize ripple current by properly selecting the delays so that the switching frequencies are out of phase. The default switching frequency is at CLK\_DIV =  $F_{OSC}$  / 1 with PHASE\_DELAY for SW1 at 0°, SW2 at 180°, SW3 at 90°, and SW4 at 270°. More information on frequency selection and delay is given in (D7h) FREQUENCY\_PHASE.

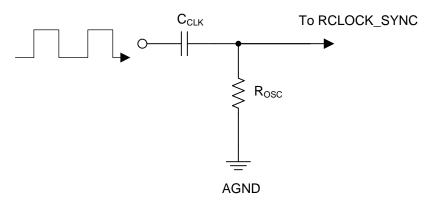

#### 8.3.5 Clock Synchronization

The RCLOCK\_SYNC terminal can be used to synchronize the master clock switching frequency,  $F_{OSC}$ , with an external clock source or another TPS65400-Q1. The external clock signal (which can come from another TPS65400-Q1 CLK\_OUT terminal) should be AC coupled to the RCLOCK\_SYNC terminal as shown in Figure 14. Choose the ROSC value so that the fixed frequency is nominally 30% lower than the external synchronizing clock frequency. An internal protection diode clamps the low level of the synchronizing signal to approximately -0.5 V. The internal clock synchronizes to the rising edge of the external clock.

Copyright © 2015, Texas Instruments Incorporated

TEXAS INSTRUMENTS

www.ti.com

#### Feature Description (continued)

Figure 14. AC-Coupled Clock Synchronization

TI recommends to choose an AC-coupling capacitance in the range of 50 to 100 pF. Exceeding the recommended capacitance may inject excessive energy through the internal clamping diode structure present on the RCLOCK\_SYNC terminal. The typical trip level of the synchronization terminal is 1.5 V. To ensure proper synchronization and to avoid damaging the IC, the peak-to-peak value (amplitude) should be between 2.5 V and  $V_{DDA}$ . The minimum duration of this pulse must be greater than 200 ns, and its maximum duration must be 200 ns less than the period of the switching cycle.

The external clock synchronization process begins after the TPS65400-Q1 is enabled and an external clock signal is detected. The frequency modulator adjusts the oscillator frequency to match the frequency of the pulses into the RCLOCK\_SYNC terminal. It generally takes 50 cycles before the PWM frequency locks. If the external clock signal is removed after frequency synchronization, the master clock  $F_{OSC}$  drifts to the frequency selected by ROSC.

#### 8.3.6 Phase Interleaving

The TPS65400-Q1 offers the ability to output rails of higher currents by connecting SW1 and SW2 in parallel, or by connecting SW3 and SW4 in parallel. To configure this option, the COMP2 or COMP4 terminal must be tied to VDDA through a  $4-k\Omega$  resistor.

Upon the initialization sequence after a reset, the TPS65400-Q1 attempts to discharge the COMP terminal through a 2-k $\Omega$  internal resistor. When it detects that the COMP terminal is pulled high, it configures itself to operate in current sharing mode. If SW2 is set to current sharing mode, its PWM output is controlled by the error amplifier and COMP1 terminal of SW1 and set to the same frequency as SW1. Likewise, if SW4 is set to current sharing mode, its PWM output is controlled by the error amplifier and COMP3 terminal of SW3 and set to the same frequency as SW3. This means that the frequency settings for SW2 and SW4 in the EEPROM are ignored in that mode of operation.

When current sharing mode is detected on a particular pair, the output slave's l<sup>2</sup>C access is invalid and the output slave's default settings follow that of its master (see *(00h) PAGE*). The only exception is that the slave switcher PWM is a fixed 180° phase-shift from its master.

| Pair        | Output | Current Sharing Relationship | Switching Frequency | Switching Phase |

|-------------|--------|------------------------------|---------------------|-----------------|

| 014/4 014/0 | SW1    | Master                       | Programmable        | Programmable    |

| SW1-SW2     | SW2    | Slave                        | Follows master      | Master + 180°   |

| 01012 01014 | SW3    | Master                       | Programmable        | Programmable    |

| SW3-SW4     | SW4    | Slave                        | Follows master      | Master + 180°   |

Table 1. Programmable Options When Current Sharing Enabled

#### 8.3.7 Fault Handling

OVP, OCP, and undervoltage protection (UVP) are handled for each switcher independently. OVP or OCP faults that occur on one switcher do not affect the other outputs. There are two exceptions:

- If current-sharing mode (ISHARE) is detected for a switcher that faults, both switchers in parallel have the same response to OVP or OCP.

- When using internal sequencing, in the case of faults occurring during the initial power-up sequence, all switchers are disabled for 500 ms, after which, the startup sequence is restarted.

During the soft-start time for a switcher, all fault signals (OVP, OCP, and UVP) are disabled and reset to the unfaulted condition. The first moment when faults can be triggered is after the end of the soft-start sequence.

OVP thresholds are set as a percentage of VREF. A deglitching time of 50 µs is used for the overvoltage. When an overvoltage occurs at the OVP upper threshold limit, the high-side FET and the low-side FET are disabled for that switcher until the OVP falling threshold is reached. When the OVP falling threshold is reached, the low-side FET turns on for 200 ns to ensure that the bootstrap capacitor is recharged before resuming normal operation of the converter.

Output voltage falling below the UVP thresholds causes the corresponding PGOOD output to fall, but the switcher continues to operate as it tries to increase the output voltage. However, if the PGOOD terminal is tied to the enable ENSWx signal of another switcher on the PCB (for external sequencing), the output for that ENSWx-PGOOD-tied switcher is disabled until output voltage is nominal and PGOOD is good.

OTP shuts down all switchers. When the temperature drops below the hysteresis level, a soft reset is triggered and the chip restarts from the startup sequence.

*Fault Monitoring* describes fault reporting and clearing of fault status registers.

The OVP and UVP sensing is deglitched to prevent unwanted tripping. The faults need to be sustained for more than 55 µs typically (60 µs max) to be registered and trigger protection circuits and PGOOD output to fall. Fault detection is disabled on a given switcher when its VREF is being ramped (as result of an I<sup>2</sup>C command to change VREF). An additional 100-µs fault blanking time results after VREF has been adjusted to its target level.

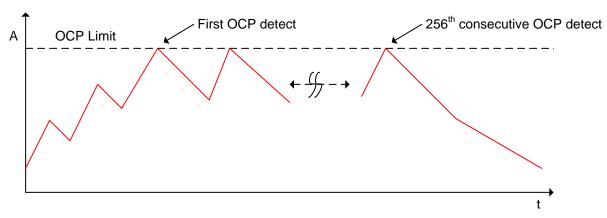

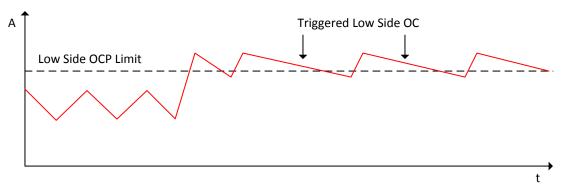

#### 8.3.8 OCP for SW1 to SW4

The OCP is I<sup>2</sup>C-programmable and set by the IOUT\_MAX command. By default, the peak current IOUT\_MAX for SW1 and SW2 is 6 A, and for SW3 and SW4 it is 3 A. When the current reaches this threshold, the unit immediately turns off the high-side FET and keeps the low-side FET off for the remainder of the switching cycle. The following cycle are skipped (high-side FET off, low-side FET off) regardless of the inductor current. If the current in the inductor is still higher than the IOUT\_MAX after the skipped cycle, the following cycles are also skipped until the current reach below the IOUT\_MAX.