Order

Now

## UCC28630, UCC28631 UCC28632, UCC28633, UCC28634

SLUSBW3D - MARCH 2014 - REVISED DECEMBER 2017

# UCC2863x, High-Power Flyback Controller with Primary-Side Regulation and Peak-Power Mode

## 1 Features

- High-Power, Primary-Side CV/CC Regulation

- Continuous Conduction Mode (CCM) and Discontinuous Conduction Mode (DCM) Operation

- Built-In 700-V Start-Up Current Source

- Active X-Capacitor Discharge (UCC28630 and UCC28633)

- Adjustable Constant-Current (CC) Mode Limiting (except for UCC28630)

- High Gate Drive Current 1-A Source and 2-A Sink

- Low Power Modes for <30-mW System Standby

- Best-In-Class Light Load (10%) Efficiency >85%

- PSR design with no opto-coupler can meet high CM isolation & surge requirements

- VDD OVP for independent indirect output OV under open-feedback fault conditions

- Peak-Power Mode for Transient Overload

- Shutdown Pin Interface for External NTC

- Protections: Overvoltage, Overcurrent, Over-Temperature, Overload Timer (UCC28630), AC Line UV, Brownout and Pin Protections

- Frequency Dither to Ease EMI Compliance (except the UCC28632)

- Create a Custom Design Using the UCC2863x With the WEBENCH<sup>®</sup> Power Designer

## 2 Applications

- AC-DC Adapters for Notebook, Game Consoles, Printers

- Open Frame SMPS for Industrial, Printer, White Goods, LCD Monitors

- Energy Efficient AC-DC Supplies for Nominal Power 10-W to 65-W, (with up to 200% transient peak power)

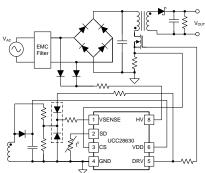

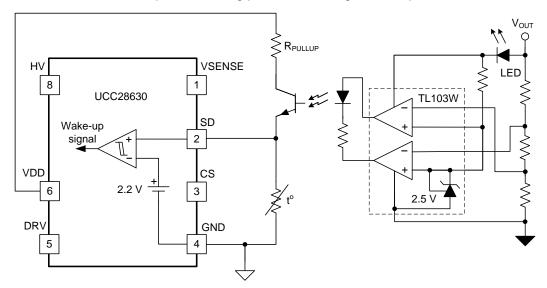

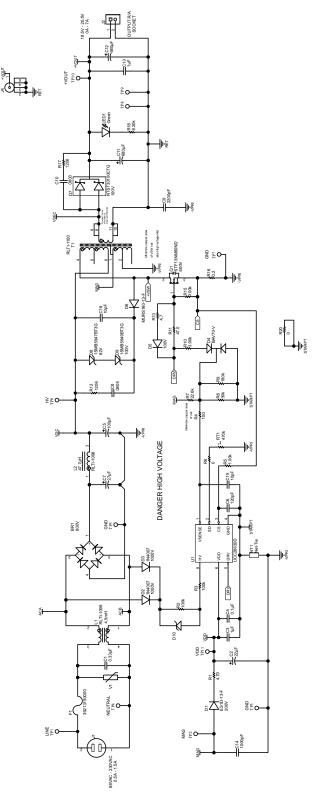

### Simplified Schematic

## 3 Description

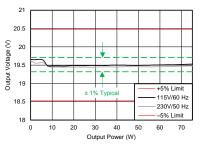

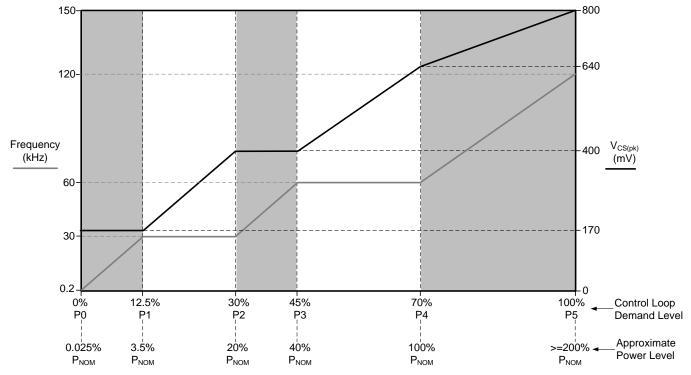

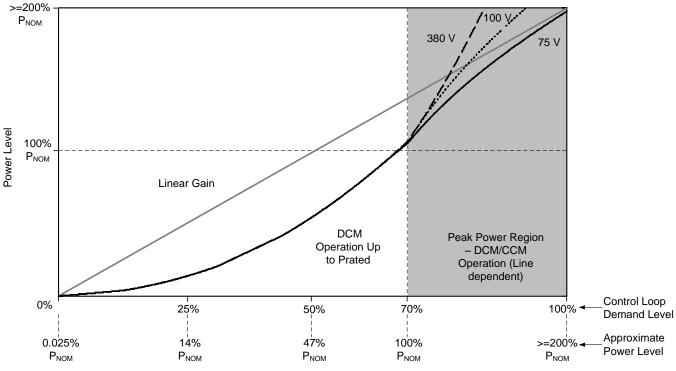

The UCC2863x targets high-power, primary-side regulated flyback converters. The ability to operate in both CCM and DCM make the device suitable for applications with a wide power range. The peak power mode allows transient peak power delivery up to 200% of nominal rating, with only a 25% peak current increase, maximizing transformer utilization.

The transformer bias winding is used to sense output voltage for regulation, and for low-loss input voltage sensing. Advanced sampling techniques allow CCM operation, and deliver excellent output voltage regulation performance for opto-coupler-less designs at power levels of 100 W and above.

A high-voltage current source enables fast and efficient start-up. Advanced light-load modes are deployed to reduce both controller and system power consumption at no load and light load. These modes enable potential system designs to meet 30-mW noload power for power designs up to 30 W nominal, 60 W peak.

The device has been designed for ease-of-use and incorporates many features to enable a wide range of designs. Extensive protection features are included to simplify system design.

See the Device Comparison Table for details.

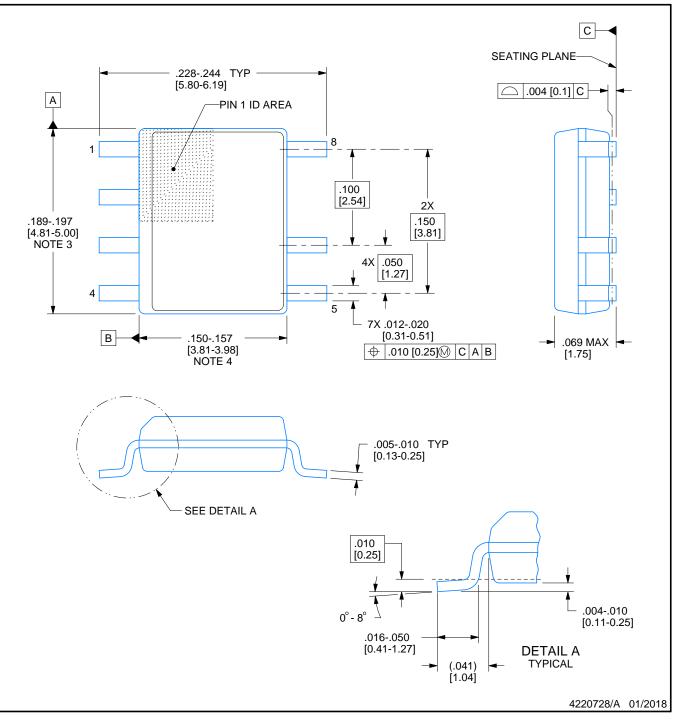

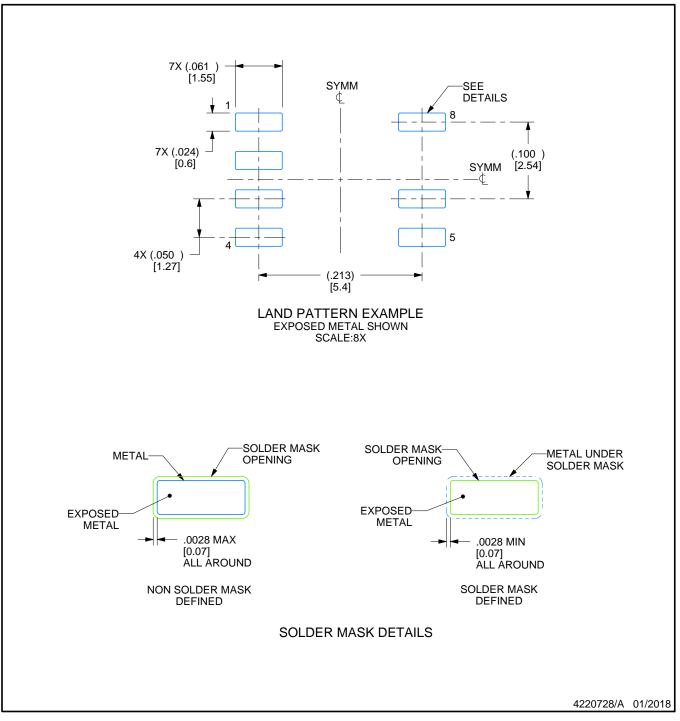

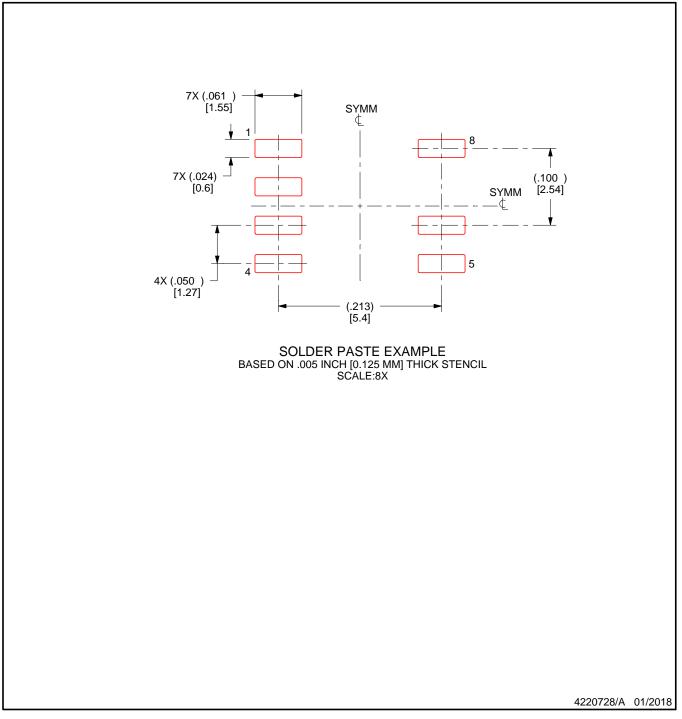

| Device Information |          |                   |  |  |  |  |

|--------------------|----------|-------------------|--|--|--|--|

| PART NUMBER        | PACKAGE  | BODY SIZE         |  |  |  |  |

| UCC28630           |          |                   |  |  |  |  |

| UCC28631           |          |                   |  |  |  |  |

| UCC28632           | SOIC (7) | 4.90 mm x 3.90 mm |  |  |  |  |

| UCC28633           |          |                   |  |  |  |  |

| UCC28634           |          |                   |  |  |  |  |

For all available packages, see the orderable addendum at the end of the data sheet.

### **Typical Application Measured Regulation**

# **Table of Contents**

| 1 | Fea  | tures 1                                                       |

|---|------|---------------------------------------------------------------|

| 2 | Арр  | lications1                                                    |

| 3 | Des  | cription1                                                     |

| 4 | Rev  | ision History 3                                               |

| 5 | Dev  | ice Comparison Table5                                         |

| 6 | Pin  | Configuration and Functions 5                                 |

| 7 | Spe  | cifications                                                   |

|   | 7.1  | Absolute Maximum Ratings 6                                    |

|   | 7.2  | ESD Ratings 6                                                 |

|   | 7.3  | Recommended Operating Conditions 6                            |

|   | 7.4  | Thermal Information (UCC28630, UCC28631)7                     |

|   | 7.5  | Thermal Information (UCC28632, UCC28633, (UCC28630, UCC28634) |

|   | 7.6  | Electrical Characteristics                                    |

|   | 7.7  | Typical Characteristics 10                                    |

| 8 | Deta | ailed Description 13                                          |

|   | 8.1  | Overview 13                                                   |

|   | 8.2  | Functional Block Diagram 14                                   |

|   | 8.3  | Feature Description 15                                        |

|    | 8.4  | Device Functional Modes                         | 52 |

|----|------|-------------------------------------------------|----|

| 9  | App  | lications and Implementation                    | 53 |

|    | 9.1  | Application Information                         | 53 |

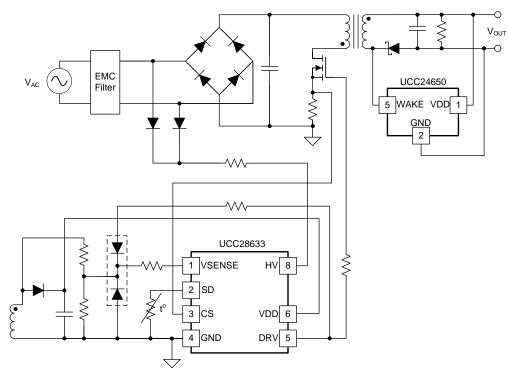

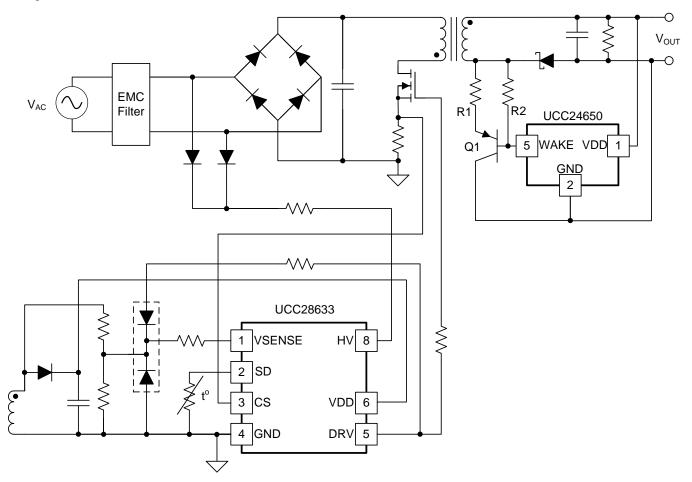

|    | 9.2  | Typical Application                             | 53 |

|    | 9.3  |                                                 |    |

| 10 | Pow  | er Supply Recommendations                       | 73 |

| 11 | Lay  | out                                             | 74 |

|    | 11.1 | Layout Guidelines                               | 74 |

|    | 11.2 | Layout Example                                  | 75 |

| 12 | Dev  | ice and Documentation Support                   | 76 |

|    | 12.1 | Device Support                                  | 76 |

|    | 12.2 | Documentation Support                           | 76 |

|    | 12.3 | Receiving Notification of Documentation Updates | 76 |

|    | 12.4 | Community Resources                             | 76 |

|    | 12.5 | Trademarks                                      | 77 |

|    | 12.6 | Electrostatic Discharge Caution                 | 77 |

|    | 12.7 | Glossary                                        | 77 |

| 13 | Мес  | hanical, Packaging, and Orderable               |    |

|    | Info | mation                                          | 77 |

|    |      |                                                 |    |

2

## **4** Revision History

### Changes from Revision C (March 2015) to Revision D

SLUSBW3D - MARCH 2014 - REVISED DECEMBER 2017

| CI | hanges from Revision C (March 2015) to Revision D                                              | Page |

|----|------------------------------------------------------------------------------------------------|------|

| •  | Added UCC28634 initial release.                                                                | 1    |

| •  | Deleted text "for 65-W Nominal Power Design"                                                   | 1    |

| •  | Added text "PSR design with no opto-coupler - can meet high CM isolation & surge requirements" | 1    |

| •  | Added text "VDD OVP for independent indirect output OV under open-feedback fault conditions"   | 1    |

| •  | Added Webench links                                                                            | 1    |

| •  | Added Device Comparison Table details.                                                         | 1    |

| •  | Added UCC28634 to the Device Information Table.                                                | 1    |

| •  | Added UCC28634 to the Device Comparison Table                                                  | 5    |

| •  | Added UCC28634 to Thermal Information                                                          |      |

| •  | Added UCC28634 to Electrical Characteristics                                                   |      |

| •  | Added UCC28634 to Electrical Characteristics                                                   | 8    |

| •  | Changed picture to represent added UCC28634                                                    | 10   |

| •  | Added UCC28634                                                                                 | 13   |

| •  | Added UCC28634                                                                                 | 15   |

| •  | Added UCC28634                                                                                 | 16   |

| •  | Changed to correct picture link                                                                | 19   |

| •  | Changed to fix equation typo                                                                   | 21   |

| •  | Added UCC28634                                                                                 | 41   |

| •  | Changed to correct typo                                                                        | 41   |

| •  | Changed to correct typo, changed from 4.7 to 47                                                | 41   |

| •  | Added paragraph to clarify the fault protection.                                               | 41   |

| •  | Added UCC28634                                                                                 | 42   |

| •  | Added text "For UCC28634, all pin-faults are non-latching."                                    | 43   |

| •  | Added UCC28634 to the table                                                                    | 52   |

| •  | Changed equation to fix typo                                                                   | 67   |

#### Changes from Revision B (March 2014) to Revision C

#### Page

Page

| • | Changed "No" to "Yes" in Device Comparison Table for Part# UCC28633D, "ACTIVE-X CAPACITOR DISCHARGE" column                       | . 5 |

|---|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| • | Changed "Handling Ratings" table to "ESD Ratings" table. Moved Storage Temperature and Lead Temperature to Abs Max Ratings table. |     |

| • | Revised Figure 40                                                                                                                 |     |

#### Changes from Revision A (January 2014) to Revision B

| • | Added parts UCC28631, UCC28632 and UCC28633 to the datasheet.                       | . 1 |

|---|-------------------------------------------------------------------------------------|-----|

| • | Added Active X-Capacitor Discharge Function reference to the UCC28630 and UCC28633. | . 1 |

| • | Added Adjustable Constant-Current (CC) Mode Limiting bullet.                        | . 1 |

| • | Added Overload Timer reference to the UCC28630 only                                 | . 1 |

| • | Added Frequency Dither to Ease EMI Compliance exception for the UCC28632.           | . 1 |

| • | Added UCC28631D, UCC28632D and UCC28633D to the Device Information Section          | . 1 |

| • | Added Device Comparison Table                                                       | 5   |

| • | Added UCC28632 Frequency dither range exception.                                    | . 8 |

| • | Added UCC28632 Dither repetition period exception.                                  | . 8 |

#### UCC28630, UCC28631 UCC28632, UCC28633, UCC28634 SLUSBW3D – MARCH 2014 – REVISED DECEMBER 2017

TEXAS INSTRUMENTS

www.ti.com

Added UCC28630 and UCC28633 only exception to the "AC sense input for X-capacitor discharge detect" bullet. ........ 15 Added sentence, "In the UCC28631 and the UCC28632, the HV pin can connect to either the AC or DC side of the Added UCC28630 only note added to the Overload Timer Adjustment section. Added CC-Mode I<sub>OUT(lim)</sub> Adjustment section. 41

#### Changes from Original (January 2014) to Revision A

4

### Page

| • | Changed marketing status from Product Preview to Production Data1 |

|---|-------------------------------------------------------------------|

|---|-------------------------------------------------------------------|

## 5 Device Comparison Table

|              | FEATURES                           |                   |                        |                     |                            |  |

|--------------|------------------------------------|-------------------|------------------------|---------------------|----------------------------|--|

| ORDER NUMBER | ACTIVE-X<br>CAPACITOR<br>DISCHARGE | OVERLOAD<br>TIMER | ADJUSTABLE<br>CC LIMIT | FREQUENCY<br>DITHER | SECONDARY-<br>SIDE WAKE UP |  |

| UCC28630D    | Yes                                | Yes               | No                     | Yes                 | SD Pin                     |  |

| UCC28631D    | No                                 | No                | Yes                    | Yes                 | SD Pin                     |  |

| UCC28632D    | No                                 | No                | Yes                    | No                  | SD Pin                     |  |

| UCC28633D    | Yes                                | No                | Yes                    | Yes                 | VSENSE Pin                 |  |

| UCC28634D    | No                                 | No                | Yes                    | Yes                 | SD Pin                     |  |

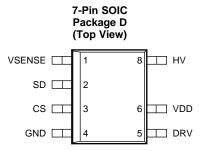

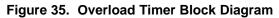

## 6 Pin Configuration and Functions

### **PIN Functions**

| PIN<br>NAME NO. |                                                                                                                                               | 1/0 | DESCRIPTION                                                                                                                                                                                                                     |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                 |                                                                                                                                               | I/O |                                                                                                                                                                                                                                 |  |

| CS              | 3                                                                                                                                             | I   | Current sense input                                                                                                                                                                                                             |  |

| DRV             | 5                                                                                                                                             | 0   | Output drive pin for the external flyback MOSFET                                                                                                                                                                                |  |

| GND             | 4                                                                                                                                             | G   | Ground reference connection for all signals                                                                                                                                                                                     |  |

| HV              | 8                                                                                                                                             | Р   | High-voltage connection to the internal high-voltage start-up current source                                                                                                                                                    |  |

| SD              | 2                                                                                                                                             | I   | Latching fault shutdown input pin. May be connected to an external temperature sensor                                                                                                                                           |  |

| VDD             | 6                                                                                                                                             | Ρ   | Bias supply input pin to the device. Decoupled with a 1-µF ceramic bypass capacitor, connect directly across pins 6-4. Connect an additional hold-up capacitor charged from the transformer auxiliary bias winding to this pin. |  |

| VSENSE          | 1 Sense pin for the flyback transformer bias and sense winding for output feedback regorder output OVP, and input voltage sense/UV protection |     | Sense pin for the flyback transformer bias and sense winding for output feedback regulation, output OVP, and input voltage sense/UV protection                                                                                  |  |

## 7 Specifications

### 7.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating junction temperature range (unless otherwise noted)

|                                       |                                | MIN  | MAX | UNIT |  |

|---------------------------------------|--------------------------------|------|-----|------|--|

| Start-up pin voltage                  | HV                             |      | 700 |      |  |

| Bias supply voltage                   | VDD                            |      | 20  |      |  |

| Current sense input voltage           | cs                             | -0.3 | 1.5 | V    |  |

| All other input size                  | VSENSE                         | -0.3 | VDD |      |  |

| All other input pins                  | SD                             | -0.3 | VDD |      |  |

| Operating junction terr               | perature range, T <sub>J</sub> | -40  | 125 |      |  |

| Storage temperature, T <sub>stg</sub> |                                | -65  | 125 | °C   |  |

| Lead temperature                      |                                |      | 260 |      |  |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. Exposure to absolutemaximum-rated conditions for extended periods may affect device reliability. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. All voltages are with respect to GND. These ratings apply over the junction operating temperature ranges unless otherwise noted.

### 7.2 ESD Ratings

|                    |                                        | VALUE                                                                                 | UNIT  |   |

|--------------------|----------------------------------------|---------------------------------------------------------------------------------------|-------|---|

|                    |                                        | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(2)</sup>                     | ±2000 |   |

| V <sub>(ESD)</sub> | Electrostatic discharge <sup>(1)</sup> | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{\left( 3\right) }$ | ±500  | V |

(1) Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

(2) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions. Pins listed as ±2000 V may actually have higher performance.

(3) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions. Pins listed as ±500 V may actually have higher performance.

## 7.3 Recommended Operating Conditions

over operating junction temperature range (unless otherwise noted)

|                                                                         | MIN | NOM | MAX | UNIT |

|-------------------------------------------------------------------------|-----|-----|-----|------|

| CS input                                                                | 0   |     | 1.0 | M    |

| All other inputs (except HV, CS)                                        | 0   |     | VDD | v    |

| SD pin external capacitance                                             | 0   |     | 1   | nF   |

| R <sub>HV</sub> , external resistor on HV pin, see Figure 15            | 180 | 200 | 220 | ko   |

| R <sub>P</sub> , external pull-up resistor on VSENSE pin, see Figure 21 | 3.8 | 3.9 | 4.0 | kΩ   |

6

7

#### www.ti.com

### 7.4 Thermal Information (UCC28630, UCC28631)

|                         |                                              | UCC28630 | UCC28631 |      |

|-------------------------|----------------------------------------------|----------|----------|------|

|                         | THERMAL METRIC <sup>(1)</sup>                | D        | D        | UNIT |

|                         |                                              | 7 PINS   | 7 PINS   |      |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 128.5    | 128.5    |      |

| $\theta_{\text{JCtop}}$ | Junction-to-case (top) thermal resistance    | 57.3     | 57.3     |      |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 83.4     | 83.4     | °C/W |

| ΨJT                     | Junction-to-top characterization parameter   | 12.3     | 12.3     |      |

| Ψјв                     | Junction-to-board characterization parameter | 82.1     | 82.1     |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 7.5 Thermal Information (UCC28632, UCC28633, (UCC28630, UCC28634)

|                         |                                              | UCC28632 | UCC28633 | UCC28634 |      |

|-------------------------|----------------------------------------------|----------|----------|----------|------|

|                         | THERMAL METRIC <sup>(1)</sup>                | D        | D        | D        | UNIT |

|                         |                                              | 7 PINS   | 7 PINS   | 7 PINS   |      |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 128.5    | 128.5    | 128.5    |      |

| $\theta_{\text{JCtop}}$ | Junction-to-case (top) thermal resistance    | 57.3     | 57.3     | 57.3     |      |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 83.4     | 83.4     | 83.4     | °C/W |

| ΨJT                     | Junction-to-top characterization parameter   | 12.3     | 12.3     | 12.3     |      |

| Ψјв                     | Junction-to-board characterization parameter | 82.1     | 82.1     | 82.1     |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

SLUSBW3D-MARCH 2014-REVISED DECEMBER 2017

### 7.6 Electrical Characteristics

over operating junction temperature range (unless otherwise noted) and VDD = 12 V

|                         | PARAMETER                                                  | TEST CONDITIONS                                                                               | MIN   | TYP    | MAX   | UNIT |

|-------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------|--------|-------|------|

| START-UP                | CURRENT SOURCE                                             | · · · · ·                                                                                     |       |        |       |      |

| I <sub>VDD0</sub>       | VDD pin short-circuit charging<br>current                  | VDD = 0.2 V, V <sub>HV</sub> = 100 V                                                          | 0.6   | 0.9    | 1.2   | mA   |

| I <sub>VDD1</sub>       | VDD pin final charging current                             | VDD = 11.9 V, V <sub>HV</sub> = 100 V                                                         | 1.1   | 4.0    | 7.6   | mA   |

| I <sub>LEAK</sub>       | HV current source leakage current                          | VDD = 18 V, $V_{HV}$ = 100 V HV,<br>current source off, $T_A$ = 25°C                          |       | 0.1    | 0.5   | μΑ   |

| SUPPLY V                | OLTAGE MONITORING                                          |                                                                                               |       |        |       |      |

| V <sub>DD(start)</sub>  | VDD start-up voltage                                       | VDD increasing                                                                                | 13.00 | 14.75  | 16.50 | V    |

| V <sub>DD(stop)</sub>   | VDD minimum operating voltage after start-up               | VDD decreasing after start-up                                                                 | 7.3   | 8.0    | 8.5   | V    |

| V <sub>DD(hyst)</sub>   | VDD start – VDD stop level                                 |                                                                                               |       | 6.5    |       | V    |

| V <sub>DD(reset)</sub>  | VDD reset restart level                                    |                                                                                               | 3.5   | 5.0    | 6.5   | V    |

| V <sub>DD(ovp)</sub>    | VDD over-voltage protection level                          | VDD increasing after start-up,<br>UCC28630, UCC28631, UCC28632,<br>UCC28633                   | 16.5  | 17.5   | 18.3  | V    |

| (                       |                                                            | VDD increasing after start-up,<br>UCC28634 only                                               | 14.0  | 14.85  | 15.55 | V    |

| I <sub>DD(run)</sub>    | Supply current during normal operation                     | $V_{SENSE}$ = 0.45 V, CS = 0 V See <sup>(1)</sup><br>C <sub>LOAD</sub> = 700 pF on DRV        | 6.0   | 9.0    | 13.0  | mA   |

| I <sub>DD(sleep)</sub>  | Supply current during sleep mode, between switching pulses | $V_{SENSE}$ = 8.0 V, $V_{CS}$ = 1.0 V, light-<br>load mode at 200 Hz, $T_A$ = 25°C            |       | 90     | 110   | μΑ   |

| OSCILLAT                | OR                                                         |                                                                                               |       |        |       |      |

| f <sub>SW(max)</sub>    | Maximum switching frequency                                | $V_{SENSE} = 0.45 \text{ V}, V_{CS} = 0 \text{ V}$                                            | 110   | 120    | 130   | kHz  |

| f <sub>SW(min)</sub>    | Minimum switching frequency                                | $V_{SENSE}$ = 8.0 V, $V_{CS}$ = 1.0 V, light-<br>load mode                                    | 0.18  | 0.20   | 0.22  | kHz  |

| D <sub>MAX</sub>        | Maximum Duty Cycle                                         | $V_{SENSE} = 0.45 \text{ V}, V_{CS} = 0 \text{ V}$                                            |       | 70%    |       |      |

| t <sub>ON(min)</sub>    | Minimum On time                                            | $V_{SENSE}$ = 8.0 V, $V_{CS}$ = 1.0 V, light-<br>load mode                                    | 550   | 600    | 650   | ns   |

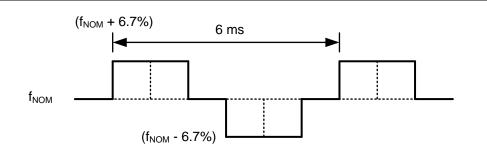

| f <sub>SW(dith)</sub>   | Frequency dither range                                     | Except UCC28632                                                                               |       | ± 6.7% |       |      |

| t <sub>DITH</sub>       | Dither repetition period                                   | Except UCC28632                                                                               |       | 6.0    |       | ms   |

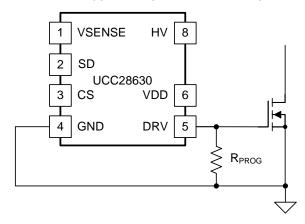

| SHUTDOW                 | N (SD) PIN (EXTERNAL FAULT INPL                            |                                                                                               |       |        |       |      |

| I <sub>PULLUP</sub>     | Internal pull-up current source                            | See <sup>(2)</sup> , <sup>(3)</sup> , <sup>(4)</sup>                                          | 185   | 210    | 235   | μA   |

| V <sub>TRIP(rise)</sub> | Fault ok level (rising)                                    | See <sup>(2)</sup> , <sup>(3)</sup> , <sup>(4)</sup> , UCC28630, UCC28631, UCC28632, UCC28633 | 3.2   | 3.5    | 3.8   | V    |

| ()                      |                                                            | See <sup>(2)</sup> , <sup>(3)</sup> , <sup>(4)</sup> , UCC28634 only                          | 2.2   | 2.5    | 2.8   | V    |

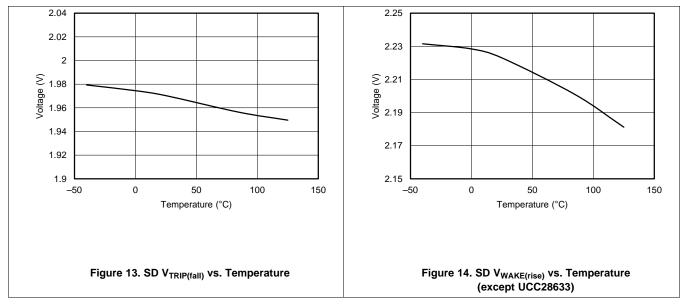

| V <sub>TRIP(fall)</sub> | Fault trip level (falling)                                 | See <sup>(2)</sup> , <sup>(3)</sup> , <sup>(4)</sup>                                          | 1.7   | 2.00   | 2.3   | V    |

| V <sub>TRIP(hyst)</sub> |                                                            | See <sup>(2)</sup> , <sup>(3)</sup> , <sup>(4)</sup>                                          |       | 1.5    |       | V    |

| V <sub>WAKE(rise)</sub> | Wake-up level (rising)                                     | See <sup>(2)</sup> , <sup>(3)</sup> , <sup>(4)</sup> Except UCC28633                          | 1.8   | 2.2    | 2.6   | V    |

| t <sub>WAKE</sub>       | Wake delay time                                            | Delay to first DRV pulse                                                                      |       | 10     |       | μs   |

(1)  $C_{LOAD} = 700 \text{ pF}$  included on DRV pin.

(2) The SD pin functions as an NTC input pin (with internal pull-up) during normal operation. The internal pull-up is clamped to 4 V. At start-up, the external temperature sensor (NTC) must be cool enough that the SD pin pulls up above the V<sub>TRIP(rise)</sub> start level. After start-up, if this pin is pulled below V<sub>TRIP(fall)</sub> level, this activates external over-temperature shut-down.

(3) During low power modes (when F<sub>SW</sub> < F<sub>SMP(max</sub>)), the internal SD pin pull-up is disabled, and the pin functions as a transient wake-up input. In this case, if the pin is raised above V<sub>WAKE(rise)</sub> level, the device wakes from low power sleep mode (rather than waiting for the scheduled timer-based wake). This is useful for applications that require a response to load transients from zero or near-zero load, where a wake-up signal can be appropriately coupled to the SD pin from the secondary-side.

(4) A decoupling capacitor on the SD pin should not be required; if used, it must not exceed 1 nF.

8

9

www.ti.com

### **Electrical Characteristics (continued)**

over operating junction temperature range (unless otherwise noted) and VDD = 12 V

|                       | PARAMETER                                        | TEST CONDITIONS                                                         | MIN   | TYP   | MAX   | UNIT  |

|-----------------------|--------------------------------------------------|-------------------------------------------------------------------------|-------|-------|-------|-------|

| VSENSE P              | in (MAGNETIC SENSE)                              |                                                                         |       |       |       |       |

| V <sub>OUT(ref)</sub> | Internal output voltage sense<br>reference level | Required positive voltage at<br>VSENSE pin during off-time (at<br>25°C) | 7.425 | 7.500 | 7.575 | V     |

| t <sub>OUT(smp)</sub> | Vsense sample delay for $V_{OUT}$                | Measured w.r.t. DRV falling edge                                        |       | 1.7   |       | μs    |

| V <sub>OUT(ovp)</sub> | Internal output voltage sense OVP level          | Measured w.r.t. regulation level, tracking                              |       | 120%  |       |       |

| CURRENT               | SENSE (CS) Pin                                   |                                                                         |       |       | ·     |       |

| V <sub>CS(max)</sub>  | Peak CS pin voltage level                        | At maximum modulator demand                                             |       | 800   |       | mV    |

| V <sub>CS(min)</sub>  | Peak CS pin voltage level                        | At minimum modulator demand                                             |       | 172   |       | mV    |

| V <sub>SLOPE</sub>    | Slope compensation ramp                          |                                                                         |       | 30    |       | mV/µs |

| OVER TEM              | IPERATURE PROTECTION                             |                                                                         |       |       | ·     |       |

| TEMP <sub>TRIP</sub>  | Thermal protection shutdown temperature          | Default internal setting, latch-off protection                          |       |       | 125   | °C    |

| TEMP <sub>HYST</sub>  | Thermal protection hysteresis                    |                                                                         |       | 10    |       | °C    |

| GATE DRIV             | /E OUTPUT (DRV)                                  | · · · · · · · · · · · · · · · · · · ·                                   |       |       |       |       |

| R <sub>OH</sub>       | High level source resistance                     | I <sub>OH</sub> = 100 mA                                                |       | 22    | 35    | Ω     |

| R <sub>OL</sub>       | Low level sink resistance                        | I <sub>OL</sub> = -100 mA                                               |       | 1.2   | 2.5   | Ω     |

#### UCC28630, UCC28631 UCC28632, UCC28633, UCC28634 SLUSBW3D-MARCH 2014-REVISED DECEMBER 2017

TEXAS INSTRUMENTS

www.ti.com

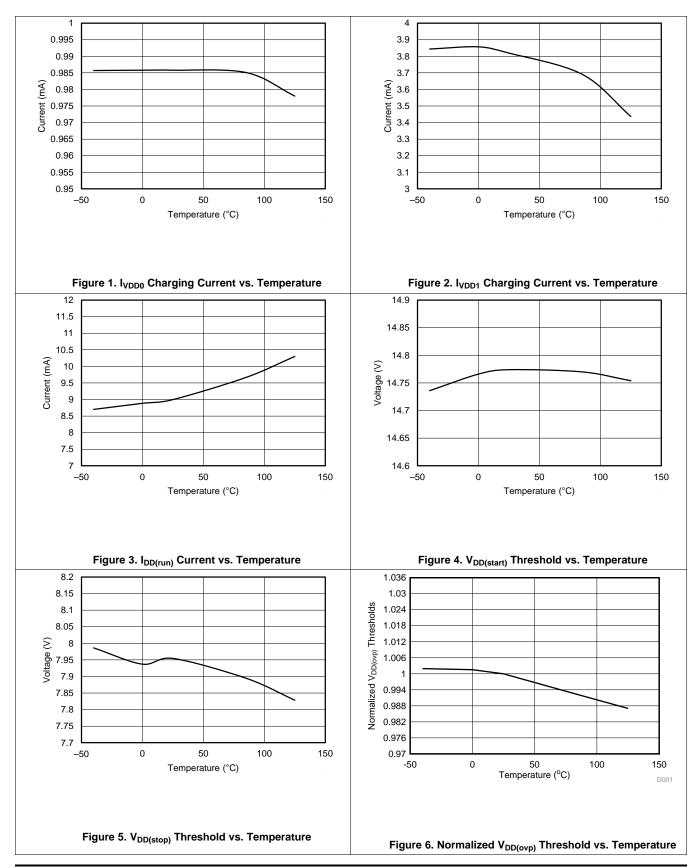

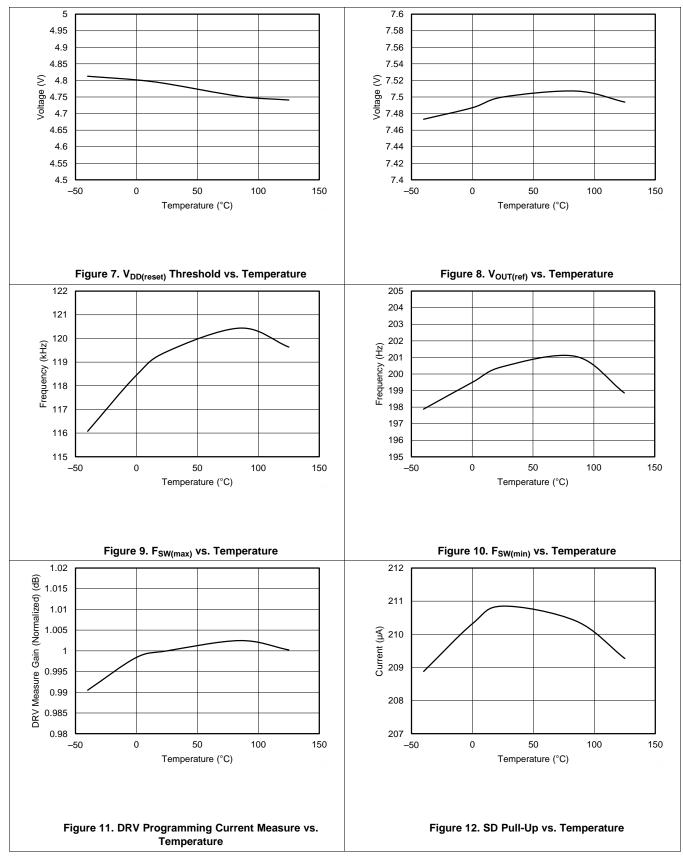

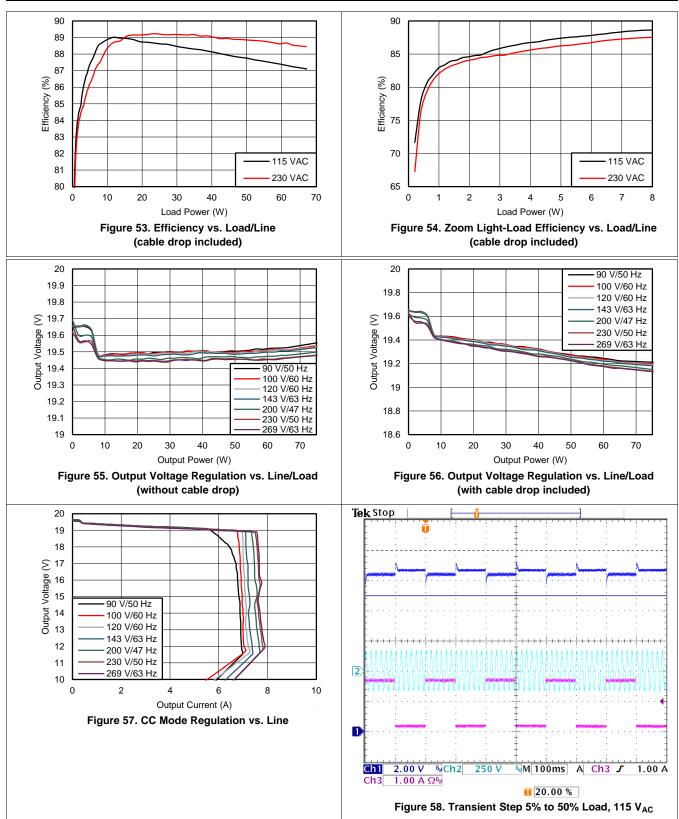

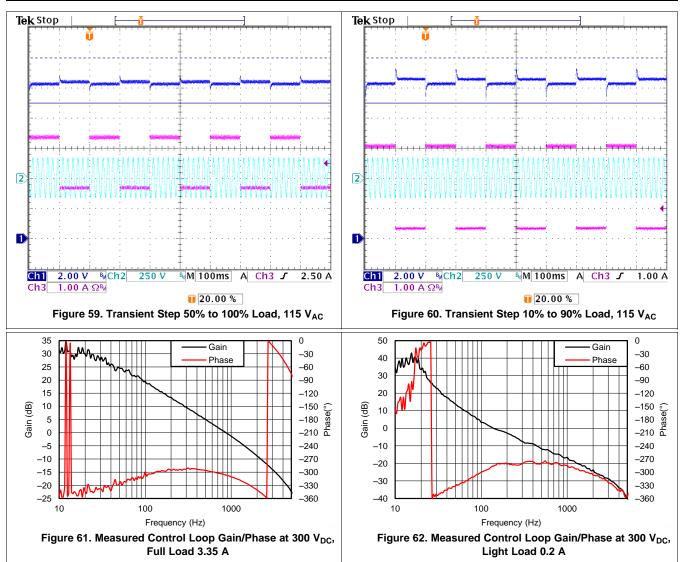

## 7.7 Typical Characteristics

Copyright © 2014–2017, Texas Instruments Incorporated

Product Folder Links: UCC28630 UCC28631 UCC28632 UCC28633 UCC28634

### **Typical Characteristics (continued)**

Product Folder Links: UCC28630 UCC28631 UCC28632 UCC28633 UCC28634

#### UCC28630, UCC28631 UCC28632, UCC28633, UCC28634 SLUSBW3D – MARCH 2014 – REVISED DECEMBER 2017

Texas Instruments

www.ti.com

### **Typical Characteristics (continued)**

## 8 Detailed Description

### 8.1 Overview

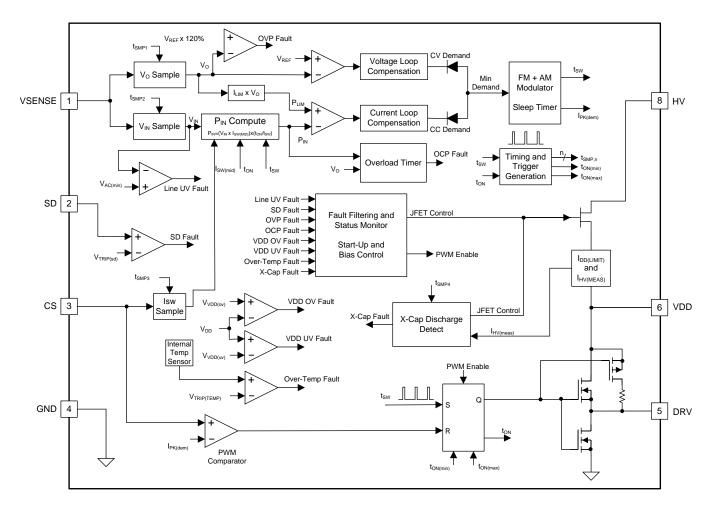

The UCC28630, UCC28631, UCC28633, UCC28633 and UCC28634 family of devices are highly-integrated, primary-side-regulated (PSR) flyback controllers. The device supports magnetically-sensed output voltage regulation via the transformer bias winding. This feature eliminates the need for a secondary-side reference, error amplifier and opto-isolator. The device employs an advanced internal control algorithm that offers accurate static output voltage regulation against line and load. The fixed-point, magnetic-sampling scheme allows operation in both continuous conduction mode (CCM) and discontinuous conduction mode (DCM). Additionally, the device achieves accurate constant-current (CC) control of the output current limit using only primary-side, current sensing. Uniquely, this CC function operates seamlessly as the operating mode changes between DCM and CCM operation.

The controller includes an internal, high-voltage (HV) start-up current-source, and employs low-power sleep modes and switching frequency reduction, to improve light-load efficiency and standby power. The device typically achieves standby power levels between 0.05% and 0.1% of peak output power.

The controller operates in either DCM and CCM, using a mix of peak current-mode PWM (AM) and switchingfrequency modulation (FM) schemes. The control approach improves performance (efficiency, size and cost) and can reduce transformer size and cost by allowing operation in CCM with FM during peak overload conditions. Extensive protection features are incorporated, including output overvoltage protection (OVP), bias rail overvoltage and undervoltage (OV/UV), active X-capacitor discharge, line undervoltage and brownout protection, overcurrent overload timer, open- and short-circuit pin protections, peak current adjustment with line and frequency dither for system EMI reduction. The various devices in the UCC2863x family offer a different mix of features to suit a wide range of applications and requirements.

#### UCC28630, UCC28631 UCC28632, UCC28633, UCC28634 SLUSBW3D – MARCH 2014 – REVISED DECEMBER 2017

Texas Instruments

www.ti.com

### 8.2 Functional Block Diagram

#### 8.3 Feature Description

The application designer requires some key device internal parameters in order to calculate the required power stage components and values for a given design specification. Table 6 summarizes the key parameters.

#### 8.3.1 High-Voltage Current Source Start-Up Operation

The controller includes a switched, high-voltage, current source on the HV pin to allow fast start-up, and eliminates the static power dissipation in a conventional resistive start-up approach. This feature reduces standby power consumption.

The HV pin has three major functions:

- Supply the device start-up current

- Supply the device bias power during latched fault mode

- AC sense input for X-capacitor discharge detect (UCC28630 and UCC28633 only)

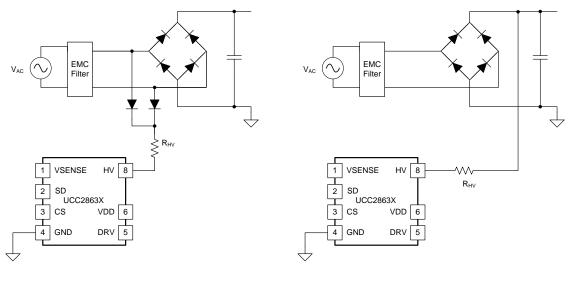

The UCC28630 and UCC28633 input supply to the HV start-up pin must be connected to the AC side of the bridge rectifier as shown in Figure 15, in order to support X-capacitor discharge. More details are given in Active X-Capacitor Discharge (UCC28630 and UCC28633 only), below. Connection to the AC side of the bridge also allows faster detection of AC mains removal under latched fault conditions, allowing prompt reset of latched faults for fast restart.

(a) AC-side

(b) DC-side

Figure 15. HV Pin Connection: (a) AC-side, (b) DC-side (UCC28631, UCC28632 and UCC28634 only)

TEXAS INSTRUMENTS

### Feature Description (continued)

In the UCC28631, UCC28632 and UCC28634, the HV pin can connect to either the AC or DC side of the bridge. The addition of the 200-k $\Omega$  external HV resistance (required for X-capacitor discharge sensing) limits the available charging current for the external bias supply input capacitor. However, for typical values of between 22  $\mu$ F and 33  $\mu$ F of input capacitance, start-up bias times of less than 1.5 s are achievable at 90 V<sub>AC</sub>. Start-up time can be estimated using Equation 1.

$$t_{\text{START}} = R_{\text{HV}} \times C_{\text{VDD}} \times \ln\left(\frac{V_{\text{IN}(\text{avg})}}{V_{\text{IN}(\text{avg})} - V_{\text{DD}(\text{start}\_\text{max})}}\right)$$

where

$$V_{IN(avg)} = V_{RMS} \times \frac{2 \times \sqrt{2}}{\pi}$$

for AC connection and  $V_{IN(avg)} = V_{RMS} \times \sqrt{2}$  for DC connection (1)

For 90 V<sub>AC</sub>, if  $C_{VDD} = 22 \ \mu\text{F}$  and worst case  $V_{DD(\text{start max})} = 16.5 \text{ V}$ , then  $t_{\text{START}}$  is 1.002 s.

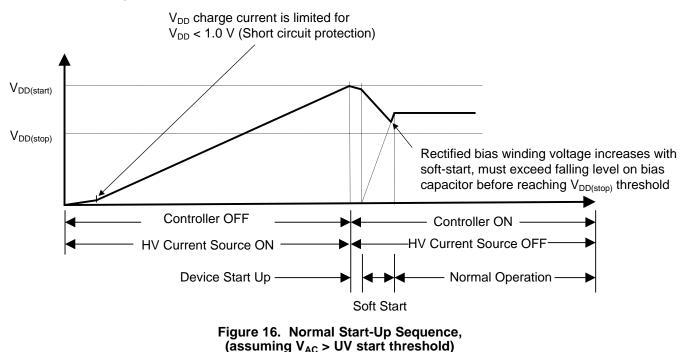

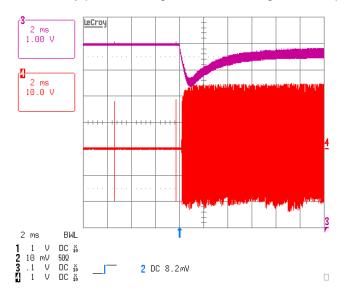

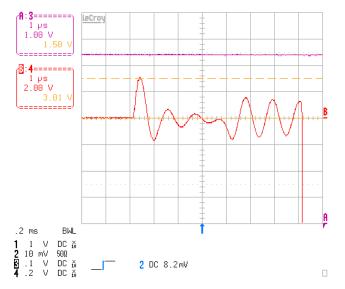

Figure 16 illustrates the start-up behavior of the controller. The HV current source has built-in short-circuit protection that limits the initial charge current out of the bias voltage pin until the bias voltage reaches  $V_{DD(sc)}$ . This limits the power dissipated in the HV current source in the event of a short circuit on the VDD pin. Thereafter, the HV current source switches to full available current. The controller remains in a low-power, start-up mode until the bias voltage reaches  $V_{DD(start)}$ , after which the HV current source is turned off and the controller initiates a start-up sequence.

17

#### www.ti.com

#### Feature Description (continued)

The bias voltage decays during the start-up sequence at a rate dependent on the size of the energy storage capacitor connected to the VDD pin. The VDD storage capacitor must be sized appropriately to ensure adequate energy storage to supply both the controller bias power and MOSFET drive power during start-up, until the VDD rail can be supplied through the transformer bias winding. If the bias voltage falls below  $V_{DD(stop)}$  (due to bias winding fault or an inadequate VDD storage capacitance), the controller stops switching, and transitions into low-power mode for a time delay of  $t_{RESET(long)}$ , or until the bias voltage falls to the  $V_{DD(reset)}$  level, whichever is shorter. See VDD Capacitor Selection for required VDD capacitor sizing. Once the time delay elapses, the bias voltage rapidly discharges to the  $V_{DD(reset)}$  level, followed by turn-on of the internal HV current source, and a normal restart attempt follows.

#### **Feature Description (continued)**

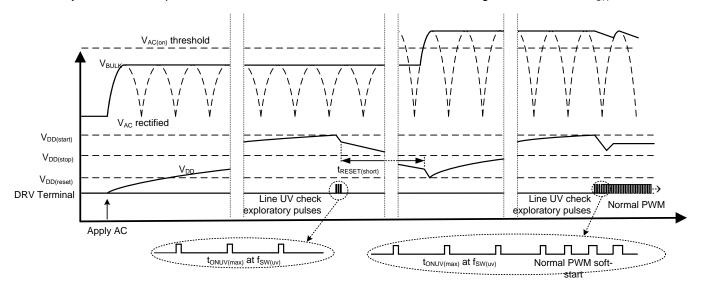

### 8.3.2 AC Input UVLO / Brownout Protection

At start-up, once the VDD pin has reached the  $V_{DD(start)}$  level, the internal start-up current source is turned off. The controller tests the voltage across the bulk capacitor to determine if the level is high enough to allow the power stage to start, if it has exceeded the rising AC<sub>ON</sub> level. Because there is no load across the bulk capacitor at this stage, the bulk voltage can be used as a proxy for the peak of the AC line. In order to measure the bulk voltage in a low-loss fashion, the controller generates a sequence of three exploratory switching pulses at a frequency of  $f_{SW(uv)}$ , at minimum peak-current demand level  $V_{CS(min)}$  to avoid audible noise, and to deliver minimum energy to the output of the power stage.

Based on the magnetic sampling information determined via the bias winding during these switching pulses, if the output voltage is greater than the output overvoltage threshold, the pulsing stops immediately, and the controller transitions into latched-fault mode. If, however, there is no overvoltage condition detected at the output, the pulse-set completes. If the sensed line voltage is above the line  $AC_{ON}$  start threshold, then the controller starts up normally, and begins to generate the PWM drive pulses that charge and regulate the output voltage. Alternatively, if the sensed bulk level is below the  $AC_{ON}$  threshold, then the controller enters low power mode for the reset period ( $t_{RESET(short)}$ ). It then depletes the VDD rail to the  $V_{DD(reset)}$  level. At this point, the start-up sequence repeats, and the device generates another set of exploratory switching pulses. This sequence repeats indefinitely until the AC input is increased to a sufficient level that the bulk voltage exceeds the AC<sub>ON</sub> level.

Figure 17. AC Input UVLO Detection and Start Up

Once started, the controller regularly monitors the bulk capacitor voltage. Because the ripple on the bulk capacitor depends on the load level, the device determines the maximum bulk level every 11 ms (approprite for minimum AC frequency of 47 Hz), so the AC peak can be determined. The controller provides input undervoltage protection based on the sensed AC peak level. Once the peak drops below the  $AC_{OFF}$  level for the delay period ( $t_{UV(delay)}$ ), the PWM switching halts, and the controller enters low-power mode for the reset period ( $t_{RESET(short)}$ ). The device then discharges the bias voltage to the  $V_{DD(reset)}$  level, followed by a restart sequence. The controller cycles through the  $AC_{ON}$ , monitoring (detailed above) indefinitely until the AC input again rises above the  $AC_{ON}$  level.

Product Folder Links: UCC28630 UCC28631 UCC28632 UCC28633 UCC28634

#### Feature Description (continued)

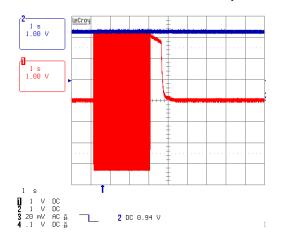

#### 8.3.3 Active X-Capacitor Discharge (UCC28630 and UCC28633 only)

Safety standards such as EN60950 require that any X-capacitors in EMC filters on the AC side of the bridge rectifier quickly discharge to a safe level when AC is disconnected. This discharge requirement ensures that any high-voltage level present at the pins of the AC plug does not present an electric shock hazard. The standards require that the voltage across the X-capacitor decay with a maximum time constant of 1 second. Typically, this requirement is achieved by including a resistive discharge element in parallel with the X-capacitor. However, this resistance causes a continuous power dissipation that impacts the standby power performance. The power dissipation in the discharge resistors depends on the X-capacitor value. Assuming that the discharge resistor meets the 1-second time-constant requirement, (in other words, the R-C product is 1 second) the dissipation is described in Equation 2.

$$P_X = V_{AC}^2 \times C_X$$

(2)

Thus at 230  $V_{AC}$ , the discharge resistor causes 5.3-mW dissipation for every 100 nF of X-capacitance – for a typical 470-nF X-capacitor value, that causes 25 mW to be lost in the discharge resistors.

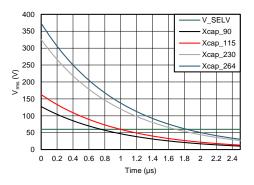

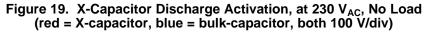

The safety standard does not mandate that the X-capacitor is fully discharged to zero within one second. It simply requires the discharge rate to exhibit a 1-s time constant. Figure 18 shows the discharge characteristic (for a 1-s discharge time constant) versus time, for disconnection at the peak of 90 V<sub>AC</sub>, 115 V<sub>AC</sub>, 230 V<sub>AC</sub> and 264 V<sub>AC</sub>. For AC inputs above 115 V<sub>AC</sub>, with 1-s discharge time constant, the voltage does not drop below the Safety-Extra-Low-Voltage (SELV) 60-V level until 1 s or longer. In fact, at 264 V<sub>AC</sub>, 1.83 seconds elapse before reaching 60 V.

Figure 18. X-Capacitor Discharge with 1-s Time Constant, for Various Voltages

#### Feature Description (continued)

#### 8.3.3.1 Improved Performance with UCC28630 and UCC28633

In order to reduce standby power and eliminate the standing loss associated with the conventional discharge resistors, the UCC28630 and the UCC28633 devices incorporate active X-capacitor discharge circuitry. This circuit periodically monitors the voltage across the X-capacitor to detect any possible DC-condition (which would indicate that AC mains disconnection has occurred), and then discharges the voltage across the X-capacitor using the internal HV current source. The X-capacitor discharge function discharges the X-capacitor to the SELV 60-V level in 1 s (as long as the design considerations discussed in this section are followed).

The device internally monitors the current into the HV pin to determine if the voltage across the X-capacitor in the EMI filter has a sufficient AC ripple component. If insufficient AC content is detected, then a DC condition is internally flagged. This causes the controller to enter low-power mode for the reset period ( $t_{RESET(short)}$ ), followed by bias voltage discharge to the reset level ( $V_{DD(reset)}$ ), and then the start-up HV current source turns on again to effectively discharge the X-capacitor by transferring charge to the VDD reservoir capacitor.

Because the device monitors the HV pin to detect a DC condition on the X-capacitor, the system cannot operate with DC input to the HV pin. Instead, the HV pin must be connected to an AC source only. The device interprets any DC input on the HV pin as DC across the X-capacitor, indicating an AC-disconnect event. This causes a repeating cycle of start-up and shutdown. The device requires an external 200-k $\Omega$  of resistance on the HV pin, to limit the current to a level below the saturation point of the internal HV current source. This limit produces a HV input current that is approximately proportional to AC line, so that the AC content can be sensed.

The size of the X-capacitor that can be discharged depends on the VDD energy storage capacitor. Assuming the worst case, a maximum X-capacitor disconnect voltage could be at the peak of 264  $V_{RMS}$ , and assuming that it should be discharged down to 60-V SELV level, the minimum allowed VDD capacitor can be sized based on the worst case  $V_{DD(reset)}$  and  $V_{DD(start)}$  levels as described in Equation 3.

$$C_{VDD} \ge C_{X} \times \left(\frac{V_{AC(pk)} - V_{SELV}}{V_{DD(start_min)} - V_{DD(reset_max)}}\right) = C_{X} \times \left(\frac{373 - 60}{13.0 - 6.5}\right) = C_{X} \times (48.15)$$

(3)

For example, for a 330-nF X-capacitor value, the required VDD capacitor is 15.9  $\mu$ F, so a 22- $\mu$ F capacitor suffices.

$C_{VDD} \ge 330 \text{ nF} \times (48.15) = 15.9 \, \mu\text{F}$

In order to reduce the power consumption from the high voltage AC line, the device pulses current into the HV pin at a low frequency with very low duty-cycle. The HV current source on-time  $(t_{ON(HV)})$ , repeats at intervals of  $t_{SMP(HV)}$ . Moreover, the pulsing occurs in bursts, with a time delay between bursts. The sampling occurs in bursts of 21, at intervals of  $t_{SMP(HV)}$ , with a wait time of  $t_{WAIT(HV)}$  between bursts. This reduces the effective average duty-cycle to a very low value (approximately 0.2%), and minimizes the overhead of X-capacitor sampling current and device bias consumption overhead to approximately 2 mW of extra standby consumption at high-line 230 V<sub>AC</sub>.

The device enables the X-capacitor monitor in latched fault mode, and in light-load regions where the power level is below  $P_{LL(\%)}$ , as a percentage of the nominal rated level. Above the  $P_{LL(\%)}$  level, the X-capacitor monitor is disabled. At this load level the bulk capacitor discharges at a rate that is sufficient to also discharge the X-capacitor, which appears in parallel with the bulk capacitor once the bulk voltage drops far enough to forward bias the bridge rectifier diodes. In this case ensure that the bulk capacitor discharge rate is fast enough to olischarge the X-capacitor to meet the 1-s discharge target. This can be calculated in Equation 5.

$$C_{BULK} \leq \frac{2\left(\frac{P_{NOM} \times P_{LL\%}}{\eta}\right) \times t_{XCAP(dis)}}{\left(V_{AC(pk)}^{2} - V_{SELV}^{2}\right)}$$

(5)

(4)

(6)

(7)

(8)

#### www.ti.com

#### Feature Description (continued)

Assuming a worst case AC disconnect at the peak at 264  $V_{RMS}$  (373  $V_{PK}$ ), and a requirement to discharge to SELV level of 60 V in  $t_{XCAP(dis)}$  of 1 s, for a  $P_{NOM}$  of 65 W at 87% efficiency, this is calculated in Equation 6.

$$C_{\text{BULK}} \le \frac{2 \times \left[\frac{(65 \times 0.125)}{0.87}\right] \times 1}{(373^2 - 60^2)} = 138 \,\mu\text{F}$$

Once the bulk capacitance value is chosen, also ensure that when the bulk capacitor has been discharged down to the line UV  $AC_{OFF}$  threshold, that it continues to discharge to an acceptable level during the line UV persistence delay time ( $t_{UV(delay)}$ ) as shown in Equation 7.

$$C_{\text{BULK}} \leq \frac{2 \times \left(\frac{P_{\text{NOM}} \times P_{\text{LL\%}}}{\eta}\right) \times t_{\text{UV(delay)}}}{2 \times A C_{\text{OFF}}^2 - V_{\text{SELV}}^2}$$

Again, taking the example above:

$$C_{\text{BULK}} \le \frac{2 \times \left(\frac{(65 \times 0.125)}{0.87}\right) \times 0.04}{(2 \times 65^2 - 60^2)} = 154 \,\mu\text{F}$$

Once the first constraint is satisfied, the second one is also automatically met.

Copyright © 2014–2017, Texas Instruments Incorporated

### Feature Description (continued)

Figure 20. X-Capacitor Decay Rate Without Active Discharge (time constant dominated by  $20-M\Omega$  probe impedance) (red = X-capacitor, blue = bulk-capacitor, both 100 V/div)

#### Feature Description (continued)

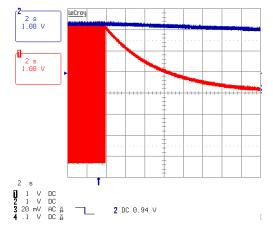

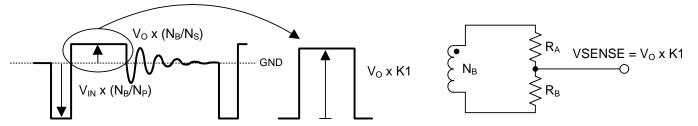

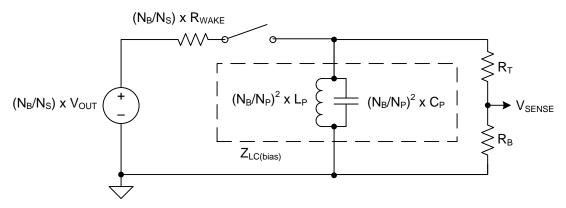

#### 8.3.4 Magnetic Input and Output Voltage Sensing

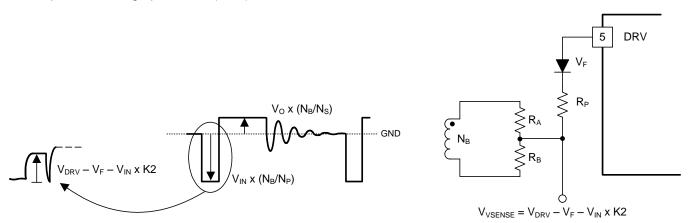

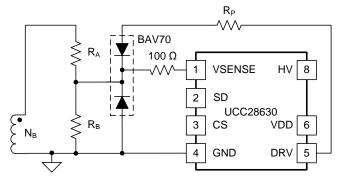

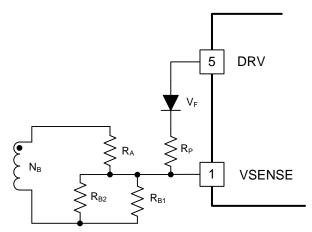

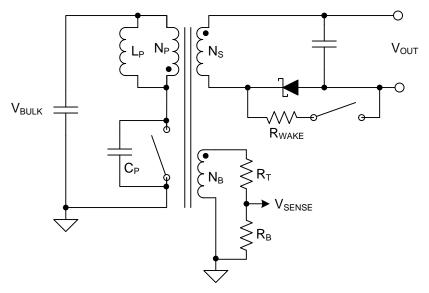

A sense winding on the transformer is used to measure the input voltage and output voltage of the power stage. This winding is typically the converter bias winding. The sense winding should be interfaced to the VSENSE pin as shown in Figure 21. This interface requires that the voltage across the winding be scaled with a resistor divider  $R_A / R_B$ , and then offset with a switched, pull-up resistor  $R_P$  (in series with a diode) connected to the gate drive pin DRV.

Figure 21. VSENSE Pin Interface Arrangement

During the off-time portion of the switching cycle (also referred to as the flyback interval), the resistor divider ( $R_B / (R_A + R_B)$ ) scales the positive voltage swing at the VSENSE pin for output voltage regulation, as shown in Figure 22. During this interval, since the DRV output is low, the diode in series with  $R_P$  is reverse-biased, and so  $R_P$  is out-of-circuit.

Figure 22. V<sub>OUT</sub> Sense Using the Positive Swing on the Sense Winding

#### UCC28630, UCC28631 UCC28632, UCC28633, UCC28634 SLUSBW3D-MARCH 2014-REVISED DECEMBER 2017

TEXAS INSTRUMENTS

www.ti.com

### Feature Description (continued)

During the on-time portion of the switching cycle, when the DRV pin goes high (should swing very close to the value at the VDD pin), the switched pull-up  $R_P$  allows the negative swing on the winding to be level-shifted positive, and thus also be sensed at the VSENSE pin, as shown in Figure 23. In this way the bias winding may be used to sense both line input voltage and output voltage.

#### NOTE

The input voltage sensed by the transformer bias winding is actually the voltage across the bulk capacitor, not the AC input voltage, because the bulk capacitor voltage appears across the primary winding when the flyback switch turns on

Uses of the sensed bulk and output voltages:

- Input AC mains UVLO

- Input brownout

- Line-dependent peak-current adjustment

- Accurate output-current regulation

- Output-voltage regulation

- Output over-voltage protection (OVP)

Figure 23. Line Input Sense by Offsetting the Negative Swing on the Sense Winding

In order to protect the VSENSE pin from excessive negative current in the event of a manufacturing fault (such as an open circuit on R<sub>P</sub>), use a series limiting resistor and clamping diode on the VSENSE pin. Combine the clamping diode and DRV pull-up diode into a single-package common-cathode diode to reduce the component count of the system. This is illustrated in Figure 24.

Figure 24. VSENSE Pin Protection and Interface to Bias Winding

24 Submit Documentation Feedback

#### Feature Description (continued)

The device continually adjusts the input voltage sample delay, measuring the sample half-way through the ontime interval, to ensure the cleanest signal. The device uses same mid-point sample trigger when measuring the main MOSFET switch current ( $I_{SW}$ ). Sampling MOSFET switch current in the middle of the on-time automatically measures the average current during the on-time,  $I_{SW(on\_avg)}$ , which is required for the current limit and overload timer block.

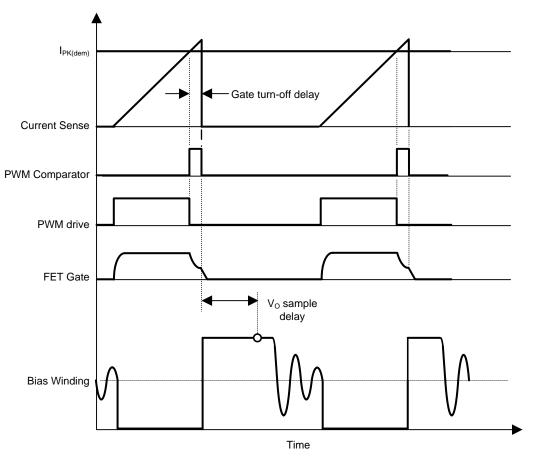

The output voltage sample point is always time relative to the turn-off instant. Internally, the device uses the CS pin to determine the cycle end, rather than the PWM falling edge on the DRV pin. The device bases this determination on the instant that the MOSFET switch current drops below the demanded peak current level ( $I_{PEAK}$ ) at the peak current mode comparator. Some delay always occurs from the falling edge on DRV to the point when the external power MOSFET turns off. This internal timing method ensures a more accurate measure of  $I_{SW(on\_avg)}$ , and also ensures that the output voltage sample point is not measured too early, before the leakage ringing has subsided. The effect of the gate turn-off delay and the adjustment of the output voltage sample point is illustrated in Figure 25.

Figure 25. V<sub>OUT</sub> Sample Adjust for External Gate Delay

#### UCC28630, UCC28631 UCC28632, UCC28633, UCC28634 SLUSBW3D-MARCH 2014-REVISED DECEMBER 2017

www.ti.com

### **Feature Description (continued)**

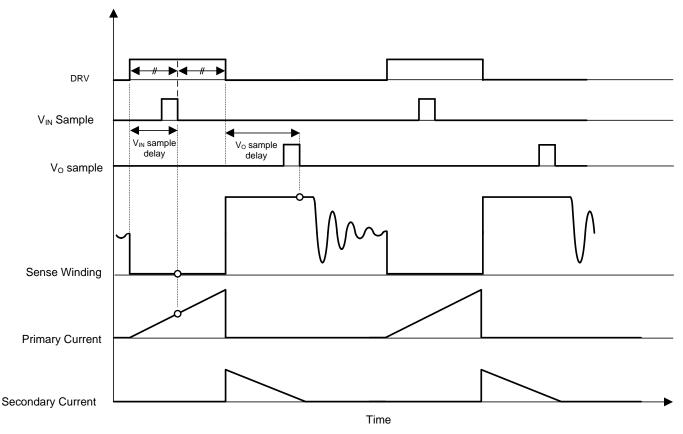

The sampling of the input voltage and output voltage signals on the bias winding must be synchronized to the ontime and off-time flyback intervals respectively, because the signals occur during only those intervals in the switching cycle. Typical waveforms and timing are illustrated in Figure 26.

More conventional *knee-point* detection schemes, where the sample is measured at the end of the flyback interval when the secondary-side current has decayed to zero, inherently always operate in discontinuous conduction mode (DCM). However, the fixed sample-point scheme used on the UCC2863x has the advantages of being able to operate in regions of fixed frequency, and being able to operate in continuous conduction mode (CCM). Fixed sample-point schemes conventionally suffer poorer regulation than *knee-point* schemes, because there is always current flowing at the sample instant. This current produces a sensing error as a result of the voltage drop produced across the secondary-side resistance and leakage inductance. This parasitic voltage drop varies with output voltage, line and load, thus influencing the regulation. The UCC2863x devices uses a novel internal compensation scheme to adjust for this parasitic voltage drop, and can deliver excellent static line and load regulation, even when operating heavily in CCM.

Figure 26. V<sub>IN</sub> and V<sub>OUT</sub> Sample Trigger Timing

Product Folder Links: UCC28630 UCC28631 UCC28632 UCC28633 UCC28634

#### Feature Description (continued)

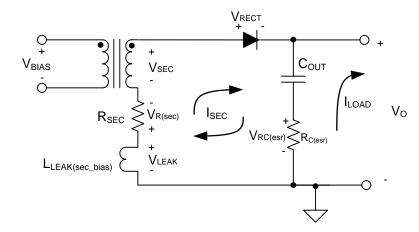

#### 8.3.5 Fixed-Point Magnetic Sense Sampling Error Sources

To support operation in CCM, and allow operation at fixed frequency over a large percentage of the load range, the UCC2863x uses fixed-point sampling rather than *knee-point* detection. When conventionally used, fixed-point sampling typically suffers from poorer regulation performance. This poor performance results from the voltage drops across the secondary-side parasitic resistance  $R_{SEC}$ , and the secondary-side leakage inductance from secondary-side to bias  $L_{LK(sec\_bias)}$ , as a consequence of the fact that current remains flowing on the secondary-side when the device measures the output voltage. As shown in Figure 27, the secondary-side pin voltage that gets reflected to the bias winding is detailed in Equation 9.

$$V_{SEC} = V_{OUT} + V_{RECT} + V_{R(sec)} - V_{L(leak)} + V_{RC(esr)}$$

(9)

Equation 9 can be expanded and rearranged into Equation 10.

$$V_{SEC} = V_{OUT} \times \left(1 - \frac{L_{LK(sec \ bias)}}{L_{SEC}}\right) + V_{RECT} + I_{SEC} \times \left(R_{SEC} + R_{C(esr)}\right) - \left(I_{LOAD} \times R_{C(esr)}\right)$$

(10)

Figure 27. Secondary-Side Pin Voltage Contributors with Secondary-Side Current Flow

### Feature Description (continued)

Many elements contribute errors to the sensed secondary-side pin voltage, when measured across the bias winding:

- V<sub>L(leak)</sub>: Negative voltage drop across the sec-bias leakage inductance L<sub>LK(sec\_bias)</sub>; assuming constant regulated output voltage, this voltage drop is fixed constant offset, because V<sub>OUT</sub>/L<sub>SEC</sub> is constant as long as the output is in regulation.

- V<sub>RECT</sub>: Positive voltage drop across the output rectifier (assuming use of a conventional diode). This voltage drop varies with load current and temperature. However, a constant nominal voltage drop can usually be used, because the increasing forward voltage drop with increasing load current is largely cancelled by the decrease in forward drop as a result of the temperature rise that results.

- V<sub>R(sec)</sub>: This is the drop across the secondary-side winding resistance. This value depends on loading, and varies in proportion to the primary peak current demand that is set by the modulator.

- V<sub>RC(esr)</sub>: This is the drop across the output capacitor equivalent series resistance (esr). This value depends on the difference between the secondary-side winding current and the DC load current being drawn.

Typically, the peak secondary-side winding current  $I_{SEC}$  is many times larger than the load current, and the secondary-side winding resistance is typically larger than the output capacitor esr. Thus, the last term in Equation 10 involving  $I_{LOAD}$  can typically be neglected.

The leakage inductance and secondary-side rectifier terms represent quasi-constant offset terms, so do not affect regulation to a significant extent. Thus, the quasi-constant offset terms can be accounted for in the calculation of the required scaling resistors to produce the desired setpoint voltage.

The remaining term that dominates the regulation error in Equation 10 is the drop across the secondary-side winding resistance and capacitor esr at the sample instant, { $I_{SEC} x(R_{SEC} + R_{C(esr)})$ }. The controller internally adjusts the control loop reference in proportion to the primary peak current demand in order to null the  $I_{SEC}$  related error term in the sampled bias winding voltage. Since the peak secondary-side current  $I_{SEC(pk)}$  is the primary peak current  $I_{PRI(pk)}$  scaled by the transformer turns ratio, the internal control loop reference effectively varies in approximate proportion to  $I_{SEC}$ , resulting in dramatically improved regulation performance.

This improved regulation performance allows the use of primary-side regulation in a wider range of applications, and at unprecedented power levels, operating in both CCM and DCM.

#### Feature Description (continued)

#### 8.3.6 Magnetic Sense Resistor Network Calculations

Because the device uses the VSENSE pin to measure both  $V_{OUT}$  and  $V_{IN}$  of the power stage, it is important to calculate the resistor values correctly. The step-by-step design process is outlined in this section.

### 8.3.6.1 Step 1

Depending on the power level, choice of transformer size, and required trade-offs between primary MOSFET and secondary-side rectifier ratings, the transformer turns  $N_P$ ,  $N_S$  and  $N_B$  will be chosen first. The controller can support a wide range of turns ratios.

#### Figure 28. Practical Magnetic Sense Setup with Extra Resistor R<sub>B2</sub> for Setpoint Fine Adjust

#### 8.3.6.2 Step 2

Once N<sub>P</sub>, and N<sub>B</sub> are known, the required value of R<sub>A</sub> in Figure 28 is calculated using Equation 11.

$$R_A = R_P \times \left(\frac{N_B}{N_P}\right) \times K_{LINE}$$

(11)

In this equation, the internal controller gain  $K_{\text{LINE}}$  is 49.25 (see Table 6 for key internal controller parameters), and the internal gains are designed for a fixed value for  $R_P$ , (i.e.  $R_P$  MUST be 3.9 k $\Omega$ ).

### Feature Description (continued)

### 8.3.6.3 Step 3

Once N<sub>S</sub>, target V<sub>OUT</sub>, output rectifier drop V<sub>RECT</sub>, and the secondary-side-to-bias leakage inductance L<sub>LK(sec\_bias)</sub> are known, the required value for R<sub>B</sub> can be calculated. Referring to Equation 10, L<sub>LK(sec\_bias)</sub> can be approximated as a percentage of the secondary-side-referred magnetizing inductance L<sub>SEC</sub>. (See Magnetic Sense Resistor Network Selection for details).

$$R_{B} = \frac{R_{A}}{\left(\frac{\left(V_{OUT} \times \left(1 - \%L_{LK(sec\_bias})\right) + V_{RECT}\right) \times \left(\frac{N_{B}}{N_{S}}\right)}{V_{OUT(ref)}} - 1\right)}$$

(12)

In this case,  $R_B$  may need to be empirically adjusted to achieve the required exact output set-point, especially if  $V_{RECT}$  varies or is not known precisely. For this reason, it is recommended that  $R_B$  should be implemented on the system PCB as two parallel resistors  $R_{B1}$  and  $R_{B2}$  as shown in Figure 28, to allow easier fine-tuning of set-point. For set-point tuning, only  $R_B$  should be adjusted.  $R_A$  should never be adjusted, because to do so would affect the line sense gain and introduce errors into the line voltage measurement.

### 8.3.6.4 Step 4

Verify that the equivalent Thevenin resistance  $R_{TH}$  of the  $R_A/R_B$  combination falls in the required range of 10 k $\Omega$  to 20 k $\Omega$ .

$$R_{TH} = \frac{R_A \times R_B}{R_A + R_B}$$

(13)

10 k $\Omega < R_{TH} < 20 k\Omega$  (14)

If the Thevenin resistance is outside of that range, then the original choice of turns ratio must be adjusted, and design steps repeated until a valid value for  $R_{TH}$  is determined. This is unlikely to occur in practice, unless an extreme turns ratio is chosen. If  $R_{TH}$  is outside this range, it triggers the VSENSE pin open or short pin-check at start-up.

#### Feature Description (continued)

#### 8.3.7 Magnetic Sensing: Power Stage Design Constraints

$V_{RECT}$  is the voltage drop across the output rectifier

delay. The choice of transformer turns ratio, transformer inductance (LPRI), and current sense resistance (RCS) must ensure that the corresponding reset volt-seconds during the flyback interval are sufficient that a valid output sample is available at the sample point, t<sub>OUT(smp)</sub>. This constraint is summarized in Equation 15.

$$\frac{R_{CS}}{L_{PRI}} \le \frac{V_{CS(min)}}{t_{OUT(smp)}} \times \frac{N_S}{N_P} \times \frac{1}{(V_{OUT} + V_{RECT})}$$

where

٠

(15)

Additionally, the device requires a minimum on-time, t<sub>ON(min)</sub>, to ensure enough time for the system input voltage (V<sub>IN</sub>) and switch current (I<sub>SW</sub>) to be measured. To meet the minimum on-time requirement at maximum line, and minimum load, the ratio of current sense resistance (R<sub>CS</sub>) to transformer inductance (L<sub>PRI</sub>) must meet the constraint shown in Equation 16

$$\frac{R_{CS}}{L_{PRI}} \le \frac{1}{V_{IN(pk_{max})}} \times \frac{V_{CS(min)}}{t_{ON(min)}}$$

(16)

Equation 15 or Equation 16 sets the limit for the ratio of R<sub>CS</sub> to L<sub>PRI</sub>, but both need to be verified. See Typical Application for more details.

### **Feature Description (continued)**

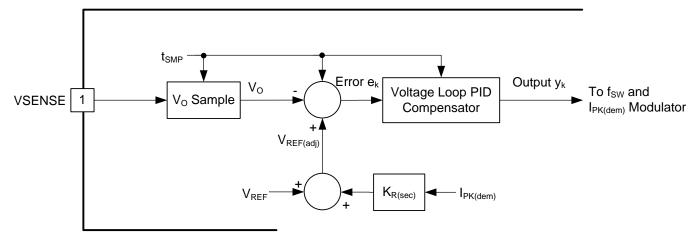

#### 8.3.8 Magnetic Sense Voltage Control Loop

Because the output voltage feedback is inherently a sampled signal obtained from the bias winding, the internal voltage control loop is most naturally implemented digitally. The internal control loop implements the equivalent of a PID loop in digital form. Because the output can be sampled only at certain intervals in each switching cycle, the sample rate is naturally tied to the switching frequency, and the sample rate increases with increasing frequency. However, the device clamps the sample rate at a normalized maximum rate, f<sub>SMP(max)</sub>. But because the device must always synchronize to the next available switching cycle to obtain a new sample of the output voltage, the effective sample rate varies somewhat around this value.

The digital control loop compensator block diagram is shown in Figure 29. A new sample of output voltage is supplied to the compensator at the normalized maximum clock rate  $(f_{SMP(max)})$ , or  $f_{SW}$ , whichever is lower. An updated output voltage demand signal,  $y_k$ , is produced at the same clock rate. This voltage loop demand represents the required operating point on the modulator curves to keep the output voltage in regulation. The modulator sets the appropriate switching frequency and peak current demand depending on the load power.

Figure 29. Digital Voltage Control Loop Simplified Block Diagram

The control loop PID gain factors are internally fixed values, optimized for flyback power stages in the range between 20 W and 130 W. The loop is designed to work with magnetizing inductance values in the range between 200  $\mu$ H and 1500  $\mu$ H. Assuming that the output capacitance value is chosen based on required ripple current rating, then loop stability is not a problem. Adding extra output capacitance does not degrade the loop performance and the resulting extra output hold-up improves transient response.

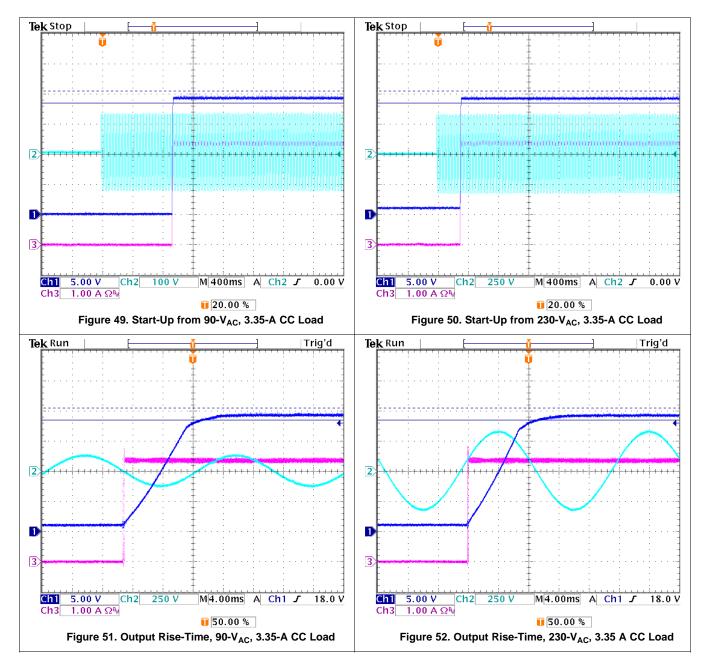

The Typical Application section includes gain-phase measurements taken using the 65-W UCC28630EVM-572 evaluation module.

Product Folder Links: UCC28630 UCC28631 UCC28632 UCC28633 UCC28634

#### Feature Description (continued)

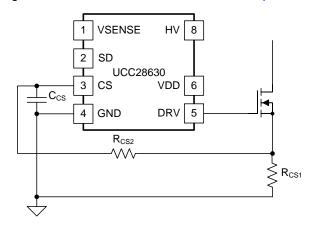

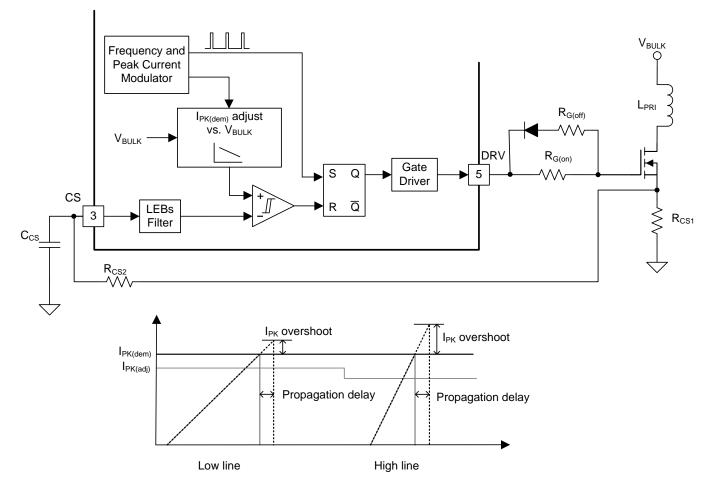

#### 8.3.9 Peak Current Mode Control

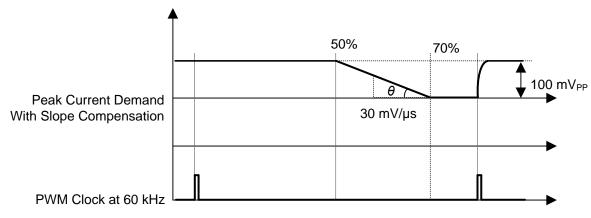

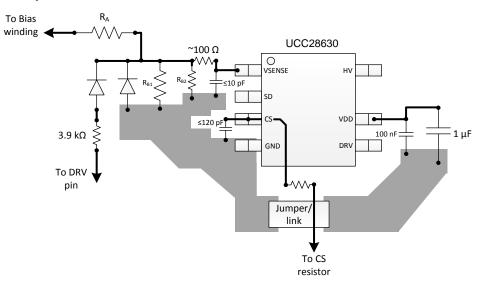

The controller operates in peak current mode. The primary-side switch (MOSFET) current is sensed by a shunt resistor ( $R_{CS1}$ ) connected in series with the source of the FET as shown in Figure 30. The voltage that is developed across the sense resistor is connected to the CS pin of the controller. The device uses the current sense signal at the CS pin to terminate the PWM pulse according to the peak current demand of the modulator. The device automatically applies slope compensation as soon as the duty cycle of the DRV pin pulse exceeds 50%. This compensation provides stable operation up to maximum DRV duty cycle. The device applies this slope compensation as a downslope on the demand signal at the PWM comparator, so is not measureable at the CS pin. The device synchronizes the slope compensation signal to the PWM and is active only between 50% and 70% duty cycle, as shown in Figure 31.

Normal operating range for the CS pin is between 0 mV and 800 mV. The R<sub>CS1</sub> resistor should be scaled such that the peak current at maximum peak load and minimum bulk capacitor voltage produces a signal of approximately 800 mV peak at the CS pin. This resistor value is calculated in conjunction with the calculation of the required primary magnetizing inductance, as outlined in Notebook Adapter, 19.5 V, 65 W, section.

Figure 30. Primary-Side Current Sensing

### Feature Description (continued)

A nominal 100 ns of filtering that is internal to the CS pin helps filter the leading turn-on spike of current. Depending on PCB layout, an RC filter ( $R_{CS2}$  and  $C_{CS}$ ) may be required on the CS pin as shown in Figure 30 to filter noise and spikes. The capacitor  $C_{CS}$  should be positioned as close as possible to pins 3 and 4 and tracked directly to the pins. Series resistor  $R_{CS2}$  should also be located close to pin 3 to minimize noise pick-up.  $R_{CS2}$  value should not exceed 20 k $\Omega$ , because a larger value could be detected as a possible open circuit on the CS pin during the start-up pin-fault checks. The R-C filter time constant should not be excessive (timing between 100 ns and 200 ns is typical). Otherwise the filter reduces the measured peak current, and allows greater actual peak current to flow versus the modulator demand level. Such effects force the regulation loop to reduce the switching frequency to compensate, and at highest line, no load, this can lead to regulation difficulties if the control loop attempts to drop the frequency so far that it reaches the f<sub>MIN</sub> limit.

Figure 31. Peak Current Demand with Slope Compensating Downslope

### Feature Description (continued)

### 8.3.10 IPEAK Adjust vs. Line

The controller applies a line-dependent reduction in the peak-current demand to correct for the current overshoot due to the PWM and gate drive propagation delay, with the aim of delivering a constant peak current versus line at a given power level. This maintains approximately constant switching frequency versus line for a given power level (until the operation enters into CCM), improves regulation, reduces audio noise, and allows lower standby power at high line. If not corrected, the current overshoot could become significant at high line, where the inductor current di/dt is higher. This overshoot would cause a pronounced increase in transferred power per switching cycle at high line, because power is proportional to  $I_{PK}^2$ . The effect of the delay on the peak-current overshoot is illustrated in Figure 32.

Figure 32. Peak-Current Demand Adjustment vs V<sub>BULK</sub> to Correct Prop Delay Overshoot

For different power stage designs, the combination of primary magnetizing inductance L<sub>PRI</sub>, current sense resistance R<sub>CS</sub> and external MOSFET gate turn-off delay t<sub>OFF(ext)</sub>, must be verified against Equation 17, to ensure that the internal peak-current compensation gain range is satisfied. The K<sub>LINE(adj)</sub> factor should be within the range indicated. If the external turn-off delay is too long, then the internal IPEAK adjustment factor is too low, and the adjustment at high line is not able to achieve the required level of over-shoot compensation. As noted previously, this could result in regulation difficulties at no-load, and may cause poor line and load regulation, or require an increase in output pre-load power.

$$K_{LINE(adj)} = \left(\frac{R_{CS}}{L_{PRI}} \times \left(t_{PROP(gate)} + t_{OFF(ext)}\right)\right) > 120 \,\mu \text{ and} < 350 \mu$$

where

where t<sub>PROP(gate)</sub> is the internal controller gate-drive turn-off propagation delay, given in Table 6.

(17)

35

#### **Feature Description (continued)**

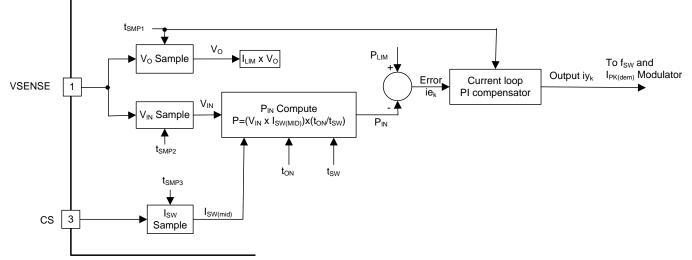

#### 8.3.11 Primary-Side Constant-Current Limit (CC Mode)

In addition to the peak-current mode PWM function, the device also uses sensed current at the CS pin to estimate the secondary-side load current. The device samples the CS pin voltage and measures it in the middle of the on-time, which is effectively the average switch current during the on time,  $I_{SW(avg_on)}$ . This measurement scheme is the case during both DCM and CCM operational modes. The average switch current during the on time is scaled by the PWM duty cycle to give the  $I_{IN(avg)}$  of the power stage. The power stage input power,  $P_{IN}$ , can then be estimated as the product of ( $V_{IN} \times I_{IN(avg)}$ ). The CC mode operation regulates  $P_{IN}$  to track ( $I_{OUT(lim)} \times V_{OUT}$ ), if  $P_{IN}$  increases to reach  $P_{IN(lim)}$ , thereby achieving a regulated constant current as shown in Equation 18.

$$P_{IN} = V_{IN} \times I_{IN(avg)} = \frac{V_{OUT} \times I_{OUT(lim)}}{\eta} = P_{IN(lim)}$$

$$I_{IN} = \frac{V_{IN} \times I_{IN(avg)} \times \eta}{\eta} - \frac{P_{IN(lim)} \times \eta}{\eta} = I$$

(18)

$$V_{\rm OUT} = \frac{1}{V_{\rm OUT}} = \frac{1}{V_{\rm OUT}} = 1_{\rm OUT(lim)}$$

(19)

Figure 33. Digital Current Control Loop Simplified Block Diagram

# Feature Description (continued)

Assuming that the power stage efficiency does not change significantly with operating point, by regulating the input power in inverse proportion to output voltage, this regulates output current. This achieves a *brick-wall* CC characteristic, where the output current is regulated as the input voltage changes and as the output voltage rolls off, regardless of power stage operating mode (CCM or DCM). The CC mode protection eliminates the characteristic load current *tail-out* that is typically seen with peak-current mode control as output voltage collapses and operation goes deeper into CCM mode.

## NOTE

As the output voltage decreases in CC mode, the VDD level also decreases. If the overload is severe, the drop in output voltage causes VDD to drop below the  $V_{DD(stop)}$  UV level. This drop causes a shutdown for  $t_{RESET(long)}$ , as given in Table 6, followed by a restart attempt.

The constant-current mode output current limit level  $(I_{OUT(lim)})$  is a function of both the R<sub>CS1</sub> resistor and the transformer turns ratio. The device uses an internal reference and gain for the CC loop, K<sub>CC1</sub> and K<sub>CC2</sub>, that set the CC I<sub>OUT(lim)</sub> point as a function of the chosen turns ratio, output voltage and current sense resistance as shown in Equation 20.

$$I_{OUT(lim)} = \frac{1}{R_{CS1}} \times \frac{N_P}{N_S} \times \frac{K_{CC1}}{K_{CC2} + V_{OUT} \times \frac{N_P}{N_S}}$$

(20)

37

For the UCC28631, UCC28632 and the UCC28633 devices, the  $I_{OUT(lim)}$  can be adjusted to be a percentage of the maximum value calculated by equation Equation 20. see CC-Mode  $I_{OUT(lim)}$  Adjustment for more details.

# Feature Description (continued)

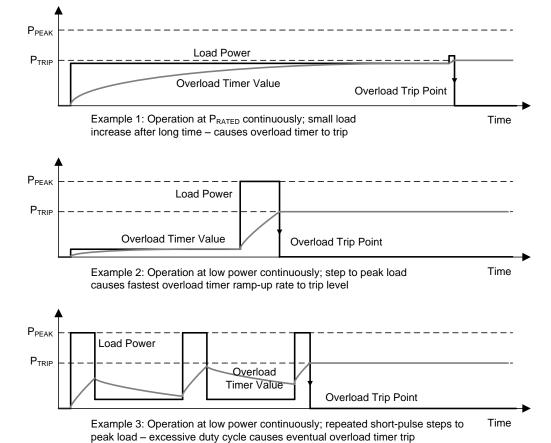

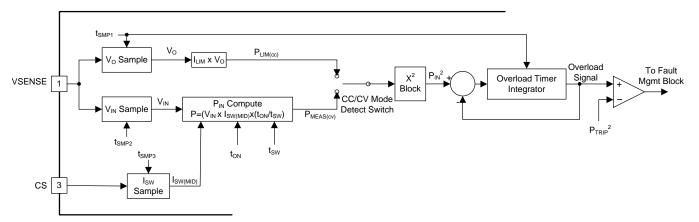

# 8.3.12 Primary-Side Overload Timer (UCC28630 only)

The internal overload timer in the UCC28630 uses the same output load current measurement that is used by the CC loop. This measurement tracks the power stage thermal stress, and protects the power stage against output overload. If the output is overloaded for too long such that the power stage would be over-stressed, then the PWM shuts down, and enters low-power mode for a time period of  $t_{RESET(long)}$ ; thereafter the device discharges VDD to the  $V_{DD(reset)}$  level and initiates a hiccup mode restart.

The overload timer operates by taking an estimate of output current, squaring it (assuming the power stage losses are dominated by resistive  $I^2$  losses) to produce (K x  $I^2_{OUT}$ ), where K is a scaling gain factor. The overload timer is constantly running at every load level, and accumulates at a rate dependent on the difference between (K x  $I^2_{OUT}$ ) and the previous level of the timer. If (K x  $I^2_{OUT}$ ) is greater than the previous timer level, the timer level continues to increase; if (K x  $I^2_{OUT}$ ) is less than the previous timer level, then the timer level decreases. At any steady load, the overload timer level eventually settles at a level proportional to  $I^2_{OUT}$ . Because the overload timer level adjusts at a rate dependent on the difference between (K x $I^2_{OUT}$ ) and the previous level, the timer initially reacts faster to larger differences, but over time settles exponentially at a level proportional to (K x  $I^2_{OUT}$ ).