*TMS470MF0660x Microcontroller* **Silicon Revision B**

# **Silicon Errata**

Literature Number: SPNZ179A November 2010–Revised November 2015

## **Contents**

| 1 | Introdu | ction                                          | 4  |

|---|---------|------------------------------------------------|----|

|   | 1.1     | Device Nomenclature                            | 4  |

|   | 1.2     | Revision Identification                        | 5  |

| 2 | Known   | Design Exceptions to Functional Specifications | 6  |

| 3 | Revisio | n History                                      | 79 |

| www | .ti. | .com |

|-----|------|------|

|     |      |      |

## List of Figures

| 1 | Example, Device Revision Code for TMS470MF0660x (PZ Package) | 5 |

|---|--------------------------------------------------------------|---|

|   | List of Tables                                               |   |

| 1 | TMS470ME0660x Device Revision Codes                          | 5 |

| - |                                                                      |    |

|---|----------------------------------------------------------------------|----|

| 2 | Advisory List                                                        | 6  |

| 3 | Revision History from Initial Errata Document Revision to Revision A | 79 |

## TMS470MF0660x Microcontroller Silicon Revision B

## 1 Introduction

This document describes the known exceptions to the functional specifications for the TMS470MF0660x devices. For more detailed information on this device, see the device-specific data sheet:

• TMS470MF0660x 16/32-BIT RISC Flash Microcontroller data manual (Literature Number SPNS157)

### 1.1 Device Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all devices. Each commercial family member has one of three prefixes: TMX, TMP, or TMS (e.g., TMS470MF0660xPZ). These prefixes represent evolutionary stages of product development from engineering prototypes (TMX) through fully qualified production devices/tools (TMS).

Device development evolutionary flow:

- **TMX** Experimental device that is not necessarily representative of the final device's electrical specifications.

- **TMP** Final silicon die that conforms to the device's electrical specifications but has not completed quality and reliability verification.

- **TMS** Fully-qualified production device.

TMX and TMP devices are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

TMS devices have been characterized fully, and the quality and reliability of the device have been demonstrated fully. TI's standard warranty applies.

Predictions show that prototype devices (TMX or TMP) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

TI device nomenclature also includes a suffix with the device family name. This suffix indicates the package type (for example, PZ), the temperature range (for example, "Blank" is the commercial temperature range), and the device speed range in megahertz.

## 1.2 Revision Identification

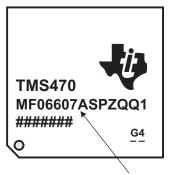

Figure 1 provides an example(s) of the TMS570LS series device markings. The device revision can be determined by the symbols marked on the top of the package.

**Device Revision Code**

### Figure 1. Example, Device Revision Code for TMS470MF0660x (PZ Package)

Silicon revision is identified by a device revision code. The code is of the format TMS470MF06607x, where "x" denotes the silicon revision. If x is "B" in the device part number, it represents silicon version B. Table 1 lists the information associated with each silicon revision.

| DEVICE PART NUMBER<br>DEVICE REVISION CODE | SILICON REVISION | PART NUMBERS/COMMENTS                                                           |

|--------------------------------------------|------------------|---------------------------------------------------------------------------------|

| TMX470MF0660x                              | Initial          | This silicon revision is available as TMX <i>only.</i><br><b>TMX</b> 470MF0660x |

| TMS470MF0660xA                             | A                | This silicon revision is available as TMX <i>only.</i><br><b>TMX</b> 470MF0660x |

| TMS470MF0660xB                             | В                | This silicon revision is available as TMS TMS470MF0660x                         |

#### Table 1. TMS470MF0660x Device Revision Codes

## 2 Known Design Exceptions to Functional Specifications Table 2. Advisory List

#### Title

Page

|                                                                                                                | ugo |

|----------------------------------------------------------------------------------------------------------------|-----|

| CORTEX-M3#18 — Async Not Generated If No Trace In Previous Session                                             | . 8 |

| CORTEX-M3#19 — Trigger Packets Sometimes Not Inserted In Trace Stream                                          | . 9 |

| CORTEX-M3#20 — BKPT In Debug Monitor Mode Can Cause DFSR Mismatch                                              | 10  |

| CORTEX-M3#21 — Core May Freeze For SLEEPONEXIT Single Instruction ISR                                          | 11  |

| CORTEX-M3#22 — Unaligned MPU Fault During A Write Causes Wrong Data Written To Successful First Access         |     |

| CORTEX-M3#23 — Unaligned MPU Fault During A Write Causes Wrong Data To Be Written                              | 13  |

| CORTEX-M3#24 — Cortex-M3 Fetches Instructions Using Incorrect Privilege On Exception Return                    | 14  |

| CORTEX-M3#25 — DWT CPI Counter Increments During Sleep                                                         | 15  |

| CORTEX-M3#26 — Cortex-M3 TPIU Clock Domain Crossing                                                            | 16  |

| CORTEX-M3#27 — Internal write buffer Active While In Sleep Mode                                                | 17  |

| CORTEX-M3#30 — SWJ-DP Internal Reset Synchronizer                                                              | 18  |

| <b>CORTEX-M3#31</b> — LDRD With Base In List May Result In Incorrect Base Register When Interrupted Or Faulted | 19  |

| CORTEX-M3#32 — Cortex-M3 Reserved Interface Allowing An External Interrupt Controller Connection               | 20  |

| CORTEX-M3#34 — ETM Traces BKPT As An Executed Instruction                                                      | 21  |

| CORTEX-M3#35 — HPROT And MEMATTR Incorrect On Some Unaligned Transactions                                      | 22  |

| CORTEX-M3#36 — Incorrect Core Feature Identification Registers                                                 | 23  |

| CORTEX-M3#37 — Bit-Band Access Could Read Or Write Wrong Bit In BE8                                            | 24  |

| CORTEX-M3#39 — TBH Will Never Cause An Alignment Fault                                                         | 25  |

| CSHTM#10 — TraceOff Packet Duplicated At End Of Trace Session                                                  | 26  |

| CSHTM#11 — ASYNC Packet Generation Suppressed By HREADY Highs                                                  | 27  |

| CTAP#21 — CTAP TMS_PSEL Not Getting Reset Values Asynchronously                                                | 28  |

| DCAN#18 — Write To A Mailbox Address Beyond Implemented Number Corrupts Implemented Mailbox                    | 29  |

| DCAN#21 — In Interrupt Multiplexer Registers, Bit To Message Objects Mapping Is Left Rotated By 1              | 30  |

| DCAN#22 — Incorrect Payload Stored In Mailbox                                                                  | 31  |

| DCAN#23 — WRITE Accesses From IFx Registers To Message RAM Lost                                                | 32  |

| ESRAMW#22 — DERR Address Register Cleared While Being Read                                                     | 34  |

| ESRAMW#32 — AHB Transaction Initiated During Auto Initialization Mode Fails                                    | 35  |

| FWM#87 — IFLUSH Mode Hangs Or Returns Incorrect Data                                                           | 36  |

| FWM#90 — New Algorithm Required To Meet Flash Bank's Read Margin Test Requirements                             | 37  |

| FWM#115 — Flash Clock Is One Cycle Late                                                                        | 38  |

| FWM#123 — Bad Data Read At End Of FSM Operation                                                                | 39  |

| FWM#135 — Reads To ECC Space Fail                                                                              | 40  |

| FWM#138 — Data Read Corrupted                                                                                  | 41  |

| FWM#141 — Single Bit Error Address Register Updated With Incorrect Address                                     | 42  |

| FWM#142 — Uncorrectable Error Address Register Updated With Incorrect Address                                  | 43  |

| FWM#143 — FWM Issuing Spurious Single Bit Error Interrupt (CE_INT)                                             | 44  |

| FWM#144 — Wrong Read Data Given To FWM                                                                         | 45  |

| FWM#145 — Single Bit Or Double Bit Error Not Generated                                                         | 46  |

| FWM#148 — When Iflush Enabled Error Count Increments Incorrectly                                               |     |

| FWM#149 — No Magnitude Comparator For FCOR_ERR_CNT Register                                                    | 48  |

| FWM#151 — Clearing An Error Status Bit Blocks New Errors                                                       | 49  |

| HET#19 — Incorrect Software Interrupt Generated                                                                | 50  |

|                                                                                                                |     |

## Table 2. Advisory List (continued)

| HET#20 — Captured Period/Pulse Count Is Wrong                                                            | 51        |

|----------------------------------------------------------------------------------------------------------|-----------|

| LIN#46 — Super-Fractional Divider Table Mismatch For Synch Field And ID Field Transmission (Master Mode) | 52        |

| LIN#48 — Header Not Received By Slave                                                                    | 53        |

| LIN#49 — First Byte Of Data Is Corrupted                                                                 | 54        |

| LIN#50 — Timeout Flag Not Set                                                                            | 55        |

| LIN#51 — Slave Not Transmitting Response                                                                 | 56        |

| LIN#57 — LIN Rejects Data                                                                                | 57        |

| LIN#58 — Incomplete Synch Field Reception Results In Loss Of Next Header                                 | 58        |

| LIN#59 —LIN transmission Impacted                                                                        | 59        |

| LIN#60 — Start Bit Transmitted Within One VCLK During Extended Frame Transmission In Single Buffer Mode  | 60        |

| LIN#61 — TOA3WUP Flagged When New Header Is Received During Waitstate                                    | 61        |

| LIN#62 — FE During Checksum Byte Restarts Reception                                                      | 62        |

| LIN#63 —LIN Timeout Counters Need To Stop Incrementing During Power Down Mode                            | 63        |

| LIN#65 — NRE/Timeout Not Flagged                                                                         | 64        |

| MIBSPI#109 — BITERR Limitation                                                                           | 65        |

| MIBSPI#110 — Multibuffer Slave In 3 Pin Mode Transmits Data Incorrectly                                  | 66        |

| MIBSPI#111 — Data Length Error Is Generated Repeatedly In Slave Mode                                     | 67        |

| MIBSPI#118 — TXPIN_P Register Has No Reset In MIBSPI                                                     | 68        |

| PCR#9 —Wakeup Interrupt Generated Twice                                                                  | <b>69</b> |

| SSW#17 — FBSLIP And/Or RFSLIP Inadvertently Set On Power Up                                              | 70        |

| SYS#103 — SYS_Nrst Requires Extra VCLK Cycles To Guarantee Complete Device Reset                         | 71        |

| TPIU#6 — CSTPIU Unable To Disable Pattern Generator If Trace Data Is Output Immediately On Stopping      | 72        |

| TPIU#7 — Unsynchronized Clock Domain Crossing In CSTPIU                                                  | 73        |

| TMS470Mx#6 — HET Data-In Register Shows Value Of TDI & TDO Pins                                          | 74        |

| TMS470Mx#8 — GIO Slew Rate Select Register Inaccessible For Read Or Write                                | 75        |

| TMS470Mx#10 — Receive Buffers In Peripherals Will Receive The Data Even When INENA Disabled              | 76        |

| TMS470Mx#11 — Die-ID Not Read Properly After Power-On Reset                                              | 77        |

| TMS470Mx#12 — No Abort Generated When Accessing Illegal Location                                         | 78        |

|                                                                                                          |           |

| CORTEX-M3#18         | Async Not Generated If No Trace In Previous Session                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision(s) Affected | Revision B and earlier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Details              | The ETM is required to generate an alignment synchronisation packet as the first packet<br>every time the programming bit is cleared, in order to allow the tools to synchronize with<br>the protocol stream. If no trace is generated in a session, the A-sync packet will be<br>correctly generated as the progbit is cleared, but if the progbit is then set and cleared<br>again, second and subsequent A-sync packets are not generated. No other aspects of<br>the trace generation are affected by this, and once any other trace packet is generated<br>the A-sync logic will be correctly reset.                                                                                                                               |  |

|                      | Conditions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                      | This erratum only occurs when the following sequence of events occurs:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                      | <ul><li>The ETM is programmed and enabled.</li><li>No instructions are traced.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                      | <ul> <li>The ETM programming bit is cleared<br/>The absence of any traced instructions can be due either to the Trace Enable<br/>conditions not being satisfied, or the core not executing any instructions</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                      | Implications: This erratum only affects the trace stream which is generated by the ETM. There is no impact on the normal processing operation of the core. The conditions which cause this erratum are expected to occur whilst debug is being performed. The A-sync packet may be missing at the start of a trace session. All trace packets which are generated will still be correct, and there is no corruption of the trace stream. If the A-sync from a previous session was captured, it can be used for synchronisation. Tools will typically fail to capture the trace relating to any bytes of trace before the next periodic A-sync packet is seen. For short trace sessions, it is possible to lose the whole trace session |  |

| Workaround(s)        | Users may attempt to work around this erratum by forcing the generation of trace packets as part of an initialization sequence. This is only possible if the core is not in debug state, and so may not be applicable in all cases. With this ETM it is also possible to deduce that the first byte of trace captured after the progbit is cleared will be the start of a packet, provided that the formatter in the TPIU is enabled.                                                                                                                                                                                                                                                                                                   |  |

| www.ti.com           | Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CORTEX-M3#19         | Trigger Packets Sometimes Not Inserted In Trace Stream                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Revision(s) Affected | Revision B and earlier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Details              | It is possible to configure a trigger event for the ETM which is used to assist with trace capture and the subsequent analysis of trace by the user. The trigger condition is indicated by a pulse on the ETMTRIGOUT signal, and is also inserted in the trace stream using a special packet. If a trigger condition occurs when there is no data in the ETM's FIFO and there are no instructions yet to be traced, the ETMTRIGOUT signal is pulsed correctly, but the trigger packet is not inserted in the trace stream.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                      | Conditions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                      | The ETM is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                      | The trace FIFO is empty.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                      | <ul> <li>There are no instructions already executed but not yet entered in the trace FIFO.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                      | Implications: This erratum only affects the trace stream which is generated by the ETM. There is no impact on the normal processing operation of the core. This erratum only affects the inclusion of the trigger packet in the trace stream. It does not affect the visibility of the trigger condition through the ETM's programmers model (bit 2 of the ETM Status Register, register 4). It does not affect the indication of the trigger condition to the trace capture device, and a formatter trigger packet will be inserted if enabled. The erratum does not occur if a trigger is generated using DWT to detect an instruction address if Trace Enable is high. When this erratum occurs, the user will not be able to determine the location in the executed instruction sequence at which the trigger condition occurred. Due to the conditions which are required for this erratum to occur, it is more likely that the erratum occurs when an external input is being used to generate the trigger condition. |

| Workaround(s)        | If using the CoreSight formatter protocol, e.g. TPIU/ETB with trigger embedded, then the position of the embedded trigger can be used, however the location of the embedded trigger is approximate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## CORTEX-M3#20 BKPT In Debug Monitor Mode Can Cause DFSR Mismatch

Revision(s) Affected Revision B and earlier

Details

A BKPT may be executed in debug monitor mode which will cause the debug monitor handler to be run but the Debug Fault Status Register (DFSR) at address 0xE000ED30 will not have bit 1 set to indicate the cause was a BKPT instruction. This will only occur if an interrupt other than the Debug Monitor is already being processed just before the BKPT is executed.

Conditions:

- C\_DEBUGEN (bit 0) in the Debug Halting Control and Status Register at address 0xE000EDF0 is 0.

- MON\_EN (bit 16) in the Debug Exception and Monitor Control Register at address 0xE000EDFC is 1.

- An enabled interrupt occurs two cycles before the BKPT is executed that causes a preemption.

Implications: The Debug Monitor handler may be entered without the DFSR revealing the cause of the handler being entered.

## **Workaround(s)** If the DFSR does not have any bits set when the debug monitor has been entered then the cause must be due to this corner case and that it was the result of a BKPT.

| CORTEX-M3#21         | Core May Freeze For SLEEPONEXIT Single Instruction ISR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Revision(s) Affected | Revision B and earlier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Details              | The SLEEPONEXIT functionality causes the core to enter the sleep mode when the exit from the sole active interrupt occurs. This means that there are no more interrupts active and the exit would have caused a return to the thread. It is possible for the core to become frozen if the SLEEPONEXIT functionality is used and the interrupt service routine (ISR) concerned only contains a single instruction. This freezing may occur if only one interrupt is active and it is pre-empted by an interrupt whose handler only contains the single instruction. This instruction must be a legal ISR exit instruction that takes one cycle to execute (either a BX or a BLX). In this case the unstacking would occur after the single instruction had been executed as normal to return to the now only active interrupt handler. However, once it has returned no more instructions will be processed and the core will be frozen. Any new preempting interrupt will unfreeze the processor. |  |  |

|                      | Conditions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                      | <ul> <li>SLEEPONEXIT (bit 1) in the System Control Register at address 0xE000ED10 is set.</li> <li>An interrupt occurs that causes a preemption of the current ISR which is the only interrupt that is currently active.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                      | • The interrupt service routine that is entered consists of only one instruction (either BX or BLX) which causes a legal exit from that ISR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                      | Implications: The core may freeze and stop processing instructions when it returns to the only currently active ISR. Note that a new interrupt that causes a preemption would cause the core to become unfrozen and behave correctly again.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Workaround(s)        | If the SLEEPONEXIT functionality is required then do not allow an ISR to contain only one instruction. If an empty ISR is used then insert a NOP before the exit instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

## CORTEX-M3#22 Unaligned MPU Fault During A Write Causes Wrong Data Written To Successful First Access

Revision(s) Affected Revision B and earlier

Details

When an unaligned store is executed by Cortex-M3 the transaction is split up into either two or three aligned transactions forming constituent parts of the larger transaction. The MPU will check that these transactions are permitted and will block them if necessary. If an unaligned transaction occurs where it overlaps two MPU regions then each region relating to the part of the transaction that hits that region will be checked. If an unaligned store occurs that crosses an MPU region boundary and has an MPU permission fault for the second region check but not for the first region then it is possible for the second component's data to be written for the first successful transaction in place of the first transaction's data. This can occur for writes to either the D-Code or system bus but will only occur if one or more wait-states are applied for the first component of the store.

Conditions:

- The full MPU is present and enabled with at least one region programmed and enabled.

- An unaligned store is executed by the processor. The store can be to either the D-Code or the System bus.

- The store crosses an MPU region boundary.

- The first region lookup passes, the second region lookup fails. 5. One or more wait states are applied via HREADYS or HREADYD.

Implications:

The wrong data will be stored to a permitted address. However, a MemManage fault will occur immediately pointing to the instruction that caused the fault. This may lead to the instruction being re-executed and the store occurring successfully if it is for non-device memory. This would mean that the previously stored data would be overwritten and the wrong value would never be seen. This may not be true for a shared memory system.

## **Workaround(s)** A workaround is only required if the MPU is present and enabled. Do one of the following:

- Do not allow accesses to span more than one region

- Do not allow unaligned accesses at all

- Program the MPU correctly if applicable

Secondary workaround:

M3 can be configured to generate a usage fault upon ANY unaligned access by enabling UNALIGN\_TRP bit in the M3 Configuration Control Register. If the user does not intend to ever do an unaligned write, then this would be the preferred workaround, as it would prevent incorrect data from being written.

| CORTEX-M3#23         | Unaligned MPU Fault During A Write Causes Wrong Data To Be Written                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Revision(s) Affected | Revision B and earlier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Details              | When an unaligned store is executed by Cortex-M3 the transaction is split up into either<br>two or three aligned transactions forming constituent parts of the larger transaction. The<br>MPU will check that these transactions are permitted and will block them if necessary. If<br>an unaligned transaction occurs where it overlaps two MPU regions then each region<br>relating to the part of the transaction that hits that region will be checked. If an unaligned<br>store occurs that crosses an MPU region boundary and has an MPU permission fault for<br>the second region check but not for the first region then it is possible for the second<br>component's data to be written for the first successful transaction in place of the first<br>transaction's data. This can occur for writes to either the D-Code or system bus but will<br>only occur if one or more wait-states are applied for the first component of the store. |  |  |

|                      | Conditions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                      | <ul> <li>The full MPU is present and enabled with at least one region programmed and<br/>enabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                      | <ul> <li>An unaligned store is executed by the processor. The store can be to either the D-<br/>Code or the System bus.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                      | The store crosses an MPU region boundary.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                      | <ul> <li>The first region lookup passes, the second region lookup fails.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                      | <ul> <li>One or more wait states are applied via HREADYS or HREADYD.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                      | Implications: The wrong data will be stored to a permitted address. However, a MemManage fault will occur immediately pointing to the instruction that caused the fault. This may lead to the instruction being re-executed and the store occurring successfully if it is for non-device memory. This would mean that the previously stored data would be overwritten and the wrong value would never be seen. This may not be true for a shared memory system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Workaround(s)        | A workaround is only required if the MPU is present and enabled. Do one of the following:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                      | <ul> <li>Do not allow accesses to span more than one region.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                      | Do not allow unaligned accesses at all.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                      | Program the MPU correctly if applicable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                      | Additional Workaround: M3 can be configured to generate a usage fault upon ANY unaligned access by enabling UNALIGN_TRP bit in the M3Configuration Control Register. If the user does not intend to ever do an unaligned write, then this would be the preferred workaround, as it would prevent incorrect data from being written.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| CORTEX-M3#24         | Cortex-M3 Fetches Instructions Using Incorrect Privilege On Exception Return                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected | Revision B and earlier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Details              | While unstacking registers on return from an exception to a User-privilege thread,<br>Cortex-M3 attempts to simultaneously prefetch the thread's instruction stream. Before<br>the register unstacking is complete, up to the first three memory transactions used to<br>perform instruction prefetching may be erroneously marked as Privileged. This may allow<br>between three and six instructions from a Privileged-access-only region to be executed<br>by a User-privilege thread. Once fetched, the instructions are executed with User-<br>privilege. Instruction fetches performed after register unstacking has completed will be<br>performed with User-privilege. Both the register unstacking, and any data transactions<br>generated by executing the erroneously executed instructions will be performed and<br>correctly marked as User-privilege.        |

|                      | Conditions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                      | Exception return is executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                      | The exception return is to user code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                      | Implications: User-privileged code may contrive a situation in order to allow execution of up to three words worth of instructions intended to be accessible to Privileged-only execution; however, execution of said instructions will always be performed with User-privilege, thus there are no additional capabilities provided to User-privilege through this erratum. There exists a theoretical possibility that User-privilege code could use this erratum to allow limited extraction of code and or data from Privileged-access only memory. Note that read sensitive Privileged-access only peripherals should always be placed in an XN region either via the default memory map, or via the optional memory-protection-unit. Alternatively such peripherals should ignore transactions with HPROT[0] indicating that the transaction is an instruction fetch. |

| Workaround(s)        | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CORTEX-M3#25         | DWT CPI Counter Increments During Sleep                                                                                                                                                                                                                                                                                                                                               |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected | Revision B and earlier                                                                                                                                                                                                                                                                                                                                                                |

| Details              | The DWT contains a number of counters for the profiling of applications. The CPI counter is used to indicate the total number of clock cycles beyond the first cycle of each instruction. The counter is specified to not increment whilst the core is sleeping but for previous revisions it does increment. This results in sleep cycles being counted as program execution cycles. |

|                      | <ul><li>Conditions:</li><li>The CPI counter in the DWT is enabled.</li><li>Core sleeps during profiling.</li></ul>                                                                                                                                                                                                                                                                    |

|                      | Implications: Profiling information could be calculated incorrectly if the following<br>calculation is used:<br>InstructionCount = CycleCount (CPIcount+LSUcount+INTcount+SLEEPcount) +<br>FOLDcount                                                                                                                                                                                  |

| Workaround(s)        | The number of sleep cycles given by SLEEPCNT can be subtracted from the CPI cycle count to obtain the correct CPI cycle information. Use the following equation:<br>InstructionCount = CycleCount (CPIcount+LSUcount+INTcount) + FOLDcount                                                                                                                                            |

| CORTEX-M3#26         | Cortex-M3 TPIU Clock Domain Crossing                                                                                                                                                                                                                                                                                                      |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected | Revision B and earlier                                                                                                                                                                                                                                                                                                                    |

| Details              | Combinatorial paths exist in control signals crossing the asynchronous clock boundary between FCLK and TRACECLKIN. Some of these signals control the reading and writing of data in the trace data FIFO on both sides of the FCLK and TRACECLKIN clock boundary and therefore could cause old data to be repeated or new data to be lost. |

|                      | Conditions:                                                                                                                                                                                                                                                                                                                               |

|                      | <ul> <li>FCLK/HCLK is asynchronous to TRACECLKIN</li> </ul>                                                                                                                                                                                                                                                                               |

|                      | Implications: When FCLK and TRACECLKIN are asynchronous and depending on the silicon implementation of the block, trace data might become corrupted.                                                                                                                                                                                      |

| Workaround(s)        | System implementers should make FCLK and TRACECLKIN operate synchronously. To avoid the possibility of corrupted trace data, the Trace Port must be fed with a clock synchronous to FCLK. Any crossing to an asynchronous TRACECLKIN domain should be done externally before the TPIU via a separate ATB asynchronous bridge.             |

| CORTEX-M3#27         | Internal write buffer Active While In Sleep Mode                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected | Revision B and earlier                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Details              | If a store immediate that is marked as not strongly ordered is used immediately before a WFE or WFI then the store may still be in progress when the core has asserted the SLEEPING signal. This will only occur if wait states are applied to the store operation. This will not cause a problem unless the location that the store was accessing was using a free-running clock whilst a clock-gating cell has been used to gate FCLK to form HCLK. |

|                      | Conditions:                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                      | A store with immediate offset is executed.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                      | The store operation is allowed to be bufferable                                                                                                                                                                                                                                                                                                                                                                                                       |