## DM3730, DM3725 Digital Media Processors Silicon Revisions 1.2, 1.1, 1.0

# **Silicon Errata**

Literature Number: SPRZ319F August 2010–Revised April 2014

## Contents

| 1     | Introdu   | ction                                                          | 5  |

|-------|-----------|----------------------------------------------------------------|----|

|       | 1.1       | DM3730/25 Device and Development Support Tool Nomenclature     | 5  |

|       | 1.2       | Revision Identification                                        | 6  |

| 2     | All Erra  | ta Listed With Silicon Revision Numbers                        | 8  |

| 3     | All Erra  | ta Listed by Module                                            | 12 |

| 4     | Usage     | Notes and Known Design Exceptions to Functional Specifications | 17 |

|       | 4.1       | Usage Notes (Limitations)                                      | 17 |

|       | 4.2       | Known Design Exceptions to Functional Specifications (Bugs)    | 32 |

| Revis | sion Hist | ory 1                                                          | 12 |

2

### List of Figures

| 1  | Example, Device Revision Codes for DM3730/25 Digital Media Processor          | . 6              |

|----|-------------------------------------------------------------------------------|------------------|

| 2  | Synclost Interrupt                                                            | 24               |

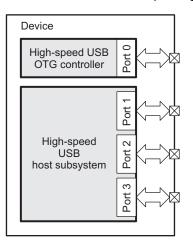

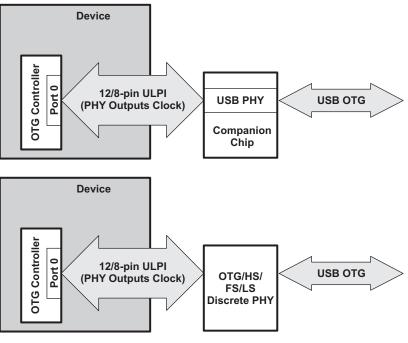

| 3  | DM37x USB Modules                                                             | 28               |

| 4  | Typical Uses for USB Port 0                                                   | 28               |

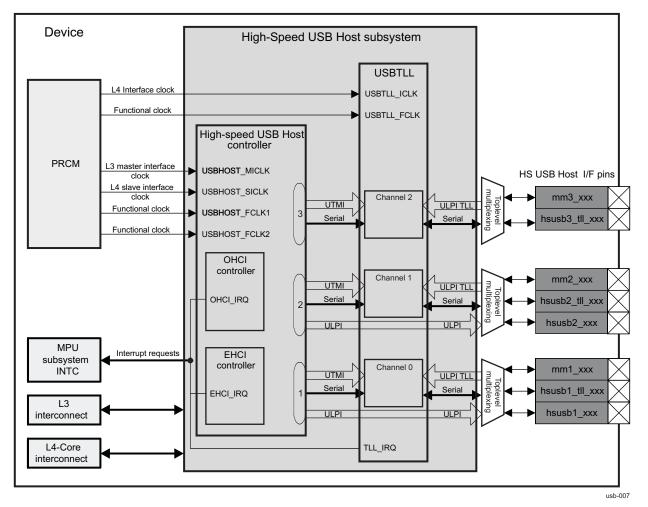

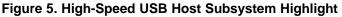

| 5  | High-Speed USB Host Subsystem Highlight                                       | 29               |

| 6  | Connecting to High-Speed PHYs Using USB Ports                                 | 30               |

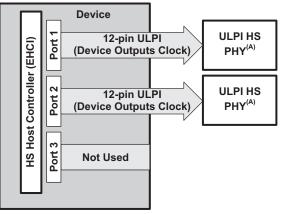

| 7  | Connecting to a High-Speed USB Hub                                            | 30               |

| 8  | I2C Flowchart                                                                 | 35               |

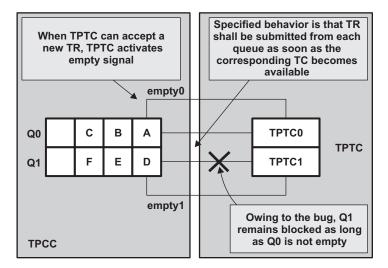

| 9  | TR Submission Scheme                                                          | 36               |

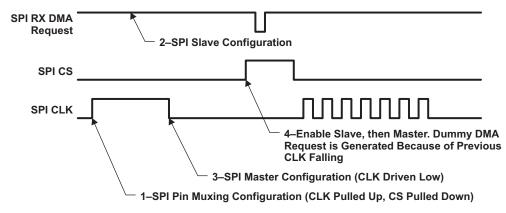

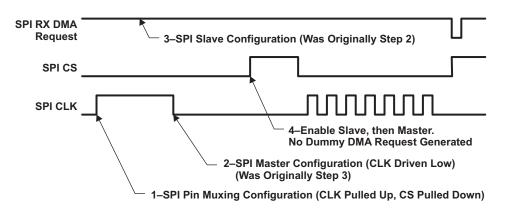

| 10 | SPI Dummy DMA RX Generation                                                   | 42               |

| 11 | Dummy DMA RX Generation (No Clock Edge)                                       | 42               |

| 12 | Dummy DMA RX Generation (Slave Mode After Clock Line Driven to Default Value) | 43               |

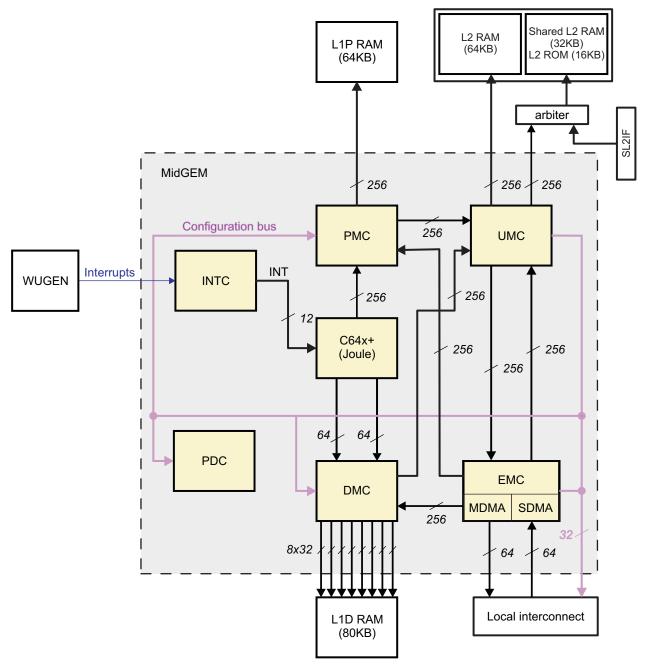

| 13 | C64x+ Megamodule Block Diagram                                                | 51               |

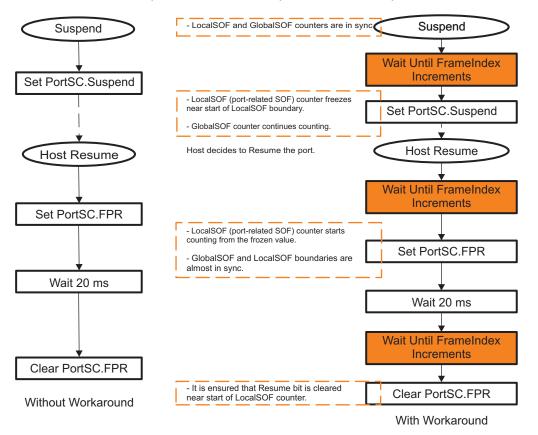

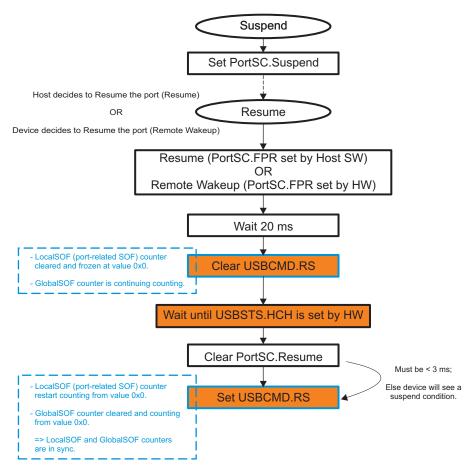

| 14 | Workaround 1 Implementation Diagram                                           | 60               |

| 15 | Workaround 2 Implementation Diagram                                           | <mark>6</mark> 1 |

### List of Tables

| 1  | DM37x Production Device Revision Codes                    | . 6 |

|----|-----------------------------------------------------------|-----|

| 2  | XDM37x Experimental Device Revision Codes                 | . 6 |

| 3  | Silicon Revision Variables                                | . 7 |

| 4  | All Usage Notes (Limitations)                             | . 8 |

| 5  | All Design Exceptions to Functional Specifications (Bugs) | . 9 |

| 6  | Errata List for the Control Module                        | 12  |

| 7  | Errata List for the Cortex-A8                             | 12  |

| 8  | Errata List for the Display Module                        | 12  |

| 9  | Errata List for the DMA4 Module                           | 12  |

| 10 | Errata List for the DPLL Module                           | 12  |

| 11 | Errata List for the GPMC Module                           | 12  |

| 12 | Errata List for the HDQ Module                            | 12  |

| 13 | Errata List for the HS USB Module                         | 13  |

| 14 | Errata List for the HS USB OTG Module                     | 13  |

| 15 | Errata List for the I2C Module                            | 13  |

| 16 | Errata List for the INTC Module                           | 14  |

| 17 | Errata List for the ISP Module                            |     |

| 18 | Errata List for the IVA2 Module                           | 14  |

| 19 | Errata List for the IVA2.2 Module                         | 14  |

| 20 | Errata List for the JTAG Module                           |     |

| 21 | Errata List for the McBSP Module                          |     |

| 22 | Errata List for the MMC Module                            |     |

| 23 | Errata List for the MPU                                   | 15  |

| 24 | Errata List for the PRCM Module                           |     |

| 25 | Errata List for the ROM Code Module                       |     |

| 26 | Errata List for the SDRC Module                           | 15  |

| 27 | Errata List for the SGX Module                            | 15  |

| 28 | Errata List for the SPI Module                            |     |

| 29 | Errata List for the SR Module                             |     |

| 30 | Errata List for the TDL Module                            | 16  |

3

| 31 | Errata List for the Timer Module                                                                        | 16  |

|----|---------------------------------------------------------------------------------------------------------|-----|

| 32 | Errata List for the UART Module                                                                         |     |

| 33 | Errata List for the VENC Module                                                                         | 16  |

| 34 | Errata List for Cautions                                                                                | 16  |

| 35 | DPLL5 Configurations for New Designs and Designs With 12 MHz, 19.2 MHz or 38.4 MHz Clock<br>Frequencies | 111 |

| 36 | DPLL5 Configurations With 13 MHz and 26 MHz Clock Frequencies                                           | 111 |

## DM3730, DM3725 Digital Media Processors (Silicon Revisions 1.2, 1.1, 1.0)

#### 1 Introduction

This document describes the known exceptions to the functional specifications for the DM3730/25 digital media processors. [See the DM3730/25 Digital Media Processor Data Manual (literature number SPRS685).]

For additional information, see the latest version of the *AM/DM37x Multimedia Device Technical Reference Manual* (literature number SPRUGN4).

The advisory numbers in the document are not sequential. Some advisory numbers are not applicable.

This document also contains "Usage Notes." Usage Notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data sheet), and the behaviors they describe will not be altered in future silicon revisions.

#### 1.1 DM3730/25 Device and Development Support Tool Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all microprocessors and support tools. Each commercial platform member has one of three prefixes: X, P, or null (no prefix). Texas Instruments recommends two of three possible prefix designators for its support tools: TMDX and TMDS. These prefixes represent evolutionary stages of product development from engineering prototypes (TMDX) through fully qualified production devices/tools (TMDS).

Device development evolutionary flow:

- **X** Experimental device that is not necessarily representative of the final device's electrical specifications

- **P** Final silicon die that conforms to the device's electrical specifications but has not completed quality and reliability verification

- NULL Fully-qualified production device

Support tool development evolutionary flow:

- **TMDX** Development-support product that has not yet completed Texas Instruments internal qualification testing

- TMDS

Fully-qualified development-support product

X and P devices and TMDX development-support tools are shipped against the following disclaimer: "Developmental product is intended for internal evaluation purposes."

Production devices and TMDS development-support tools have been characterized fully, and the quality and reliability of the device have been demonstrated fully. TI's standard warranty applies.

Sitara is a trademark of Texas Instruments. Cortex is a trademark of ARM Limited. ARM is a registered trademark of ARM Ltd. 1-Wire is a registered trademark of Maxim Integrated Products, Inc.. All other trademarks are the property of their respective owners.

Predictions show that prototype devices (X or P) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

#### 1.2 Revision Identification

The device revision can be determined by the symbols marked on the top of the package. Figure 1 provides an example of the DM3730/25 Digital Media Processor device markings.

**Device Revision Code**

#### Figure 1. Example, Device Revision Codes for DM3730/25 Digital Media Processor

#### NOTES:

- (A) Non-qualified devices are marked with the letters "X" or "P" at the beginning of the device name, while qualified devices have a "blank" at the beginning of the device name.

- (B) DM3730 is the device part number.

- (C) CBP is the package designator.

- (D) YM denotes year/month.

- (E) LLLL denotes Lot Trace Code.

- (F) S denotes Assembly Site Code.

- (G) On some "X" devices, the device speed may not be shown.

Silicon revision is identified by a code marked on the package. The code is of the format DM3730xCBP, where "x" denotes the silicon revision. Table 1 and Table 2 list the information associated with each silicon revision for each device type. For more details on device nomenclature, see the device-specific data manual.

#### Table 1. DM37x Production Device Revision Codes

| DEVICE REVISION CODE (x) | SILICON REVISION | COMMENTS                |

|--------------------------|------------------|-------------------------|

| (blank)                  | 1.2              | Silicon revision is new |

| DEVICE REVISION CODE (x) | SILICON REVISION | COMMENTS                                            |

|--------------------------|------------------|-----------------------------------------------------|

| В                        | 1.2              | Silicon revision is new (also referred to as ES1.2) |

| A                        | 1.1              | Silicon revision 1.1 (also referred to as ES1.1)    |

| (blank)                  | 1.0              | Silicon revision 1.0 (also referred to as ES1.0)    |

#### Table 2. XDM37x Experimental Device Revision Codes

7

Each silicon revision uses a specific revision of Sitara<sup>™</sup> ARM<sup>®</sup> Cortex<sup>™</sup>-A8 processor. The Sitara ARM Cortex-A8 processor variant and revision can be read from the Main ID Register. The ROM code revision can be read from base address 4001 BFFCh. The ROM code version consists of two decimal numbers: major and minor. The major number is always 18, minor number counts ROM code version. The ROM code version is coded as hexadecimal readable values, e.g. ROM version 18.07 will be coded as 0000 1807h. Table 3 shows the ROM code revision for each silicon revision of the device

#### **Table 3. Silicon Revision Variables**

| SILICON<br>REVISION | Sitara ARM CORTEX-A8<br>VARIANT/REVISION | ROM<br>REVISION |

|---------------------|------------------------------------------|-----------------|

| 1.2                 | r3p2                                     | 18.07           |

| 1.1                 | r3p2                                     | 18.07           |

| 1.0                 | r3p2                                     | 18.07           |

8

### 2 All Errata Listed With Silicon Revision Numbers

| Type/Number     | Title                                                                                                                    | 1.0 | 1.1 | 1.2 |

|-----------------|--------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|

| Usage Note 2.1  | Performance Limitation On LCD Read/Write Access Through<br>RFBI L4 Port                                                  | Х   | Х   | х   |

| Usage Note 2.2  | IVA2: Under Hardware Emulation, IDLE Instruction Must Be<br>Executed From L1P or L2 SRAM                                 | Х   | Х   | х   |

| Usage Note 2.3  | Domain Woken Up by Wake-Up Dependency Cannot Transition to Inactive State                                                | Х   | Х   | Х   |

| Usage Note 2.4  | VENC: Last Data Line Missing in PAL                                                                                      | Х   | Х   | Х   |

| Usage Note 2.5  | Observability Signals Not Functional in OFF Mode                                                                         | Х   | Х   | Х   |

| Usage Note 2.6  | Constraints on Module Clocks When Using DVFS                                                                             | Х   | Х   | Х   |

| Usage Note 2.7  | UART: Cannot Acknowledge Idle Requests in Smartidle Mode<br>When Configured for DMA Operations                           | Х   | Х   | х   |

| Usage Note 2.9  | GPIO is Driving Random Values When Device Returns From<br>OFF Mode                                                       | Х   | Х   | х   |

| Usage Note 2.10 | Maximum 12 Bits Output (1 bit sign + 11 bits of value) Is<br>Supported on CAVLD of iVLCD                                 | Х   | х   | х   |

| Usage Note 2.11 | Extra Power Consumed When Repeated Start Operation Mode<br>Is Enabled on I2C Interface Dedicated for Smart Reflex (I2C4) |     | х   | х   |

| Usage Note 2.12 | SGX 192 MHz Limitation With TVOUT @ 54 MHz                                                                               | Х   | Х   | Х   |

| Usage Note 2.13 | PWDNx Bit in CLock Manager Is Reseting the DPLL4 Mx<br>HSDIVIDER Coefficient Previously Programmed                       | Х   | х   | х   |

| Usage Note 2.15 | MMC IOs Reliability Issue                                                                                                | Х   | Х   |     |

| Usage Note 2.16 | Downscaling Limitations                                                                                                  | Х   | Х   | Х   |

| Usage Note 2.17 | TVOUT Line Shift Issue When Using DSI PLL for DISPC_FCLK                                                                 | Х   | Х   | Х   |

| Usage Note 2.18 | HDQ™/1-Wire® Communication Constraints                                                                                   | Х   | Х   | Х   |

| Usage Note 3.4  | Avoiding Voltage Drop When Booting at 1 GHz OPP With TPS65950A3                                                          | Х   | Х   | х   |

| Usage Note 3.5  | Undesired McBSP slave mode behavior during reset without CLKR/CLKX                                                       | Х   | Х   | х   |

| Usage Note 4.1  | HS USB Host Subsystem: Some Limitations Exist When<br>Connecting to External Devices                                     | Х   | Х   | х   |

| Usage Note 4.2  | "Speed Binned" Bit in Control Device Status Register Not<br>Programmed in Devices Built and Tested Prior to June 2011    | Х   | Х   | Х   |

#### Table 4. All Usage Notes (Limitations)

TEXAS INSTRUMENTS

www.ti.com

| Type/Number   | Title                                                                                                                         | 1.0 | 1.1 | 1.2 |

|---------------|-------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|

| Advisory 1.2  | I2C Module Does Not Allow 0-Byte Data Requests                                                                                | Х   | Х   | Х   |

| Advisory 1.3  | Delay Required to Read Some GP, WD, and Sync Timer<br>Registers After Wake-Up                                                 | Х   | х   | х   |

| Advisory 1.4  | IVA2: C64x+ L1D Cache May Lose Data or Hang DMA<br>Operations Under Certain Conditions                                        | Х   | х   | х   |

| Advisory 1.5  | MDR1 Access Can Freeze UART Module When in IrDa Mode                                                                          | Х   | Х   | Х   |

| Advisory 1.6  | IVA2: Block Cache Operations Word Count (*WC) Must be Less<br>Than or Equal to 0xFF80                                         | Х   | Х   | х   |

| Advisory 1.7  | I2C: RDR Flag May Be Incorrectly Set                                                                                          | Х   | Х   | Х   |

| Advisory 1.8  | IVA2: EDMA Channel Priority Is Not Correctly Enforced                                                                         | Х   | Х   | Х   |

| Advisory 1.9  | Inactive State Management: Impossible to Transition to OFF or RETENTION States                                                | Х   | х   | x   |

| Advisory 1.10 | Cortex-A8 Errata List                                                                                                         | Х   | Х   | Х   |

| Advisory 1.11 | Inappropriate Warm Reset Generation on Smart Reflex I2C<br>Error                                                              | Х   | Х   | х   |

| Advisory 1.12 | IVA2: Back-to-Back SPLOOPS With Interrupts Can Cause Incorrect Operation                                                      | Х   | Х   | х   |

| Advisory 1.13 | IVA2: DSP Generates False Internal Exception for Multiple<br>Writes                                                           | Х   | Х   | х   |

| Advisory 1.14 | GPMC May Stall After 256 Write Accesses in NAND_DATA, NAND_COMMAND, or NAND_ADDRESS Registers                                 | Х   | Х   | х   |

| Advisory 1.15 | SPI Dummy DMA RX Request Generation                                                                                           | Х   | Х   | Х   |

| Advisory 1.17 | IVA2: ISP/GFX Dependencies                                                                                                    | Х   | Х   | Х   |

| dvisory 1.20  | OCP Error Does Not Get Communicated to USBOTG                                                                                 | Х   | Х   | Х   |

| Advisory 1.21 | y 1.21 L3 Interconnect Clock Divisor Default Value Must be Modified<br>Before Configuration of SDRAM Controller               |     | х   | х   |

| Advisory 1.28 | DMA: Drain_IE Reset Value                                                                                                     | Х   | Х   | Х   |

| Advisory 1.29 | sDMA: Channel Is Not Disabled After a Transaction Error                                                                       | Х   | Х   | Х   |

| Advisory 1.30 | SGX Bugs Documented in Imagination Technologies™ Errata                                                                       | Х   | Х   | Х   |

| Advisory 1.31 | HS USB HOST Controller: Device Aborts the Remote Wake-Up<br>Sequence if AM3715/03 Wakes From OFF/RET to ON in USB<br>TLL Mode | Х   | х   | x   |

| Advisory 1.32 | Pending Interrupt to Video Sequencer Prevents IVA2 from Going<br>Into Idle Mode                                               | Х   | Х   | х   |

| Advisory 1.33 | McSPI Can Generate a Wrong Underflow Interrupt                                                                                | Х   | Х   | Х   |

| dvisory 1.34  | VENC: TV Detect AC Coupling Mode Not Supported                                                                                | Х   | Х   | Х   |

| Advisory 1.35 | Unexpected Stalling May Occur During SDMA/IDMA Accesses to DSP L2 Memory                                                      | Х   | Х   | х   |

| dvisory 1.38  | HS USB OTG Failing Access to Registers                                                                                        | Х   | Х   | Х   |

| dvisory 1.39  | HS USB OTG Software Reset Is Not Fully Functional                                                                             | Х   | Х   | Х   |

| Advisory 1.40 | ROM Code: CKE PAD Is Not Set When Initializing External RAM                                                                   | Х   | Х   | Х   |

| Advisory 1.41 | ROM Code: SDRC_POWER Register Is Initialized With<br>Hardcoded Value                                                          | Х   | Х   | х   |

| Advisory 1.42 | ROM Code: When sys-clock = 16.8MHz, Then Peripheral<br>Booting via UART3 Is Not Operational                                   | Х   | Х   | х   |

| Advisory 1.43 | I2C: I2C_STAT:XUDF Is Not Functional in Slave Transmitter<br>Mode                                                             | Х   | х   | х   |

| Advisory 1.44 | EHCI Controller: Issue in Suspend Resume Protocol                                                                             | Х   | Х   | Х   |

| Advisory 1.45 | GPIO Pad Spurious Transition (Glitch/Spike) During Wake Up<br>Entering or Exiting System OFF Mode                             | Х   | Х   | х   |

| Advisory 1.46 | Voltage Processor TRANXDONE Interrupt Occurs Too Early                                                                        | Х   | Х   | Х   |

| Advisory 1.47 | HS USB OTG: OTG_SYSCONFIG:AUTOIDLE Bit Is Not Reset<br>Correctly                                                              | Х   | Х   | х   |

#### Table 5. All Design Exceptions to Functional Specifications (Bugs)

| Type/Number   | Title                                                                                                                           | 1.0 | 1.1 | 1.2 |

|---------------|---------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|

| Advisory 1.48 | IVA2 Does Not Wake-Up After It Goes to IDLE While DMA<br>Request Is Still Asserted                                              | Х   | х   | х   |

| Advisory 1.49 | Software Reset Done While ISP Processing Is Ongoing Can<br>Cause OCP Protocol Violations                                        | Х   | Х   | х   |

| Advisory 1.51 | Accesses to DDR Stall in SDRC After a Warm-Reset                                                                                | Х   | Х   | Х   |

| Advisory 1.52 | Standard OTG Compliance Electrical Tests for HOST Mode Will Fail                                                                | Х   | Х   | х   |

| Advisory 1.54 | GPMC Has Incorrect ECC Computation for 4-Bit BCH Mode                                                                           | Х   |     |     |

| Advisory 1.56 | HS USB Host: ECHI and OHCI Controllers Cannot Work<br>Concurrently                                                              | х   |     |     |

| Advisory 1.57 | MMC OCP Clock Not Gated When Thermal Sensor Is Used                                                                             | Х   | Х   | Х   |

| Advisory 1.58 | Context Save Operation Randomly Failing for<br>CONTROL_PAD_CONF_ETK_D14                                                         | х   | Х   | х   |

| Advisory 1.59 | I2C4 Does Not Meet I2C Standard AC Timing in FS Mode                                                                            | Х   | Х   | Х   |

| Advisory 1.60 | I2C1 to 3 SCL Low Period Is Shorter in FS Mode                                                                                  | Х   | Х   | Х   |

| Advisory 1.61 | Missed Dependency With McBSP External Clock Prevents<br>Transition to OSWR                                                      | х   | Х   | х   |

| Advisory 1.62 | MPU Cannot Exit from Standby                                                                                                    | Х   | Х   | Х   |

| Advisory 1.63 | sDMA FIFO Draining Does Not Finish                                                                                              | Х   | Х   | Х   |

| Advisory 1.64 | HSUSB Interoperability Issue With SMSC USB3320 PHY                                                                              | Х   |     |     |

| Advisory 1.65 | IVA2 Does Not Wake-Up After It Goes to IDLE While an<br>Interrupt Line Is Not Cleared                                           | х   | х   | х   |

| Advisory 1.66 | IVA2 SEQ (ARM9) JTAG Failures With a Free Running Clock<br>Emulator                                                             | х   |     |     |

| Advisory 1.67 | Isolation Issue in OFF Mode Impacting the CORE Power<br>Domain                                                                  | х   |     |     |

| Advisory 1.68 | Safe Mode Does Not Work on GPMC_A11 Pad                                                                                         | Х   |     |     |

| Advisory 1.69 | GPMC_A11 Address Bit Does Not Behave as Expected (256MB NOR Flash Addressability)                                               | х   |     |     |

| Advisory 1.71 | DM37x Device May Wake Up From Low Power Modes if IO<br>Wake-Up and Pull Down Are Enabled                                        | Х   |     |     |

| Advisory 1.72 | Excessive Leakage on BRGC Memories in Cortex A8 When<br>Periphery Is Turned Off                                                 | Х   |     |     |

| Advisory 1.73 | JTAG Pins With bq18jtagfbpbnopm_ssbhv IO Have ESD (<br>Electro Static Discharge) Weakness in Input Buffer                       | Х   |     |     |

| Advisory 1.74 | Scan Shift Issues in GWG Memories                                                                                               | Х   |     |     |

| Advisory 1.75 | DMA4 Channel Fails to Continue With Descriptor Load When<br>Pause Bit Is Cleared Through Config Port Access While in<br>Standby | Х   | х   | x   |

| Advisory 1.76 | USB OTG DMA Status Register Read Return Zero                                                                                    | Х   | Х   | Х   |

| Advisory 1.77 | POWERVR SGX™: MMU Lockup on Multiple Page Miss                                                                                  | Х   |     |     |

| Advisory 1.78 | Device Cannot Reboot if Warm Reset Occurs During MPU DPLL<br>Lock Sequence                                                      | х   |     |     |

| Advisory 1.79 | USB Host EHCI May Stall When Exiting Smart-Standby Mode                                                                         | Х   | Х   |     |

| Advisory 1.80 | USB Host EHCI May Stall When Running High Peak-Bandwidth<br>Demanding Use Cases                                                 | х   | Х   |     |

| Advisory 1.81 | USB OTG DMA May Stall Under Specific Configuration                                                                              | Х   | Х   | Х   |

| Advisory 1.82 | USB OTG DMA May Stall When Entering Standby Mode                                                                                | Х   | Х   | Х   |

| Advisory 1.84 | DPLL3 in Manual Lock Mode Cannot Be Used When CORE<br>Goes to OSWR or OFF State                                                 | х   | Х   | х   |

| Advisory 1.85 | PRCM DPLL Control FSM Removes SDRC_IDLEREQ Before<br>DPLL3 Locks                                                                | Х   | Х   | х   |

| Advisory 1.86 | PER Domain Reset Issue After Domain-OFF/OSWR Wake-Up                                                                            | Х   | Х   |     |

| Table 5. All Design | Exceptions to | Functional Speci | fications (Bugs) | (continued) |

|---------------------|---------------|------------------|------------------|-------------|

|                     |               |                  |                  |             |

| Type/Number    | Title                                                                                                                                          | 1.0 | 1.1 | 1.2 |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|

| Advisory 1.87  | Self-Refresh Exit Issue After OFF Mode                                                                                                         | Х   | Х   |     |

| Advisory 1.88  | Programming of tCKE                                                                                                                            | Х   | Х   | Х   |

| Advisory 1.89  | McBSP Used in Slave Mode Can Create a Dead Lock Situation<br>When Doing Power Management                                                       | Х   | Х   | х   |

| Advisory 1.90  | DPLL3 Bypass Condition Does Not Consider State of SGX<br>FCLK                                                                                  | Х   | x   | Х   |

| Advisory 1.91  | Top Ball Compliancy With LPDDR JEDEC Standard                                                                                                  | Х   | Х   | Х   |

| Advisory 1.92  | I2C: In SCCB Mode, Under Specific Conditions, the Module<br>Might Hold the Bus by Keeping SCL Low                                              | Х   | x   | Х   |

| Advisory 1.93  | I2C: Wrong Behavior When Data With MSB 0 Is Put in the FIFO<br>Before a Transfer With SBLOCK Is Started                                        | Х   | x   | Х   |

| Advisory 1.94  | I2C: After an Arbitration is Lost the Module Incorrectly Starts the Next Transfer                                                              | Х   | x   | х   |

| Advisory 1.95  | One Timing Does Not Follow the JEDEC Standard                                                                                                  | Х   | Х   | Х   |

| Advisory 1.96  | 4-cycle Saturating .M Unit Instructions May Mask 2-cycle<br>Saturating .M Unit                                                                 | Х   | x   | Х   |

| Advisory 1.97  | SPLOOP CPU Cross-Path Stall                                                                                                                    | Х   | Х   | Х   |

| Advisory 1.98  | RTA Feature is Not Supported                                                                                                                   | Х   | Х   | Х   |

| Advisory 1.99  | HS USB OTG Spurious IRQ When Switching From DMA Mode 1<br>to DMA Mode 0 or to CPU Mode for Unloading the Last Short<br>Packet of a Transaction | х   | х   | х   |

| Advisory 1.100 | Write to OHCI Registers May Not Complete                                                                                                       | Х   | Х   | Х   |

| Advisory 1.101 | Violation of Vix Crossing Specification                                                                                                        | Х   | Х   |     |

| Advisory 1.102 | HS USB OTG Bus Reset                                                                                                                           | Х   | Х   | Х   |

| Advisory 1.104 | McBSP2 Data Corruption                                                                                                                         | Х   | Х   | Х   |

| Advisory 1.105 | DSI-PLL Power Command 0x3 Not Working                                                                                                          | Х   | Х   | Х   |

| Advisory 1.106 | MPU Leaves MSTANDBY State Before IDLEREQ of Interrupt<br>Controller is Released                                                                | Х   | x   | Х   |

| Advisory 1.107 | Some Power Domains Cannot Go To OFF Mode After Warm<br>Reset                                                                                   | Х   | x   | Х   |

| Advisory 1.108 | USBHOST Configured In Smart-Idle Can Lead To a Deadlock                                                                                        | Х   | Х   | Х   |

| Advisory 1.109 | USB OTG Software Initiated ULPI Accesses To PHY Registers Can Halt the Bus                                                                     | Х   | x   | х   |

| Advisory 1.110 | At Context Restore, a Certain PER DPLL Programming Can<br>Introduce Wake-up Latencies                                                          | Х   | х   | Х   |

| Advisory 1.111 | USB Peripheral Booting is Not Operational When an MMC<br>Booting has Been Attempted Before                                                     | х   | Х   | х   |

| Advisory 1.112 | DSS: Color Phase Rotation (CPR) Breaks 2 Pixel Wide Updates When in Stall Mode                                                                 | Х   | Х   | Х   |

| Advisory 1.113 | USB HOST: Impossible To Attach a FS Device To An EHCI Port<br>- Handoff To OHCI Is Not Functional                                              | Х   | Х   | Х   |

| Advisory 2.1   | USB Host Clock Drift Causes USB Spec Non-compliance in Certain Configurations                                                                  | Х   | x   | х   |

Table 5. All Design Exceptions to Functional Specifications (Bugs) (continued)

All Errata Listed by Module

Title

Title

#### 3 All Errata Listed by Module

#### Table 6. Errata List for the Control Module

### Advisory 1.71 — DM37x Device May Wake Up From Low Power Modes if IO Wake-Up and Pull Down Are Enabled ... 77

#### Table 7. Errata List for the Cortex-A8

###

#### Table 8. Errata List for the Display Module

| Fitle Pa                                                                                        |      |

|-------------------------------------------------------------------------------------------------|------|

| Usage Note 2.1 — Performance Limitation On LCD Read/Write Access Through RFBI L4 Port           | . 17 |

| Usage Note 2.12 — SGX 192 MHz Limitation With TVOUT @ 54 MHz                                    | . 22 |

| Usage Note 2.17 — TVOUT Line Shift Issue When Using DSI PLL for DISPC_FCLK                      | . 25 |

| Advisory 1.105 — DSI-PLL Power Command 0x3 Not Working                                          | 102  |

| Advisory 1.112 — DSS: Color Phase Rotation (CPR) Breaks 2 Pixel Wide Updates When in Stall Mode | 108  |

#### Table 9. Errata List for the DMA4 Module

| Title                                                                                                                                        |    |

|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| Advisory 1.28 — DMA: Drain_IE Reset Value                                                                                                    | 46 |

| Advisory 1.29 — sDMA: Channel Is Not Disabled After a Transaction Error                                                                      | 46 |

| Advisory 1.63 — sDMA FIFO Draining Does Not Finish                                                                                           | 73 |

| Advisory 1.75 — DMA4 Channel Fails to Continue With Descriptor Load When Pause Bit Is Cleared Through Config<br>Port Access While in Standby | 79 |

#### Table 10. Errata List for the DPLL Module

| Title                                                                                   | Page |

|-----------------------------------------------------------------------------------------|------|

| Advisory 1.78 — Device Cannot Reboot if Warm Reset Occurs During MPU DPLL Lock Sequence | 81   |

| Advisory 1.90 — DPLL3 Bypass Condition Does Not Consider State of SGX FCLK              | 92   |

#### Table 11. Errata List for the GPMC Module

| Title                                                                                                  | Page |

|--------------------------------------------------------------------------------------------------------|------|

| Advisory 1.14 — GPMC May Stall After 256 Write Accesses in NAND_DATA, NAND_COMMAND, or                 | 44   |

| NAND_ADDRESS Registers           Advisory 1.54 — GPMC Has Incorrect ECC Computation for 4-Bit BCH Mode |      |

| Advisory 1.68 — Safe Mode Does Not Work on GPMC_A11 Pad                                                |      |

| Advisory 1.69 — GPMC_A11 Address Bit Does Not Behave as Expected (256MB NOR Flash Addressability)      | 76   |

|                                                                                                        |      |

#### Table 12. Errata List for the HDQ Module

| • | Title                                                    | Page |

|---|----------------------------------------------------------|------|

| - | Usage Note 2.18 — HDQ™/1-Wire® Communication Constraints | . 25 |

www.ti.com

Page

Page

Title

ÈXAS

RUMENTS

#### Table 13. Errata List for the HS USB Module

| ge |

|----|

| 3  |

| 7  |

| 9  |

| 9  |

| 1  |

| 1  |

| 2  |

| 1  |

| 5  |

| 9  |

| )  |

|    |

#### Table 14. Errata List for the HS USB OTG Module

#### Title Page Advisory 1.20 — OCP Error Does Not Get Communicated to USBOTG..... 45 Advisory 1.76 — USB OTG DMA Status Register Read Return Zero ...... 79 Advisory 1.99 — HS USB OTG Spurious IRQ When Switching From DMA Mode 1 to DMA Mode 0 or to CPU Mode for Unloading the Last Short Packet of a Transaction ..... 100 Advisory 1.109 — USB OTG Software Initiated ULPI Accesses To PHY Registers Can Halt the Bus ...... 106

#### Table 15. Errata List for the I2C Module

#### Page

| Usage Note 2.11 — Extra Power Consumed When Repeated Start Operation Mode Is Enabled on I2C Interface<br>Dedicated for Smart Reflex (I2C4) | 21 |

|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| Advisory 1.2 — I2C Module Does Not Allow 0-Byte Data Requests                                                                              | 32 |

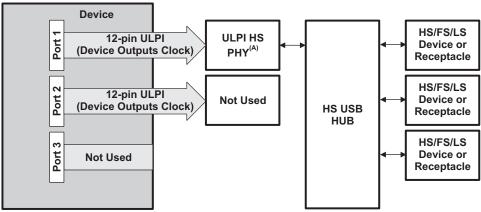

| Advisory 1.7 — I2C: RDR Flag May Be Incorrectly Set                                                                                        | 35 |

| Advisory 1.43 — I2C: I2C_STAT:XUDF Is Not Functional in Slave Transmitter Mode                                                             | 58 |

| Advisory 1.59 — I2C4 Does Not Meet I2C Standard AC Timing in FS Mode                                                                       | 72 |

| Advisory 1.60 — I2C1 to 3 SCL Low Period Is Shorter in FS Mode                                                                             | 72 |

| Advisory 1.92 — I2C: In SCCB Mode, Under Specific Conditions, the Module Might Hold the Bus by Keeping SCL Low                             | 94 |

| Advisory 1.93 — I2C: Wrong Behavior When Data With MSB 0 Is Put in the FIFO Before a Transfer With SBLOCK Is Started.                      | 94 |

| Advisory 1.94 — I2C: After an Arbitration is Lost the Module Incorrectly Starts the Next Transfer                                          | 95 |

All Errata Listed by Module

#### Table 16. Errata List for the INTC Module

#### Title

#### Table 17. Errata List for the ISP Module

#### Title

Title

Title

Title

Titlo

#### Table 18. Errata List for the IVA2 Module

#### Page Usage Note 2.2 — IVA2: Under Hardware Emulation, IDLE Instruction Must Be Executed From L1P or L2 SRAM ..... 17 Advisory 1.6 — IVA2: Block Cache Operations Word Count (\*WC) Must be Less Than or Equal to 0xFF80 ...... 34 Advisory 1.96 — 4-cycle Saturating .M Unit Instructions May Mask 2-cycle Saturating .M Unit Instruction Saturation 96 Bit Update..... ..... Advisory 1.97 — SPLOOP CPU Cross-Path Stall ..... 97

#### Table 19. Errata List for the IVA2.2 Module

#### Page

Page

Usage Note 2.10 — Maximum 12 Bits Output (1 bit sign + 11 bits of value) Is Supported on CAVLD of iVLCD ..... 21

#### Table 20. Errata List for the JTAG Module

| Advisory 1.66 — IVA2 SEQ (ARM9) JTAG Failures With a Free Running Clock Emulator                                         | 75 |

|--------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                          |    |

| Advisory 1.67 — Isolation Issue in OFF Mode Impacting the CORE Power Domain                                              |    |

| Advisory 1.73 — JTAG Pins With bq18jtagfbpbnopm_ssbhv IO Have ESD (Electro Static Discharge) Weakness in<br>Input Buffer |    |

#### Table 21. Errata List for the McBSP Module

|                                                                                                       | i ugo |

|-------------------------------------------------------------------------------------------------------|-------|

| Usage Note 3.5 — Undesired McBSP slave mode behavior during reset without CLKR/CLKX                   | . 27  |

| Advisory 1.86 — PER Domain Reset Issue After Domain-OFF/OSWR Wake-Up                                  | . 87  |

| Advisory 1.89 — McBSP Used in Slave Mode Can Create a Dead Lock Situation When Doing Power Management | . 91  |

| Advisory 1.104 — McBSP2 Data Corruption                                                               | 102   |

#### Table 22. Errata List for the MMC Module

| Т | ïtle                                                                | Page |

|---|---------------------------------------------------------------------|------|

|   | Usage Note 2.15 — MMC IOs Reliability Issue                         | 23   |

|   | Advisory 1.57 — MMC OCP Clock Not Gated When Thermal Sensor Is Used |      |

Page

### Page

Page

SPRZ319F-August 2010-Revised April 2014 DM3730, DM3725 Digital Media Processors (Silicon Revisions 1.2, 1.1, 1.0) Submit Documentation Feedback

Copyright © 2010–2014, Texas Instruments Incorporated

Advisory 1.106 — MPU Leaves MSTANDBY State Before IDLEREQ of Interrupt Controller is Released...... 103

#### Table 24. Errata List for the PRCM Module

| Usage Note 2.3 — Domain Woken Up by Wake-Up Dependency Cannot Transition to Inactive State                             | 18  |

|------------------------------------------------------------------------------------------------------------------------|-----|

| Usage Note 2.5 — Observability Signals Not Functional in OFF Mode                                                      | 18  |

| Usage Note 2.6 — Constraints on Module Clocks When Using DVFS                                                          | 19  |

| Usage Note 2.9 — GPIO Is Driving Random Values When Device Returns From OFF Mode                                       | 20  |

| Usage Note 2.13 — PWDNx Bit in CLock Manager Is Reseting the DPLL4 Mx HSDIVIDER Coefficient Previously<br>Programmed   | 23  |

| Advisory 1.9 — Inactive State Management: Impossible to Transition to OFF or RETENTION States                          | 37  |

| Advisory 1.11 — Inappropriate Warm Reset Generation on Smart Reflex I2C Error                                          | 38  |

| Advisory 1.21 — L3 Interconnect Clock Divisor Default Value Must be Modified Before Configuration of SDRAM Controller. | 45  |

| Advisory 1.45 — GPIO Pad Spurious Transition (Glitch/Spike) During Wake Up Entering or Exiting System OFF Mode         | 62  |

| Advisory 1.61 — Missed Dependency With McBSP External Clock Prevents Transition to OSWR                                | 72  |

| Advisory 1.84 — DPLL3 in Manual Lock Mode Cannot Be Used When CORE Goes to OSWR or OFF State                           | 84  |

| Advisory 1.98 — RTA Feature is Not Supported                                                                           | 99  |

| Advisory 1.107 — Some Power Domains Cannot Go To OFF Mode After Warm Reset                                             | 104 |

#### Table 25. Errata List for the ROM Code Module

| Title F                                                                                                  |      |

|----------------------------------------------------------------------------------------------------------|------|

| Advisory 1.40 — ROM Code: CKE PAD Is Not Set When Initializing External RAM                              | . 56 |

| Advisory 1.41 — ROM Code: SDRC_POWER Register Is Initialized With Hardcoded Value                        | . 57 |

| Advisory 1.42 — ROM Code: When sys-clock = 16.8MHz, Then Peripheral Booting via UART3 Is Not Operational | . 57 |

| Advisory 1.110 — At Context Restore, a Certain PER DPLL Programming Can Introduce Wake-up Latencies      | 106  |

| Advisory 1.111 — USB Peripheral Booting is Not Operational When an MMC Booting has Been Attempted Before | 107  |

#### Table 26. Errata List for the SDRC Module

| Advisory 1.51 — Accesses to DDR Stall in SDRC After a Warm-Reset              | 67  |

|-------------------------------------------------------------------------------|-----|

| Advisory 1.85 — PRCM DPLL Control FSM Removes SDRC_IDLEREQ Before DPLL3 Locks | 85  |

| Advisory 1.87 — Self-Refresh Exit Issue After OFF Mode                        | 88  |

| Advisory 1.88 — Programming of tCKE                                           | 90  |

| Advisory 1.95 — One Timing Does Not Follow the JEDEC Standard                 |     |

| Advisory 1.101 — Violation of Vix Crossing Specification 1                    | 101 |

#### Table 27. Errata List for the SGX Module

| Advisory 1.30 — SGX Bugs Documented in Imagination Technologies™ Errata | 46 |

|-------------------------------------------------------------------------|----|

| Advisory 1.77 — POWERVR SGX™: MMU Lockup on Multiple Page Miss          | 80 |

#### www.ti.com

Title

Title

Title

Title

#### All Errata Listed by Module

Page

Page

#### Page

#### Page

15

Page

| All Errata Listed by Module www.ti.com                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| Table 28. Errata List for the SPI Module                                                                                                     |

| Title Page                                                                                                                                   |

| Advisory 1.15 — SPI Dummy DMA RX Request Generation       42         Advisory 1.33 — McSPI Can Generate a Wrong Underflow Interrupt       49 |

| Table 29. Errata List for the SR Module                                                                                                      |

| Title Page                                                                                                                                   |

| Advisory 1.46 — Voltage Processor TRANXDONE Interrupt Occurs Too Early                                                                       |

| Table 30. Errata List for the TDL Module                                                                                                     |

| Title Page                                                                                                                                   |

| Advisory 1.74 — Scan Shift Issues in GWG Memories                                                                                            |

| Table 31. Errata List for the Timer Module                                                                                                   |

| Title Page                                                                                                                                   |

| Advisory 1.3 — Delay Required to Read Some GP, WD, and Sync Timer Registers After Wake-Up 32                                                 |

| Table 32. Errata List for the UART Module                                                                                                    |

| Title Page                                                                                                                                   |

| Usage Note 2.7 — UART: Cannot Acknowledge Idle Requests in Smartidle Mode When Configured for DMA<br>Operations                              |

| Advisory 1.5 — MDR1 Access Can Freeze UART Module When in IrDa Mode                                                                          |

| Table 33. Errata List for the VENC Module                                                                                                    |

| Title Page                                                                                                                                   |

| Usage Note 2.4 — VENC: Last Data Line Missing in PAL                                                                                         |

| Table 34. Errata List for Cautions                                                                                                           |

| Title Page                                                                                                                                   |

| Usage Note 3.4 — Avoiding Voltage Drop When Booting at 1-GHz OPP With TPS65950A3 26                                                          |

#### 4 Usage Notes and Known Design Exceptions to Functional Specifications

#### 4.1 Usage Notes (Limitations)

Usage Notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data manual), and the behaviors they describe will not be altered in future silicon revisions.

**Note:** The peripherals supported on the various microprocessors are different. The user should only refer to usage notes and advisories pertaining to features supported on the specific device. For a complete list of the supported features of the microrocessors, see the device-specific data manuals.

#### Usage Note 2.1 Performance Limitation On LCD Read/Write Access Through RFBI L4 Port

#### Revision(s) Affected 1.2, 1.1 and 1.0

Details

**Read access to the LCD through the RFBI L4 port**: The data of a *Read* access is sent back to the initiator of the access only at RECycleTime. RECycleTime is used as a reference event for CS release as well (CS is used as an on-going access notification signal depending on the type of LCD panel connected). This means that any *Read* access to the LCD through the L4 interface of the RFBI will be ended by a CS release (CS going inactive at the end of the access). Therefore, the processor does not support two consecutive *Read* accesses to the LCD (there is always 1 L4 clock cycle between 2 accesses).

Write access to the LCD through the RFBI L4 port: For a *Write* access, the back-toback data of a single access that has been split is supported and guaranteed (e.g., one 32-bit write split in two consecutive, back-to-back, 16-bit accesses). In this case, the internal bus CS signal will be kept active until split access completion. However, when there are two different write accesses from the initiator, they will not be seen as back-toback by the LCD. At the end of the transaction corresponding to one write access from the initiator, the internal bus CS will be released at WECycleTime, and the next command from the initiator will be accepted. Consequently, any *Write* access to the LCD through the L4 interface of the RFBI will be ended by a CS release (CS going inactive at the end of the access). Therefore, the processor does not support two consecutive data transmits to the LCD (corresponding to two different and consecutive *Write* accesses from the initiator).

## Usage Note 2.2 *IVA2: Under Hardware Emulation, IDLE Instruction Must Be Executed From L1P or L2 SRAM*

Revision(s) Affected 1.2, 1.1 and 1.0

**Details** This limitation was fixed and is kept for silicon errata consistency only. The workaround can be removed from the code.

| Usage Note 2.3       | Domain Woken Up by Wake-Up Dependency Cannot Transition to Inactive State                                                                                                                                                                                                                                                                                                                               |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected | 1.2, 1.1 and 1.0                                                                                                                                                                                                                                                                                                                                                                                        |

| Details              | When a domain is activated up by a wake-up dependency, it cannot transition to an inactive (RET/OFF) state until one of the following conditions are satisfied:                                                                                                                                                                                                                                         |

|                      | <ol> <li>If the domain has a sleep dependency with another domain, this domain and the<br/>sleep dependency must be also activated (hard-wired or enabled by the software).</li> </ol>                                                                                                                                                                                                                  |

|                      | 2. If the domain is an initiator, it must be taken out of <i>Standby</i> mode.                                                                                                                                                                                                                                                                                                                          |

|                      | <b>Note:</b> The user should ensure that when a wake-up dependency is enabled for a domain, it is expected to be fully active after the wake-up occurs. This issue happens in a case where a domain has been woken-up, but not activated and used.                                                                                                                                                      |

|                      | This issue can be avoided by ensuring the IVA2 processor is taken out of <i>Standby</i> mode prior to any new sleep transition.                                                                                                                                                                                                                                                                         |

| Usage Note 2.4       | VENC: Last Data Line Missing in PAL                                                                                                                                                                                                                                                                                                                                                                     |

| Revision(s) Affected | 1.2, 1.1 and 1.0                                                                                                                                                                                                                                                                                                                                                                                        |

| Details              | The VENC cannot show the image data at the end of the even frames on line 623. This is a minor violation of the ITU-R BT.470-6. Since lines 23 and 336 are reserved for WSS, the VENC can only show 574 lines of data instead of the 576 lines defined in the standard. One half line is missing for lines 23 (reserved for WSS) and 623, and one full line is missing for line 336 (reserved for WSS). |

| Usage Note 2.5       | Observability Signals Not Functional in OFF Mode                                                                                                                                                                                                                                                                                                                                                        |

| Revision(s) Affected | 1.2, 1.1 and 1.0                                                                                                                                                                                                                                                                                                                                                                                        |

| Details              | Signals are routed to observability pins through a buffer powered by VDD2.<br>Consequently, observability is not functional when VDD2 is powered off. This impacts<br>the observability debug feature, but has no functional drawback.                                                                                                                                                                  |

|                      | <b>Note:</b> Maintaining the VDD2 supply on the board has no effect since isolation cells are activated regardless of the supplied voltage.                                                                                                                                                                                                                                                             |

| www.ti.com           | <b>Usage Note 2.6</b> — Constraints on Module Clocks When Using DVFS                                                                                                                                                                                                                                                                                             |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Usage Note 2.6       | Constraints on Module Clocks When Using DVFS                                                                                                                                                                                                                                                                                                                     |

| Revision(s) Affected | 1.2, 1.1 and 1.0                                                                                                                                                                                                                                                                                                                                                 |

| Details              | Module interface timings can depend on the operating point (OPP). The timing closure is done for one instance of a module at a particular voltage. Operating conditions which work on one OPP are not automatically guaranteed on another module's OPP. For more details on the module interface switching characteristics, see the device-specific data manual. |

| Workaround(s)        | <ul> <li>When Dynamic Voltage and Frequency Scaling (DVFS) is performed, the software should ensure that no timing violations will occur by the two following methods:</li> <li>Using software, reconfigure the module accordingly when DVFS is performed to avoid timing violations.</li> </ul>                                                                 |

|                      | <ul> <li>Use a conservative frequency on the module interface clock corresponding to the<br/>performance of the lower OPP used to ensure that DVFS can be performed without<br/>additional software management.</li> </ul>                                                                                                                                       |

| Usage Note 2.7       | UART: Cannot Acknowledge Idle Requests in Smartidle Mode When Configured for DMA Operations                                                                                                                                                                                                                                                                      |

| Revision(s) Affected | 1.2, 1.1 and 1.0                                                                                                                                                                                                                                                                                                                                                 |

| Details              | When configured for DMA operations using <i>smartidle</i> mode (SYSC[4:3].IDLEMODE = 0x2), the UART module will not acknowledge incoming idle requests. As a consequence, it can prevent L4 from going to idle.                                                                                                                                                  |

|                      | When there are additional expected transfers, the UART should be placed in <i>force-idle</i> mode.                                                                                                                                                                                                                                                               |

#### Usage Note 2.9 GPIO Is Driving Random Values When Device Returns From OFF Mode

**Revision(s)** Affected 1.2, 1.1 and 1.0

Details The GPIO modules in the PER (Peripheral) domain are driving random values when the device returns from OFF mode with the VDD2 voltage shut down. Regardless of the active configuration of a GPIO (input or output), when coming back from OFF mode, GPIO can randomly drive the line high or low.

> Root cause: The isolation at the boundary of the peripheral domain is done through isolation latches that are supplied by VDD2. When VDD2 is shut down, the content of the latches is lost. When the device is waking-up from the OFF mode, the padconf is automatically restored by the hardware and the isolation latches are driving the pin until isolation is released (PER is woken-up). There is no reset value for the isolation latches, leading to random values driven by the GPIO.

This is not impacting the GPIO from the WU domain. Only GPIO is implementing this kind of isolation latch, other functions are not impacted by this limitation.

Workaround 1 allows software to work in software supervised mode while Workaround 2 Workaround(s) gets the benefit of hardware dependency. For both workarounds, software is used to configure the internal pull in the padconf register to the desired value.

> Workaround1: Change padconf mode to safe mode before initiating the transition to OFF. This avoids the line being driven by the isolation latch and the desired level is maintained by the pull.

Workaround2: Create a WU dependency between WU domain and PER domain (PM\_WKDEP\_PER[4]: EN\_WKUP=1). This will wake up the PER domain, then release the isolation latch before the isolation cell is released at the pad boundary. The reset value of the GPIO module is configuring the GPIO in input, then the pull ensures that the line is driven to the right value until the GPIO module is restored by the applicative software

| Usage Note 2.10      | Maximum 12 Bits Output (1 bit sign + 11 bits of value) Is Supported on CAVLD of iVLCD                                                                                                                                                                                                                                                                                           |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected | 1.2, 1.1 and 1.0                                                                                                                                                                                                                                                                                                                                                                |

| Details              | While decoding DC coefficients of an Intra16x16 MB, the iVLCD is not able to handle coefficients with range greater than 11 bits. It is observed that the value returned by the iVLCD will be the equivalent of (actual_value & 0x07FF). For example, value of 0x08A7 will be decoded as 0x00A7. However, the bits consumed by the iVLCD is correct and the decoding continues. |

|                      | As per the standard, normal imagery can generate DC coeffs with range greater than 11 bits (especially at low QP) and some of the test cases are failing due to this issue. Since the error is in DC it will not only affect the MB in question, but propagate to neighboring MBs in the slice. The impact is visually noticeable.                                              |

|                      | This issue only occurs if either of the following conditions are met:                                                                                                                                                                                                                                                                                                           |

|                      | <ul> <li>For QP&lt;10, Luma DC coefficients of Intra16x16 MB</li> </ul>                                                                                                                                                                                                                                                                                                         |

|                      | <ul> <li>For QP&lt;4, Chroma DC coefficients</li> </ul>                                                                                                                                                                                                                                                                                                                         |

|                      | This special case must be handled with C64x+ software, which increases code size and adds extra MHz.                                                                                                                                                                                                                                                                            |

|                      | The estimate of the cost for the work added is: extra 3-4 MHz and 25kB of code.                                                                                                                                                                                                                                                                                                 |

| Usage Note 2.11      | Extra Power Consumed When Repeated Start Operation Mode Is Enabled on I2C<br>Interface Dedicated for Smart Reflex (I2C4)                                                                                                                                                                                                                                                        |

| Revision(s) Affected | 1.2, 1.1 and 1.0                                                                                                                                                                                                                                                                                                                                                                |

| Details              | On the I2C interface dedicated for Smart Reflex communication with the Power<br>Management IC (I2C4), when Repeated Start operation mode is enabled<br>(PRM_VC_I2C_CFG[SREN]='1'), the I2C lines (SCL and SDA) are always driving a low<br>state between two I2C commands (i.e. when there is no I2C traffic).                                                                  |

|                      | Knowing that there are external Pull-Up attached on these lines, this will impact the power consumption.                                                                                                                                                                                                                                                                        |

|                      | Setting PRM_VC_I2C_CFG[SREN] register bit to '0' will allow the I2C4 lines driving a high state between two I2C commands.                                                                                                                                                                                                                                                       |

| Usage Note 2.12      | SGX 192 MHz Limitation With TVOUT @ 54 MHz                                                                                                                                                                                                                                                                                  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected | 1.2, 1.1 and 1.0                                                                                                                                                                                                                                                                                                            |

| Details              | The siimultaneous operation of SGX530 @ 192 MHz and TVOUT clock @ 54 MHz is not possible.                                                                                                                                                                                                                                   |

|                      | SGX functional clock can be selected from four sources:                                                                                                                                                                                                                                                                     |

|                      | <ul> <li>Divided version of the CORE.CLK [by 2, 3, 4, 6]</li> </ul>                                                                                                                                                                                                                                                         |

|                      | <ul> <li>Divided version of the COREX2.CLK [by 3, 5]</li> </ul>                                                                                                                                                                                                                                                             |

|                      | 96 MHz clock version                                                                                                                                                                                                                                                                                                        |

|                      | 192 MHz clock version                                                                                                                                                                                                                                                                                                       |

|                      | The frequency combination of SGX530 @ 192 MHz along with TVOUT @ 54 MHz is not possible with the TVout clock divider which maximum value is 31.                                                                                                                                                                             |

|                      | TV-Out requires a 54MHz clock provided by the DPLL-PER (DPLL4) , then the DPLL-<br>PER has to be set to 864 MHz to get the 54MHz clock. In the case of setting DPLL-PER<br>at 1728MHz to get 192Mhz on SGX will not allow getting the 54MHz on TVOUT since<br>high-speed divider is limited to 31.                          |

| Workaround(s)        | Only if TVOUT@54MHz is a workaround required. The SGX clock will have to be sourced from CORE-DPLL (SGX clock will scale with L3 clock). When software is using TV-Out @ 54 Mhz, SGX functional clock has to be derived from CORE-DPLL which allows up to 200MHz clock frequency depending on the CORE clock configuration. |

| www.ti.com           | Usage Note 2.13 — PWDNx Bit in CLock Manager Is Reseting the DPLL4 Mx HSDIVIDER Coefficient<br>Previously Programmed                                                                                                                                                                    |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Usage Note 2.13      | PWDNx Bit in CLock Manager Is Reseting the DPLL4 Mx HSDIVIDER Coefficient<br>Previously Programmed                                                                                                                                                                                      |

| Revision(s) Affected | 1.2, 1.1 and 1.0                                                                                                                                                                                                                                                                        |

| Details              | <ul> <li>When PWRDN bit is set, it resets the internal HSDIVIDER divide-by value (Mx). The reset value gets loaded instead of the previous value. The following HSDIVIDERs exhibit this behavior:</li> <li>DPLL4: M6 / M5 / M4 / M3 / M2 (CM_CLKEN_PLL[31:26] register bits)</li> </ul> |

|                      | DPLL3: M3 (CM_CLKEN_PLL[12] register bit).                                                                                                                                                                                                                                              |

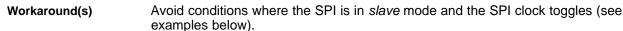

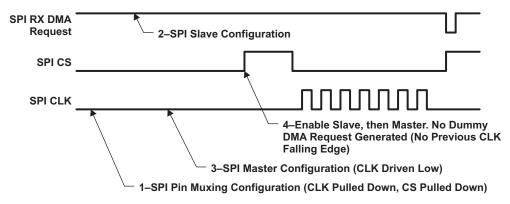

| Workaround(s)        | No performance impact by using the following workaround.                                                                                                                                                                                                                                |