# 66AK2G0x Multicore DSP+ARM KeyStone II System-on-Chip (SoC) Silicon Revision 1.0

This document describes the known exceptions to the functional specifications (advisories). This document may also contain usage notes. Usage notes describe situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness.

#### Topic

#### Page

| 1 | Usage Notes and Advisories Matrices                              | 2  |

|---|------------------------------------------------------------------|----|

| 2 | Nomenclature, Package Symbolization, and Revision Identification | 3  |

| 3 | Silicon Revision 1.0 Usage Notes and Advisories                  | 5  |

| 4 | Modules Affected                                                 | 10 |

2

## **1** Usage Notes and Advisories Matrices

Table 1 lists all usage notes and the applicable silicon revision(s). Table 2 lists all advisories, modules affected, and the applicable silicon revision(s).

## Table 1. Usage Notes Matrix

| ID                                 | DESCRIPTION                                         | SILICON<br>REVISIONS<br>AFFECTED |

|------------------------------------|-----------------------------------------------------|----------------------------------|

|                                    |                                                     | 1.0                              |

| KeyStonell.BTS_errata_usagenote.10 | Section 3.1.1, I2C: I2C Bus Hang After Master Reset | Yes                              |

#### **Table 2. Advisories Matrix**

| MODULE                    | DESCRIPTION                                                                                                                             | SILICON<br>REVISIONS<br>AFFECTED |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|                           |                                                                                                                                         | 1.0                              |

| PCIe®                     | KeyStonell.BTS_errata_advisory.21 — PCIe: Descriptors Placed in PCIe Memory<br>Space Can Cause Problems                                 | Yes                              |

| PCle                      | KeyStonell.BTS_errata_advisory.43 — PCIe: SerDes Fails to Adapt BOOST<br>Equalization                                                   | Yes                              |

| PCIe, Control Module      | KeyStonell.BTS_errata_advisory.44 — PCIe, Control Module: PCIe Hot Reset Not<br>Honored by ROM Code                                     | Yes                              |

| BOOT, GMAC_SW             | KeyStonell.BTS_errata_advisory.45 — BOOT, GMAC_SW: Ethernet Boot Failure on<br>RESETn                                                   | Yes                              |

| BOOT, GPMC                | KeyStonell.BTS_errata_advisory.46 — BOOT, GPMC: GPMC XIP Boot Failure                                                                   | Yes                              |

| Control Module            | KeyStonell.BTS_errata_advisory.48 — Control Module: Internal Oscillator Does Not<br>Always Start Reliably                               | Yes                              |

| PADCONFIG, Control Module | KeyStonell.BTS_errata_advisory.49 — PADCONFIG, Control Module: Unexpected<br>Write Operation to BOOTCFG_PADCFG194 and BOOTCFG_PADCFG202 | Yes                              |

## 2 Nomenclature, Package Symbolization, and Revision Identification

## 2.1 Device and Development-Support Tool Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all microprocessors (MPUs) and support tools. Each device has one of three prefixes: X, P, or null (no prefix) (for example, 66AK2G02). Texas Instruments recommends two of three possible prefix designators for its support tools: TMDX and TMDS. These prefixes represent evolutionary stages of product development from engineering prototypes (X/TMDX) through fully qualified production devices and tools (null/TMDS).

Device development evolutionary flow:

- **X** Experimental device that is not necessarily representative of the final device's electrical specifications and may not use production assembly flow.

- **P** Prototype device that is not necessarily the final silicon die and may not necessarily meet final electrical specifications.

- null- Production version of the silicon die that is fully qualified.

Support tool development evolutionary flow:

- **TMDX** Development-support product that has not yet completed Texas Instruments internal qualification testing.

- TMDS Fully-qualified development-support product.

X and P devices and TMDX development-support tools are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

Production devices and TMDS development-support tools have been characterized fully, and the quality and reliability of the device have been demonstrated fully. TI's standard warranty applies.

Predictions show that prototype devices (X or P) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

For additional information how to read the complete device name for any 66AK2G0x device, see the device Data Manual (SPRS932).

## 2.2 Devices Supported by This Document

This document supports the following devices:

- 66AK2G01

- 66AK2G02

#### Nomenclature, Package Symbolization, and Revision Identification

www.ti.com

#### Package Symbolization and Revision Identification 2.3

Figure 1 and Table 3 describe package symbolization and device revision codes.

**Device Revision Code**

## Figure 1. Package Symbolization

## **Table 3. Revision Identification**

| DEVICE REVISION CODE | SILICON REVISION | COMMENTS           |

|----------------------|------------------|--------------------|

| BLANK                | 1.0              | Available as null. |

## 3 Silicon Revision 1.0 Usage Notes and Advisories

This section lists the usage notes and advisories for this silicon revision.

## 3.1 Silicon Revision 1.0 Usage Notes

## 3.1.1 I<sup>2</sup>C: I<sup>2</sup>C Bus Hang After Master Reset

On 66AK2G0x silicon revision 1.0, the I<sup>2</sup>C bus can hang if an I<sup>2</sup>C master is removed from the bus in the middle of a data read. This can occur because the I<sup>2</sup>C protocol does not mandate a minimum clock rate. Therefore, if a master is reset in the middle of a read while a slave is driving the data line low, the slave will continue driving the data line low while it waits for the next clock edge. This prevents bus masters from initiating transfers.

If this condition is detected, the following three steps will clear the bus hang condition:

- 1. An I<sup>2</sup>C master must generate up to 9 clock cycles.

- 2. After each clock cycle, the data pin must be observed to determine whether it has gone high while the clock is high.

- 3. As soon as the data pin is observed high, the master can initiate a start condition.

## 3.2 Silicon Revision 1.0 Advisories

## Table 4. Silicon Revision 1.0 Advisory List

| itle Pa                                                                                                                                 | age |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| KeyStonell.BTS_errata_advisory.21 — PCIe: Descriptors Placed in PCIe Memory Space Can Cause Problems                                    | 5   |

| KeyStonell.BTS_errata_advisory.43 — PCIe: SerDes Fails to Adapt RX BOOST Equalization                                                   | 6   |

| KeyStonell.BTS_errata_advisory.44 — PCIe, Control Module: PCIe Hot Reset Not Honored by ROM Code                                        | 7   |

| KeyStonell.BTS_errata_advisory.45 — BOOT, GMAC_SW: Ethernet Boot Failure on RESETn                                                      | 7   |

| KeyStonell.BTS_errata_advisory.46 — BOOT, GMPC: GPMC XIP Boot Failure                                                                   | 7   |

| KeyStonell.BTS_errata_advisory.48 — Control Module: Internal Oscillator Does Not Always Start Reliably                                  | 8   |

| KeyStonell.BTS_errata_advisory.49 — PADCONFIG, Control Module: Unexpected Write Operation to<br>BOOTCFG_PADCFG194 and BOOTCFG_PADCFG202 | 9   |

## KeyStonell.BTS\_errata\_advisory.21

#### PCIe: Descriptors Placed in PCIe Memory Space Can Cause Problems

| Revision(s) Affected: | 1.0                                                                                                                                                                                                                                                                                                                                           |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Details:              | Packet DMA can generate write transactions with partial byte enables when trying to access descriptors. This can cause problems if the descriptors are stored in PCIe memory space since PCIe cannot handle partial byte enables. Here, partial byte enables means that the transactions are accessing memory that is not a full 32-bit word. |

| Workaround(s):        | As long as host-mode descriptors are used and these descriptors are located in a memory space that can properly handle partial byte enables (such as L2 SRAM, DDR3 or MSMC), the issue will not affect Packet DMA accesses to PCIe memory space. As mentioned earlier, data buffers can be stored in PCIe memory space without any problems.  |

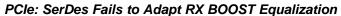

### KeyStonell.BTS\_errata\_advisory.43

Revision(s) Affected: 1.0

Details:

**NOTE:** The advisory does not impact 10GbE operation.

The SerDes on PCIe will not automatically adapt its RX equalization when provided with certain data encodings common to that peripheral's electrical standard.

The TI SerDes contains an adaptation algorithm that allows the RX equalization blocks to adapt their parameters to the SerDes data channel. The adaptation algorithm sets the optimal values for the ATT, BOOST, and DFE blocks in order to equalize the signal, maximize margin, and minimize channel distortion. For higher data rates (that is 5Gbps and greater), the high frequency gain provided by the BOOST block is generally considered necessary to compensate for the low-pass characteristics of data channels and widen the data eye.

The SerDes BOOST block was designed to require a specific set of patterns in order to best adapt its parameters to the channel. If these patterns are not found, the BOOST adaptation algorithm will not update the internal block settings and/or may incorrectly update these settings. The required data pattern is a series of six 0'-s followed by a 101 pattern. This pattern must occur numerous times on both odd and even bit alignments. This data pattern is not present in the 8b/10b coded symbols that are sent over many of the high speed peripheral links.

The data pattern is present in longer length PRBS patterns such as PRBS-23, and PRBS-31 used by the SerDes internal BIST hardware used during BER testing. The data pattern that is required is not present in the symbols used in PCIe SerDes interfaces during data transport.

If the BOOST has not been properly adapted for the received signal, then there is a chance that the SerDes will be unable to recover the RX data or the error rate may be higher than expected.

Workaround(s): The recommended workaround is to not use the RX equalization auto-adaptation mechanism with the impacted interfaces at higher data rates. As an alternative, a user can hardcode the optimal ATT and BOOST values for their channel. These optimal ATT and BOOST values must be determined by the user through one of two options:

Perform BER test with PRBS sequence and sweep across all values of ATT/BOOST

#### www.ti.com KeyStonell.BTS\_errata\_advisory.44 — PCle, Control Module: PCle Hot Reset Not Honored by ROM Code

while using a fixed set of TX parameters that have already been optimized. Use optimal ATT and BOOST value permutation that has the most margin. This is the value permutation that is both error-free and "farthest" from permutations with errors.

- The SerDes DIAG tests can be found under <TI\_PDK\_INSTALL\_DIR>\packages\ti\diag\serdes\_diag in the latest CSL/PDK release and can be configured to perform this test.

- Perform a test where a PRBS data pattern is presented to the RX and the ATT/BOOST are allowed to auto-adapt. This method can also be used to identify the optimal ATT and BOOST value permutation that has the most margin.

The optimal ATT and BOOST values found by one of the two above methods can be hardcoded into the SerDes upon initialization.

## KeyStonell.BTS\_errata\_advisory.44

#### PCIe, Control Module: PCIe Hot Reset Not Honored by ROM Code

| Revision(s) Affected: | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Details:              | When receiving a PCI-Express (PCIe) Hot Reset request during the PCIe boot process, the PCI-Express Subsystem (PCIESS) will disable the Link Training and Status State Machine (LTSSM) and suspend the PCIe bus in the Detect.Quiet state. With the LTSSM disabled, there will be no subsequent transition from Detect.Quiet to Detect.Active and the PCIe boot process will fail.                                                                                                                                              |

| Workaround(s):        | <ol> <li>Prevent the PCIe Root Complex (RC) from issuing PCIe Hot Reset during the PCIe boot process or</li> <li>Do not use PCIe as the primary boot mode. Use an alternative boot mode and post boot application software or secondary boot loader implement the PCIe hot reset handling to appropriately communicate with the root complex host. The interrupt handling support in bootloader depends on its software architecture. Note that many bootloaders like U-Boot (http://www.denx.de/wiki/U-Boot) do not</li> </ol> |

|                       | support interrupt handling on ARM architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## KeyStonell.BTS\_errata\_advisory.45

## BOOT, GMAC SW: Ethernet Boot Failure on RESETn **Revision(s) Affected:** 1.0 On hard/soft resets (for example, RESETn pin) the boot ROM incorrectly configures the Details: internal Ethernet switch. This causes a boot failure if the configuration happens while packets are traversing the switch. Workaround(s): Only RESETFULLn or PORn reliably allow Ethernet boot mode to work. KeyStonell.BTS\_errata\_advisory.46 BOOT, GMPC: GPMC XIP Boot Failure **Revision(s) Affected:** 1.0 General-Purpose Memory Controller (GPMC) eXecute in Place (XIP) boot fails with Details: default timing value. The default timing value is too aggressive for the currently available flash devices. To Workaround(s): work around this issue, the boot pins should select a PLL reference clock frequency that

is higher than the actual reference clock frequency. For example, if the actual reference clock frequency is 24 MHz, then the boot pins need to select a 100 MHz reference clock

#### KeyStonell.BTS\_errata\_advisory.48 — Control Module: Internal Oscillator Does Not Always Start Reliably www.ti.com

frequency. The XIP boot then will succeed and the PLLs can be reconfigured along with the XP timing to continue the booting process.

# KeyStonell.BTS\_errata\_advisory.48

Control Module: Internal Oscillator Does Not Always Start Reliably

Revision(s) Affected:

1.0

Details:

The default state of the internal HF Oscillator is not always set correctly. If this condition occurs, the internal HF Oscillator will not start causing the SoC to remain in the reset state.

This issue is only observed if the SYSCLKSEL is set low to select the internal HF OSC. If the problem occurs, no oscillation will be observed at the SYSOSC\_OUT pin and the part will not exit reset. JTAG access will not be possible either.

Warkessurd(a):

This state can be evalued by setting RSV(6 to a bigh state while DORp is low for a

Workaround(s): This state can be avoided by setting RSV6 to a high state while PORn is low for a minimum of 5msec after the power supplies are stable. Setting the RSV6 high will cause the HF OSC to initialize correctly allowing it to oscillate. RSV6 must then be set low a minimum of 1msec before PORn is set high. From that time on, RSV6 must be held low for proper operation.

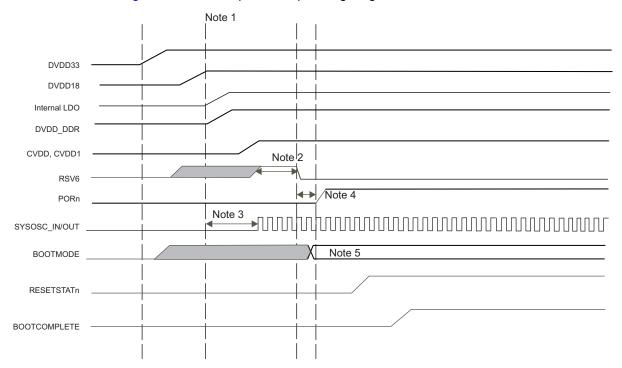

Figure 3 shows the power sequencing diagram when HF OSC.

#### Figure 3. Power System Sequence when SYSCLKSEL is Low

Note 1 – Power-up begins by enabling the DVDD33 supply first.

Note 2 – Once DVDD33 is present, RSV6 is set high and must remain high for 5msec after all supplies have ramped.

Note 3 – Oscillator Power-up time once DVDD18 is present and RSV6 is high (approx. 1-2msec).

Note 4 – PORn must be held low until all supplies have ramped and for a minimum of 1msec after RSV6 is brought low. RSV6 must remain low after PORn is set high.

Note 5 – BOOTMODE pins are latched at the rising edge of PORn (synchronously using SYSOSC\_IN/OUT).

| www.ti.com Ke         | yStonell.BTS_errata_advisory.49 — PADCONFIG, Control Module: Unexpected Write Operation to<br>BOOTCFG_PADCFG194 and BOOTCFG_PADCFG202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| KeyStonell.BTS_er     | rrata_advisory.49<br>PADCONFIG, Control Module: Unexpected Write Operation to<br>BOOTCFG_PADCFG194 and BOOTCFG_PADCFG202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Revision(s) Affected: | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Details:              | A logic error in the BOOTCFG_RSTMUX0 and BOOTCFG_RSTMUX8 lock circuit has<br>unexpected side effects on writes to the BOOTCFG_PADCFG194 and<br>BOOTCFG_PADCFG202 registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                       | The BOOTCFG_RSTMUX0 and BOOTCFG_RSTMUX8 lock circuit uses the respective RSTMUX_LOCK bit and the lower 12 bits of the address bus to select one of two data sources that will be written into the respective register during a write operation. When the lock bit is not set, data is sourced from the master performing the write operation. When the lock bit is set, data is sourced from the respective register. This effectively locks the contents of the register since it can only be updated with its own value once the lock bit is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                       | The multiplexer used in the lock circuit to select the data source was inserted in the path of all BOOTCFG registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       | Any writes to BOOTCFG_PADCFG194 or BOOTCFG_PADCFG202 when the lock bit of the corresponding BOOTCFG_RSTMUX0 or BOOTCFG_RSTMUX8 register is set will cause the respective BOOTCFG_PADCFG194 or BOOTCFG_PADCFG202 register to be updated with the contents of the corresponding BOOTCFG_RSTMUX0 or BOOTCFG_RSTMUX8 register during a write operation since the address decode logic in the lock circuit only uses the lower 12 address bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Workaround(s):        | There are two workaround options.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | <ol> <li>The BOOTCFG_PADCFG194 and BOOTCFG_PADCFG202 registers can be<br/>configured to any value required by the application before setting the lock bit in the<br/>corresponding BOOTCFG_RSTMUX0 or BOOTCFG_RSTMUX8 register. Any<br/>attempt to write a new value to the BOOTCFG_PADCFG194 and<br/>BOOTCFG_PADCFG202 registers after the lock bit has been set will change its<br/>value to the current value of the corresponding BOOTCFG_RSTMUX0 or<br/>BOOTCFG_RSTMUX8 register. Therefore, dynamic pin multiplexing is not supported<br/>for the pins associated with the BOOTCFG_PADCFG194 and<br/>BOOTCFG_PADCFG202 registers when the application requires the corresponding<br/>BOOTCFG_RSTMUX0 or BOOTCFG_RSTMUX8 register to be locked. In this use<br/>case, the BOOTCFG_PADCFG194 and BOOTCFG_PADCFG202 registers must be<br/>configured before locking the corresponding BOOTCFG_RSTMUX0 or<br/>BOOTCFG_RSTMUX8 registers and never change the contents of the<br/>BOOTCFG_PADCFG194 and BOOTCFG_PADCFG202 registers.</li> </ol> |

|                       | <ol> <li>If the application requires BOOTCFG_PADCFG194 and BOOTCFG_PADCFG202<br/>registers to be changed after being configured to their initial value, the corresponding<br/>BOOTCFG_RSTMUX0 or BOOTCFG_RSTMUX8 registers should never be locked.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Modules Affected

#### 4 **Modules Affected**

Table 5 shows the module(s) that are affected by each advisory.

| Module name    | Silicon Advisories, Limitations, and Cautions                                                                                        |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------|

| BOOT           | KeyStonell.BTS_errata_advisory.45 — BOOT, GMAC_SW: Ethernet Boot Failure on RESETn                                                   |

|                | KeyStonell.BTS_errata_advisory.46 — BOOT, GPMC: GPMC XIP Boot Failure                                                                |

| Control Module | KeyStonell.BTS_errata_advisory.44 — PCIe, Control Module: PCIe Hot Reset Not Honored by ROM Code                                     |

|                | KeyStonell.BTS_errata_advisory.48 — Control Module: Internal Oscillator Does Not Always Start Reliably                               |

|                | KeyStonell.BTS_errata_advisory.49 — PADCONFIG, Control Module: Unexpected Write Operation to BOOTCFG_PADCFG194 and BOOTCFG_PADCFG202 |

| GMAC_SW        | KeyStonell.BTS_errata_advisory.45 — BOOT, GMAC_SW: Ethernet Boot Failure on RESETn                                                   |

| GPMC           | KeyStonell.BTS_errata_advisory.46 — BOOT, GPMC: GPMC XIP Boot Failure                                                                |

| PADCONFIG      | KeyStonell.BTS_errata_advisory.49 — PADCONFIG, Control Module: Unexpected Write Operation to BOOTCFG_PADCFG194 and BOOTCFG_PADCFG202 |

| PCle           | KeyStonell.BTS_errata_advisory.21 — PCIe: Descriptors Placed in PCIe Memory Space Can Cause Problems                                 |

|                | KeyStonell.BTS_errata_advisory.43 — PCIe: SerDes Fails to Adapt BOOST Equalization                                                   |

|                | KeyStonell.BTS_errata_advisory.44 — PCle, Control Module: PCle Hot Reset Not Honored by ROM Code                                     |

## Table 5. Advisories by Modules

Table 6 shows the module(s) that are affected by each usagenote.

#### Table 6. Usagenote by Modules

| MODULE NAME | SILICON ADVISORY                                                          |

|-------------|---------------------------------------------------------------------------|

| I2C         | KeyStonell.BTS_errata_usagenote.10 — I2C: I2C Bus Hang After Master Reset |

Page

## **Revision History**

| Changes from B Revision (February 2017) to C Revision |

|-------------------------------------------------------|

|                                                       |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated