SNLS474E -FEBRUARY 2015-REVISED JUNE 2018

LMH1218

# LMH1218 Low Power Ultra HD Cable Driver With Integrated Reclocker

#### **Features**

- Supports ST-2082 (Proposed), ST-2081 (Proposed), SMPTE 424M, 344M, 292M, 259M, DVB-ASI, SFF-8431 (SFP+) and 10GbE Ethernet for SMPTE 2022-5/6

- Locks to Rates 11.88 Gbps, 5.94 Gbps, 2.97 Gbps, 1.485 Gbps, or Divided by 1.001 Sub-Rates, DVB-ASI (270 Mbps) and 10GbE (10.3125 Gbps)

- Reference-Free Operation With Fast Lock Time Covering All Supported or Selected Data Rates

- 75- $\Omega$  and 100- $\Omega$  Transmitter Outputs

- Integrated 2:1 Mux Input, 1:2 Demux/Fanout Outputs

- Automatic Slew Rate Based on Input Rate Detect

- On-Chip Eye Monitor

- Low 300-mW Power Consumption With Automatic Power Down on Loss of Input Signal

- Programmable Through SPI or SMBus Interface

- Single 2.5-V Supply Operation

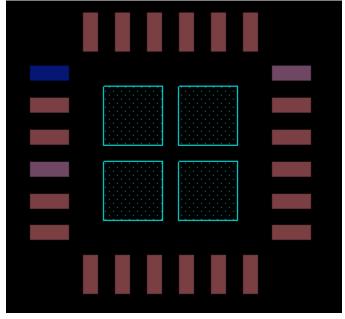

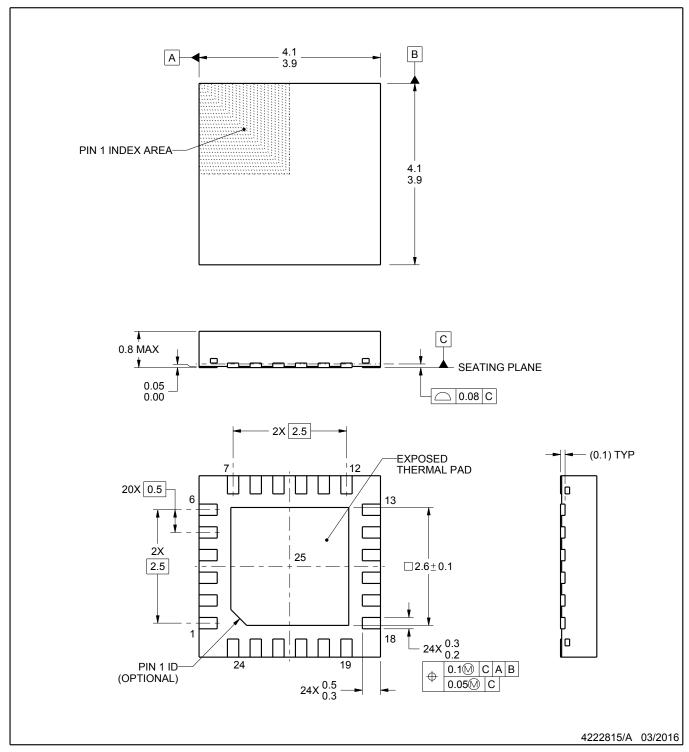

- Small 4-mm x 4-mm 24-Pin WQFN Package

- -40°C to +85°C Operating Temperature Range

### **Applications**

- UHDTV/4K/8K/HDTV/SDTV Video

- Digital Video Routers and Switches

- Digital Video Processing and Editing

- **DVB-ASI** and Distribution Amplifiers

- 10GbE for SMPTE 2022-5/6

### Description

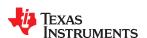

The LMH1218 device is a low-power cable driver with integrated reclocker to drive serial video data compatible to SMPTE-SDI, SMPTE 2022-5/6, 10GbE Ethernet, and DVB-ASI standards. The LMH1218 supports up to 11.88 Gbps to enable Ultra High Definition Video for 4K/8K applications. With 75- $\Omega$ and  $50-\Omega$  transmitter outputs, the LMH1218 enables multiple media options such as coax, fiber, and FR-4 PCB.

The integrated 2-to-1 MUX on the input of the LMH1218 enables selection between two video programmable sources, while the equalizer compensates for the printed-circuit board loss to extend signal reach. With a wide range clock-anddata recovery (CDR) circuit, the on-chip reclocker automatically detects and locks to serial data from 270 Mbps to 11.88 Gbps without the need for an external reference clock and loop filter component, thereby simplifying board design and lowering system cost. The reclocked serial data can be routed to either the 75- $\Omega$  or 50- $\Omega$  transmitter output, or both simultaneously (1-to-2 fanout mode). The output voltage swing is compatible to SFF-8431 (SFP+), ST-2082/1 (Proposed), SMPTE 424M, 344M, 292M, and 259M standards.

A non-disruptive eye monitor allows for real-time measurement of serial data to simplify system startup or field tuning. The LMH1218 can be programmed using SPI or SMBus Interface.

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |  |

|-------------|-----------|-------------------|--|--|

| LMH1218     | WQFN (24) | 4.00 mm × 4.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

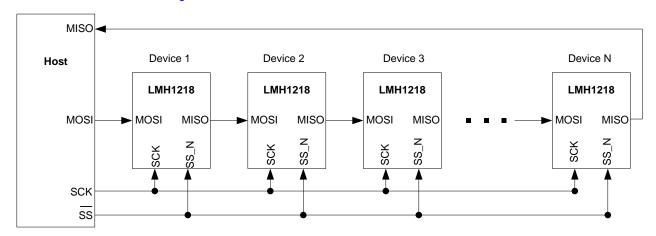

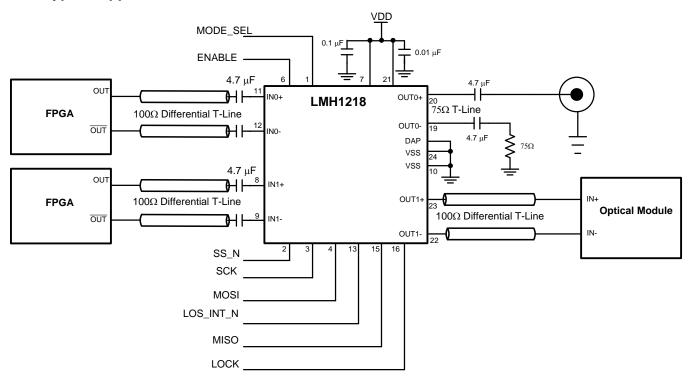

#### Simplified SPI Schematic

## **Table of Contents**

| 1 | Features 1                                           | 7.6 Register Maps                                    | . 26         |

|---|------------------------------------------------------|------------------------------------------------------|--------------|

| 2 | Applications 1                                       | 8 Application and Implementation                     | 44           |

| 3 | Description 1                                        | 8.1 Application Information                          |              |

| 4 | Revision History                                     | 8.2 Typical Application                              |              |

| 5 | Pin Configuration and Functions 4                    | 8.3 Do's and Don'ts                                  |              |

|   | _                                                    | 8.4 Initialization Set Up                            | . 47         |

| 6 | Specifications                                       | 9 Power Supply Recommendations                       |              |

|   | 6.2 ESD Ratings                                      | 10 Layout                                            |              |

|   | 6.3 Recommended Operating Conditions                 | 10.1 Layout Guidelines                               |              |

|   | 6.4 Thermal Information                              | 10.2 Layout Example                                  | . 48         |

|   | 6.5 Electrical Characteristics                       | 10.3 Solder Profile                                  |              |

|   | 6.6 Recommended SMBus Interface AC Timing            | 11 Device and Documentation Support                  | 50           |

|   | Specifications                                       | 11.1 Device Support                                  |              |

|   | 6.7 Serial Parallel Interface (SPI) Bus Interface AC | 11.2 Documentation Support                           |              |

|   | Timing Specifications 12                             | 11.3 Receiving Notification of Documentation Updates | s <b>5</b> 0 |

|   | 6.8 Typical Characteristics                          | 11.4 Community Resources                             |              |

| 7 | Detailed Description 14                              | 11.5 Trademarks                                      |              |

|   | 7.1 Overview 14                                      | 11.6 Electrostatic Discharge Caution                 | 50           |

|   | 7.2 Functional Block Diagram                         | 11.7 Glossary                                        |              |

|   | 7.3 Feature Description                              | 12 Mechanical, Packaging, and Orderable              |              |

|   | 7.4 Device Functional Modes25                        | Information                                          | <b>.</b> 50  |

|   | 7.5 Programming                                      |                                                      |              |

|   |                                                      |                                                      |              |

## 4 Revision History

| CI | nanges from Revision D (December 2017) to Revision E                                                                                                                          | Page |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Changed the note under Float(Default) setting from: Reserved to: Power down until valid signal detected                                                                       | 5    |

| •  | Changed MISO pin I/O description from 3-Level back to 2-Level                                                                                                                 | 5    |

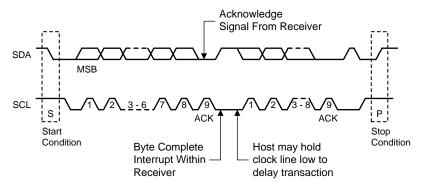

| •  | Changed the Acknowledge (ACK) graphic text from: Clock Line Held Low by Receiver While Interrupt is Serviced to Host may held clock line low to delay transaction             |      |

| •  | Changed Channel Register 0x80 default from: 0xXX to: 0x20                                                                                                                     | 43   |

| •  | Changed the OUT0_VOD bit 7 default from x to 0                                                                                                                                | 43   |

| •  | Changed the bit description for the OUT0_VOD bits 7-3 from: drv_0_sel_vod[3:0] default value may change from part to part to: drv_0_sel_vod[3:0] is typically 42 mV per step. | 43   |

| •  | Changed the OUT0_VOD bit 6 default from x to 0                                                                                                                                | 43   |

| •  | Changed the OUT0_VOD bit 5 default from x to 1                                                                                                                                | 43   |

| •  | Changed the OUT0_VOD bit 4 default from x to 0                                                                                                                                | 43   |

| CI | nanges from Revision C (December 2016) to Revision D                                                                                                                          | Page |

| •  | Changed Channel Register 0x80 default value from 0101 0100'b to XXXX 0000'b                                                                                                   | 43   |

| CI | nanges from Revision B (February 2016) to Revision C                                                                                                                          | Page |

| •  | Changed MISO pin I/O description from 2-Level to 3-Level                                                                                                                      | 5    |

| •  | Added test conditions to the source transmit differential launch amplitude parameters                                                                                         | 7    |

| •  | Changed OUT0 VOD_Scaling_PD description for bits 7 through 4                                                                                                                  | 43   |

| C | nanges from Revision A (March 2015) to Revision B                                                                                                                     | Page |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Changed ESD Ratings for Human-body model (HBM) From: ±2500 To ±4500                                                                                                   | 7    |

| • | Added typical launch amplitude for 20 and 30 inch FR4 trace in the Recommended Operating Conditions                                                                   | 7    |

| • | Added new Note to the <i>Electrical Characteristics:</i> "ATE Production tested using DC method"                                                                      | 9    |

| • | Changed the V <sub>VOD_OUT0</sub> row information and values in the <i>Electrical Characteristics</i>                                                                 | 9    |

| • | Added MAX value of 45 ps to T <sub>R_F_OUT0</sub> in the <i>Electrical Characteristics</i>                                                                            | 10   |

| • | Changed the TYP value From: 900 To: 950 ps, Added MIN and MAX values to T <sub>R_F_OUT0</sub> (270 Mbps) in the<br>Electrical Characteristics                         | 10   |

| • | Changed the TYP value to 3 ps, Added MAX value of 18 ps to T <sub>R_F_OUTO_delta</sub> in the <i>Electrical Characteristics</i>                                       | 10   |

| • | Changed the TYP value From: 100 To: 72 ps, Added MAX value of 500 ps to T <sub>R_F_OUT0_delta</sub> (270 Mbps) in the<br>Electrical Characteristics                   | 10   |

| • | Changed the V <sub>OVR UDR SHOOT</sub> row information and values in the <i>Electrical Characteristics</i>                                                            | 10   |

| • | Added t <sub>SU</sub> MIN = 4 ns in the Serial Parallel Interface (SPI) Bus Interface AC Timing Specifications <sup>(4)(5)</sup>                                      | 12   |

| • | Added t <sub>H</sub> MIN = 4 ns in the Serial Parallel Interface (SPI) Bus Interface AC Timing Specifications <sup>(4)(5)</sup>                                       | 12   |

| • | Added t <sub>SSSu</sub> MIN = 14 ns, Changed TYP value From: 14 To: 18 ns in the <i>Serial Parallel Interface (SPI) Bus Interface AC Timing Specifications</i> (4)(5) |      |

| • | Added t <sub>SSh</sub> MIN = 4 ns in the Serial Parallel Interface (SPI) Bus Interface AC Timing Specifications <sup>(4)(5)</sup>                                     | 12   |

| • | Added Selective Data Rate Lock in Application and Implementation section.                                                                                             | 47   |

#### Changes from Original (February 2015) to Revision A

Page

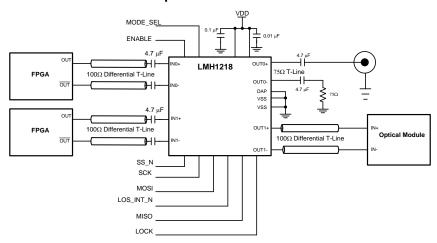

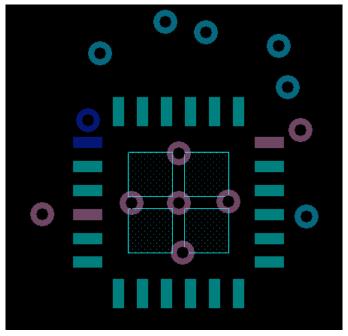

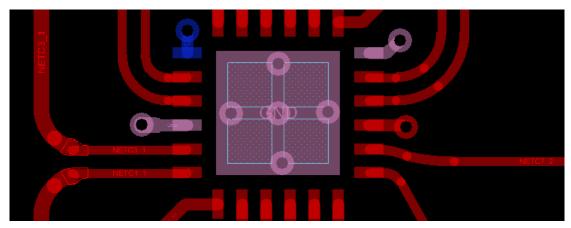

## 5 Pin Configuration and Functions

### Pin Descriptions – SPI Mode/ Mode\_SEL = 1 $k\Omega$ to VDD

|                            | i iii Des | criptions – or r                          | Pin Descriptions – SPI Mode/ Mode_SEL = 1 KΩ to VDD  PIN                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|----------------------------|-----------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NAME                       | NO.       | TYPE                                      | DESCRIPTION                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| CONTROL/INDICATOR I/O      | 110.      |                                           |                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| ENABLE                     | 6         | Input, 4-Level                            | Powers down device when pulled low 1 k $\Omega$ to VDD:  • Power down until valid signal detected Float( <b>Default</b> ):  • Power down until valid signal detected 20 k $\Omega$ to GND:  • Reserved 1 k $\Omega$ to GND:  • Power down including signal detects and Reset Registers upon power-up |  |  |  |  |  |  |

| LOCK                       | 16        | Output, 2.5-V<br>LVCMOS, 2-Level          | Indicates CDR lock detect status High:  CDR locked Low: CDR not locked                                                                                                                                                                                                                               |  |  |  |  |  |  |

| LOS_INT_N                  | 13        | Output,<br>LVCMOS Open-<br>Drain, 2-Level | Programmable Interrupt caused by change in LOS, violation of internal eye monitor threshold, or change in lock. External 4.7-k $\Omega$ pullup resistor i required. This pin is 3.3-V LVCMOS tolerant.                                                                                               |  |  |  |  |  |  |

| MISO                       | 15        | Output, 2.5-V<br>LVCMOS, 2-Level          | SPI Master Input / Slave Output. LMH1218 SPI data transmit                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| MODE_SEL                   | 1         | Input, 4-Level                            | Determines Device Configuration: SPI or SMBus 1 kΩ to VDD: • SPI mode. See <i>Initialization Set Up</i> .                                                                                                                                                                                            |  |  |  |  |  |  |

| MOSI                       | 4         | Input, 2-Level                            | SPI Master Output / Slave Input. LMH1218 SPI data receive                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| RESERVED                   | 5, 17, 18 | _                                         | No Connect                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| SCK                        | 3         | Input, 2.5V<br>LVCMOS, 2-Level            | SPI serial clock input                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| SMPTE_10GbE                | 14        |                                           | No Connect                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| SS_N                       | 2         | Input, 2-Level                            | SPI Slave Select. This pin has internal pullup                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| HIGH-SPEED DIFFERENTIAL I/ | O         |                                           |                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| INO+                       | 11        | Input, Analog                             | Inverting and noninverting differential inputs. An on-chip 100-Ω terminating                                                                                                                                                                                                                         |  |  |  |  |  |  |

| INO-                       | 12        | Input, Analog                             | resistor connects IN0+ to IN0 Inputs require 4.7-µF, AC-coupling capacitors.                                                                                                                                                                                                                         |  |  |  |  |  |  |

| IN1+                       | 8         | Input, Analog                             | Inverting and noninverting differential inputs. An on-chip $100-\Omega$ terminating                                                                                                                                                                                                                  |  |  |  |  |  |  |

| IN1-                       | 9         | Input, Analog                             | resistor connects IN1+ to IN1 Inputs require 4.7-µF, AC-coupling capacitors.                                                                                                                                                                                                                         |  |  |  |  |  |  |

| OUT0+                      | 20        | Output, 75-Ω CML<br>Compatible            | Inverting and noninverting 75-Ω outputs. An on-chip 75-Ω terminating                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| OUT0-                      | 19        | Output, 75-Ω CML<br>Compatible            | resistor connects OUT0+ and OUT0- to VDD. Outputs require 4.7-µF, ACcoupling capacitors                                                                                                                                                                                                              |  |  |  |  |  |  |

| OUT1+                      | 23        | Output, Analog                            | Inverting and noninverting differential outputs. An on-chip 100- $\Omega$                                                                                                                                                                                                                            |  |  |  |  |  |  |

| OUT1-                      | 22        | Output, Analog                            | terminating resistor connects OUT1+ to OUT1 Outputs require 4.7-μF, AC-coupling capacitors                                                                                                                                                                                                           |  |  |  |  |  |  |

| POWER                      |           |                                           |                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

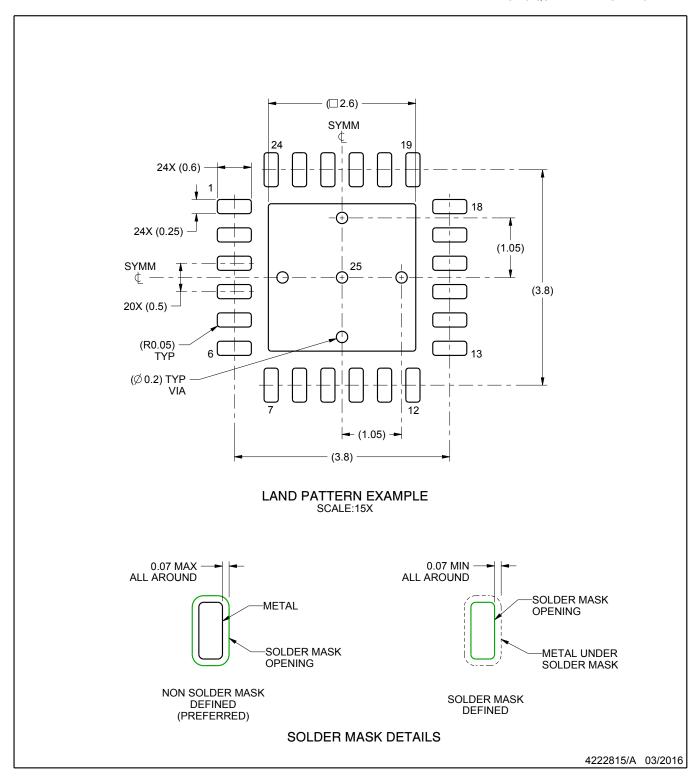

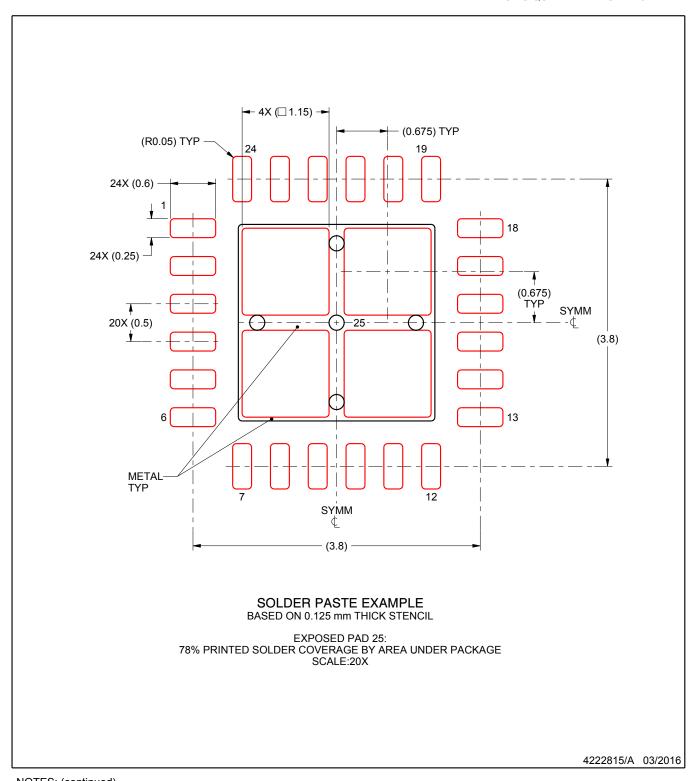

| DAP                        | _         | Ground                                    | Exposed DAP, connect to GND using at least 5 vias (see package drawing)                                                                                                                                                                                                                              |  |  |  |  |  |  |

|                            | 7, 21     | 2.5-V Supply                              | 2.5 V ± 5%                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| VDD                        | 1, 21     | 2.0 v Oupply                              | 2.0 1 2 0 70                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

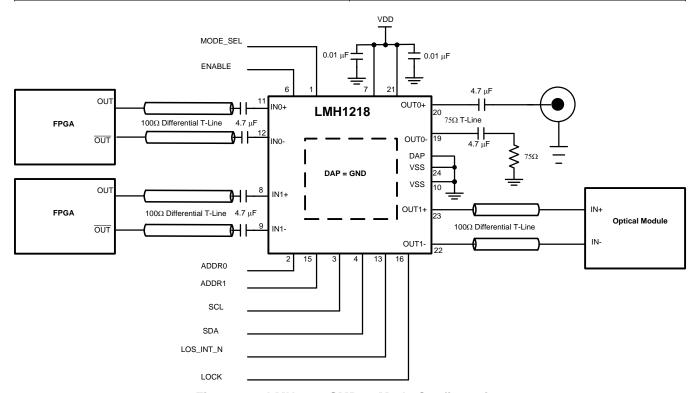

### Pin Descriptions – SMBUS Mode/ MODE\_SEL = 1 $k\Omega$ to GND

| PIN                     | III DC3011 | Priorio OMBO                              | JS MODE_SEL = 1 KQ to GND                                                                                                                                                                                                                                                       |  |  |

|-------------------------|------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                    | NO.        | TYPE                                      | DESCRIPTION                                                                                                                                                                                                                                                                     |  |  |

| ADDR0                   | 2          |                                           | 4-level strap pins used to set the SMBus address of the device. The pin state is read on power-up. The multi-level nature of these pins allows for 16 unique device addresses. Note the SMBus section for further details. The four strap options include: 1 k $\Omega$ to VDD: |  |  |

| ADDR1                   | 15         | Input, 4-Level                            | • Represents logic state 11'b Float( <b>Default</b> ): Represents logic state 10'b 7-bits SMBus address = $0x17$ $20 \text{ k}\Omega$ to GND: • Represents logic state $01$ 'b $1 \text{ k}\Omega$ to GND: • Represents logic state $00$ 'b                                     |  |  |

| ENABLE                  | 6          | Input, 4-Level                            | Powers down device when pulled low 1 k $\Omega$ to VDD:  • Power down until valid signal detected Float( <b>Default</b> ): Reserved 20 k $\Omega$ to GND:  • Reserved 1 k $\Omega$ to GND:  • Power down including signal detects and Reset Registers upon power-up             |  |  |

| LOCK                    | 16         | Output, 2.5-V<br>LVCMOS, 2-Level          | Indicates CDR lock Status High: CDR locked Low: CDR not locked                                                                                                                                                                                                                  |  |  |

| LOS_INT_N               | 13         | Output, LVCMOS<br>Open-Drain, 2-<br>Level | Programmable Interrupt caused by change in LOS, violation of internal eye monitor threshold, change in lock. External 4.7-k $\Omega$ pullup resistor is required. This pin is 3.3-V LVCMOS tolerant.                                                                            |  |  |

| MODE_SEL                | 1          | Input, 4-Level                            | Determines Device Configuration: SPI or SMBus 1 k $\Omega$ to GND: SMBUS mode. See <i>Initialization Set Up</i>                                                                                                                                                                 |  |  |

| RESERVED                | 5, 17, 18  | _                                         | No Connect                                                                                                                                                                                                                                                                      |  |  |

| SCL                     | 3          | Input, 2-Level                            | SMBus clock input / open-drain. External $2\text{-}k\Omega$ to $5\text{-}k\Omega$ pullup resistor is required as per SMBus interface standard. This pin is 3.3-V LVCMOS tolerant.                                                                                               |  |  |

| SDA                     | 4          | I/O, Open-Drain, 2-<br>Level              | SMBus data input / open-drain. External $2\text{-}k\Omega$ to $5\text{-}k\Omega$ pullup resistor is required as per SMBus interface standard. This pin is 3.3-V LVCMOS tolerant.                                                                                                |  |  |

| SMPTE_10GbE             | 14         |                                           | No Connect                                                                                                                                                                                                                                                                      |  |  |

| HIGH-SPEED DIFFERENTIAL | 1/0        |                                           | T=                                                                                                                                                                                                                                                                              |  |  |

| DAP                     | _          | Ground                                    | Exposed DAP, connect to GND using at least 5 vias (see package drawing)                                                                                                                                                                                                         |  |  |

| INO+                    | 11         | Input, Analog                             | Inverting and noninverting differential inputs. An on-chip 100-Ω terminating                                                                                                                                                                                                    |  |  |

| INO-                    | 12         | Input, Analog                             | resistor connects IN0+ to IN0 Inputs require 4.7-µF, AC-coupling capacitors.                                                                                                                                                                                                    |  |  |

| IN1+                    | 8          | Input, Analog                             | Inverting and noninverting differential inputs. An on-chip 100-Ω terminating                                                                                                                                                                                                    |  |  |

| IN1-                    | 9          | Input, Analog                             | resistor connects IN0+ to IN0–. Inputs require 4.7-μF, AC-coupling capacitors.                                                                                                                                                                                                  |  |  |

| OUT0+                   | 20         | Output, 75-Ω CML<br>Compatible            | Inverting and noninverting 75-Ω outputs. An on-chip 75-Ω terminating resistor connects OUT0+ and OUT0– to VDD. Outputs require 4.7-μF, AC-                                                                                                                                      |  |  |

| OUT0-                   | 19         | Output, 75-Ω CML<br>Compatible            | coupling capacitors                                                                                                                                                                                                                                                             |  |  |

| OUT1+                   | 23         | Output, Analog                            |                                                                                                                                                                                                                                                                                 |  |  |

| OUT1-                   | 22         | Output, Analog                            | terminating resistor connects OUT1+ to OUT1 Outputs require 4.7-µF, AC-coupling capacitors                                                                                                                                                                                      |  |  |

| VDD                     | 7, 21      | 2.5-V Supply                              | 2.5 V ± 5%                                                                                                                                                                                                                                                                      |  |  |

| VSS                     | 10, 24     | Ground                                    | Ground                                                                                                                                                                                                                                                                          |  |  |

### 6 Specifications

### 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                     | MIN  | MAX       | UNIT |

|---------------------------------------------------------------------|------|-----------|------|

| Supply voltage (VDD to GND)                                         | -0.5 | 2.75      | V    |

| 3.3-V open-drain I/O input and output voltage (SDA, SCL, LOS_INT_N) | -0.5 | 4.0       | V    |

| 2.5-V LVCMOS input and output voltage                               | -0.5 | VDD + 0.5 | V    |

| High-speed input voltage                                            | -0.5 | VDD + 0.5 | V    |

| High-speed input current                                            | -30  | 30        | mA   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                    |               |                                                                     | VALUE | UNIT |

|--------------------|---------------|---------------------------------------------------------------------|-------|------|

| V                  | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±4500 | \/   |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1500 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions. Pins listed as ±2000 V may actually have higher performance.

### 6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

| Over operating free-air temperature i                                   | 3 (                                                       | MIN   | TYP | MAX   | UNIT       |

|-------------------------------------------------------------------------|-----------------------------------------------------------|-------|-----|-------|------------|

| Supply voltage <sup>(1)</sup>                                           |                                                           | 2.375 | 2.5 | 2.625 | V          |

| 3.3-V open-drain I/O input and output vo                                | ltage                                                     | 3     | 3.3 | 3.6   | V          |

| Supply noise, 50 Hz to 10 MHz, sinusoic                                 | al <sup>(1)</sup>                                         |       | 40  |       | $mV_{P-P}$ |

| Ambient temperature                                                     |                                                           | -40   | 25  | 85    | °С         |

| Source transmit differential launch amplitude (up to 20 inch FR4 trace) | PRBS15, EQ, and PLL pathological pattern. Reg 0x03 = 0x50 | 300   | 500 | 1000  | $mV_{P-P}$ |

| Source transmit differential launch amplitude (up to 35 inch FR4 trace) | PRBS15, EQ, and PLL pathological pattern. Reg 0x03 = 0x95 | 600   | 700 | 800   | $mV_{P-P}$ |

| SMBus clock frequency (SCL) in SMBus                                    | slave mode                                                |       | 100 | 400   | kHz        |

| SMBUS SDA and SCL voltage level                                         |                                                           |       |     | 3.6   | V          |

| SPI clock frequency                                                     |                                                           |       | 10  | 20    | MHz        |

<sup>(1)</sup> DC plus AC power should not exceed these limits.

#### 6.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)(2)</sup>             | RTW (WQFN) | UNIT |  |

|-----------------------|----------------------------------------------|------------|------|--|

|                       | THE MINE INC.                                | 24 PINS    | OMI  |  |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 34         | °C/W |  |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 31.4       | °C/W |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 11.8       | °C/W |  |

| ΨͿΤ                   | Junction-to-top characterization parameter   | 0.3        | °C/W |  |

| ΨЈВ                   | Junction-to-board characterization parameter | 11.8       | °C/W |  |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.7        | °C/W |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions. Pins listed as ±1000 V may actually have higher performance.

<sup>(2)</sup> No heat sink is assumed for these estimations. Depending on the application, a heat sink, faster air flow, and/or reduced ambient temperature ( < 85°C) may be required in order to maintain the maximum junction temperature specified in *Electrical Characteristics*.

### 6.5 Electrical Characteristics

Over operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                   | TEST CONDITIONS                                                                                     | MIN         | TYP     | MAX | UNIT |

|-------------------|-----------------------------|-----------------------------------------------------------------------------------------------------|-------------|---------|-----|------|

| POWER             |                             |                                                                                                     |             |         |     |      |

|                   |                             | Locked 75 $\Omega$ OUT0 only (800 mVpp), EOM powered down                                           |             | 300     |     | mW   |

| PD                | Power dissipation           | Locked OUT1 only (600 mVpp, diff), EOM powered down                                                 |             | 195     |     | mW   |

|                   |                             | Transient power during CDR lock acquisition, 75 $\Omega$ OUT0 and OUT1 powered up, EOM powered down |             | 400     | 500 | mW   |

|                   | Power dissipation in force  | EQ bypass, OUT0<br>720mVpp, OUT1 600mVpp<br>IN0 to OUT0 and OUT1 or<br>IN1 to OUT0 and OUT1         |             | 195     |     | mW   |

| PD_RAW            | RAW mode (CDR bypass)       | IN0 to OUT0, OUT1 powered down                                                                      |             | 160     |     | mW   |

|                   |                             | IN1 to OUT1, OUT0 powered down                                                                      |             | 80      |     | mW   |

| 4-LEVEL INP       | UT AND 2.5 V LVCMOS DC SPEC |                                                                                                     |             |         | T   |      |

| V <sub>IH</sub>   | High level input voltage    | 4-level input (MODE_SEL, ADDR0/1, ENABLE pins)                                                      | 0.9         | 5 × VDD |     | V    |

| $V_{IF}$          | Float level input voltage   | 4-level input (MODE_SEL, ADDR0/1, ENABLE pins)                                                      | 0.6         | 7 × VDD |     | V    |

| V <sub>I20K</sub> | 20K to GND input voltage    | 4-level input (MODE_SEL, ADDR0/1, ENABLE pins)                                                      | 0.3         | 3 × VDD |     | V    |

| $V_{IL}$          | Low level input voltage     | 4-level input (MODE_SEL, ADDR0/1, ENABLE pins)                                                      |             | 0.1     |     | V    |

| $V_{OH}$          | High level output voltage   | IOH = -3 mA                                                                                         | 2           |         |     | V    |

| V <sub>OL</sub>   | Low level output voltage    | IOL = 3 mA                                                                                          |             |         | 0.4 | V    |

|                   |                             | V <sub>input</sub> = VDD<br>SPI Mode: LVCMOS<br>(SPI_SCK, SPI_SS_N)<br>pins                         |             |         | 15  | μΑ   |

| I <sub>IH</sub>   | Input high leakage current  | SMBus Mode: LVCMOS<br>(SMB_SDA, SMB_SCL)<br>pins                                                    |             |         | 15  | μΑ   |

|                   |                             | SMBus Mode: 4-Levels (ADDR0, ADDR1) pins                                                            | 20          | 44      | 80  | μΑ   |

|                   |                             | 4-Levels (MODE_SEL,<br>ENABLE) pins                                                                 | 20          | 44      | 80  | μΑ   |

|                   |                             | Vinput = GND<br>SPI Mode: LVCMOS<br>(SPI_MOSI, SPI_SCK)<br>pins                                     | <b>–1</b> 5 |         |     | μΑ   |

|                   | hand house to be a some     | Vinput = GND<br>SPI Mode: LVCMOS<br>(SPI_SS_N) pins                                                 | -37         |         |     | μА   |

| I <sub>IL</sub>   | Input low leakage current   | SMBus Mode: LVCMOS<br>(SMB_SDA, SMB_SCL<br>pins                                                     | -15         |         |     | μΑ   |

|                   |                             | SMBus Mode: 4-Levels (ADDR0, ADDR1) pins                                                            | -160        | -93     | -40 | μΑ   |

|                   |                             | 4-Levels (MODE_SEL,<br>ENABLE) pins                                                                 | -160        | -93     | -40 | μΑ   |

### **Electrical Characteristics (continued)**

Over operating free-air temperature range (unless otherwise noted)

| P                                                       | PARAMETER                                                           | TEST CONDITIONS                                                | MIN  | TYP  | MAX        | UNIT       |

|---------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------|------|------|------------|------------|

| 3.3-V TOLERANT                                          | LVCMOS / LVTTL DC SPECI                                             |                                                                |      |      |            |            |

| V <sub>IH25</sub>                                       | High level input voltage                                            | 2.5-V Supply Voltage                                           | 1.75 |      | 3.6        | V          |

| V <sub>IL</sub>                                         | Low level input voltage                                             | 117                                                            | GND  |      | 0.8        | V          |

| V <sub>OL</sub>                                         | Low level output voltage                                            | IOL = 1.25 mA                                                  |      |      | 0.4        | V          |

| Ін                                                      | Input high current                                                  | VIN = 2.5 V, VDD = 2.5 V                                       | 20   |      | 40         | μА         |

| lL                                                      | Input low current                                                   | VIN = GND, VDD = 2.5 V                                         | -10  |      | 10         | μΑ         |

| SIGNAL DETECT                                           |                                                                     | 1                                                              |      |      |            |            |

|                                                         |                                                                     | 11.88 Gbps, SMPTE (EQ, PLL) Pathological Pattern               |      | 26   |            | $mV_{P-P}$ |

| S <sub>DH</sub>                                         | Signal detect (default)<br>Assert threshold level <sup>(1)(2)</sup> | 10.3125 Gbps, 1010 Clock<br>Pattern, no media                  |      | 30   |            | $mV_{P-P}$ |

|                                                         |                                                                     | 10.3125 Gbps, PRBS31<br>Pattern                                |      | 21   |            | $mV_{P-P}$ |

|                                                         | O'constitute of (defeed)                                            | 11.88 Gbps, SMPTE (EQ, PLL) Pathological Patterns              |      | 20   |            | $mV_{P-P}$ |

| Signal detect (default)  De-assert threshold  level (1) | 10.3125 Gbps, 1010 Clock<br>Pattern                                 |                                                                | 15   |      | $mV_{P-P}$ |            |

|                                                         |                                                                     | 10.3125 Gbps, PRBS31<br>Pattern                                |      | 12   |            | $mV_{P-P}$ |

| HIGH-SPEED REC                                          | CEIVE RX INPUTS (IN_n+, IN_                                         | _n_)                                                           |      |      |            |            |

| R_RD                                                    | DC Input differential resistance                                    |                                                                | 75   | 100  | 125        | Ω          |

| RL <sub>RX-SDD</sub>                                    | Input differential return loss <sup>(3)</sup>                       | Measured with the device powered up. SDD11 10 MHz to 2 GHz     |      | -14  |            | dB         |

|                                                         |                                                                     | SDD11 2 GHz to 6 GHz                                           |      | -6.5 |            | dB         |

|                                                         |                                                                     | SDD11 6 GHz to 12 GHz                                          |      | -6.5 |            | dB         |

| RL <sub>RX-SCD</sub>                                    | Differential to common mode Input conversion (3)                    | Measure with the device powered up.SCD11, 10 MHz to 12 GHz     |      | -20  |            | dB         |

| HIGH-SPEED OU                                           | TPUTS (OUT_n+, OUT_n-)                                              |                                                                |      |      |            |            |

| V <sub>VOD_OUT1</sub>                                   | Output differential voltage (3) (4)                                 | Default setting, 8T clock pattern                              | 400  | 600  | 700        | $mV_{P-P}$ |

| V <sub>VOD_OUT1_DE</sub>                                | De-emphasis Level                                                   | VOD = 600 mV, maximum<br>De-Emphasis with 16T<br>clock pattern |      | -9   |            | dB         |

| V <sub>VOD_OUT1_CLK</sub>                               | Clock output differential voltage                                   | 2.97 GHz,1.485 GHz, 297<br>MHz, and 270 MHz                    |      | 560  |            | $mV_{P-P}$ |

| / <sub>VOD_OUT0</sub>                                   | Output single ended voltage at OUT0+ with OUT0- terminated (5) (4)  | Default setting                                                | 720  | 778  | 880        | $mV_{P-P}$ |

| R <sub>DIFF_OUT1</sub>                                  | DC output differential resistance                                   |                                                                |      | 100  |            | Ω          |

| R <sub>DIFF_OUT0</sub>                                  | DC output single-ended resistance                                   |                                                                |      | 75   |            | Ω          |

| T <sub>R F OUT1</sub>                                   | Output rise/fall time                                               | Full Slew Rate, 20% to 80% using 8T Pattern                    |      | 45   |            | ps         |

<sup>(1)</sup> Data with extraordinarily long periods of high-frequency 1010 data, and for long, lossy channels, the signal amplitude at the input to the device may be severely attenuated by the channel and may fall below the signal detect assert and/or de-assert thresholds.

<sup>(2)</sup> The voltage noise on the receiver inputs which has an amplitude larger than the signal detect assert threshold may trigger a signal detect assert condition

<sup>3)</sup> These limits are ensured by bench characterization and are not production tested.

<sup>(4)</sup> Dependent on board layout. Characterization data was measured with LMH1218EVM evaluation board

<sup>(5)</sup> ATE Production tested using DC method. Apply differential DC signal at the input and measure OUT0P amplitude. OUT0N terminated in 75 Ω.

## **Electrical Characteristics (continued)**

Over operating free-air temperature range (unless otherwise noted)

| P                           | ARAMETER                                                         | TEST CONDITIONS                                                                           | MIN | TYP     | MAX  | UNIT                 |

|-----------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----|---------|------|----------------------|

|                             |                                                                  | 11.88 Gbps                                                                                |     | 35      | 45   | ps                   |

|                             |                                                                  | 5.94 Gbps                                                                                 |     | 35      | 45   | ps                   |

| T <sub>R_F_OUT0</sub>       | Output rise/fall time,<br>PRBS10 <sup>(3)(4)</sup>               | 2.97 Gbps                                                                                 |     | 35      | 45   | ps                   |

|                             | 110010                                                           | 1.485 Gbps                                                                                |     | 35      | 45   | ps                   |

|                             |                                                                  | 270 Mbps                                                                                  | 400 | 950     | 1500 | ps                   |

|                             |                                                                  | 11.88 Gbps                                                                                |     | 3       | 18   | ps                   |

|                             |                                                                  | 5.94 Gbps                                                                                 |     | 3       | 18   | ps                   |

| T <sub>R_F_OUT0_delta</sub> | Output rise/fall time mismatch (3) (4)                           | 2.97 Gbps                                                                                 |     | 3       | 18   | ps                   |

| N_1 _0010_della             | mismatori                                                        | 1.485 Gbps                                                                                |     | 3       | 18   | ps                   |

|                             |                                                                  | 270 Mbps                                                                                  |     | 72      | 500  | ps                   |

| V <sub>OVR_UDR_</sub> SHOOT | Output overshoot, undershoot <sup>(3)</sup> (4)                  | 12G/6G/3G/HD/SD<br>Measured with 8T pattern                                               |     | 2.4%    | 3.4% |                      |

| V <sub>DC_OFFSET</sub>      | DC offset <sup>(3)</sup>                                         | 12G/6G/3G/HD/SD                                                                           |     | ±0.2    |      | V                    |

| V <sub>DC_WANDER</sub>      | DC wander <sup>(3)</sup>                                         | 12G/6G/3G/HD/SD EQ<br>Pathological                                                        |     | 20      |      | mV                   |

|                             |                                                                  | S22 5 MHz to 1.485 GHz                                                                    |     | < -15   |      | dB                   |

| RL <sub>OUT0_S22</sub>      | OUT0 single-ended 75-Ω                                           | S22 1.485 GHz to 3 GHz                                                                    |     | < -10   |      | dB                   |

|                             | return loss (3)(4)(6)                                            | S22 3 GHz to 6 GHz                                                                        |     | < -7    |      | dB                   |

|                             |                                                                  | S22 6 GHz to 12 GHz                                                                       |     | < -4    |      | dB                   |

|                             |                                                                  | SDD22 10 MHz - 2 GHz                                                                      |     | -20     |      | dB                   |

| RL <sub>OUT1_SDD22</sub>    | OUT1 differential 100- $\Omega$ return loss <sup>(3)(4)(7)</sup> | SDD22 2 GHz - 6 GHz                                                                       |     | -17     |      | dB                   |

|                             |                                                                  | SDD22 6 GHz - 11.1 GHz                                                                    |     | -14     |      | dB                   |

| DI.                         | OUT1 common-mode 50-                                             | SCC22 10 MHz - 4.75<br>GHz                                                                |     | -11     |      | dB                   |

| RL <sub>OUT1_SCC22</sub>    | $\Omega$ return loss <sup>(3)(4)(7)</sup>                        | SCC22 4.75 GHz - 11.1<br>GHz                                                              |     | -12     |      | dB                   |

| V <sub>VCM_OUT1_NOISE</sub> | AC common-mode voltage noise (3)(4)                              | VOD = 0.6 Vpp, DE = 0dB,<br>PRBS31, 10.3125 Gbps                                          |     | 8       |      | ${\rm mV}_{\rm RMS}$ |

| T <sub>RCK_LATENCY</sub>    | Latency reclocked                                                | Reclocked Data                                                                            | 1.5 | UI +195 |      | ps                   |

| T <sub>RAW_LATENCY</sub>    | Latency CDR bypass                                               | Raw Data                                                                                  |     | 230     |      | ps                   |

| TRANSMIT OUTP               | UT JITTER SPECIFICATIONS                                         |                                                                                           |     |         |      |                      |

| A <sub>J_OUT0</sub>         | Alignment jitter (3)(4)                                          | OUT0, PRBS15, 11.88<br>Gbps                                                               |     | 0.18    |      | UI                   |

| $T_{ m J\_OUT1}$            | Total jitter (1E-12) <sup>(3)(4)</sup>                           | OUT1, PRBS15 10.3125<br>Gbps                                                              |     | 0.12    |      | UI                   |

| R <sub>J_OUT1</sub>         | Random jitter (rms)                                              | OUT1, PRBS15, 10.3125<br>Gbps                                                             |     | 0.38    |      | ps <sub>RMS</sub>    |

| D <sub>J_OUT1</sub>         | Deterministic jitter                                             | OUT1, PRBS15, 10.3125<br>Gbps                                                             |     | 7       |      | ps <sub>P-P</sub>    |

| O <sub>J_OUT1_RAW</sub>     | Deterministic jitter                                             | OUT1, RAW MODE (CDR bypass) PRBS15, 11.88 Gbps, 35 inch FR4 trace, EQ=0x95, VID = 800mVpp |     | 25      |      | ps <sub>P-P</sub>    |

Output return loss is dependent on board design, this is measured with the LMH1218EVM evaluation board Measure with the device powered up and outputs a clock signal.

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

## **Electrical Characteristics (continued)**

Over operating free-air temperature range (unless otherwise noted)

|                        | PARAMETER                      | TEST CONDITIONS                                                                                                                                                 | MIN TYP          | MAX | UNIT |

|------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|------|

| CLOCK DATA             | RECOVERY                       |                                                                                                                                                                 |                  | -   |      |

|                        |                                | ST-2082 (proposed) (8)                                                                                                                                          | 11.88,<br>11.868 |     | Gbps |

|                        |                                | ST-2081 (proposed) <sup>(8)</sup>                                                                                                                               | 5.94, 5.934      |     | Gbps |

| D                      |                                | SMPTE 424 <sup>(8)</sup>                                                                                                                                        | 2.97, 2.967      |     | Gbps |

| D <sub>DATA_RATE</sub> |                                | SMPTE 292 <sup>(8)</sup>                                                                                                                                        | 1.485,<br>1.4835 |     | Gbps |

|                        |                                | SMPTE 259M <sup>(8)</sup>                                                                                                                                       | 270              |     | Mbps |

|                        |                                | 10 GbE <sup>(8)</sup>                                                                                                                                           | 10.3125          |     | Gbps |

|                        |                                | Measured with 0.2UI S <sub>J</sub> at 10.3125 Gbps                                                                                                              | 8                |     | MHz  |

|                        |                                | Measured with 0.2UI S <sub>J</sub> at 11.88 Gbps                                                                                                                | 13               |     | MHz  |

| _                      | DI L benduidth et 2 dD         | Measured with 0.2UI S <sub>J</sub> at 5.94 Gbps                                                                                                                 | 7                |     | MHz  |

| P <sub>PLL_BW</sub>    | PLL bandwidth at –3 dB         | Measured with 0.2UI S <sub>J</sub> at 2.97 Gbps                                                                                                                 | 5                |     | MHz  |

|                        |                                | Measured with 0.2UI S <sub>J</sub> at 1.485 Gbps                                                                                                                | 3                |     | MHz  |

|                        |                                | Measured with 0.2UI S <sub>J</sub> at 270 Mbps                                                                                                                  | 1                |     | MHz  |

| $J_TOL$                | Total input jitter tolerance   | $TJ = D_J + R_J + S_J$ ,<br>$D_J + R_J = 0.15 UI$<br>$S_J/P_J$ , low to high upward<br>sweep (10 kHz to 80 MHz)                                                 | 0.65             |     | UI   |

| T <sub>LOCK</sub>      | Lock time <sup>(3)(9)</sup>    | From signal detected to<br>the lock asserted,<br>HEO/VEO lock monitor<br>disable, same setting for<br>11.88G, 5.94G, 2.97G,<br>1.485G and 270-MHz data<br>rates | <5               |     | ms   |

| T <sub>TEMP_LOCK</sub> | CDR lock with temperature ramp | Temperature Lock Range,<br>5°C per minute ramp up<br>and down, –40°C to 85°C<br>operating range                                                                 | 125              |     | °C   |

<sup>(8)</sup> Data rate tolerance is within ±1000 ppm

(9) The total CDR lock time depends on number of rate settings enabled and application data rate

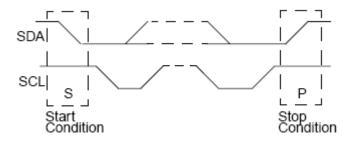

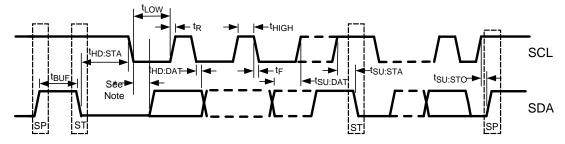

# 6.6 Recommended SMBus Interface AC Timing Specifications (1)(2)(3)

Over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                                                                        | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---------------------|--------------------------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| f <sub>SMB</sub>    | Bus operating frequency                                                                          | MODE_SEL = 0    | 10  | 100 | 400 | kHz  |

| t <sub>BUF</sub>    | Bus free time between stop and start condition                                                   |                 | 1.3 |     |     | μS   |

| t <sub>HD:STA</sub> | Hold time after (repeated) start condition<br>After this period, the first clock is<br>generated |                 | 0.6 |     |     | μS   |

| t <sub>SU:STA</sub> | Repeated start condition setup time                                                              |                 | 0.6 |     |     | μS   |

| t <sub>SU:STO</sub> | Stop condition setup time                                                                        |                 | 0.6 |     |     | μS   |

| t <sub>HD:DAT</sub> | Data hold time                                                                                   |                 | 0   |     |     | ns   |

| t <sub>SU:DAT</sub> | Data setup time                                                                                  |                 | 100 |     |     | ns   |

| $t_{LOW}$           | Clock low period                                                                                 |                 | 1.3 |     |     | μS   |

| t <sub>HIGH</sub>   | Clock high period                                                                                |                 | 0.6 |     | 50  | μS   |

| t <sub>F</sub>      | SDA fall time read operation                                                                     |                 |     |     | 300 | ns   |

| t <sub>R</sub>      | SDA rise time read operation                                                                     |                 |     |     | 300 | ns   |

- SMBus operation is available 20ms after power up These specifications support SMBus 2.0 specifications

- These Parameters are not production tested

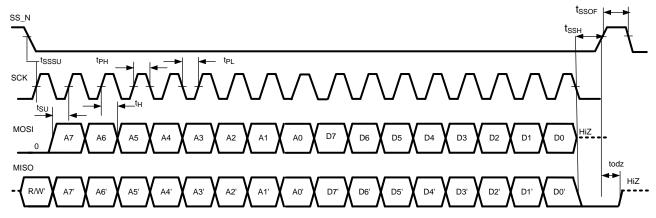

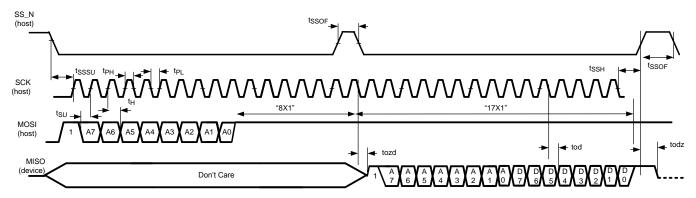

## 6.7 Serial Parallel Interface (SPI) Bus Interface AC Timing Specifications (1)(2)

Over operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                     | TEST<br>CONDITIONS | MIN | TYP                  | MAX | UNIT |

|-------------------|-------------------------------|--------------------|-----|----------------------|-----|------|

| f <sub>SCK</sub>  | SCK frequency                 | MODE_SEL = 1       |     | 10                   | 20  | MHz  |

| T <sub>SCK</sub>  | SCK period                    |                    | 50  |                      |     | ns   |

| t <sub>PH</sub>   | SCK pulse width high          |                    |     | $0.4 \times T_{SCK}$ |     | ns   |

| t <sub>PL</sub>   | SCK pulse width low           |                    |     | $0.4 \times T_{SCK}$ |     | ns   |

| t <sub>SU</sub>   | MOSI setup time               |                    | 4   | 4                    |     | ns   |

| t <sub>H</sub>    | MOSI hold time                |                    | 4   | 4                    |     | ns   |

| t <sub>SSSu</sub> | SS_N setup time               |                    | 14  | 18                   |     | ns   |

| t <sub>SSH</sub>  | SS_N hold time                |                    | 4   | 4                    |     | ns   |

| t <sub>SSOF</sub> | SS_N off time                 |                    |     | 1                    |     | μS   |

| t <sub>ODZ</sub>  | MISO driven to TRI-STATE time |                    |     | 20                   |     | ns   |

| t <sub>OZD</sub>  | MISO TRI-STATE-to-Driven time |                    |     | 10                   |     | ns   |

| t <sub>OD</sub>   | MISO output delay time        |                    |     | 15                   |     | ns   |

Typical values are parametric norms at VDD = 2.5 V, TA = 25°C, and recommended operating conditions at the time of product characterization. Typical values are not production tested.

These specifications support SPI 1.0 specifications.

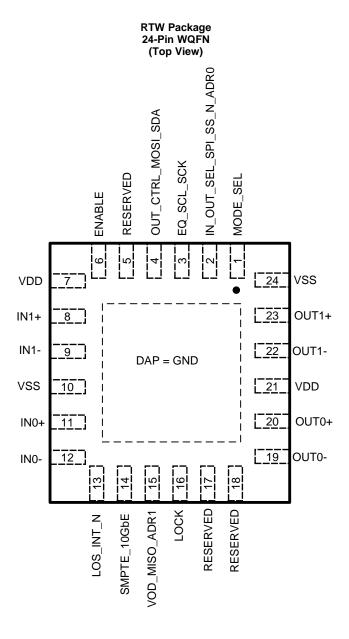

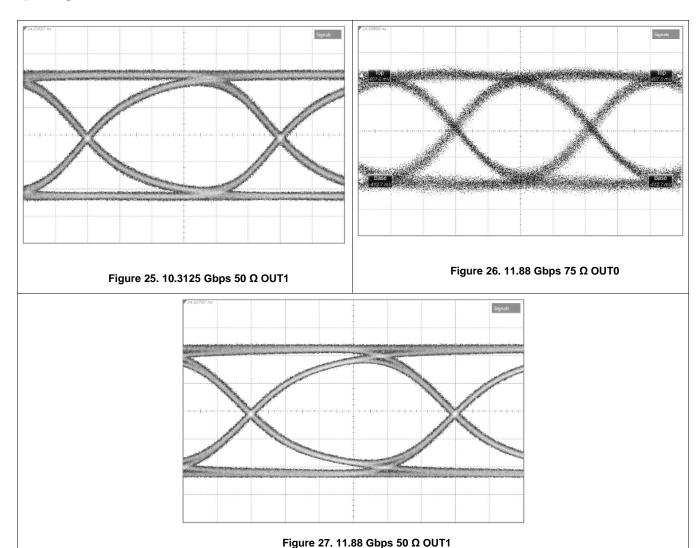

### 6.8 Typical Characteristics

Typical device characteristics at  $T_A = +25$ °C and VDD = 2.5 V, unless otherwise noted.

Copyright © 2015–2018, Texas Instruments Incorporated

Submit Documentation Feedback

### 7 Detailed Description

#### 7.1 Overview

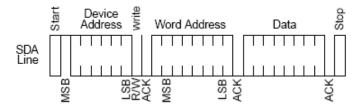

The LMH1218 is a 11.88Gbps/5.94Gbps/2.97Gbps/1.485Gbps/0.27Gbps/10GbE multi-rate serial digital video data cable driver with integrated reclocker intended for equalizing, reclocking, and driving data compatible to the SMPTE standards, proposed ST-2081/2, and 10GbE specifications. It is a 2-input, 2-output single-core chip, enabling 1:2 fan-out or 2:1 MUX operation. Each input has a  $100-\Omega$  continuous time linear equalizer (CTLE) at the front-end, intended to compensate for loss over STP coax, fiber, or FR-4 backplane. OUT1 is a  $100-\Omega$  driver compatible to 10GbE SFF-8431 optical module requirements. The LMH1218 OUT0 is a  $75-\Omega$  cable driver compatible to the SMPTE and proposed ST-2081/2 requirements.

The referenceless Clock-and-Data Recovery (CDR) circuit selects between the two inputs based on user choice. The reclocked output can be driven to one or two outputs. One of the outputs supports  $100-\Omega$  differential cable connection, while the other output can drive a  $75-\Omega$  SMPTE specified cable while meeting transmitter requirements as specified in SMPTE standard. The LMH1218 locks to all required SDI data rates, including 270Mbps, 1.485 Gbps, 1.4835 Gbps, 2.97 Gbps, 2.967 Gbps, 5.94 Gbps, 5.934 Gbps, 11.88 Gbps, and 11.868 Gbps as well as 10.3125 Gbps. The LMH1218 is assembled in a 4 mm × 4 mm 24-pin QFN package. The chip can be programmed using SPI or SMBus interface.

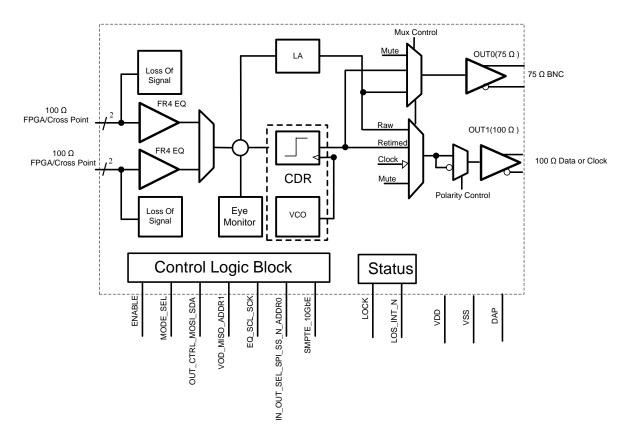

#### 7.2 Functional Block Diagram

#### 7.3 Feature Description

The LMH1218 data path consists of several key blocks as shown in the *Functional Block Diagram*. These key circuits are:

- Loss of Signal Detector

- Continuous Time Linear Equalizer (CTLE) for FR4 Compensation

- 2:1 Multiplexer/1:2 Fanout

- CDR

- Eye Monitor

- Differential Output Selection

- 75- $\Omega$  and 100- $\Omega$  Output Drivers

- SMBus/SPI Configuration

#### 7.3.1 Loss of Signal Detector

The LMH1218 supports two high speed differential input ports, with internal  $100-\Omega$  terminations. The inputs must be AC coupled. The external AC coupling capacitor value should take into account the pathological low frequency content. For most applications, the RC time constant of 4.7  $\mu$ F AC coupling capacitor plus the  $50-\Omega$  termination resistor is capable of handing the pathological video pattern's low frequency content.

The signal detect circuit is designed to assert when data traffic with a certain minimum amplitude is present at the input of the device. It is also designed to de-assert, or remain de-asserted, when there is noise below certain amplitude at the input to the device.

The LMH1218 has two signal detect circuits, one for each input. Each signal detect threshold can be set independently. By default, both signal detects are powered on. The user selects IN1 or IN0 through SMBus/SPI interface.

#### 7.3.2 Continuous Time Linear Equalizer (CTLE)

The LMH1218 has receive-side equalization, and a key part is the Continuous Time Linear Equalizer (CTLE). This circuit operates on the received differential signal and compensates for frequency-dependent loss due to the transmission media. The CTLE applies gain to the input signal. This gain varies over frequency: higher frequencies are boosted more than lower frequencies. The CTLE works to restore the input signal to full amplitude across a wide range of frequencies.

The CTLE consists of 4 stages with each stage having two boost control bits. This allows 256 different boost settings. CTLE boost levels are determined by summing the boost levels of the 4 stages. The CTLE is configured manually. Refer to *LMH1218 Programming Guide* (SNLU174) on how to quickly select the most appropriate CTLE boost setting.

There are two CTLEs, one for each input, INO and IN1. Only one CTLE is enabled at a time, according to the user input channel selection. If INO is selected, the CTLE for INO is powered on and the IN1 CTLE is powered off. The CTLE compensates for up to 27 dB of loss at 6 GHz. The CTLE is able to handle low loss channels without over-equalizing by bypassing the CTLE.

### **Feature Description (continued)**

#### 7.3.3 2:1 Multiplexer

A 2:1 input multiplexor connects IN0 and IN1 to the CDR. By default, IN0 is selected. To select IN1, the 2:1 multiplexer must be set. Refer to *LMH1218 Programming Guide* (SNLU174) for detailed settings.

#### 7.3.4 Clock and Data Recovery

By default, the equalized data is fed into the CDR for clock and data recovery. The CDR consists of a reference-less Phase Frequency Detector (PFD), Charge Pump (CP), Voltage Controlled Oscillator (VCO), and Output Data Multiplexer (Mux).

The inputs to the Phase and Frequency Detector (PFD) are the data after the CTLE as well as I and Q clocks from the VCO. The LMH1218 will attempt to lock to the incoming data by tuning the VCO to phase-lock to the incoming data rate.

The supported data rates are listed in the following table. Refer to *LMH1218 Programming Guide* (SNLU174) for further information on configuring the LMH1218 for different data rates.

| DATA RATE RANGE         | CDR MODE | COMMENT                              |

|-------------------------|----------|--------------------------------------|

| 11.88 Gbps, 11.868 Gbps | Enabled  |                                      |

| 5.94Gbps, 5.934 Gbps    | Enabled  |                                      |

| 2.97 Gbps, 2.967 Gbps   | Enabled  |                                      |

| 1.485 Gbps, 1.4835 Gbps | Enabled  |                                      |

| 270 Mbps                | Enabled  |                                      |

| 10.3125 Gbps            | Enabled  |                                      |

| 125 Mbps                | Disabled | At 125 Mbps device is in CDR bypass  |

| 1.25 Gbps               | Disabled | At 1.25 Gbps device is in CDR bypass |

|                         |          |                                      |

**Table 1. Supported Data Rates**

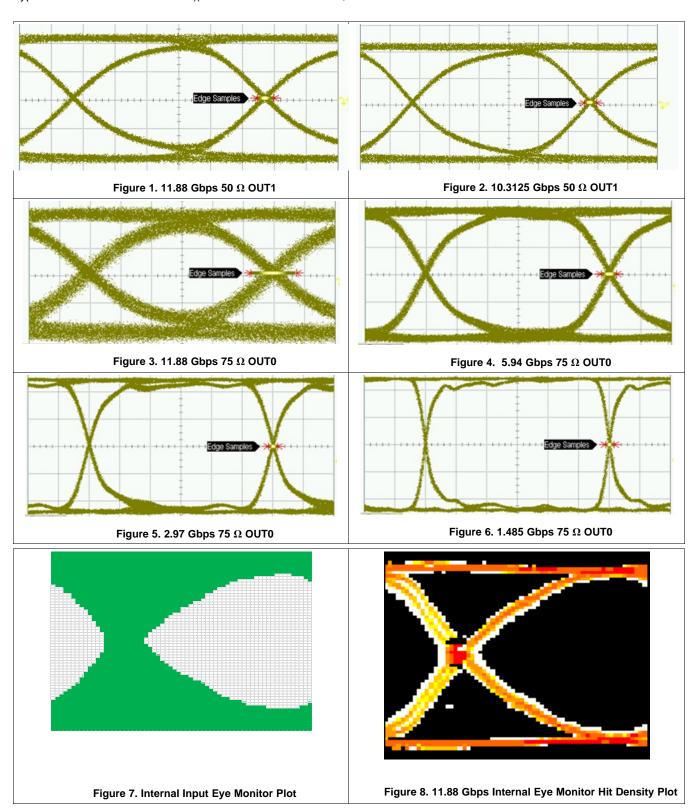

#### 7.3.5 Eye Opening Monitor (EOM)

The LMH1218 has an on-chip eye opening monitor (EOM) which can be used to analyze, monitor, and diagnose the performance of the link. The EOM operates on the post-equalized waveform, just prior to the data sampler. Therefore, it captures the effects of all the equalization circuits within the receiver before the data is reclocked. The EOM is operational for 1.485 Gbps and higher data rates.

The EOM monitors the post-equalized waveform in a time window that spans one unit intervals and a configurable voltage range that spans up to  $\pm 400$  mV differential. The time window and voltage range are divided into 64 steps, so the result of the eye capture is a 64 × 64 matrix of "hits," where each point represents a specific voltage and phase offset relative to the main data sampler. The number of "hits" registered at each point needs to be taken in context with the total number of bits observed at that voltage and phase offset in order to determine the corresponding probability for that point. The number of bits observed at each point is configurable.

A common measurement performed by the EOM is the horizontal and vertical eye opening. The horizontal eye opening (HEO) represents the width of the post-equalized eye at 0-V differential amplitude, measured in unit intervals or picoseconds. The vertical eye opening (VEO) represents the height of the post-equalized eye, measured midway between the mean zero crossing of the eye. This position in time approximates the CDR sampling phase.

The resulting  $64 \times 64$  matrix produced by the EOM can be processed by software and visualized in a number of ways. Two common ways to visualize this data are shown in Figure 7 and Figure 8. These diagrams depict examples of eye monitor plot implemented by software. The first plot is an example of using the EOM data to plot a basic eye using ASCII character, which can be useful for simple diagnostics software. The second plot shows the first derivative of the EOM data, revealing the density of hits and the actual waveforms and crossing that comprise the eye.

#### 7.3.6 Fast EOM

Fast EOM is a mechanism that provides an option to read out EOM through SPI/SMBus interfaces by reading the hits observed for each point of  $64 \times 64$  points matrix. Since SPI interface operates at faster clock rate than SMBus interface, the SPI master will have to wait until the EOM start bit, reg 0x24[0], goes low. This indicates EOM samples are available and the SPI master can proceed to read register 0x25 and 0x26. Refer to *LMH1218 Programming Guide* (SNLU174) for further details of Fast EOM operation.

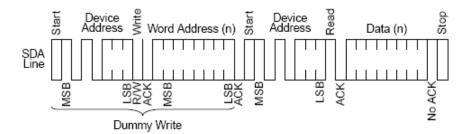

#### 7.3.6.1 SMBus Fast EOM Operation

In SMBus mode, the read on register 0x26 acts as an automatic trigger to read the next EOM count value:

- 1. Enable EOM (power it on), and set VRANGE=0. Write Reg 0x24[7] to 1 to turn on fast EOM

- 2. Do burst read register 0x25 and 0x26 (EOM hit count) and discard

- 3. Do burst read register 0x25 and 0x26 (EOM hit count) and discard

- 4. Do burst read register 0x25 and 0x26 (EOM hit count) and save

- 5. Perform Step 4 4095 times (64 x 64 cells)

#### 7.3.6.2 SPI Fast EOM Operation

To perform EOM calculation over SPI:

- 1. Enable EOM (power it on), and set VRANGE=0. Write Reg 0x24[7] to 1 to turn on fast EOM

- 2. Read Reg 0x26 to initialize. Discard read data

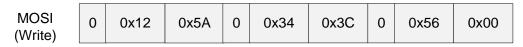

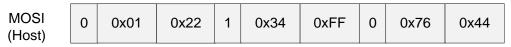

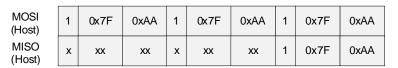

- 3. Read Reg 0x24[0] which is EOM start bit. Wait for this bit to go low