# 4.25-Gbps Transimpedance Amplifier With AGC and RSSI

Check for Samples: ONET4291T

### **FEATURES**

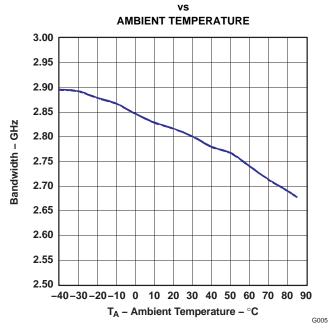

- 2.8-GHz Bandwidth

- 3.2-kΩ Differential Transimpedance

- Automatic Gain Control (AGC)

- 8.8-pA/√Hz Typical Input Referred Noise

- 2-mA<sub>p-p</sub> Maximum Input Current

- · Received Signal Strength Indication (RSSI)

- CML Data Outputs With On-Chip 50-Ω Back-Termination

- On-Chip Supply Filter Capacitor

- Single 3.3-V Supply

- Die Size: 0,78 × 1,18 mm

### **APPLICATIONS**

- SONET/SDH Transmission Systems at OC24 and OC48

- 4.25-Gbps, 2.125-Gbps, and 1.0625-Gbps

Fiber-Channel Receivers

- · Gigabit Ethernet Receivers

- PIN Preamplifier-Receivers

### DESCRIPTION

The ONET4291T is a high-speed transimpedance amplifier used in optical receivers with data rates up to 4.25 Gbps.

It features a low input referred noise, 2.8-GHz bandwidth, automatic gain control (AGC), 3.2-k $\Omega$  transimpedance, and received signal strength indication (RSSI).

The ONET4291T is available in die form and is optimized for use in a TO can.

The ONET4291T requires a single 3.3-V supply, and its power-efficient design typically dissipates less than 56 mW. The device is characterized for operation from -40°C to 85°C ambient temperature.

### **AVAILABLE OPTIONS**

| T <sub>A</sub> | DIE        |

|----------------|------------|

| -40°C to 85°C  | ONET4291TY |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SLLSE82 -APRIL 2011 \_\_\_\_\_\_ www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

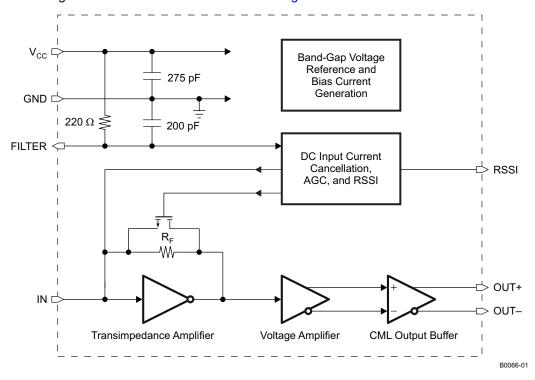

### **BLOCK DIAGRAM**

The ONET4291T is a high-performance, 4.25-Gbps transimpedance amplifier consisting of the signal path, supply filter, a control block for dc input current cancellation, automatic gain control (AGC), received signal strength indication (RSSI), and a band-gap voltage reference and bias current generation block.

The signal path comprises a transimpedance amplifier stage, a voltage amplifier, and a CML output buffer.

The on-chip filter circuit provides filtered  $V_{CC}$  for the photodiode and for the transimpedance amplifier. The dc input current cancellation and AGC use internal low-pass filters to cancel the dc current on the input and to adjust the transimpedance amplifier gain. Furthermore, circuitry to monitor the received signal strength is provided.

A simplified block diagram of the ONET4291T is shown in Figure 1.

Figure 1. Simplified Block Diagram of the ONET4291T

### **SIGNAL PATH**

The first stage of the signal path is a transimpedance amplifier that takes the photodiode current and converts it into a voltage signal.

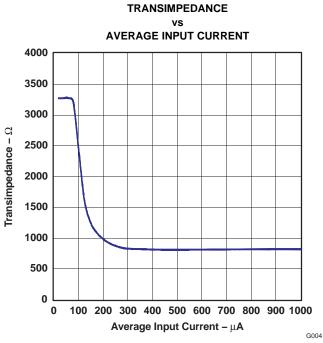

If the input signal current exceeds a certain value, the transimpedance gain is reduced by means of AGC circuitry.

The second stage is a voltage amplifier that provides additional gain and converts its single-ended input voltage into a differential data signal.

The third signal-path stage is the output buffer, which provides CML outputs with on-chip,  $50-\Omega$  back-termination to  $V_{CC}$ .

### **FILTER CIRCUITRY**

The filter pin provides filtered  $V_{CC}$  for the photodiode bias. The on-chip, low-pass filter for the photodiode  $V_{CC}$  is implemented using a filter resistor of 220  $\Omega$  and an internal 200-pF capacitor. The corresponding corner frequency is below 4 MHz.

The supply voltage for the whole amplifier is filtered by means of an on-chip, 275-pF capacitor as well, thus avoiding the necessity to use an external supply-filter capacitor.

### DC INPUT CURRENT CANCELLATION, AGC, AND RSSI

The voltage drop across the internal photodiode supply-filter resistor is monitored by means of a dc input current cancellation, AGC, and RSSI control circuit block.

If the dc input current exceeds a certain level, it is partially cancelled by means of a controlled current source. This measure keeps the transimpedance amplifier stage within sufficient operating point limits for optimum performance. Furthermore, disabling the dc input cancellation at low input currents leads to superior noise performance.

The AGC circuitry lowers the effective transimpedance feedback resistor  $R_F$  by means of a MOSFET device acting as a controlled shunt. This prevents the transimpedance amplifier from being overdriven at high input currents, which leads to improved jitter behavior within the complete input-current dynamic range. Because the voltage drop across the supply-filter resistor is sensed and used by the AGC circuit, the photodiode must be connected to a FILTER pad for the AGC to function correctly.

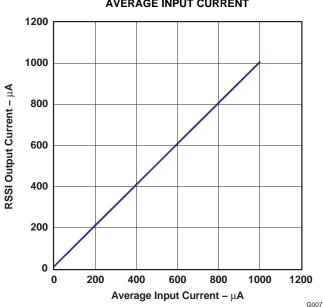

Finally, this circuit block senses the current through the filter resistor and generates a mirrored current, which is proportional to the input signal strength. The mirrored current is available at the RSSI output and must be sunk to ground (GND) using an external resistor. The RSSI gain can be adjusted by choosing the external resistor; however, for proper operation, ensure that the voltage at the RSSI pad never exceeds  $V_{CC} = 0.65 \text{ V}$ .

### BAND-GAP VOLTAGE AND BIAS GENERATION

The ONET4291T transimpedance amplifier is supplied by a single, 3.3-V supply voltage connected to the  $V_{CC}$  pad. This voltage is referred to GND.

On-chip band-gap voltage circuitry generates a supply-voltage-independent reference from which all other internally required voltages and bias currents are derived.

SLLSE82 -APRIL 2011 www.ti.com

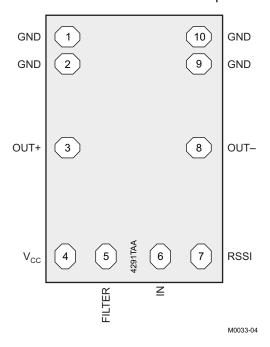

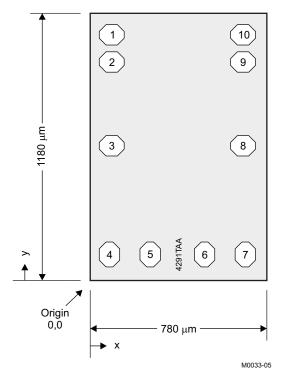

### **BOND PAD ASSIGNMENT**

The ONET4291T is available as a bare die. The locations of the bond pads are shown in the following figure.

### **BOND PAD DESCRIPTION**

| I               | PAD         | TVDE          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|-----------------|-------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME            | NO.         | TYPE          | JESCRIF HON                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| FILTER          | 5           | Analog        | Bias voltage for photodiode (cathode). This pads connects through an internal 220- $\Omega$ resistor to $V_{CC}$ and a 200-pF filter capacitor to ground (GND). The FILTER pad(s) must be connected to the photodiode for the AGC to function.                                                                                                                                                                                                                   |  |  |  |  |  |

| GND             | 1, 2, 9, 10 | Supply        | Circuit ground. All GND pads are connected on die. Bonding all pads is optional; however, for optimum performance a good ground connection is mandatory.                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| IN              | 6           | Analog input  | Data input to TIA (photodiode anode)                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| OUT+            | 3           | Analog output | Non-inverted data output. On-chip 50- $\Omega$ back-terminated to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| OUT-            | 8           | Analog output | Inverted data output. On-chip 50- $\Omega$ back-terminated to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| RSSI            | 7           | Analog output | Analog output current proportional to the input data amplitude. Indicates the strength of the received signal (RSSI). Must be sunk through an external resistor to ground (GND). The RSSI gain can be adjusted by choosing the external resistor; however, for proper operation, ensure that the voltage at the RSSI pad never exceeds $V_{\rm CC}-0.65$ V. If the RSSI feature is not used, this pad must be bonded to ground (GND) to ensure proper operation. |  |  |  |  |  |

| V <sub>CC</sub> | 4           | Supply        | 3.3-V, +10%/–12% supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1)

| V <sub>CC</sub>                                                                 | Supply voltage (2)                      | -0.3 V to 4 V     |

|---------------------------------------------------------------------------------|-----------------------------------------|-------------------|

| V <sub>FILTER</sub> , V <sub>OUT+</sub> , V <sub>OUT-</sub> , V <sub>RSSI</sub> | Voltage at FILTER, OUT+, OUT-, RSSI (2) | -0.3 V to 4 V     |

| I <sub>IN</sub>                                                                 | Current into IN                         | –0.7 mA to 2.5 mA |

| I <sub>FILTER</sub>                                                             | Current into FILTER                     | – 8 mA to 8 mA    |

| I <sub>OUT+</sub> , I <sub>OUT-</sub>                                           | Continuous current at outputs           | – 8 mA to 8 mA    |

| F0D                                                                             | ESD rating at all pins except IN (3)    | 1.5 kV (HBM)      |

| ESD                                                                             | ESD rating at IN (3)                    | 300 V (HBM)       |

| $T_{J,max}$                                                                     | Maximum junction temperature            | 125°C             |

| T <sub>stg</sub>                                                                | Storage temperature range               | –65°C to 85°C     |

| T <sub>A</sub>                                                                  | Operating free-air temperature range    | -40°C to 85°C     |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                                          |                                          | MIN | NOM | MAX | UNIT |

|------------------------------------------|------------------------------------------|-----|-----|-----|------|

| $V_{CC}$                                 | Supply voltage                           | 2.9 | 3.3 | 3.6 | V    |

| T <sub>A</sub>                           | Operating free-air temperature           | -40 |     | 85  | °C   |

| L <sub>FILTER</sub> ,<br>L <sub>IN</sub> | Wire-bond inductor at pins FILTER and IN |     |     | 8.0 | nΗ   |

| C <sub>PD</sub>                          | Photodiode capacitance                   |     | 0.2 |     | pF   |

### DC ELECTRICAL CHARACTERISTICS

over recommended operating conditions (unless otherwise noted). Typical values are at V<sub>CC</sub> = 3.3 V and T<sub>A</sub> = 25°C.

|                     | PARAMETER                    | TEST CONDITIONS                                   | MIN | TYP  | MAX  | UNIT |

|---------------------|------------------------------|---------------------------------------------------|-----|------|------|------|

| V <sub>CC</sub>     | Supply voltage               |                                                   | 2.9 | 3.3  | 3.6  | V    |

| I <sub>VCC</sub>    | Supply current               | Average photodiode current I <sub>PD</sub> = 0 mA | 11  | 17   | 25   | mA   |

| V <sub>IN</sub>     | Input bias voltage           |                                                   |     | 0.85 | 1.05 | V    |

| R <sub>OUT</sub>    | Output resistance            | Single-ended to V <sub>CC</sub>                   | 40  | 50   | 60   | Ω    |

| R <sub>FILTER</sub> | Photodiode filter resistance |                                                   |     | 220  |      | Ω    |

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

<sup>(3)</sup> For optimum high-frequency performance, the input pin has reduced ESD protection.

SLLSE82 - APRIL 2011 www.ti.com

### **AC ELECTRICAL CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted). Typical values are at  $V_{CC} = 3.3 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$ .

|                         | PARAMETER                             | TEST CONDITIONS                                              | MIN  | TYP   | MAX  | UNIT              |

|-------------------------|---------------------------------------|--------------------------------------------------------------|------|-------|------|-------------------|

| i <sub>IN-OVL</sub>     | AC input overload current             |                                                              | 2    |       |      | mA <sub>p-p</sub> |

| A <sub>RSSI</sub>       | RSSI gain                             | Resistive load to GND (1)                                    | 0.95 | 1     | 1.05 | A/A               |

|                         | RSSI output offset current (no light) |                                                              |      | 15    | 30   | μΑ                |

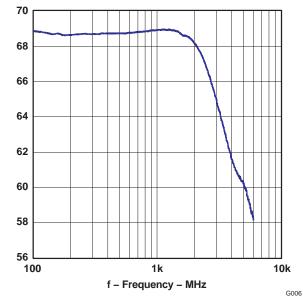

| Z <sub>21</sub>         | Small-signal transimpedance           | Differential output; input current $i_{IN} = 50 \mu A_{p-p}$ | 2300 | 3200  | 3900 | Ω<br>GHz          |

| f <sub>H,3dB</sub>      | Small-signal bandwidth                | $i_{IN} = 50 \ \mu A_{p-p}^{(2)}$                            | 2.2  | 2.8   |      |                   |

| f <sub>L,3dB</sub>      | Low-frequency, -3-dB bandwidth        | -3 dB, input current i <sub>IN</sub> < 50 μA <sub>p-p</sub>  |      | 40    | 70   | kHz               |

| f <sub>H,3dB,RSSI</sub> | RSSI bandwidth                        |                                                              |      | 3.5   |      | MHz               |

| i <sub>N-IN</sub>       | Input referred RMS noise              | 50 kHz–4 GHz <sup>(3)</sup>                                  |      | 465   | 590  | nA                |

|                         | Input referred noise current density  |                                                              |      | 8.8   |      | pA/√Hz            |

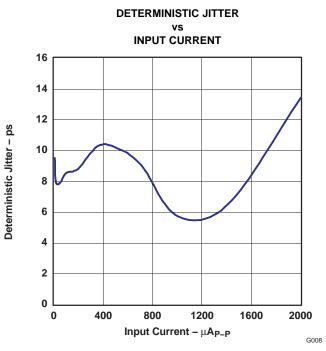

|                         |                                       | $i_{IN} = 50 \mu A_{p-p} (K28.5 \text{ pattern})^{-(4)}$     |      | 10    | 23   |                   |

| DJ                      | Data was in intin litter              | $i_{IN} = 100  \mu A_{p-p}  (K28.5  pattern)^{(4)}$          |      | 10    | 30   |                   |

|                         | Deterministic jitter                  | i <sub>IN</sub> = 1 mA <sub>p-p</sub> (K28.5 pattern)        |      | 8     | 28   | ps <sub>p-p</sub> |

|                         |                                       | i <sub>IN</sub> = 2 mA <sub>p-p</sub> (K28.5 pattern)        |      | 13 42 |      |                   |

| V <sub>OUT,D,MAX</sub>  | Maximum differential output voltage   | Input current i <sub>IN</sub> = 1 mA <sub>p-p</sub>          | 140  | 200   | 310  | $mV_{p-p}$        |

<sup>(1)</sup> The RSSI output is a current output, which requires a resistive load to ground (GND). The voltage gain can be adjusted for the intended application by choosing the external resistor. However, for proper operation of the ONET4291T, ensure that the voltage at RSSI never exceeds V<sub>CC</sub> – 0.65 V.

<sup>(2)</sup> The minimum small-signal bandwidth is specified over process corners, temperature, and supply voltage variation. The assumed photodiode capacitance is 0.2 pF. The bond-wire inductance is 0.8 nH. The small-signal bandwidth strongly depends on environmental parasitics. Careful attention to layout parasitics and external components is necessary to achieve optimal performance.

<sup>(3)</sup> Input referred RMS noise is (RMS output noise)/(gain @ 100 MHz). The maximum input referred noise is specified over process corners, temperature, and supply voltage variation.

<sup>(4)</sup> At small input currents a significant portion of the deterministic jitter (DJ) is caused by duty-cycle distortion (DCD) due to residual offset in the output signal. Because the TIA is not limiting, the DCD portion of the DJ is removed by the following limiting amplifier. The given maximum values include DCD as well as six-sigma margin.

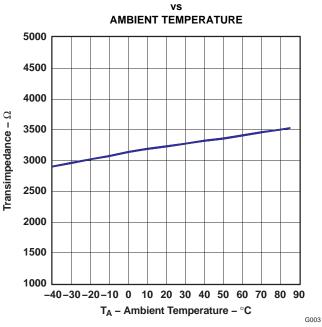

### **TYPICAL CHARACTERISTICS**

Typical operating condition is at  $V_{CC} = 3.3 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$ .

G001

### **UNFILTERER INPUT REFERRED NOISE AVERAGE INPUT CURRENT** 2400 2200 Input Referred Noise Current - nARMS 2000 1800 1600 1400 1200 1000 800 600 400 200 0 10 100 1k Average Input Current – $\mu$ A

### Figure 2.

# UNFILTERED INPUT REFERRED NOISE VS AMBIENT TEMPERATURE 800 700 600 400 300 -40-30-20-10 0 10 20 30 40 50 60 70 80 90 T<sub>A</sub> - Ambient Temperature - °C

Figure 3.

### **SMALL-SIGNAL TRANSIMPEDANCE**

Figure 4.

Figure 5.

### **TYPICAL CHARACTERISTICS (continued)**

Typical operating condition is at  $V_{CC} = 3.3 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$ .

### **SMALL-SIGNAL BANDWIDTH**

### Figure 6.

# Transimpedance – dBΩ

**SMALL-SIGNAL TRANSFER CHARACTERISTICS**

Figure 7.

## **RSSI OUTPUT CURRENT AVERAGE INPUT CURRENT** 1200

Figure 8.

Figure 9.

G010

Differential Output Voltage - 10 mV/Div

Differential Output Voltage - 50 mV/Div

www.ti.com SLLSE82 -APRIL 2011

### **TYPICAL CHARACTERISTICS (continued)**

Differential Output Voltage – 10 mV/Div

Differential Output Voltage - 50 mV/Div

Typical operating condition is at  $V_{CC} = 3.3 \text{ V}$  and  $T_A = 25 ^{\circ}\text{C}$ .

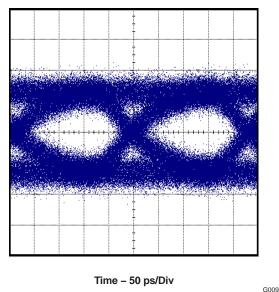

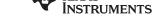

# OUTPUT EYE DIAGRAM AT 4.25 Gbps AND 10- $\mu$ A $_{p-p}$ INPUT CURRENT

### Figure 10.

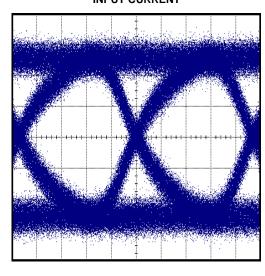

# OUTPUT EYE DIAGRAM AT 4.25 Gbps AND 20- $\mu$ A $_{p-p}$ INPUT CURRENT

Time - 50 ps/Div

### Figure 11.

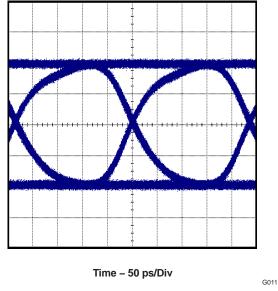

# OUTPUT EYE DIAGRAM AT 4.25 Gbps and 100- $\mu$ A $_{p-p}$ INPUT CURRENT

Figure 12.

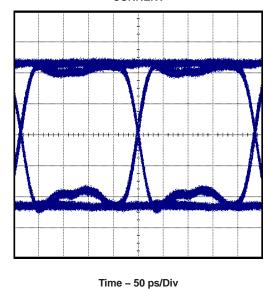

# OUTPUT EYE DIAGRAM AT 4.25 Gbps AND 1-mA $_{\rm p-p}$ INPUT CURRENT

Figure 13.

G012

SLLSE82 -APRIL 2011 www.ti.com

### TYPICAL CHARACTERISTICS (continued)

Typical operating condition is at  $V_{CC}$  = 3.3 V and  $T_A$  = 25°C.

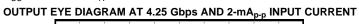

### APPLICATION INFORMATION

Figure 15 shows an application circuit for an ONET4291T being used in a typical fiber-optic receiver. The ONET4291T converts the electrical current generated by the PIN photodiode into a differential output voltage. The FILTER input provides a dc bias voltage for the PIN that is low-pass filtered by the combination of the internal  $220-\Omega$  resistor and 200-pF capacitor. Because the voltage drop across the  $220-\Omega$  resistor is sensed and used by the AGC circuit, the photodiode must be connected to a FILTER pad for the AGC to function correctly.

The RSSI output is used to mirror the photodiode average current and must be connected via a resistor to GND. The voltage gain can be adjusted for the intended application by choosing the external resistor. However, for proper operation of the ONET4291T, ensure that the voltage at RSSI never exceeds  $V_{CC}$  – 0.65 V. If the RSSI output is not used, it must be grounded.

The OUT+ and OUT- pads are internally terminated by  $50-\Omega$  pullup resistors to  $V_{CC}$ . The outputs must be ac-coupled (e.g., using C1 = C2 = 0.1  $\mu$ F) to the succeeding device. An additional capacitor,  $C_{NBW}$ , which is differentially connected between the two output pins OUT+ and OUT-, can be used to limit the noise bandwidth and thus optimize the noise performance.

Figure 15. Basic Application Circuit

### **ASSEMBLY RECOMMENDATIONS**

When packaging the ONET4291T, careful attention to parasitics and external components is necessary to achieve optimal performance. Recommendations that optimize performance include:

- 1. Minimize total capacitance on the IN pad by using a low-capacitance photodiode and paying attention to stray capacitances. Place the photodiode close to the ONET4291T die to minimize the bond wire length and thus the parasitic inductance.

- 2. Use identical termination and symmetrical transmission lines at the ac-coupled differential output pins OUT+ and OUT-. A differential capacitor C<sub>NBW</sub> can be used to limit the noise bandwidth.

- 3. Use short bond-wire connections for the supply terminals V<sub>CC</sub> and GND. Supply-voltage filtering is provided on-chip. Filtering can be improved by using an additional external capacitor.

SLLSE82 -APRIL 2011 www.ti.com

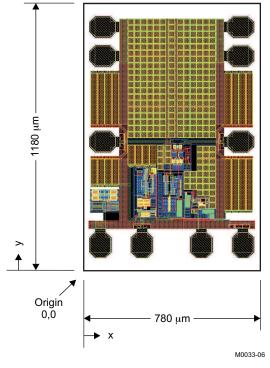

### **CHIP DIMENSIONS AND PAD LOCATIONS**

Overall chip dimensions and depiction of the bond-pad locations are given in Figure 16. Layout of the chip componentry is shown in Figure 17.

Figure 16. Chip Dimensions and Pad Locations

Figure 17. Chip Layout

| Table 1. Pad Locations and Descriptions for the ONET4291 |

|----------------------------------------------------------|

|----------------------------------------------------------|

| DAD | COORI         | DINATES | SYMBOL          | TYPE          | DESCRIPTION                 |  |

|-----|---------------|---------|-----------------|---------------|-----------------------------|--|

| PAD | <b>x (µm)</b> | y (µm)  | STMBOL          | ITPE          | DESCRIPTION                 |  |

| 1   | 100           | 1063    | GND             | Supply        | Circuit ground              |  |

| 2   | 100           | 938     | GND             | Supply        | Circuit ground              |  |

| 3   | 100           | 570     | OUT+            | Analog output | Non-inverted data output    |  |

| 4   | 90            | 127     | V <sub>cc</sub> | Supply        | 3.3-V supply voltage        |  |

| 5   | 265           | 127     | FILTER Analog   |               | Bias voltage for photodiode |  |

| 6   | 515           | 127     | IN              | Analog input  | Data input to TIA           |  |

| 7   | 690           | 127     | RSSI            | Analog output | RSSI output signal          |  |

| 8   | 680           | 570     | OUT-            | Analog output | Inverted data output        |  |

| 9   | 680           | 938     | GND             | Supply        | Circuit ground              |  |

| 10  | 680           | 1063    | GND             | Supply        | Circuit ground              |  |

### **DIE INFORMATION**

Die size: 1180  $\mu$ m × 780  $\mu$ m Die thickness: 8 mils (203  $\mu$ m) Pad metallization: 99.5% Al, 0.5% Cu Pad size: octagonal pads 120  $\mu$ m × 100  $\mu$ m Passivation composition: 6000-Å silicon nitride

Backside contact: none

Die ID: 4291TAA

### **TO46 LAYOUT EXAMPLES**

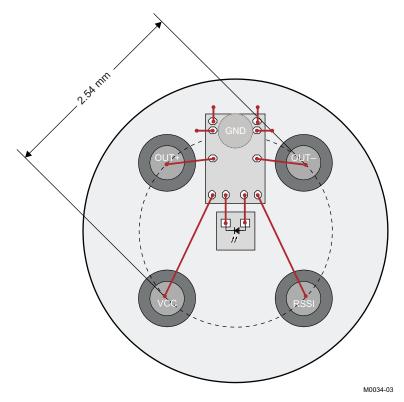

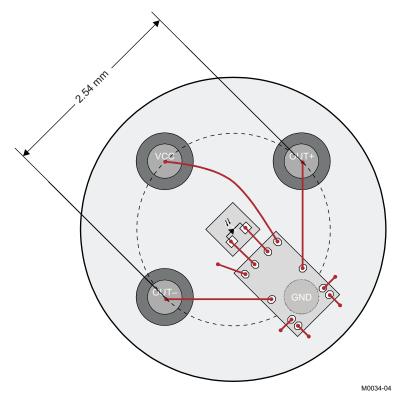

Examples for layouts (top view) in 5-pin and 4-pin TO46 headers are given in Figure 18 and Figure 19, respectively.

Figure 18. TO46 5-Pin Layout Example Using the ONET4291T

Figure 19. TO46 4-Pin Layout Example Using the ONET4291T

### PACKAGE OPTION ADDENDUM

24-Apr-2019

### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package | Pins | Package | Eco Plan | Lead/Ball Finish | MSL Peak Temp | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|---------|----------|------------------|---------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)      | (6)              | (3)           |              | (4/5)          |         |

| ONET4291TY       | ACTIVE | DIESALE      | Y       | 0    | 340     | TBD      | Call TI          | Call TI       | -40 to 85    |                | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated