#### 1 Introduction

#### 1.1 Features

- Highest-Performance Fixed-Point Digital Signal Processors (DSPs)

- 2-ns Instruction Cycle Time

- 500-MHz Clock Rate

- Eight 32-Bit Instructions/Cycle

- 28 Operations/Cycle

- 4000 MIPS

- Fully Software Compatible With C62x™

- C6414/15/16 Devices Pin Compatible

- VelociTI.2™ Extensions to VelociTI™

Advanced Very Long Instruction Word (VLIW)

TMS320C64x™ DSP Core

- Eight Highly Independent Functional Units With VelociTI.2 Extensions With Six ALUs and Two Multipliers

- Nonaligned Load-Store Architecture

- 64 32-Bit General-Purpose Registers

- Instruction Packing Reduces Code Size

- All Instructions Conditional

- Instruction Set Features

- Byte-Addressable (8-/16-/32-/64-Bit Data)

- 8-Bit Overflow Protection

- Bit-Field Extract, Set. Clear

- Normalization, Saturation, Bit Counting

- VelociTI.2 Increased Orthogonality

- Viterbi Decoder Coprocessor (VCP) (C6416)

- Supports Over 500 7.95-Kbps Adaptive Multi-Rate (AMR)

- Programmable Code Parameters

- Turbo Decoder Coprocessor (TCP) (C6416)

- Supports up to Six 2-Mbps 3GPP (Six Iterations)

- Programmable Turbo Code and Decoding Parameters

- L1/L2 Memory Architecture

- 128K-Bit (16K-Byte) L1P Program Cache

- 128K-Bit (16K-Byte) L1D Data Cache

- 8M-Bit (1024K-Byte) L2 Unified Mapped RAM/Cache

- Two External Memory Interfaces (EMIFs) for

- 1280M-Byte Addressable External Memory

- Enhanced Direct Memory Access (EDMA)

Controller (64 Independent Channels)

- Host-Port Interface (HPI)

- User-Configurable Bus Width (32/16 Bit)

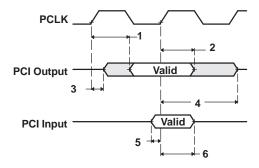

- 32-Bit/33-MHz, 3.3-V PCI Master/Slave Interface Conforms to PCI Specification 2.2 (C6415/C6416)

- Three PCI Bus Address Registers

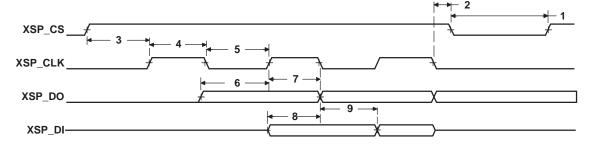

- Four-Wire Serial EEPROM Interface

- PCI Interrupt Request Under DSP Program Control

- DSP Interrupt Via PCI I/O Cycle

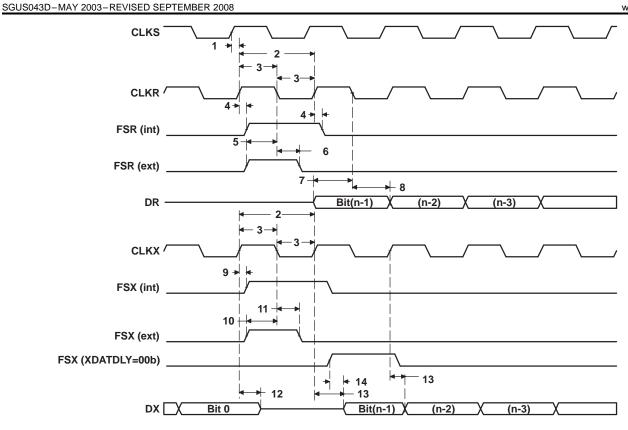

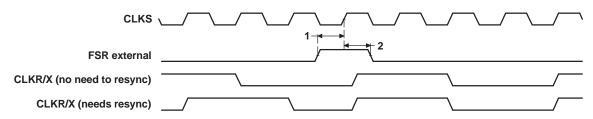

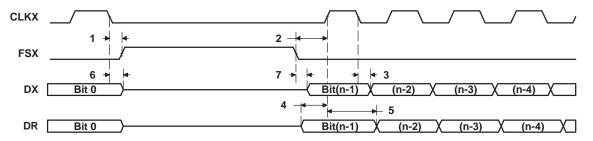

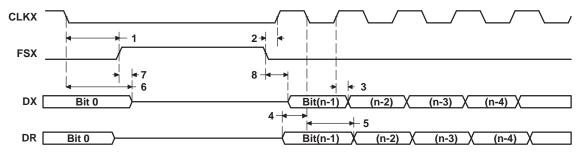

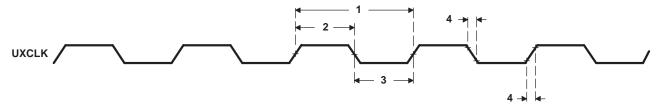

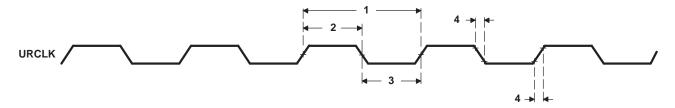

- Three Multichannel Buffered Serial Ports (McBSPs)

- Direct Interface to T1/E1, MVIP, and SCSA Framers

- Up to 256 Channels Each

- ST Bus Switching, AC97 Compatible

- Serial Peripheral Interface (SPI) Compatible (Motorola)

- Three 32-Bit General-Purpose Timers

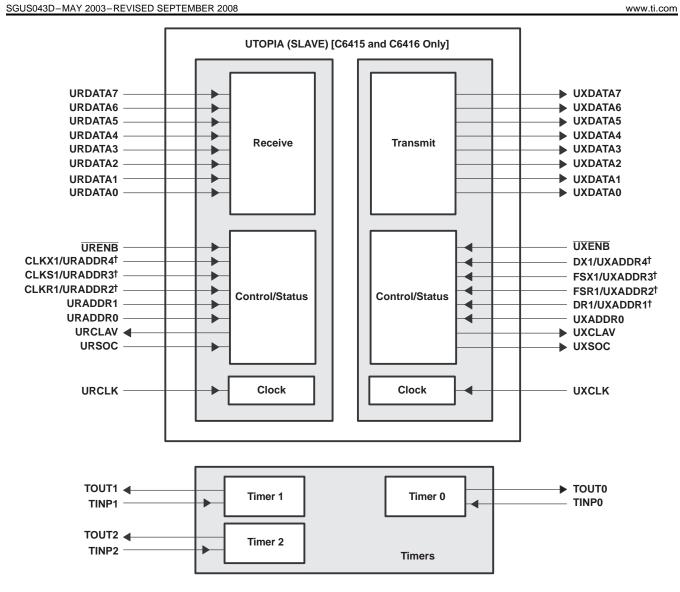

- Universal Test and Operations Physical Layer (PHY) Interface for ATM (UTOPIA) (C6415/C6416)

- UTOPIA Level-2 Slave ATM Controller

- 8-Bit Transmit and Receive Operations up to 50 MHz per Direction

- User-Defined Cell Format up to 64 Bytes

- 16 General-Purpose I/O (GPIO) Pins

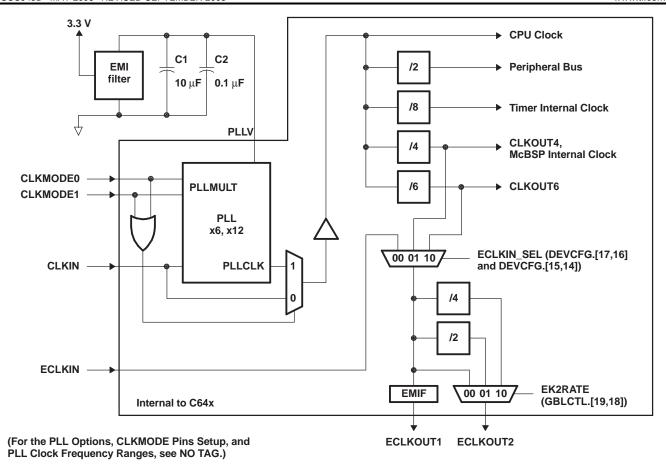

- Flexible Phase-Locked Loop (PLL) Clock Generator

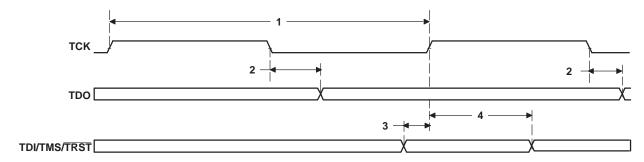

- IEEE Std 1149.1 (JTAG<sup>(1)</sup>) Boundary Scan Compatible

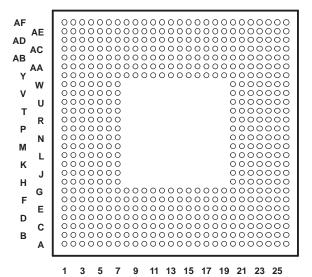

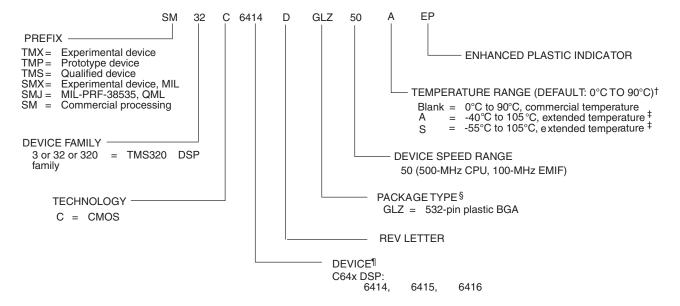

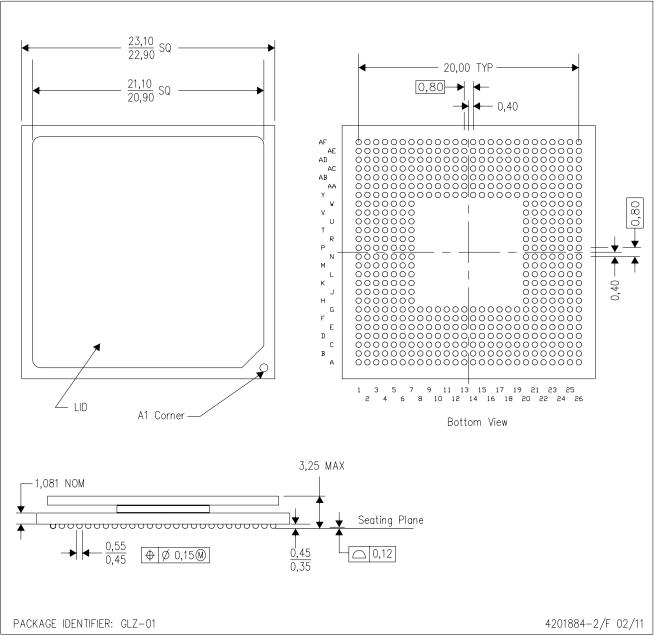

- 532-Pin Ball Grid Array (BGA) Package (GLZ Suffix), 0.8-mm Ball Pitch

- 0.13-μm/6-Level Metal Process (CMOS)

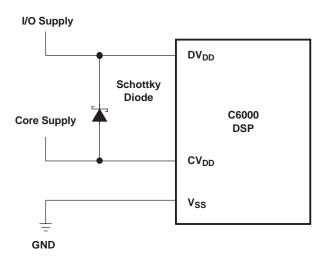

- 3.3-V I/Os, 1.25-V Internal (500 MHz)

- (1) IEEE Std 1149.1-1990 Standard Test-Access Port and Boundary Scan Architecture

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this document.

SGUS043D-MAY 2003-REVISED SEPTEMBER 2008

www.ti.com

#### 1.2 SUPPORTS DEFENSE, AEROSPACE, AND MEDICAL APPLICATIONS

- **Controlled Baseline**

- One Assembly/Test Site

- One Fabrication Site

- Available in A-Version (-40°C/105°C) and S-Version (-55°C/105°C) Temperature

#### Ranges (2)

- **Extended Product Life Cycle**

- **Extended Product-Change Notification**

- **Product Traceability**

- (2) S-Version currently available for C6415 only. Additional custom temperature ranges available upon request.

## 1.3 Description

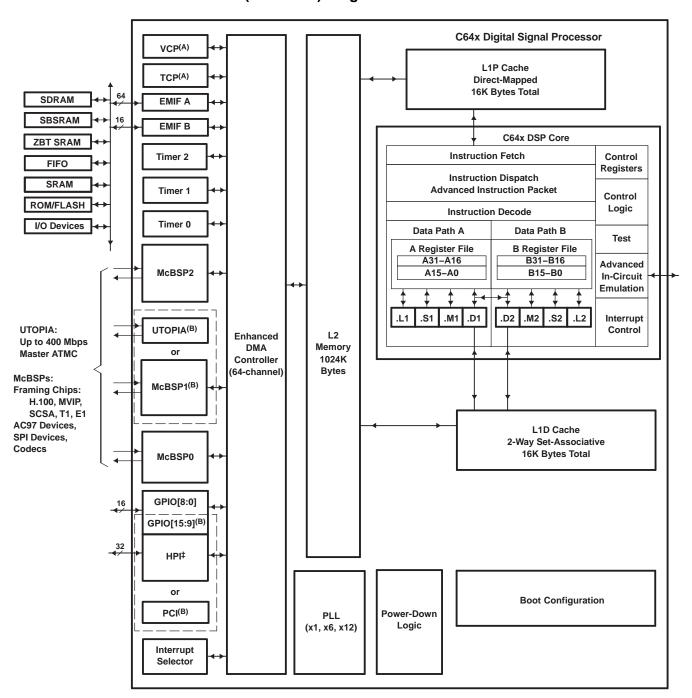

The TMS320C64x<sup>™</sup> DSPs (including the SM320C6414-EP, SM320C6415-EP, and SM320C6416-EP devices) are the highest-performance fixed-point DSP generation in the TMS320C6000™ DSP platform. The SM320C64x<sup>™</sup> (C64x<sup>™</sup>) device is based on the second-generation, high-performance, advanced VelociTI™ very-long-instruction word (VLIW) architecture (VelociTI.2™) developed by Texas Instruments (TI), making these DSPs an excellent choice for multichannel and multifunctional applications. The C64x™ is a code-compatible member of the C6000™ DSP platform.

With performance of up to 4000 million instructions per second (MIPS) at a clock rate of 500 MHz, the C64x devices offer cost-effective solutions to high-performance DSP programming challenges. The C64x DSPs possess the operational flexibility of high-speed controllers and the numerical capability of array processors. The C64x DSP core processor has 64 general-purpose registers of 32-bit word length and eight highly independent functional units - 2 multipliers for a 32-bit result and 6 arithmetic logic units (ALUs) - with VelociTI.2 extensions. The VelociTI.2 extensions in the eight functional units include new instructions to accelerate the performance in key applications and extend the parallelism of the VelociTI architecture. The C64x can produce four 32-bit multiply-accumulates (MACs) per cycle for a total of 2400 million MACs per second (MMACS), or eight 8-bit MACs per cycle for a total of 4800 MMACS. The C64x DSP also has application-specific hardware logic, on-chip memory, and additional on-chip peripherals similar to the other C6000 DSP platform devices.

The C6416 device has two high-performance embedded coprocessors [Viterbi decoder coprocessor (VCP) and turbo decoder coprocessor (TCP)] that significantly speed up channel-decoding operations on chip. The VCP operating at CPU clock divided-by-4 can decode over 500 7.95-Kbps adaptive multi-rate (AMR) (K = 9, R = 1/3) voice channels. The VCP supports constraint lengths K = 5, 6, 7, 8, and 9, rates R = 1/2, 1/3, and 1/4, and flexible polynomials, while generating hard decisions or soft decisions. The TCP operating at CPU clock divided-by-2 can decode up to 36 384-Kbps or 6 2-Mbps turbo encoded channels (assuming iterations). The TCP implements the max\*log-map algorithm and is designed to support all polynomials and rates required by Third-Generation Partnership Projects (3GPP and 3GPP2), with fully programmable frame length and turbo interleaver. Decoding parameters, such as the number of iterations and stopping criteria, are also programmable. Communications between the VCP/TCP and the CPU are carried out through the EDMA controller.

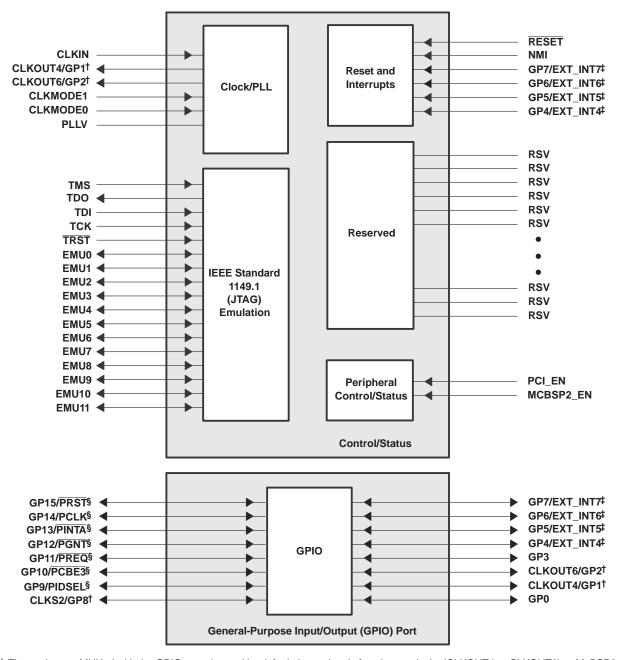

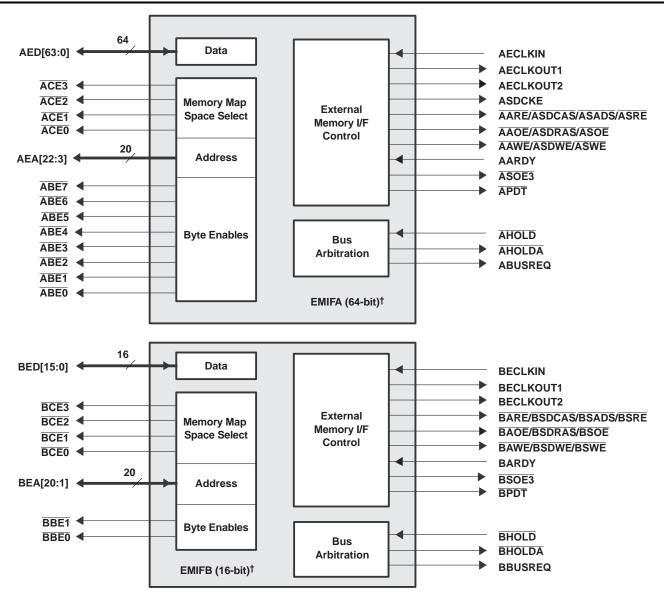

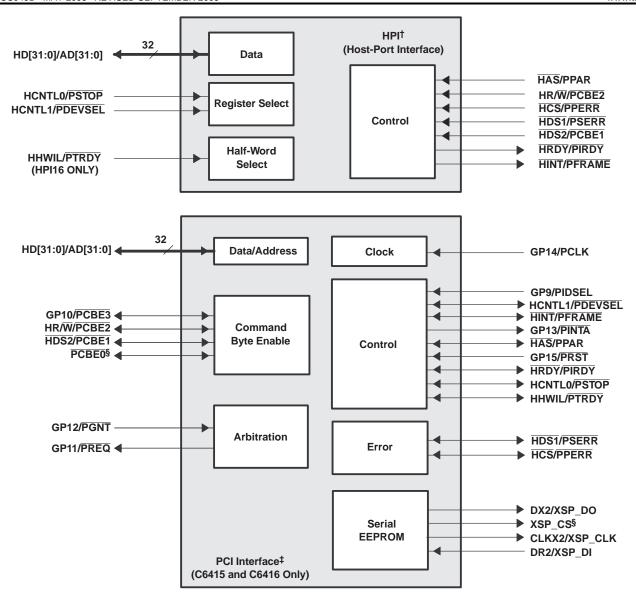

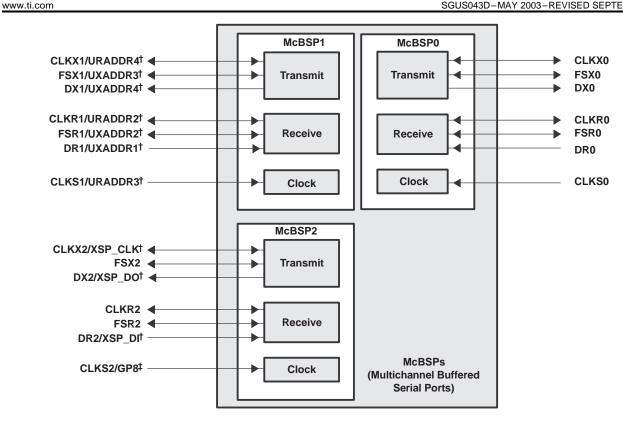

The C64x uses a two-level cache-based architecture and has a powerful and diverse set of peripherals. The level 1 program (L1P) cache is a 128K-bit direct-mapped cache and the level 1 data (L1D) cache is a 128K-bit 2-way set-associative cache. The level 2 memory/cache (L2) consists of an 8M-bit memory space that is shared between program and data space. L2 memory can be configured as mapped memory or combinations of cache (up to 256K bytes) and mapped memory. The peripheral set includes 3 multichannel buffered serial ports (McBSPs), an 8-bit universal test and operations PHY interface for asynchronous transfer mode (ATM) slave (UTOPIA slave) port (C6415/C6416 only), 3 32-bit general-purpose timers, a user-configurable 16-bit or 32-bit host-port interface (HPI16/HPI32), a peripheral component interconnect (PCI) (C6415/C6416 only), a general-purpose input/output port (GPIO) with 16 GPIO pins, and two glueless external memory interfaces (64-bit EMIFA and 16-bit EMIFB), both of which are capable of interfacing to synchronous and asynchronous memories and peripherals.

# SM320C6414-EP, SM320C6415-EP, SM320C6416-EP FIXED-POINT DIGITAL SIGNAL PROCESSORS

SGUS043D-MAY 2003-REVISED SEPTEMBER 2008

The C64x has a complete set of development tools that includes an advanced C compiler with C64x-specific enhancements, an assembly optimizer to simplify programming and scheduling, and a Windows™ debugger interface for visibility into source code execution. (3)(4)

- (3) Throughout the remainder of this document, the SM320C6414-EP, SM320C6415-EP, and SM320C6416-EP are referred to as SM320C64x or C64x where generic and, where specific, their individual full device part numbers are used or abbreviated as C6414, C6415, or C6416, respectively.

- (4) These C64x devices have two EMIFs (64-bit EMIFA and 16-bit EMIFB). The prefix "A" in front of a signal name indicates it is an EMIFA signal whereas a prefix "B" in front of a signal name indicates it is an EMIFB signal. Throughout the rest of this document, in generic EMIF areas of discussion, the prefix "A" or "B" may be omitted from the signal name.

#### 1.4 Ball-Grid Array (BGA) Package

GLZ 532-PIN BALL GRID ARRAY (BGA) PACKAGE (BOTTOM VIEW)

#### 1.4.1 Device Characteristics

Table 1-1 provides an overview of the C6414, C6415, and C6416 DSPs. Table 1-1 shows significant features of the C64x devices, including the capacity of on-chip RAM, the peripherals, the CPU frequency, and the package type with pin count.

Table 1-1. Characteristics of the C6414, C6415, and C6416 Processors

|                                                    | HARDWARE FEATURES                                                                 | C6414, C6415, AND C6416                                                                                    |  |

|----------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|

|                                                    | EMIFA (64-bit bus width)<br>(default clock source = AECLKIN)                      | 1                                                                                                          |  |

| Peripherals                                        | EMIFB (16-bit bus width) (default clock source = BECLKIN)                         | 1                                                                                                          |  |

| Not all peripherals pins                           | EDMA (64 independent channels)                                                    | 1                                                                                                          |  |

| are available at the same time. (For more details. | HPI (32- or 16-bit user selectable)                                               | 1 (HPI16 or HPI32)                                                                                         |  |

| see the Device                                     | PCI (32-bit) [DeviceID Register value 0xA106]                                     | 1 (C6415/C6416 only)                                                                                       |  |

| Configuration section.)  Peripheral performance is | McBSPs<br>(default internal clock source = CPU/4 clock frequency)                 | 3                                                                                                          |  |

| dependent on chip-level                            | UTOPIA (8-bit mode)                                                               | 1 (C6415/C6416 only)                                                                                       |  |

| configuration.                                     | 32-bit timers<br>(default internal clock source = CPU/8 clock frequency)          | 3                                                                                                          |  |

|                                                    | General-purpose input/output 0 (GP0)                                              | 16                                                                                                         |  |

| Deceder conveneers                                 | VCP                                                                               | 1 (C6416 only)                                                                                             |  |

| Decoder coprocessors                               | TCP                                                                               | 1 (C6416 only)                                                                                             |  |

|                                                    | Size (bytes)                                                                      | 1056K                                                                                                      |  |

| On-chip memory                                     | Organization                                                                      | 16K-byte (16KB) L1 program (L1P) cache<br>16KB L1 data (L1D) cache<br>1024KB unified mapped RAM/cache (L2) |  |

| CPU ID + CPU Rev ID                                | Control Status Register (CSR[31:16]) 0x0C01                                       |                                                                                                            |  |

| Device_ID                                          | Silicon Revision Identification Register (DEVICE_REV[19:16]) Address: 0x01B0 0200 | DEVICE_REV[19:16] Silicon revision 1111 1.03 or earlier 0001 1.03 0010 1.1                                 |  |

| Frequency                                          | MHz                                                                               | 500                                                                                                        |  |

| Cycle time                                         | ns 2 ns (C6414-50A, C6415-50A<br>(500-MHz CPU, 100-MH                             |                                                                                                            |  |

| Voltogo                                            | Core (V)                                                                          | 1.25 V (-50A)                                                                                              |  |

| Voltage                                            | I/O (V)                                                                           | 3.3 V                                                                                                      |  |

| PLL options                                        | CLKIN frequency multiplier                                                        | Bypass (x1), x6, x12                                                                                       |  |

| BGA package                                        | 23 mm × 23 mm                                                                     | 532-pin BGA (GLZ)                                                                                          |  |

| Process technology                                 | CMOS                                                                              | 0.3 μm                                                                                                     |  |

| Product status                                     | Product Preview (PP) Advance Information (AI) Production Data (PD)                | PD                                                                                                         |  |

<sup>(1)</sup> On these C64x devices, the rated EMIF speed affects only the SDRAM interface on EMIFA. For more detailed information, see the EMIF Device Speed section of this data manual.

# SM320C6414-EP, SM320C6415-EP, SM320C6416-EP FIXED-POINT DIGITAL SIGNAL PROCESSORS

SGUS043D-MAY 2003-REVISED SEPTEMBER 2008

#### 1.4.2 Device Compatiblity

The C64x generation of devices has a diverse and powerful set of peripherals. The common peripheral set and pin compatibility that the C6414, C6415, and C6416 devices offer lead to easier system designs and faster time to market. Table 1-2 identifies the peripherals and coprocessors that are available on the C6414, C6415, and C6416 devices.

The C6414, C6415, and C6416 devices are pin-for-pin compatible, provided the following conditions are met:

- All devices use the same peripherals.

- The C6414 is pin-for-pin compatible with the C6415/C6416 when the PCI and UTOPIA peripherals on the C6415/C6416 are disabled.

- The C6415 is pin-for-pin compatible with the C6416 when they are in the same peripheral selection mode. For more information on peripheral selection, see the Device Configurations section of this data manual.

- The BEA[9:7] pins are properly pulled up/down.

- For more details on the device-specific BEA[9:7] pin configurations, see the Terminal Functions table of this data manual.

Table 1-2. Peripherals and Coprocessors Available on C6414, C6415, and C6416 Devices (1) (2)

| PERIPHERALS/COPROCESSORS                 |  | C6414     | C6415 | C6416 |

|------------------------------------------|--|-----------|-------|-------|

| EMIFA (64-bit bus width)                 |  | $\sqrt{}$ | √     | √     |

| EMIFB (16-bit bus width)                 |  | $\sqrt{}$ | √     | √     |

| EDMA (64 independent channels)           |  | $\sqrt{}$ | √     | √     |

| HPI (32- or 16-bit user selectable)      |  | $\sqrt{}$ | √     | √     |

| PCI (32 bit) (specification v2.2)        |  | _         | √     | √     |

| McBSPs (McBSP0, McBSP1, McBSP2)          |  | $\sqrt{}$ | √     | √     |

| UTOPIA (8-bit mode) (specification v1.0) |  | _         | √     | √     |

| Timers (32 bit) (TIMER0, TIMER1, TIMER2) |  |           | √     | √     |

| GPIOs (GP[15:0])                         |  | $\sqrt{}$ | √     | √     |

| VCP/TCP coprocessors                     |  | _         | _     | √     |

<sup>(1) —</sup> denotes peripheral/coprocessor is not available on this device.

Submit Documentation Feedback

Introduction

<sup>(2)</sup> Not all peripherals pins are available at the same time. (For more details, see the Device Configuration section.)

For more detailed information on the device compatibility and similarities/differences among the C6414, C6415, and C6416 devices, see the *How To Begin Development Today With the TMS320C6414, TMS320C6415, and TMS320C6416 DSPs* application report (literature number SPRA718).

#### 1.4.3 Functional Block and CPU (DSP Core) Diagram

- A. VCP and TCP decoder coprocessors are applicable to the C6416 device only.

- B. For the C6415 and C6416 devices, the UTOPIA peripheral is multiplexed with McBSP1, and the PCI peripheral is multiplexed with the HPI peripheral and the GPIO[15:9] port. For more details on the multiplexed pins of these peripherals, see the Device Configurations section of this data manual.

SGUS043D-MAY 2003-REVISED SEPTEMBER 2008

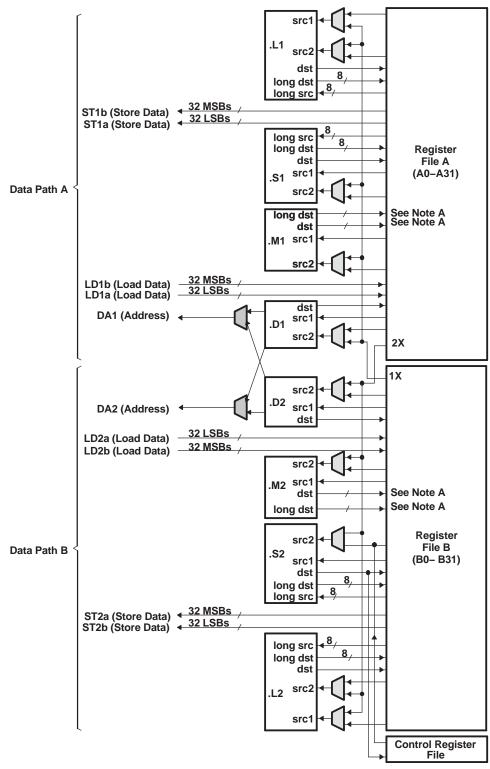

# 1.4.4 CPU (DSP Core) Description

The CPU fetches VelociTI advanced very-long instruction words (VLIWs) (256 bits wide) to supply up to eight 32-bit instructions to the eight functional units during every clock cycle. The VelociTI VLIW architecture features controls by which all eight units do not have to be supplied with instructions if they are not ready to execute. The first bit of every 32-bit instruction determines if the next instruction belongs to the same execute packet as the previous instruction, or whether it should be executed in the following clock as a part of the next execute packet. Fetch packets are always 256 bits wide; however, the execute packets can vary in size. The variable-length execute packets are a key memory-saving feature, distinguishing the C64x CPUs from other VLIW architectures. The C64x VelociTI.2 extensions add enhancements to the TMS320C62x<sup>TM</sup> DSP VelociTI architecture. These enhancements include:

- Register file enhancements

- Data-path extensions

- Quad 8-bit and dual 16-bit extensions with data-flow enhancements

- Additional functional unit hardware

- Increased orthogonality of the instruction set

- Additional instructions that reduce code size and increase register flexibility

The CPU features two sets of functional units. Each set contains four units and a register file. One set contains functional units .L1, .S1, .M1, and .D1. The other set contains units .D2, .M2, .S2, and .L2. The two register files each contain 32 32-bit registers for a total of 64 general-purpose registers. In addition to supporting the packed 16-bit and 32-/40-bit fixed-point data types found in the C62x VelociTI VLIW architecture, the C64x register files also support packed 8-bit data and 64-bit fixed-point data types. The two sets of functional units, along with two register files, compose sides A and B of the CPU [see the functional block and CPU (DSP core) diagram, and Figure 1-1]. The four functional units on each side of the CPU can freely share the 32 registers belonging to that side. Additionally, each side features a data cross path - a single data bus connected to all the registers on the other side, by which the two sets of functional units can access data from the register files on the opposite side. The C64x CPU pipelines data-cross-path accesses over multiple clock cycles. This allows the same register to be used as a data-cross-path operand by multiple functional units in the same execute packet. All functional units in the C64x CPU can access operands via the data cross path. Register access by functional units on the same side of the CPU as the register file can service all the units in a single clock cycle. On the C64x CPU, a delay clock is introduced when an instruction attempts to read a register via a data cross path if that register was updated in the previous clock cycle.

In addition to the C62x DSP fixed-point instructions, the C64x DSP includes a comprehensive collection of quad 8-bit and dual 16-bit instruction set extensions. These VelociTI.2 extensions allow the C64x CPU to operate directly on packed data to streamline data flow and increase instruction set efficiency.

Another key feature of the C64x CPU is the load/store architecture, where all instructions operate on registers (as opposed to data in memory). Two sets of data-addressing units (.D1 and .D2) are responsible for all data transfers between the register files and the memory. The data address driven by the .D units allows data addresses generated from one register file to be used to load or store data to or from the other register file. The C64x .D units can load and store bytes (8 bits), half words (16 bits), and words (32 bits) with a single instruction. And with the new data-path extensions, the C64x .D unit can load and store doublewords (64 bits) with a single instruction. Furthermore, the nonaligned load and store instructions allow the .D units to access words and doublewords on any byte boundary. The C64x CPU supports a variety of indirect addressing modes using either linear or circular addressing with 5- or 15-bit offsets. All instructions are conditional, and most can access any one of the 64 registers. Some registers, however, are singled out to support specific addressing modes or to hold the condition for conditional instructions (if the condition is not automatically true).

Submit Documentation Feedback Introduction 7

SGUS043D-MAY 2003-REVISED SEPTEMBER 2008

www.ti.com

The two .M functional units perform all multiplication operations. Each of the C64x .M units can perform two 16-bit  $\times$  16-bit multiplies or four 8-bit  $\times$  8-bit multiplies per clock cycle. The .M unit can also perform 16-bit  $\times$  32-bit multiply operations, dual 16-bit  $\times$  16-bit multiplies with add/subtract operations, and quad 8-bit  $\times$  8-bit multiplies with add operations. In addition to standard multiplies, the C64x .M units include bit-count, rotate, Galois field multiplies, and bidirectional variable shift hardware.

The two .S and .L functional units perform a general set of arithmetic, logical, and branch functions, with results available every clock cycle. The arithmetic and logical functions on the C64x CPU include single 32-bit, dual 16-bit, and quad 8-bit operations.

The processing flow begins when a 256-bit-wide instruction fetch packet is fetched from a program memory. The 32-bit instructions destined for the individual functional units are linked together by "1" bits in the least significant bit (LSB) position of the instructions. The instructions that are chained together for simultaneous execution (up to eight in total) compose an execute packet. A "0" in the LSB of an instruction breaks the chain, effectively placing the instructions that follow it in the next execute packet. A C64x DSP device enhancement now allows execute packets to cross fetch-packet boundaries. In the TMS320C62x/TMS320C67x<sup>™</sup> DSP devices, if an execute packet crosses the fetch-packet boundary (256 bits wide), the assembler places it in the next fetch packet, while the remainder of the current fetch packet is padded with no-operation (NOP) instructions. In the C64x DSP device, the execute boundary restrictions have been removed, thereby, eliminating all of the NOPs added to pad the fetch packet and, thus, decreasing the overall code size. The number of execute packets within a fetch packet can vary from one to eight. Execute packets are dispatched to their respective functional units at the rate of one per clock cycle, and the next 256-bit fetch packet is not fetched until all the execute packets from the current fetch packet have been dispatched. After decoding, the instructions simultaneously drive all active functional units for a maximum execution rate of eight instructions every clock cycle. While most results are stored in 32-bit registers, they can be subsequently moved to memory as bytes, halfwords, words, or doublewords. All load and store instructions are byte, halfword, word, or doubleword addressable.

For more details on the C64x CPU functional units enhancements, see the following documents:

- TMS320C6000 CPU and Instruction Set Reference Guide (literature number SPRU189)

- TMS320C64x<sup>™</sup> Technical Overview (literature number SPRU395)

- How to Begin Development Today With the TMS320C6414, TMS320C6415, and TMS320C6416 DSPs application report (<u>literature number SPRA718</u>)

A. For the .M functional units, the long dst is 32 MSBs and the dst is 32 LSBs.

Figure 1-1. SM320C64x™ CPU (DSP Core) Data Paths

Submit Documentation Feedback Introduction 9

#### 1.4.5 Memory Map Summary

Table 1-3 shows the memory map address ranges of the SM320C64x device. Internal memory is always located at address 0 and can be used as both program and data memory. The external memory address ranges in the C64x device begin at the hex address locations 0x6000 0000 for EMIFB and 0x8000 0000 for EMIFA.

Table 1-3. SM320C64x Memory Map Summary

| MEMORY BLOCK DESCRIPTION                               | BLOCK SIZE (BYTES) | HEX ADDRESS RANGE   |

|--------------------------------------------------------|--------------------|---------------------|

| Internal RAM (L2)                                      | 1M                 | 0000 0000-000F FFFF |

| Reserved                                               | 23M                | 0010 0000-017F FFFF |

| External Memory Interface A (EMIFA) Registers          | 256K               | 0180 0000-0183 FFFF |

| L2 Registers                                           | 256K               | 0184 0000-0187 FFFF |

| HPI Registers                                          | 256K               | 0188 0000-018B FFFF |

| McBSP 0 Registers                                      | 256K               | 018C 0000-018F FFFF |

| McBSP 1 Registers                                      | 256K               | 0190 0000-0193 FFFF |

| Timer 0 Registers                                      | 256K               | 0194 0000-0197 FFFF |

| Timer 1 Registers                                      | 256K               | 0198 0000-019B FFFF |

| Interrupt Selector Registers                           | 256K               | 019C 0000-019F FFFF |

| EDMA RAM and EDMA Registers                            | 256K               | 01A0 0000-01A3 FFFF |

| McBSP 2 Registers                                      | 256K               | 01A4 0000-01A7 FFFF |

| EMIFB Registers                                        | 256K               | 01A8 0000-01AB FFFF |

| Timer 2 Registers                                      | 256K               | 01AC 0000-01AF FFFF |

| GPIO Registers                                         | 256K               | 01B0 0000-01B3 FFFF |

| UTOPIA Registers (C6415 and C6416 only) <sup>(1)</sup> | 256K               | 01B4 0000-01B7 FFFF |

| TCP/VCP Registers (C6416 only) <sup>(2)</sup>          | 256K               | 01B8 0000-01BB FFFF |

| Reserved                                               | 256K               | 01BC 0000-01BF FFFF |

| PCI Registers (C6415 and C6416 only) <sup>(1)</sup>    | 256K               | 01C0 0000-01C3 FFFF |

| Reserved                                               | 4M-256K            | 01C4 0000-01FF FFFF |

| QDMA Registers                                         | 52                 | 0200 0000–0200 0033 |

| Reserved                                               | 736M-52            | 0200 0034–2FFF FFFF |

| McBSP 0 Data                                           | 64M                | 3000 0000–33FF FFFF |

| McBSP 1 Data                                           | 64M                | 3400 0000–37FF FFFF |

| McBSP 2 Data                                           | 64M                | 3800 0000–3BFF FFFF |

| UTOPIA Queues (C6415 and C6416 only) <sup>(1)</sup>    | 64M                | 3C00 0000-3FFF FFFF |

| Reserved                                               | 256K               | 4000 0000–4FFF FFFF |

| TCP/VCP (C6416 only) <sup>(2)</sup>                    | 256K               | 5000 0000-5FFF FFFF |

| EMIFB CE0                                              | 64M                | 6000 0000-63FF FFFF |

| EMIFB CE1                                              | 64M                | 6400 0000-67FF FFFF |

| EMIFB CE2                                              | 64M                | 6800 0000-6BFF FFFF |

| EMIFB CE3                                              | 64M                | 6C00 0000-6FFF FFFF |

| Reserved                                               | 256K               | 7000 0000–7FFF FFFF |

| EMIFA CE0                                              | 256K               | 8000 0000–8FFF FFFF |

| EMIFA CE1                                              | 256K               | 9000 0000–9FFF FFFF |

| EMIFA CE2                                              | 256K               | A000 0000–AFFF FFFF |

| EMIFA CE3                                              | 256K               | B000 0000-BFFF FFFF |

| Reserved                                               | 1G                 | C000 0000-FFFF FFFF |

For the C6414 device, these memory address locations are reserved. The C6414 device does not support the UTOPIA and PCI peripherals.

Only the C6416 device supports the VCP/TCP coprocessors. For the C6414 and C6415 devices, these memory address locations are reserved.

## 1.4.6 Peripheral Register Descriptions

Table 1-4 through Table 1-24 identify the peripheral registers for the C6414, C6415, and C6416 devices by their register names, acronyms, and hex address or hex address range. For more detailed information on the register contents and bit names and their descriptions, see the *TMS320C6000 Peripherals Reference Guide* (literature number <u>SPRU190</u>).

**Table 1-4. EMIFA Registers**

| HEX ADDRESS         | ACRONYM | REGISTER NAME                            |

|---------------------|---------|------------------------------------------|

| 0180 0000           | GBLCTL  | EMIFA Global Control                     |

| 0180 0004           | CECTL1  | EMIFA CE1 Space Control                  |

| 0180 0008           | CECTL0  | EMIFA CE0 Space Control                  |

| 0180 000C           | _       | Reserved                                 |

| 0180 0010           | CECTL2  | EMIFA CE2 Space Control                  |

| 0180 0014           | CECTL3  | EMIFA CE3 Space Control                  |

| 0180 0018           | SDCTL   | EMIFA SDRAM Control                      |

| 0180 001C           | SDTIM   | EMIFA SDRAM Refresh Control              |

| 0180 0020           | SDEXT   | EMIFA SDRAM Extension                    |

| 0180 0024-0180 003C | _       | Reserved                                 |

| 0180 0040           | PDTCTL  | Peripheral Device Transfer (PDT) Control |

| 0180 0044           | CESEC1  | EMIFA CE1 Space Secondary Control        |

| 0180 0048           | CESEC0  | EMIFA CE0 Space Secondary Control        |

| 0180 004C           | _       | Reserved                                 |

| 0180 0050           | CESEC2  | EMIFA CE2 Space Secondary Control        |

| 0180 0054           | CESEC3  | EMIFA CE3 Space Secondary Control        |

| 0180 0058-0183 FFFF | _       | Reserved                                 |

#### Table 1-5. EMIFB Registers

| HEX ADDRESS         | ACRONYM | REGISTER NAME                            |

|---------------------|---------|------------------------------------------|

| 01A8 0000           | GBLCTL  | EMIFB Global Control                     |

| 01A8 0004           | CECTL1  | EMIFB CE1 Space Control                  |

| 01A8 0008           | CECTL0  | EMIFB CE0 Space Control                  |

| 01A8 000C           | -       | Reserved                                 |

| 01A8 0010           | CECTL2  | EMIFB CE2 Space Control                  |

| 01A8 0014           | CECTL3  | EMIFB CE3 Space Control                  |

| 01A8 0018           | SDCTL   | EMIFB SDRAM Control                      |

| 01A8 001C           | SDTIM   | EMIFB SDRAM Refresh Control              |

| 01A8 0020           | SDEXT   | EMIFB SDRAM Extension                    |

| 01A8 0024-01A8 003C | -       | Reserved                                 |

| 01A8 0040           | PDTCTL  | Peripheral Device Transfer (PDT) Control |

| 01A8 0044           | CESEC1  | EMIFB CE1 Space Secondary Control        |

| 01A8 0048           | CESEC0  | EMIFB CE0 Space Secondary Control        |

| 01A8 004C           | -       | Reserved                                 |

| 01A8 0050           | CESEC2  | EMIFB CE2 Space Secondary Control        |

| 01A8 0054           | CESEC3  | EMIFB CE3 Space Secondary Control        |

| 01A8 0058-01AB FFFF | _       | Reserved                                 |

# Table 1-6. L2 Cache Registers

| HEX ADDRESS         | ACRONYM          | REGISTER NAME                                |

|---------------------|------------------|----------------------------------------------|

| 0184 0000           | CCFG             | Cache Configuration                          |

| 0184 0004-0184 0FFC | -                | Reserved                                     |

| 0184 1000           | EDMAWEIGHT       | L2 EDMA Access Control                       |

| 0184 1004-0184 1FFC | -                | Reserved                                     |

| 0184 2000           | L2ALLOC0         | L2 Allocation 0                              |

| 0184 2004           | L2ALLOC1         | L2 Allocation 1                              |

| 0184 2008           | L2ALLOC2         | L2 Allocation 2                              |

| 0184 200C           | L2ALLOC3         | L2 Allocation 3                              |

| 0184 2010-0184 3FFC | -                | Reserved                                     |

| 0184 4000           | L2FBAR           | L2 Flush Base Address Register               |

| 0184 4004           | L2FWC            | L2 Flush Word Count                          |

| 0184 4010           | L2CBAR           | L2 Clean Base Address Register               |

| 0184 4014           | L2CWC            | L2 Clean Word Count                          |

| 0184 4020           | L1PFBAR          | L1P Flush Base Address Register              |

| 0184 4024           | L1PFWC           | L1P Flush Word Count                         |

| 0184 4030           | L1DFBAR          | L1D Flush Base Address Register              |

| 0184 4034           | L1DFWC           | L1D Flush Word Count                         |

| 0184 4038-0184 4FFC | _                | Reserved                                     |

| 0184 5000           | L2FLUSH          | L2 Flush                                     |

| 0184 5004           | L2CLEAN          | L2 Clean                                     |

| 0184 5008-0184 7FFC | _                | Reserved                                     |

| 0184 8000-0184 817C | MAR0 to MAR95    | Reserved                                     |

| 0184 8180           | MAR96            | Controls EMIFB CE0 range 6000 0000–60FF FFFF |

| 0184 8184           | MAR97            | Controls EMIFB CE0 range 6100 0000–61FF FFFF |

| 0184 8188           | MAR98            | Controls EMIFB CE0 range 6200 0000–62FF FFFF |

| 0184 818C           | MAR99            | Controls EMIFB CE0 range 6300 0000–63FF FFFF |

| 0184 8190           | MAR100           | Controls EMIFB CE1 range 6400 0000–64FF FFFF |

| 0184 8194           | MAR101           | Controls EMIFB CE1 range 6500 0000–65FF FFFF |

| 0184 8198           | MAR102           | Controls EMIFB CE1 range 6600 0000–66FF FFFF |

| 0184 819C           | MAR103           | Controls EMIFB CE1 range 6700 0000–67FF FFFF |

| 0184 81A0           | MAR104           | Controls EMIFB CE2 range 6800 0000–68FF FFFF |

| 0184 81A4           | MAR105           | Controls EMIFB CE2 range 6900 0000–69FF FFFF |

| 0184 81A8           | MAR106           | Controls EMIFB CE2 range 6A00 0000–6AFF FFFF |

| 0184 81AC           | MAR107           | Controls EMIFB CE2 range 6B00 0000–6BFF FFFF |

| 0184 81B0           | MAR108           | Controls EMIFB CE3 range 6C00 0000–6CFF FFFF |

| 0184 81B4           | MAR109           | Controls EMIFB CE3 range 6D00 0000–6DFF FFFF |

| 0184 81B8           | MAR110           | Controls EMIFB CE3 range 6E00 0000–6EFF FFFF |

| 0184 81BC           | MAR111           | Controls EMIFB CE3 range 6F00 0000–6FFF FFFF |

| 0184 81C0-0184 81FC | MAR112 to MAR127 | Reserved                                     |

| 0184 8200           | MAR128           | Controls EMIFA CE0 range 8000 0000–80FF FFFF |

| 0184 8204           | MAR129           | Controls EMIFA CE0 range 8100 0000–81FF FFFF |

| 0184 8208           | MAR130           | Controls EMIFA CE0 range 8200 0000–82FF FFFF |

| 0184 820C           | MAR131           | Controls EMIFA CE0 range 8300 0000–83FF FFFF |

| 0184 8210           | MAR132           | Controls EMIFA CE0 range 8400 0000–84FF FFFF |

| 0184 8214           | MAR133           | Controls EMIFA CE0 range 8500 0000–85FF FFFF |

| 0184 8218           | MAR134           | Controls EMIFA CE0 range 8600 0000–86FF FFFF |

www.ti.com SGUS043D-MAY 2003-REVISED SEPTEMBER 2008

# Table 1-6. L2 Cache Registers (continued)

| HEX ADDRESS | ACRONYM | REGISTER NAME                                |

|-------------|---------|----------------------------------------------|

| 0184 821C   | MAR135  | Controls EMIFA CE0 range 8700 0000–87FF FFFF |

| 0184 8220   | MAR136  | Controls EMIFA CE0 range 8800 0000–88FF FFFF |

| 0184 8224   | MAR137  | Controls EMIFA CE0 range 8900 0000–89FF FFFF |

| 0184 8228   | MAR138  | Controls EMIFA CE0 range 8A00 0000–8AFF FFFF |

| 0184 822C   | MAR139  | Controls EMIFA CE0 range 8B00 0000–8BFF FFFF |

| 0184 8230   | MAR140  | Controls EMIFA CE0 range 8C00 0000–8CFF FFFF |

| 0184 8234   | MAR141  | Controls EMIFA CE0 range 8D00 0000–8DFF FFFF |

| 0184 8238   | MAR142  | Controls EMIFA CE0 range 8E00 0000–8EFF FFFF |

| 0184 823C   | MAR143  | Controls EMIFA CE0 range 8F00 0000–8FFF FFFF |

| 0184 8240   | MAR144  | Controls EMIFA CE1 range 9000 0000–90FF FFFF |

| 0184 8244   | MAR145  | Controls EMIFA CE1 range 9100 0000–91FF FFFF |

| 0184 8248   | MAR146  | Controls EMIFA CE1 range 9200 0000–92FF FFFF |

| 0184 824C   | MAR147  | Controls EMIFA CE1 range 9300 0000–93FF FFFF |

| 0184 8250   | MAR148  | Controls EMIFA CE1 range 9400 0000–94FF FFFF |

| 0184 8254   | MAR149  | Controls EMIFA CE1 range 9500 0000–95FF FFFF |

| 0184 8258   | MAR150  | Controls EMIFA CE1 range 9600 0000–96FF FFFF |

| 0184 825C   | MAR151  | Controls EMIFA CE1 range 9700 0000–97FF FFFF |

| 0184 8260   | MAR152  | Controls EMIFA CE1 range 9800 0000–98FF FFFF |

| 0184 8264   | MAR153  | Controls EMIFA CE1 range 9900 0000–99FF FFFF |

| 0184 8268   | MAR154  | Controls EMIFA CE1 range 9A00 0000–9AFF FFFF |

| 0184 826C   | MAR155  | Controls EMIFA CE1 range 9B00 0000–9BFF FFFF |

| 0184 8270   | MAR156  | Controls EMIFA CE1 range 9C00 0000–9CFF FFFF |

| 0184 8274   | MAR157  | Controls EMIFA CE1 range 9D00 0000–9DFF FFFF |

| 0184 8278   | MAR158  | Controls EMIFA CE1 range 9E00 0000–9EFF FFFF |

| 0184 827C   | MAR159  | Controls EMIFA CE1 range 9F00 0000–9FFF FFFF |

| 0184 8280   | MAR160  | Controls EMIFA CE2 range A000 0000–A0FF FFFF |

| 0184 8284   | MAR161  | Controls EMIFA CE2 range A100 0000–A1FF FFFF |

| 0184 8288   | MAR162  | Controls EMIFA CE2 range A200 0000–A2FF FFFF |

| 0184 828C   | MAR163  | Controls EMIFA CE2 range A300 0000–A3FF FFFF |

| 0184 8290   | MAR164  | Controls EMIFA CE2 range A400 0000–A4FF FFFF |

| 0184 8294   | MAR165  | Controls EMIFA CE2 range A500 0000–A5FF FFFF |

| 0184 8298   | MAR166  | Controls EMIFA CE2 range A600 0000–A6FF FFFF |

| 0184 829C   | MAR167  | Controls EMIFA CE2 range A700 0000–A7FF FFFF |

| 0184 82A0   | MAR168  | Controls EMIFA CE2 range A800 0000–A8FF FFFF |

| 0184 82A4   | MAR169  | Controls EMIFA CE2 range A900 0000–A9FF FFFF |

| 0184 82A8   | MAR170  | Controls EMIFA CE2 range AA00 0000-AAFF FFFF |

| 0184 82AC   | MAR171  | Controls EMIFA CE2 range AB00 0000–ABFF FFFF |

| 0184 82B0   | MAR172  | Controls EMIFA CE2 range AC00 0000–ACFF FFFF |

| 0184 82B4   | MAR173  | Controls EMIFA CE2 range AD00 0000–ADFF FFFF |

| 0184 82B8   | MAR174  | Controls EMIFA CE2 range AE00 0000–AEFF FFFF |

| 0184 82BC   | MAR175  | Controls EMIFA CE2 range AF00 B000–AFFF FFFF |

| 0184 82A0   | MAR176  | Controls EMIFA CE3 range B000 0000–B0FF FFFF |

| 0184 82C4   | MAR177  | Controls EMIFA CE3 range B100 0000–B1FF FFFF |

| 0184 82C8   | MAR178  | Controls EMIFA CE3 range B200 0000–B2FF FFFF |

| 0184 82CC   | MAR179  | Controls EMIFA CE3 range B300 0000–B3FF FFFF |

| 0184 82D0   | MAR180  | Controls EMIFA CE3 range B400 0000–B4FF FFFF |

| 0184 82D4   | MAR181  | Controls EMIFA CE3 range B500 0000–B5FF FFFF |

MAR191

MAR192 to MAR255

**INSTRUMENTS**

0184 82FC

0184 8300-0184 83FC

0184 8400-0187 FFFF

| HEX ADDRESS | ACRONYM | REGISTER NAME                                |

|-------------|---------|----------------------------------------------|

| 0184 82D8   | MAR182  | Controls EMIFA CE3 range B600 0000–B6FF FFFF |

| 0184 82DC   | MAR183  | Controls EMIFA CE3 range B700 B000–B7FF FFFF |

| 0184 82E0   | MAR184  | Controls EMIFA CE3 range B800 0000–B8FF FFFF |

| 0184 82E4   | MAR185  | Controls EMIFA CE3 range B900 0000-B9FF FFFF |

| 0184 82E8   | MAR186  | Controls EMIFA CE3 range BA00 0000–BAFF FFFF |

| 0184 82EC   | MAR187  | Controls EMIFA CE3 range BB00 0000–BBFF FFFF |

| 0184 82F0   | MAR188  | Controls EMIFA CE3 range BC00 0000–BCFF FFFF |

| 0184 82F4   | MAR189  | Controls EMIFA CE3 range BD00 0000–BDFF FFFF |

| 0184 82F8   | MAR190  | Controls EMIFA CE3 range BE00 0000–BEFF FFFF |

Table 1-6. L2 Cache Registers (continued)

#### Table 1-7. EDMA Registers

Reserved

Reserved

Controls EMIFA CE3 range BF00 B000-BDFF FFFF

| HEX ADDRESS        | ACRONYM | REGISTER NAME                           |

|--------------------|---------|-----------------------------------------|

| 01A0 FF9C          | EPRH    | Event Polarity High Register            |

| 01A0 FFA4          | CIPRH   | Channel Interrupt Pending High Register |

| 01A0 FFA8          | CIERH   | Channel Interrupt Enable High Register  |

| 01A0 FFAC          | CCERH   | Channel Chain Enable High Register      |

| 01A0 FFB0          | ERH     | Event High Register                     |

| 01A0 FFB4          | EERH    | Event Enable High Register              |

| 01A0 FFB8          | ECRH    | Event Clear High Register               |

| 01A0 FFBC          | ESRH    | Event Set High Register                 |

| 01A0 FFC0          | PQAR0   | Priority Queue Allocation Register 0    |

| 01A0 FFC4          | PQAR1   | Priority Queue Allocation Register 1    |

| 01A0 FFC8          | PQAR2   | Priority Queue Allocation Register 2    |

| 01A0 FFCC          | PQAR3   | Priority Queue Allocation Register 3    |

| 01A0 FFDC          | EPRL    | Event Polarity Low Register             |

| 01A0 FFE0          | PQSR    | Priority Queue Status Register          |

| 01A0 FFE4          | CIPRL   | Channel Interrupt Pending Low Register  |

| 01A0 FFE8          | CIERL   | Channel Interrupt Enable Low Register   |

| 01A0 FFEC          | CCERL   | Channel Chain Enable Low Register       |

| 01A0 FFF0          | ERL     | Event Low Register                      |

| 01A0 FFF4          | EERL    | Event Enable Low Register               |

| 01A0 FFF8          | ECRL    | Event Clear Low Register                |

| 01A0 FFFC          | ESRL    | Event Set Low Register                  |

| 1A1 0000–01A3 FFFF | -       | Reserved                                |

#### Table 1-8. EDMA Parameter RAM<sup>(1)</sup>

| HEX ADDRESS         | REGISTER NAME                    |

|---------------------|----------------------------------|

| 01A0 0000-01A0 0017 | Parameters for Event 0 (6 words) |

| 01A0 0018-01A0 002F | Parameters for Event 1 (6 words) |

| 01A0 0030-01A0 0047 | Parameters for Event 2 (6 words) |

| 01A0 0048-01A0 005F | Parameters for Event 3 (6 words) |

| 01A0 0060—01A0 0077 | Parameters for Event 4 (6 words) |

| 01A0 0078-01A0 008F | Parameters for Event 5 (6 words) |

The C64x device has 21 parameter sets (6 words each) that can be used to reload/link EDMA transfers. (1)

www.ti.com SGUS043D-MAY 2003-REVISED SEPTEMBER 2008

## Table 1-8. EDMA Parameter RAM (continued)

| HEX ADDRESS          | REGISTER NAME                                |

|----------------------|----------------------------------------------|

| 01A0 0090-01A0 00A7  | Parameters for Event 6 (6 words)             |

| 01A0 00A8-01A0 00BF  | Parameters for Event 7 (6 words)             |

| 01A0 00C0-01A0 00D7  | Parameters for Event 8 (6 words)             |

| 01A0 00D8-01A0 00EF  | Parameters for Event 9 (6 words)             |

| 01A0 00F0-01A0 00107 | Parameters for Event 10 (6 words)            |

| 01A0 0108-01A0 011F  | Parameters for Event 11 (6 words)            |

| 01A0 0120-01A0 0137  | Parameters for Event 12 (6 words)            |

| 01A0 0138-01A0 014F  | Parameters for Event 13 (6 words)            |

| 01A0 0150-01A0 0167  | Parameters for Event 14 (6 words)            |

| 01A0 0168-01A0 017F  | Parameters for Event 15 (6 words)            |

| 01A0 0150-01A0 0167  | Parameters for Event 16 (6 words)            |

| 01A0 0168-01A0 017F  | Parameters for Event 17 (6 words)            |

|                      |                                              |

|                      |                                              |

| 01A0 05D0-01A0 05E7  | Parameters for Event 62 (6 words)            |

| 01A0 05E8-01A0 05FF  | Parameters for Event 63 (6 words)            |

| 01A0 0600-01A0 0617  | Reload/link parameters for Event M (6 words) |

| 01A0 0618-01A0 062F  | Reload/link parameters for Event N (6 words) |

|                      |                                              |

| 01A0 07E0-01A0 07F7  | Reload/link parameters for Event Z (6 words) |

| 01A0 07F8-01A0 07FF  | Scratch pad area (2 words)                   |

## Table 1-9. Quick DMA (QDMA) and Pseudo Registers

| HEX ADDRESS         | ACRONYM | REGISTER NAME                   |

|---------------------|---------|---------------------------------|

| 0200 0000           | QOPT    | QDMA Options Parameter          |

| 0200 0004           | QSRC    | QDMA Source Address             |

| 0200 0008           | QCNT    | QDMA Frame Count                |

| 0200 000C           | QDST    | QDMA Destination Address        |

| 0200 0010           | QIDX    | QDMA Index                      |

| 0200 0014-0200 001C |         | Reserved                        |

| 0200 0020           | QSOPT   | QDMA Pseudo Options             |

| 0200 0024           | QSSRC   | QDMA Pseudo Source Address      |

| 0200 0028           | QSCNT   | QDMA Pseudo Frame Count         |

| 0200 002C           | QSDST   | QDMA Pseudo Destination Address |

| 0200 0030           | QSIDX   | QDMA Pseudo Index               |

SGUS043D-MAY 2003-REVISED SEPTEMBER 2008

# Table 1-10. Interrupt Selector Registers

| HEX ADDRESS            | ACRONYM | REGISTER NAME               | COMMENTS                                                          |

|------------------------|---------|-----------------------------|-------------------------------------------------------------------|

| 019C 0000              | MUXH    | Interrupt Multiplexer High  | Selects which interrupts drive CPU interrupts 10–15 (INT10–INT15) |

| 019C 0004              | MUXL    | Interrupt Multiplexer Low   | Selects which interrupts drive CPU interrupts 4–9 (INT04–INT09)   |

| 019C 0008              | EXTPOL  | External Interrupt Polarity | Sets the polarity of the external interrupts (EXT_INT4–EXT_INT7)  |

| 019C 000C-019C<br>01FF | _       | Reserved                    |                                                                   |

## Table 1-11. Peripheral Power-Down Control Register

| HEX ADDRESS         | ACRONYM | REGISTER NAME                 |

|---------------------|---------|-------------------------------|

| 019C 0200           | PDCTL   | Peripheral Power-Down Control |

| 019C 0204-019F FFFF |         | Reserved                      |

## Table 1-12. McBSP 0 Registers

| HEX ADDRESS             | ACRONYM | REGISTER NAME                                       | COMMENTS                                                                          |

|-------------------------|---------|-----------------------------------------------------|-----------------------------------------------------------------------------------|

| 018C 0000               | DRR0    | McBSP0 Data Receive Register via configuration bus  | The CPU and EDMA controller can only read this register; they cannot write to it. |

| 0x3000 0000-0x33FF FFFF | DRR0    | McBSP0 Data Receive Register via peripheral bus     |                                                                                   |

| 018C 0004               | DXR0    | McBSP0 Data Transmit Register via configuration bus |                                                                                   |

| 0x3000 0000-0x33FF FFFF | DXR0    | McBSP0 Data Transmit Register via peripheral bus    |                                                                                   |

| 018C 0008               | SPCR0   | McBSP0 Serial Port Control Register                 |                                                                                   |

| 018C 000C               | RCR0    | McBSP0 Receive Control Register                     |                                                                                   |

| 018C 0010               | XCR0    | McBSP0 Transmit Control Register                    |                                                                                   |

| 018C 0014               | SRGR0   | McBSP0 Sample Rate Generator Register               |                                                                                   |

| 018C 0018               | MCR0    | McBSP0 Multichannel Control Register                |                                                                                   |

| 018C 001C               | RCERE00 | McBSP0 Enhanced Receive Channel Enable Register 0   |                                                                                   |

| 018C 0020               | XCERE00 | McBSP0 Enhanced Transmit Channel Enable Register 0  |                                                                                   |

| 018C 0024               | PCR0    | McBSP0 Pin Control Register                         |                                                                                   |

| 018C 0028               | RCERE10 | McBSP0 Enhanced Receive Channel Enable Register 1   |                                                                                   |

| 018C 002C               | XCERE10 | McBSP0 Enhanced Transmit Channel Enable Register    |                                                                                   |

| 018C 0030               | RCERE20 | McBSP0 Enhanced Receive Channel Enable Register 2   |                                                                                   |

| 018C 0034               | XCERE20 | McBSP0 Enhanced Transmit Channel Enable Register 2  |                                                                                   |

| 018C 0038               | RCERE30 | McBSP0 Enhanced Receive Channel Enable Register 3   |                                                                                   |

| 018C 003C               | XCERE30 | McBSP0 Enhanced Transmit Channel Enable Register 3  |                                                                                   |

| 018C 0040-018F FFFF     | _       | Reserved                                            |                                                                                   |

## Table 1-13. McBSP 1 Registers

| HEX ADDRESS                | ACRONYM | REGISTER NAME                                       | COMMENTS                                                                          |

|----------------------------|---------|-----------------------------------------------------|-----------------------------------------------------------------------------------|

| 018C 0000                  | DRR1    | McBSP1 Data Receive Register via configuration bus  | The CPU and EDMA controller can only read this register; they cannot write to it. |

| 0x3400 0000–0x37FF<br>FFFF | DRR1    | McBSP1 Data Receive Register via peripheral bus     |                                                                                   |

| 019C 0004                  | DXR1    | McBSP1 Data Transmit Register via configuration bus |                                                                                   |

www.ti.com SGUS043D-MAY 2003-REVISED SEPTEMBER 2008

# Table 1-13. McBSP 1 Registers (continued)

| HEX ADDRESS                | ACRONYM | REGISTER NAME                                      | COMMENTS |

|----------------------------|---------|----------------------------------------------------|----------|

| 0x3400 0000–0x37FF<br>FFFF | DXR1    | McBSP1 Data Transmit Register via peripheral bus   |          |

| 019C 0008                  | SPCR1   | McBSP1 Serial Port Control Register                |          |

| 019C 000C                  | RCR1    | McBSP1 Receive Control Register                    |          |

| 019C 0010                  | XCR1    | McBSP1 Transmit Control Register                   |          |

| 019C 0014                  | SRGR1   | McBSP1 Sample Rate Generator Register              |          |

| 019C 0018                  | MCR1    | McBSP1 Multichannel Control Register               |          |

| 019C 001C                  | RCERE01 | McBSP1 Enhanced Receive Channel Enable Register 0  |          |

| 019C 0020                  | XCERE01 | McBSP1 Enhanced Transmit Channel Enable Register 0 |          |

| 019C 0024                  | PCR1    | McBSP1 Pin Control Register                        |          |

| 019C 0028                  | RCERE11 | McBSP1 Enhanced Receive Channel Enable Register 1  |          |

| 019C 002C                  | XCERE11 | McBSP1 Enhanced Transmit Channel Enable Register 1 |          |

| 019C 0030                  | RCERE21 | McBSP1 Enhanced Receive Channel Enable Register 2  |          |

| 019C 0034                  | XCERE21 | McBSP1 Enhanced Transmit Channel Enable Register 2 |          |

| 019C 0038                  | RCERE31 | McBSP1 Enhanced Receive Channel Enable Register 3  |          |

| 019C 003C                  | XCERE31 | McBSP1 Enhanced Transmit Channel Enable Register 3 |          |

| 019C 0040-0193 FFFF        | _       | Reserved                                           |          |

## Table 1-14. McBSP 2 Registers

| HEX ADDRESS             | ACRONYM | REGISTER NAME                                       | COMMENTS                                                                          |

|-------------------------|---------|-----------------------------------------------------|-----------------------------------------------------------------------------------|

| 01A4 0000               | DRR2    | McBSP2 Data Receive Register via configuration bus  | The CPU and EDMA controller can only read this register; they cannot write to it. |

| 0x3800 0000-0x3BFF FFFF | DRR2    | McBSP2 Data Receive Register via peripheral bus     |                                                                                   |

| 01A4 0004               | DXR2    | McBSP2 Data Transmit Register via configuration bus |                                                                                   |

| 0x3800 0000-0x3BFF FFFF | DXR2    | McBSP2 Data Transmit Register via peripheral bus    |                                                                                   |

| 01A4 0008               | SPCR2   | McBSP2 Serial Port Control Register                 |                                                                                   |

| 01A4 000C               | RCR2    | McBSP2 Receive Control Register                     |                                                                                   |

| 01A4 0010               | XCR2    | McBSP2 Transmit Control Register                    |                                                                                   |

| 01A4 0014               | SRGR2   | McBSP2 Sample Rate Generator Register               |                                                                                   |

| 01A4 0018               | MCR2    | McBSP2 Multichannel Control Register                |                                                                                   |

| 01A4 001C               | RCERE02 | McBSP2 Enhanced Receive Channel Enable Register 0   |                                                                                   |

| 01A4 0020               | XCERE02 | McBSP2 Enhanced Transmit Channel Enable Register 0  |                                                                                   |

| 01A4 0024               | PCR2    | McBSP2 Pin Control Register                         |                                                                                   |

| 01A4 0028               | RCERE12 | McBSP2 Enhanced Receive Channel Enable Register 1   |                                                                                   |

| 01A4 002C               | XCERE12 | McBSP2 Enhanced Transmit Channel Enable Register 1  |                                                                                   |

| 01A4 0030               | RCERE22 | McBSP2 Enhanced Receive Channel Enable Register 2   |                                                                                   |

| 01A4 0034               | XCERE22 | McBSP2 Enhanced Transmit Channel Enable Register 2  |                                                                                   |

| 01A4 0038               | RCERE32 | McBSP2 Enhanced Receive Channel Enable Register 3   |                                                                                   |

| 01A4 003C               | XCERE32 | McBSP2 Enhanced Transmit Channel Enable Register 3  |                                                                                   |

| 01A4 0040-01A7 FFFF     | _       | Reserved                                            |                                                                                   |

SGUS043D-MAY 2003-REVISED SEPTEMBER 2008

# Table 1-15. Timer 0 Registers

| HEX ADDRESS         | ACRONYM | REGISTER NAME   | COMMENTS                                                                                                         |

|---------------------|---------|-----------------|------------------------------------------------------------------------------------------------------------------|

| 0194 0000           | CTL0    | Timer 0 Control | Determines the operating mode of the timer, monitors the timer status, and controls the function of the TOUT pin |

| 0194 0004           | PRD0    | Timer 0 Period  | Contains the number of timer input clock cycles to count. This number controls the TSTAT signal frequency.       |

| 0194 0008           | CNT0    | Timer 0 Counter | Contains the current value of the incrementing counter                                                           |

| 0194 000C-0197 FFFF | _       | Reserved        |                                                                                                                  |

## Table 1-16. Timer 1 Registers

| HEX ADDRESS         | ACRONYM | REGISTER NAME   | COMMENTS                                                                                                         |

|---------------------|---------|-----------------|------------------------------------------------------------------------------------------------------------------|

| 0198 0000           | CTL1    | Timer 1 Control | Determines the operating mode of the timer, monitors the timer status, and controls the function of the TOUT pin |

| 0198 0004           | PRD1    | Timer 1 Period  | Contains the number of timer input clock cycles to count. This number controls the TSTAT signal frequency.       |

| 0198 0008           | CNT1    | Timer 1 Counter | Contains the current value of the incrementing counter                                                           |

| 0198 000C-019B FFFF | _       | Reserved        |                                                                                                                  |

## Table 1-17. Timer 2 Registers

| HEX ADDRESS         | ACRONYM | REGISTER NAME   | COMMENTS                                                                                                         |

|---------------------|---------|-----------------|------------------------------------------------------------------------------------------------------------------|

| 01AC 0000           | CTL2    | Timer 2 Control | Determines the operating mode of the timer, monitors the timer status, and controls the function of the TOUT pin |

| 01AC 0004           | PRD2    | Timer 2 Period  | Contains the number of timer input clock cycles to count. This number controls the TSTAT signal frequency.       |

| 01AC 0008           | CNT2    | Timer 2 Counter | Contains the current value of the incrementing counter                                                           |

| 01AC 000C-01AF FFFF | _       | Reserved        |                                                                                                                  |

## Table 1-18. HPI Registers

| HEX ADDRESS         | ACRONYM                     | REGISTER NAME                | COMMENTS                                  |

|---------------------|-----------------------------|------------------------------|-------------------------------------------|

| _                   | HPID                        | HPI Data                     | Host read/write access only               |

| 0188 0000           | HPIC                        | HPI Control                  | HPIC has both host/CPU read/write access. |

| 0188 0004           | HPIA (HPIAW) <sup>(1)</sup> | HPI Address (Write)          | HPIA has both host/CPU read/write access. |

| 0188 0008           | HPIA (HPIAR) <sup>(1)</sup> | HPI Address (Read)           | HPIA has both host/CPO fead/white access. |

| 0188 000C-0189 FFFF | _                           | Reserved                     |                                           |

| 018A 0000           | TRCTL                       | HPI Transfer Request Control |                                           |

| 018A 0004-018B FFFF | -                           | Reserved                     |                                           |

Host access to the HPIA register updates both the HPIAW and HPIAR registers. The CPU can access HPIAW and HPIAR independently.

#### Table 1-19. GPIO Registers

| HEX ADDRESS | ACRONYM | REGISTER NAME   |

|-------------|---------|-----------------|

| 01B0 0000   | GPEN    | GPIO Enable     |

| 01B0 0004   | GPDIR   | GPIO Direction  |

| 01B0 0008   | GPVAL   | GPIO Value      |

| 01B0 000C   | -       | Reserved        |

| 01B0 0010   | GPDH    | GPIO Delta High |

| 01B0 0014   | GPHM    | GPIO High Mask  |

| 01B0 0018   | GPDL    | GPIO Delta Low  |

| 01B0 001C   | GPLM    | GPIO Low Mask   |

# SM320C6414-EP, SM320C6415-EP, SM320C6416-EP FIXED-POINT DIGITAL SIGNAL PROCESSORS

SGUS043D-MAY 2003-REVISED SEPTEMBER 2008

## Table 1-19. GPIO Registers (continued)

| HEX ADDRESS         | ACRONYM    | REGISTER NAME                                                                                           |

|---------------------|------------|---------------------------------------------------------------------------------------------------------|

| 01B0 0020           | GPGC       | GPIO Global Control                                                                                     |

| 01B0 0024           | GPPOL      | GPIO Interrupt Polarity                                                                                 |

| 01B0 0028-01B0 01FF | _          | Reserved                                                                                                |

| 01B0 0200           | DEVICE_REV | Silicon revision identification (For more details, see the device characteristics listed in Table 1-3.) |

| 01B0 0204-01B3 FFFF | _          | Reserved                                                                                                |

# Table 1-20. PCI Peripheral Registers (C6415 and C6416 Only)<sup>(1)</sup>

| HEX ADDRESS         | ACRONYM | REGISTER NAME                |  |

|---------------------|---------|------------------------------|--|

| 01C0 0000           | RSTSRC  | DSP Reset Source/Status      |  |

| 01C0 0004           | -       | Reserved                     |  |

| 01C0 0008           | PCIIS   | PCI Interrupt Source         |  |

| 01C0 000C           | PCIIEN  | PCI Interrupt Enable         |  |

| 01C0 0010           | DSPMA   | DSP Master Address           |  |

| 01C0 0014           | PCIMA   | PCI Master Address           |  |

| 01C0 0018           | PCIMC   | PCI Master Control           |  |

| 01C0 001C           | CDSPA   | Current DSP Address          |  |

| 01C0 0020           | CPCIA   | Current PCI Address          |  |

| 01C0 0024           | CCNT    | Current Byte Count           |  |

| 01C0 0028           | -       | Reserved                     |  |

| 01C0 02C-01C1 FFEF  | -       | Reserved                     |  |

| 0x01C1 FFF0         | HSR     | Host Status Register         |  |

| 0x01C1 FFF4         | HDCR    | Host-to-DSP Control Register |  |

| 0x01C1 FFF8         | DSPP    | DSP Page                     |  |

| 0x01C1 FFFC         | -       | Reserved                     |  |

| 01C2 0000           | EEADD   | EEPROM Address               |  |

| 01C2 0004           | EEDAT   | EEPROM Data                  |  |

| 01C2 0008           | EECTL   | EEPROM Control               |  |

| 01C2 000C-01C2 FFFF | _       | Reserved                     |  |

| 01C3 0000           | TRCTL   | PCI Transfer Request Control |  |

| 01C3 0004-01C3 FFFF | _       | Reserved                     |  |

<sup>(1)</sup> These PCI registers are not supported on the C6414 device.

# Table 1-21. UTOPIA Registers (C6415 and C6416 Only)(1)

| HEX ADDRESS         | ACRONYM | REGISTER NAME                     |

|---------------------|---------|-----------------------------------|

| 01B4 0000           | UCR     | UTOPIA Control Register           |

| 01B4 0004           | -       | Reserved                          |

| 01B4 0008           | -       | Reserved                          |

| 01B4 000C           | UIER    | UTOPIA Interrupt Enable Register  |

| 01B4 0010           | UIPR    | UTOPIA Interrupt Pending Register |

| 01B4 0014           | CDR     | Clock Detect Register             |

| 01B4 0018           | EIER    | Error Interrupt Enable Register   |

| 01B4 001C           | EIPR    | Error Interrupt Pending Register  |

| 01B4 0020-01B7 FFFF | _       | Reserved                          |

<sup>(1)</sup> These UTOPIA registers are not supported on the C6414 device.

# Table 1-22. UTOPIA Queue Registers (C6415 and C6416 Only)(1)

| HEX ADDRESS         | ACRONYM | REGISTER NAME         |

|---------------------|---------|-----------------------|

| 3C00 0000           | URQ     | UTOPIA Receive Queue  |

| 3D00 0000           | UXQ     | UTOPIA Transmit Queue |

| 3D00 0004–3FFF FFFF | _       | Reserved              |

<sup>(1)</sup> These UTOPIA registers are not supported on the C6414 device.

## Table 1-23. VCP Registers (C6414 Only)

| HEX A     | DDRESS         | ACDONIVM | DEGISTED                  |

|-----------|----------------|----------|---------------------------|

| EDMA BUS  | PERIPHERAL BUS | ACRONYM  | REGISTER                  |

| 5000 0000 | 01B8 0000      | VCPIC0   | VCP Input Configuration 0 |

| 5000 0004 | 01B8 0004      | VCPIC1   | VCP Input Configuration 1 |

| 5000 0008 | 01B8 0008      | VCPIC2   | VCP Input Configuration 2 |

| 5000 000C | 01B8 000C      | VCPIC3   | VCP Input Configuration 3 |

| 5000 0010 | 01B8 0010      | VCPIC4   | VCP Input Configuration 4 |

| 5000 0014 | 01B8 0014      | VCPIC5   | VCP Input Configuration 5 |

| 5000 0040 | 01B8 0024      | VCPOUT0  | VCP Output 0              |

| 5000 0044 | 01B8 0028      | VCPOUT1  | VCP Output 1              |

| 5000 0080 | _              | VCPWBM   | VCP Write Branch Metrics  |

| 5000 0088 | _              | VCPRDECS | VCP Read Decisions        |

| _         | 01B8 0018      | VCPEXE   | VCP Execution             |

| _         | 01B8 0020      | VCPEND   | VCP Endian                |

| _         | 01B8 0040      | VCPSTAT0 | VCP Status Register 0     |

| _         | 01B8 0044      | VCPSTAT1 | VCP Status Register 1     |

| _         | 01B8 0050      | VCPERR   | VCP Error                 |

## Table 1-24. TCP Registers (C6414 Only)

| HEX ADDRESS |                | ACRONYM  | REGISTER                            |  |

|-------------|----------------|----------|-------------------------------------|--|

| EDMA BUS    | PERIPHERAL BUS | ACRONTIN | REGISTER                            |  |

| 5800 0000   | 01BA 0000      | TCPIC0   | TCP Input Configuration 0           |  |

| 5800 0004   | 01BA 0004      | TCPIC1   | TCP Input Configuration 1           |  |

| 5800 0008   | 01BA 0008      | TCPIC2   | TCP Input Configuration 2           |  |

| 5800 000C   | 01BA 000C      | TCPIC3   | TCP Input Configuration 3           |  |

| 5800 0010   | 01BA 0010      | TCPIC4   | TCP Input Configuration 4           |  |

| 5800 0014   | 01BA 0014      | TCPIC5   | TCP Input Configuration 5           |  |

| 5800 0018   | 01BA 0018      | TCPIC6   | TCP Input Configuration 6           |  |

| 5800 001C   | 01BA 001C      | TCPIC7   | TCP Input Configuration 7           |  |

| 5800 0020   | 01BA 0020      | TCPIC8   | TCP Input Configuration 8           |  |

| 5800 0024   | 01BA 0024      | TCPIC9   | TCP Input Configuration 9           |  |

| 5800 0028   | 01BA 0028      | TCPIC10  | TCP Input Configuration 10          |  |

| 5800 002C   | 01BA 002C      | TCPIC11  | TCP Input Configuration11           |  |

| 5800 0030   | 01BA 0030      | TCPOUT   | TCP Output Parameters               |  |

| 5802 0000   | _              | TCPSP    | TCP Systematics and Parities Memory |  |

| 5804 0000   | _              | TCPEXT   | TCP Extrinsic Memory                |  |

| 5806 0000   | _              | TCPAP    | TCP Apriori Memory                  |  |

| 5808 0000   | _              | TCPINTER | TCP Interleaver Memory              |  |

| 580A 0000   | _              | TCPHD    | TCP Hard Decisions Memory           |  |

| _           | 01BA 0038      | TCPEXE   | TCP Execution                       |  |

# SM320C6414-EP, SM320C6415-EP, SM320C6416-EP FIXED-POINT DIGITAL SIGNAL PROCESSORS

SGUS043D-MAY 2003-REVISED SEPTEMBER 2008

Table 1-24. TCP Registers (C6414 Only) (continued)

| HEX ADDRESS |                | ACRONYM   | DECISTED   |  |

|-------------|----------------|-----------|------------|--|

| EDMA BUS    | PERIPHERAL BUS | ACRONTIVI | REGISTER   |  |

| _           | 01BA 0040      | TCPEND    | TCP Endian |  |

| _           | 01BA 0050      | TCPERR    | TCP Error  |  |

| _           | 01BA 0058      | TCPSTAT   | TCP Status |  |

#### 1.4.7 EDMA Channel Synchronization Events

The C64x EDMA supports up to 64 EDMA channels that service peripheral devices and external memory. Table 1-25 lists the source of C64x EDMA synchronization events associated with each of the programmable EDMA channels. For the C64x device, the association of an event to a channel is fixed; each of the EDMA channels has one specific event associated with it. These specific events are captured in the EDMA event registers (ERL, ERH), even if the events are disabled by the EDMA event enable registers (EERL, EERH). The priority of each event can be specified independently in the transfer parameters stored in the EDMA parameter RAM. For more detailed information on the EDMA module and how EDMA events are enabled, captured, processed, linked, chained, and cleared, etc., see the EDMA Controller chapter of the TMS320C6000 Peripherals Reference Guide (literature number SPRU190).

Table 1-25. SM320C64x EDMA Channel Synchronization Events<sup>(1)</sup>

| EDMA<br>CHANNEL | EVENT NAME       | EVENT DESCRIPTION                                                               |

|-----------------|------------------|---------------------------------------------------------------------------------|

| 0               | DSP_INT          | HPI/PCI-to-DSP interrupt (PCI peripheral supported on C6415 and C6416 only) (2) |

| 1               | TINT0            | Timer 0 interrupt                                                               |

| 2               | TINT1            | Timer 1 interrupt                                                               |

| 3               | SD_INTA          | EMIFA SDRAM timer interrupt                                                     |

| 4               | GPINT4/EXT_INT4  | GPIO event 4/External interrupt pin 4                                           |

| 5               | GPINT5/EXT_INT5  | GPIO event 5/External interrupt pin 5                                           |

| 6               | GPINT6/EXT_INT6  | GPIO event 6/External interrupt pin 6                                           |

| 7               | GPINT7/ EXT_INT7 | GPIO event 7/External interrupt pin 7                                           |

| 8               | GPINT0           | GPIO event 0                                                                    |

| 9               | GPINT1           | GPIO event 1                                                                    |

| 10              | GPINT2           | GPIO event 2                                                                    |

| 11              | GPINT3           | GPIO event 3                                                                    |

| 12              | XEVT0            | McBSP0 transmit event                                                           |

| 13              | REVT0            | McBSP0 receive event                                                            |

| 14              | XEVT1            | McBSP1 transmit event                                                           |