## 13-Channel Level Shifter With Op-Amp for LCD TVs and Monitors

Check for Samples: TPS65198

#### **FEATURES**

- Six CLK Outputs

- VST and RESET Outputs

- ODD and EVEN Outputs

- VGH\_F and VGH\_R Outputs

- Panel DISCHARGE Output

- Supports Forward and Reverse Operation

- Abnormal Operation Detection

- · Supports all Display Resolutions

- High-Speed Operational Amplifier

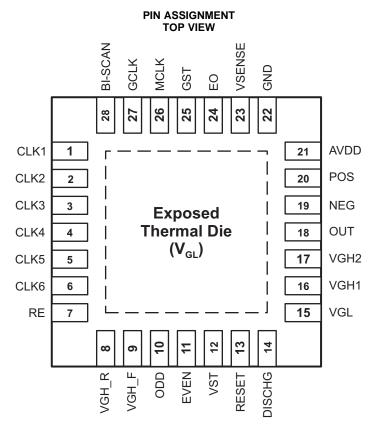

- 28-Pin 4×4 mm QFN Package

### **APPLICATIONS**

• LCD TVs and Monitors Using GIP Technology

#### DESCRIPTION

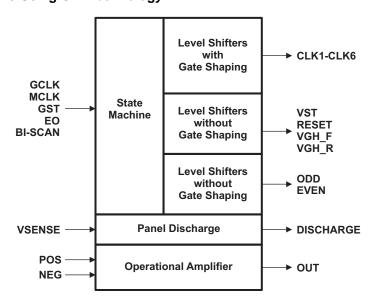

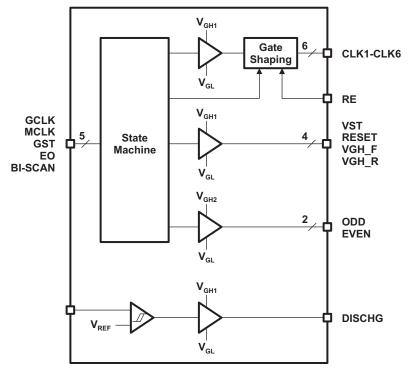

The TPS65198 provides an integrated level shifter solution, primarily intended for TV and monitor applications using GIP technology. The device features a built-in state machine that generates twelve output signals from the five input signals provided by the timing controller (T-CON). In addition, the TPS65198 generates a signal to discharge the display panel during power-down and a high-speed operational amplifier for buffering the system's  $V_{\rm COM}$  voltage.

Level shifter outputs are forced to a safe state (V<sub>GL</sub>) during abnormal panel operation, which is indicated by the T-CON using the EO and GST signals.

### ORDERING INFORMATION(1)

| TA            | ORDERING     | PACKAGE        | PACKAGE MARKING |

|---------------|--------------|----------------|-----------------|

| -40°C to 85°C | TPS65198RUYR | 28-Pin 4×4 QFN | TPS65198        |

(1) The device is supplied taped and reeled, with 3000 devices per reel.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

### **ABSOLUTE MAXIMUM RATINGS**(1)

over operating free-air temperature range (unless otherwise noted)

|             |                                                                                    | VALUE |     |      |

|-------------|------------------------------------------------------------------------------------|-------|-----|------|

|             |                                                                                    | MIN   | MAX | UNIT |

|             | GCLK, MCLK, GST, EO, BI-SCAN, VSENSE                                               |       | 7   |      |

|             | VGH1, VGH2, RE                                                                     |       | 40  |      |

|             | VGL                                                                                |       | -25 |      |

| Voltage (2) | VGH1 with respect to VGL, VGH2 with respect to VGL                                 |       | 60  | V    |

|             | POS, NEG, OUT, AVDD                                                                |       | 20  |      |

|             | CLK1, CLK2, CLK3, CLK4, CLK5, CLK6, VST, RESET, VGH-F, VGH_R, EVEN, ODD, DISCHARGE | -25   | 40  |      |

|             | Human Body Model                                                                   |       | 2   | kV   |

| ESD Rating  | Machine Model                                                                      |       | 200 | V    |

|             | Charged Device Model                                                               |       | 700 | V    |

|             | Ambient temperature, T <sub>A</sub>                                                | -40   | 85  | °C   |

|             | Junction temperature, T <sub>J</sub>                                               | -40   | 150 | °C   |

|             | Storage temperature, T <sub>STG</sub>                                              | -65   | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### THERMAL INFORMATION

|                  | THERMAL METRIC <sup>(1)</sup>                | TPS65198     | LIMITO |

|------------------|----------------------------------------------|--------------|--------|

|                  | THERMAL METRIC"                              | QFN (28) PIN | UNITS  |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 33.8         |        |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 23.6         |        |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 6.7          | °C/W   |

| ΨЈТ              | Junction-to-top characterization parameter   | 0.2          | C/VV   |

| ΨЈВ              | Junction-to-board characterization parameter | 6.7          |        |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | 2.1          |        |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> With respect to the GND pin.

### **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                                   |                                                 | MIN | TYP | MAX | UNIT |

|-----------------------------------|-------------------------------------------------|-----|-----|-----|------|

| $V_{GH1}$                         | Loyal shifter positive gupply valtage range     | 15  |     | 38  | V    |

| $V_{GH2}$                         | Level shifter positive supply voltage range     | 15  |     | 38  | V    |

| $V_{GL}$                          |                                                 | -3  |     | -23 | V    |

| V <sub>GH1</sub> -V <sub>GL</sub> | Level shifter negative supply voltage range     | 18  |     | 56  | V    |

| $V_{GH2}$ - $V_{GL}$              | Level shifter differential supply voltage range | 18  |     | 56  | V    |

| $AV_{DD}$                         | Op-amp positive supply voltage range            | 8   |     | 20  | V    |

| T <sub>A</sub>                    | Operating ambient temperature                   | -40 | 25  | 85  | °C   |

| T <sub>J</sub>                    | Operating junction temperature                  | -40 | 85  | 125 | °C   |

#### **ELECTRICAL CHARACTERISTICS**

$V_{GH1}$ = 28V,  $V_{GH2}$ = 28V,  $V_{GL}$ = -10V,  $AV_{DD}$  = 15V,  $T_A$  = -40°C to 85°C; Typical values are at 25°C (unless otherwise noted)

|                        | PARAMETER                                | TEST CONDITIONS                                                       | MIN T | YP MAX   | UNIT |

|------------------------|------------------------------------------|-----------------------------------------------------------------------|-------|----------|------|

| LEVEL SHIF             | TER                                      |                                                                       | •     |          |      |

| POWER SUF              | PPLY                                     |                                                                       |       |          |      |

| I <sub>GH1</sub>       | Positive supply current                  | GST, GCLK, MCLK, EO, BI-SCAN = 0 V                                    |       | 0.4      | mA   |

| I <sub>GH2</sub>       | Positive supply current                  | GST, GCLK, MCLK, EO, BI-SCAN = 0 V                                    | 0     | .06      | mA   |

| I <sub>GL</sub>        | Negative supply current                  | GST, GCLK, MCLK, EO, BI-SCAN = 0V                                     | 0     | ).13     | mA   |

|                        | 10404                                    | V <sub>GH1</sub> rising                                               |       | 9.2      | .,   |

| UVLO                   | UVLO threshold                           | V <sub>GH1</sub> falling                                              |       | 3.4      | V    |

| INPUT SIGN             | ALS (GCLK, MCLK, GST, EO, BI-SCAN)       |                                                                       |       |          |      |

| V <sub>IH</sub>        | High input voltage threshold             | Input rising                                                          |       | 1.4      | V    |

| V <sub>IL</sub>        | Low input voltage threshold              | Input falling                                                         | 0.8   |          | V    |

|                        |                                          | GST, GCLK, MCLK, EO = 0 V                                             |       | ±100     | nA   |

| I <sub>IN</sub>        | Input current                            | GST, GCLK, MCLK, EO = 3.3 V                                           |       | ±100     | nA   |

|                        |                                          | BI-SCAN = 3.3 V                                                       | 24    | 33 44    | μΑ   |

| R <sub>PULL-DOWN</sub> | BI-SCAN pin internal pull-down resistor  |                                                                       |       | 100      | kΩ   |

| LEVEL SHIF             | TERS (CLK1 to CLK8)                      |                                                                       | •     |          |      |

| _                      | High side ON resistance                  | I <sub>OUT</sub> = 10 mA, sourcing (high side)                        |       | 12       |      |

| r <sub>DS(ON)</sub>    | Low side ON resistance                   | I <sub>OUT</sub> = 10 mA, sinking (low side)                          |       | 7        | Ω    |

| t <sub>PLH</sub>       | GCLK rising edge propagation delay       | GCLK rising edge to CLK rising edge, C <sub>OUT</sub> = 150 pF        |       | 50 100   | ns   |

| t <sub>PHL</sub>       | MCLK falling edge propagation delay      | MCLK falling edge to CLK falling edge, C <sub>OUT</sub> = 150 pF      |       | 50 100   | ns   |

| LEVEL SHIF             | TERS (VST, RESET, ODD, EVEN, VGH_F, VGH_ | _R)                                                                   |       |          |      |

| _                      | High side ON resistance                  | I <sub>OUT</sub> = 10 mA, sourcing (high side)                        |       | 35       | 0    |

| r <sub>DS(ON)</sub>    | Low side ON resistance                   | I <sub>OUT</sub> = 10 mA, sinking (low side)                          |       | 16       | Ω    |

|                        | CCL K vising adds proposition dolor.     | GST rising edge to VST rising edge, C <sub>OUT</sub> = 150 pF         |       | 50 100   |      |

| t <sub>PLH</sub>       | GCLK rising edge propagation delay       | GST rising edge to RESET rising edge, C <sub>OUT</sub> = 150 pF       |       | 50 100   | ns   |

| •                      | CCLK falling adds propagation delay      | GST falling edge to VST falling edge, C <sub>OUT</sub> = 150 pF       |       | 50 100   | ns   |

| t <sub>PHL</sub>       | GCLK falling edge propagation delay      | GST falling edge to RESET falling edge, $C_{OUT} = 150 \text{ pF}$    |       | 50 100   | 115  |

|                        | EQ riging edge propagation delay         | EO rising edge to ODD falling edge, $C_{OUT} = 150 \text{ pF}$        |       | 50 100   | 20   |

| t <sub>PLH</sub>       | EO rising edge propagation delay         | EO rising edge to EVEN falling edge, C <sub>OUT</sub> = 150 pF        |       | 50 100   | ns   |

|                        | EO falling edge propagation delay        | EO falling edge to ODD rising edge, $C_{OUT} = 150 \text{ pF}$        |       | 50 100   | 20   |

| t <sub>PHL</sub>       | EO failing edge propagation delay        | EO falling edge to EVEN rising edge, C <sub>OUT</sub> = 150 pF        |       | 50 100   | ns   |

| t <sub>SU</sub>        | EO set-up time during abnormal operation | EO to GST rising edge                                                 |       | 50 100   | ns   |

| +                      | BI-SCAN rising edge propagation delay    | BI-SCAN rising edge to VGH_R rising edge, $C_{OUT} = 150 \text{ pF}$  |       | 50 100   | ns   |

| t <sub>PLH</sub>       | BI-SOAN Halling edge propagation delay   | BI-SCAN rising edge of VGH_F falling edge, C <sub>OUT</sub> = 150 pF  |       | 50 100   | 115  |

| t                      | RLSCAN falling edge propagation dolar    | BI-SCAN falling edge to VGH_F rising edge, C <sub>OUT</sub> = 150 pF  |       | 50 100   |      |

| t <sub>PHL</sub>       | BI-SCAN falling edge propagation delay   | BI-SCAN falling edge of VGH_F falling edge, C <sub>OUT</sub> = 150 pF |       | 50 100   | ns   |

| t <sub>12</sub>        | Bi-SCAN dead time                        | VGH_F falling edge to VGH_R rising edge, C <sub>OUT</sub> = 150 pF    | 20    | 500 1000 |      |

| t <sub>13</sub>        | DI-SCAIN DEAD LITTLE                     | VGH_R falling edge to VGH_F rising edge, C <sub>OUT</sub> = 150 pF    | 20    | 500 1000 | ns   |

| GATE SHAP              | PING (RE)                                |                                                                       |       |          |      |

| r <sub>DS(ON)</sub>    | Gate shaping resistance                  | Measured between active CLK channel and RE at 10 mA                   |       | 70       | Ω    |

| t <sub>PHL</sub>       | MCLK rising edge propagation delay       | MCLK rising edge to CLK falling edge, C <sub>OUT</sub> = 150 pF       |       | 65 100   | ns   |

### **ELECTRICAL CHARACTERISTICS (continued)**

$V_{GH1} = 28V, \ V_{GH2} = 28V, \ V_{GL} = -10V, \ AV_{DD} = 15V, \ T_A = -40^{\circ}C \ to \ 85^{\circ}C; \ Typical \ values \ are \ at \ 25^{\circ}C \ (unless \ otherwise \ noted)$

|                     | PARAMETER                              | TEST CONDITIONS                                                                     | MIN   | TYP | MAX      | UNIT |

|---------------------|----------------------------------------|-------------------------------------------------------------------------------------|-------|-----|----------|------|

| PANEL DI            | SCHARGE (DISCHG)                       | ·                                                                                   |       |     |          |      |

| V <sub>SENSEL</sub> | Discharge threshold voltage            | V <sub>SENSE</sub> falling                                                          | 1.275 | 1.5 | 1.725    | V    |

| V <sub>HYS</sub>    | Discharge threshold voltage hysteresis | V <sub>SENSE</sub> rising                                                           |       | 100 |          | mV   |

| I <sub>SENSE</sub>  | VSENSE input current                   | V <sub>SENSE</sub> = 2 V                                                            |       |     | ±1       | μΑ   |

| _                   | High side ON resistance                | I <sub>OUT</sub> = 10 mA, sourcing (high side)                                      |       | 35  |          | Ω    |

| r <sub>DS(ON)</sub> | Low side ON resistance                 | I <sub>OUT</sub> = 10 mA, sinking (low side)                                        |       | 16  |          | 12   |

| OPERATIO            | ONAL AMPLIFIER                         |                                                                                     |       |     | <u> </u> |      |

| I <sub>AVDD</sub>   | Supply current                         | V <sub>CM</sub> = 7.5 V, unity gain, no load                                        |       | 4   | 6        | mA   |

| V <sub>IO</sub>     | Input offset voltage                   | V <sub>CM</sub> = 7.5 V                                                             | -25   |     | 25       | mV   |

| I <sub>IB</sub>     | Input bias current                     | V <sub>CM</sub> = 7.5 V                                                             | -100  |     | 100      | nA   |

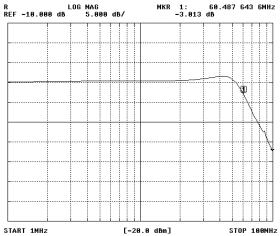

| BW                  | Unity gain 3 dB bandwidth              | $V_{CM} = 7.5 \text{ V}, V_{IN} = 63 \text{ mV}_{PP}, \text{ no load}$              |       | 70  |          | MHz  |

| $AV_{OL}$           | Open loop gain                         | V <sub>CM</sub> = 7.5 V, no load                                                    |       | 80  |          | dB   |

| CMRR                | Common-mode rejection ratio            | CMRR = $\Delta V_{CM} / \Delta V_{OS}$ , $V_{CM} = 5.5 \text{ V to } 9.5 \text{ V}$ |       | 90  |          | dB   |

| PSRR                | Power supply rejection ratio           | PSRR = $\Delta AV_{DD} / \Delta V_{OS}$ , $AV_{DD} = 8V$ to 20 V                    |       | 80  |          | dB   |

| _                   | High-side output resistance            | V <sub>POS</sub> = 9.5 V, V <sub>NEG</sub> = 7.5 V, I <sub>OUT</sub> = 10 mA        |       | 15  |          |      |

| r <sub>DS(ON)</sub> | Low-side output resistance             | V <sub>POS</sub> = 7.5 V, V <sub>NEG</sub> = 9.5 V, I <sub>OUT</sub> = 10 mA        |       | 35  |          | Ω    |

|                     | Dock cutout current                    | Unity gain, V <sub>POS</sub> = 7.25V, V <sub>OUT</sub> = 7.5V                       | 200   | 414 |          | A    |

| I <sub>PK</sub>     | Peak output current                    | Unity gain, $V_{POS} = 7.75V$ , $V_{OUT} = 7.5V$                                    | 200   | 344 |          | mA   |

Submit Documentation Feedback

### **PIN FUNCTIONS**

| PIN    | I   |     | DECODIDATION                                                |

|--------|-----|-----|-------------------------------------------------------------|

| NAME   | NO. | 1/0 | DESCRIPTION                                                 |

| CLK1   | 1   | 0   | CLK1 output                                                 |

| CLK2   | 2   | 0   | CLK2 output                                                 |

| CLK3   | 3   | 0   | CLK3 output                                                 |

| CLK4   | 4   | 0   | CLK4 output                                                 |

| CLK5   | 5   | 0   | CLK5 output                                                 |

| CLK6   | 6   | 0   | CLK6 output                                                 |

| RE     | 7   | 0   | Gate shaping resistor connection                            |

| VGH_R  | 8   | 0   | VGH_R output                                                |

| VGH_F  | 9   | 0   | VGH_F output                                                |

| ODD    | 10  | 0   | ODD output                                                  |

| EVEN   | 11  | 0   | EVEN output                                                 |

| VST    | 12  | 0   | VST output                                                  |

| RESET  | 13  | 0   | RESET output                                                |

| DISCHG | 14  | 0   | DISCHG output                                               |

| VGL    | 15  | Р   | Negative supply voltage                                     |

| VGH1   | 16  | Р   | Positive supply voltage for all outputs except ODD and EVEN |

| VGH2   | 17  | Р   | Positive supply voltage for ODD and EVEN outputs            |

| OUT    | 18  | 0   | Operational amplifier output                                |

| NEG    | 19  | 1   | Operational amplifier inverting input                       |

| POS    | 20  | 1   | Operational amplifier non-inverting input                   |

| AVDD   | 21  | Р   | Operational amplifier positive supply                       |

### **PIN FUNCTIONS (continued)**

| PIN                    |     |     | DESCRIPTION                                |  |

|------------------------|-----|-----|--------------------------------------------|--|

| NAME                   | NO. | 1/0 | DESCRIPTION                                |  |

| GND                    | 22  | Р   | Ground                                     |  |

| VSENSE                 | 23  | 1   | Voltage sense input for discharge function |  |

| EO                     | 24  | 1   | EO input                                   |  |

| GST                    | 25  | 1   | GST input                                  |  |

| MCLK                   | 26  | 1   | MCLK input                                 |  |

| GCLK                   | 27  | - 1 | GCLK input                                 |  |

| BI-SCAN                | 28  | 1   | BI-SCAN input                              |  |

| Exposed<br>Thermal Die | N/A | Р   | Connect to V <sub>GL</sub>                 |  |

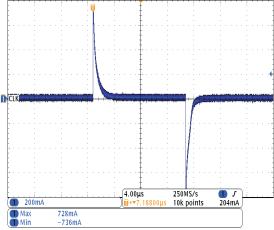

# TYPICAL CHARACTERISTICS TABLE OF GRAPHS

|                                 | TITLE                                                                                              | TEST CONDITIONS                   | FIGURE    |

|---------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------|-----------|

|                                 | CLKx                                                                                               |                                   | Figure 1  |

| Peak Output Current vs          | VST, RESET, ODD, EVEN, VGH_F, VGH_R                                                                | 10nF load                         | Figure 2  |

|                                 | DISCHARGE                                                                                          |                                   | Figure 3  |

|                                 | CLKx                                                                                               |                                   | Figure 4  |

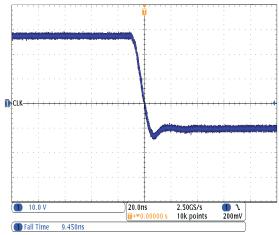

|                                 | VST, RESET, ODD, EVEN, VGH_F, VGH_R                                                                | 47Ω + 10nF load                   | Figure 5  |

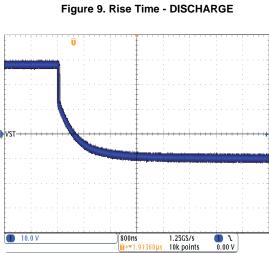

| Die e Time                      | DISCHARGE                                                                                          |                                   | Figure 6  |

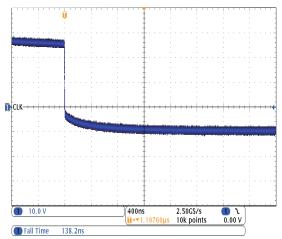

| Rise Time vs                    | CLKx                                                                                               |                                   | Figure 7  |

|                                 | VST, RESET, ODD, EVEN, VGH_F, VGH_R                                                                | 150 pF load                       | Figure 8  |

|                                 | DISCHARGE                                                                                          |                                   | Figure 8  |

|                                 | CLKx                                                                                               |                                   | Figure 10 |

|                                 | VST, RESET, ODD, EVEN, VGH_F, VGH_R                                                                | 47Ω + 10nF load                   | Figure 11 |

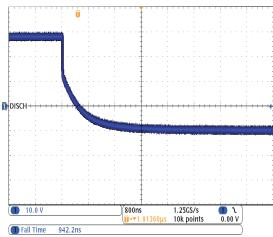

| Tall Time ve                    | DISCHARGE                                                                                          |                                   | Figure 12 |

| Fall Time vs                    | CLKx                                                                                               |                                   | Figure 13 |

|                                 | VST, RESET, ODD, EVEN, VGH_F, VGH_R                                                                | 150 pF load                       | Figure 14 |

|                                 | DISCHARGE                                                                                          |                                   | Figure 15 |

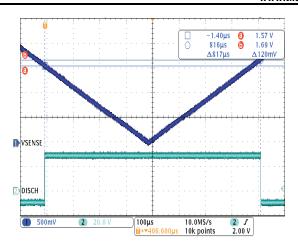

| / <sub>SENSE</sub> Threshold vs | VSENSE, DISCH                                                                                      |                                   | Figure 16 |

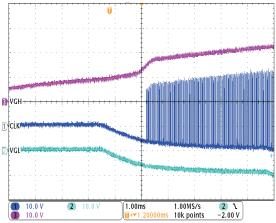

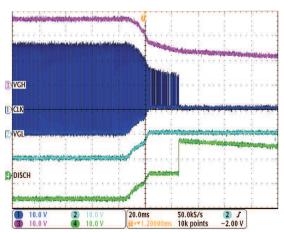

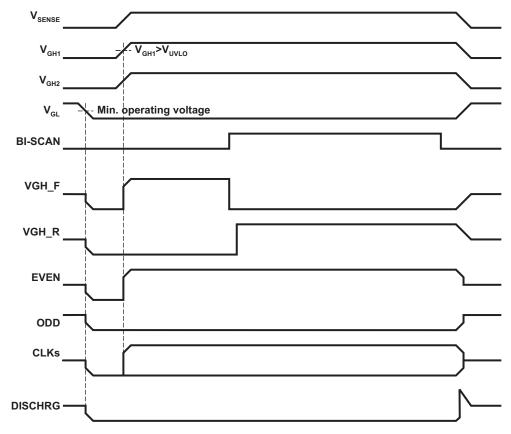

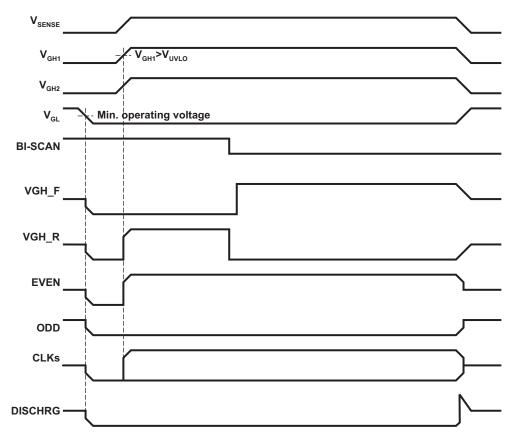

| Power-Up Sequence vs            | CLKs, VGH, VGL                                                                                     |                                   | Figure 17 |

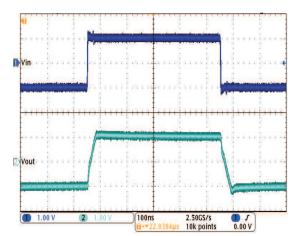

| Power-Down Sequence vs          | CLKs, VGH, VGL, DISCH                                                                              |                                   | Figure 18 |

| Small-Signal 3dB Bandwidth      | AVDD = 15 V, VCM = 7.5 V, $V_{IN}$ = 63 mV <sub>PP</sub> , Unity gain, $R_{FEEDBACK}$ = 0 $\Omega$ | No load                           | Figure 19 |

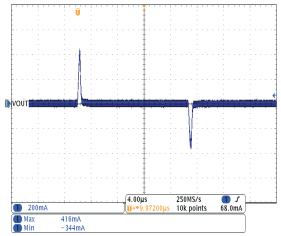

| Peak Output Current             | AVDD = 15 V, VCM = 7.5 V, $V_{IN}$ = 2 $V_{PP}$ , Open-loop                                        | 10 nF load                        | Figure 20 |

| Slew Rate                       | V <sub>OUT</sub> falling                                                                           | C <sub>OUT</sub> = 150pF, No Load | Figure 21 |

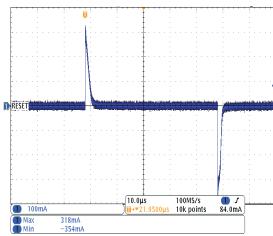

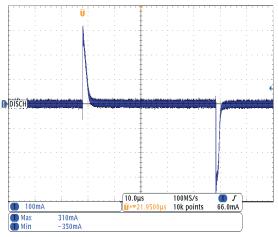

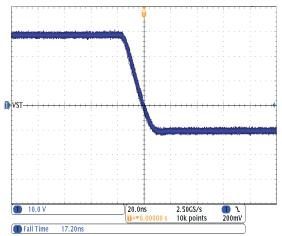

Figure 2. Peak Output Current - VST, RESET, etc.

Figure 3. Peak Output Current - DISCHARGE

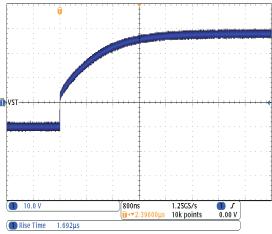

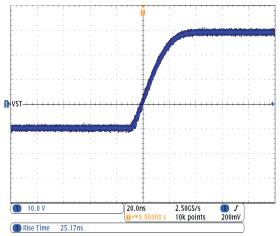

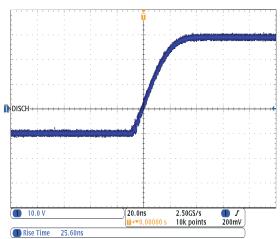

Figure 5. Rise Time - VST, RESET, etc.

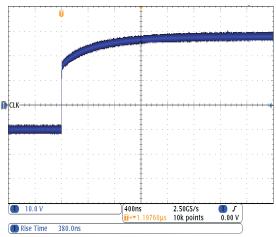

Figure 7. Rise Time - CLKs

Figure 4. Rise Time - CLKs

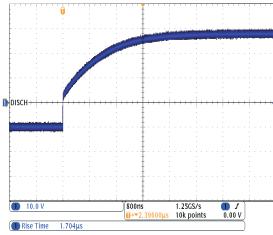

Figure 6. Rise Time - DISCHARGE

Figure 8. Rise Time - VST, RESET, etc.

Submit Documentation Feedback

1 Fall Time

915.7ns

Figure 11. Fall Time – VST, RESET, etc.

Figure 13. Fall Time - CLKs

Figure 10. Fall Time - CLKs

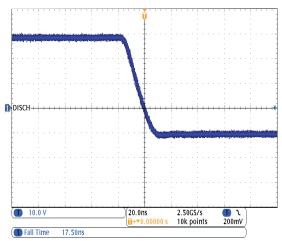

Figure 12. Fall Time - DISCHARGE

Figure 14. Fall Time - VST, RESET, etc.

Figure 15. Fall Time - DISCHARGE

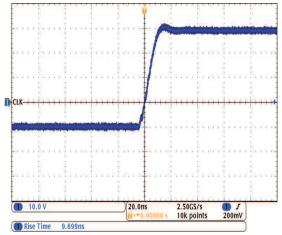

Figure 17. Power Up Sequence

Figure 19. Small-Signal 3dB Bandwidth

Figure 16.  $V_{SENSE}$  Threshold – VSENSE, DISCHARGE

Figure 18. Power Down Sequence

Figure 20. Peak Output Current

Submit Documentation Feedback

Figure 21. Slew Rate

#### **DETAILED DESCRIPTION**

#### **Level Shifter**

An internal block diagram of the level shifter block is shown in Figure 22.

Figure 22. Internal Block Diagram

#### **State Machine**

The state machine generates 12 output signals (all outputs except DISCHG) from the five input signals, as described below.

#### **GCLK**

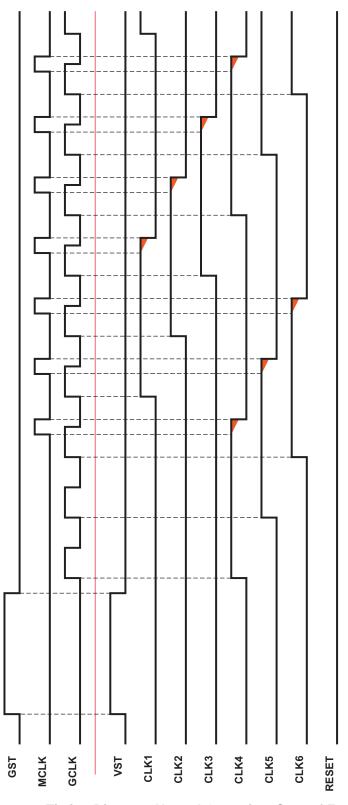

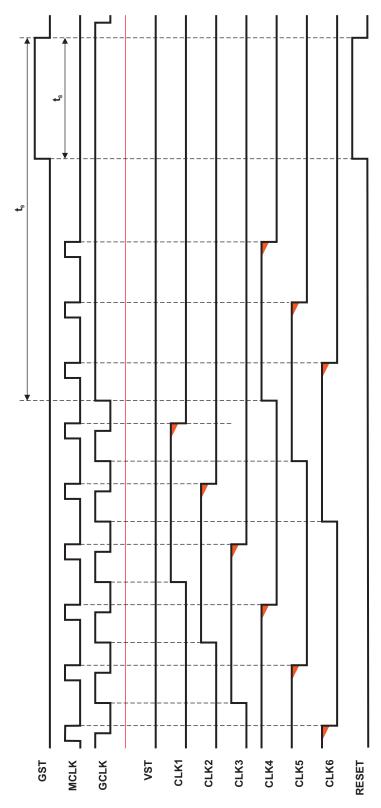

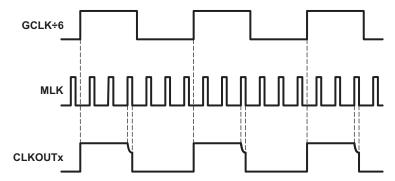

The rising edge of GCLK defines the rising edge of the active CLK channel. The phase difference between adjacent CLK signals is 60°, which means that the frequency of the output clocks is exactly one sixth the frequency of the GCLK signal (see Figure 23 to Figure 26).

The falling edge of GCLK has no effect.

#### **MCLK**

The rising edge of MCLK defines the start of gate-shaping for the active CLK channel. The phase difference between adjacent CLK signals is 60°, which means that the frequency of the output clocks is exactly one sixth the frequency of the MCLK signal (see Figure 23 to Figure 26).

The falling edge of MCLK defines the falling edge of the active CLK channel (and, by definition, the end of gate-shaping).

#### **GST**

The function of the GST signal depends on the state of GCLK when the GST pulse occurs. When GCLK is low (see Figure 23 and Figure 29, and section describing VST behavior):

- the rising edge of GST defines the rising edge of VST

- the falling edge of GST defines the falling edge of VST

- the GST signal indicates the start of a new frame, and resets all internal counters in the state machine

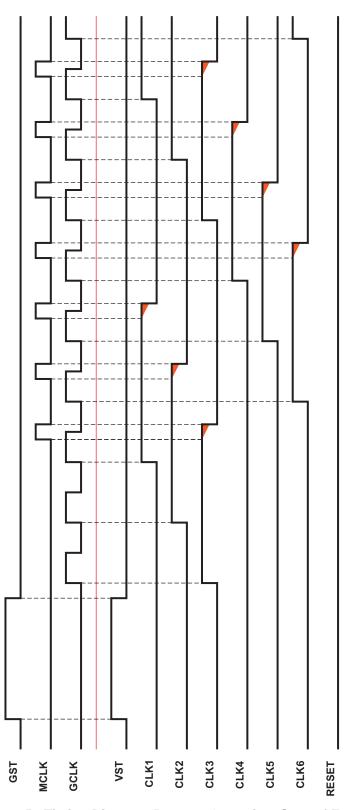

When GCLK is high (see Figure 24 and Figure 26 and section describing RESET behavior):

- · the rising edge of GST defines the rising edge of RESET

- the falling edge of GST defines the falling edge of RESET

#### EO

During normal operation a pulse applied to EO toggles the ODD and EVEN outputs (see section below describing the ODD and EVEN outputs).

See also section describing Abnormal Operation.

#### **BI-SCAN**

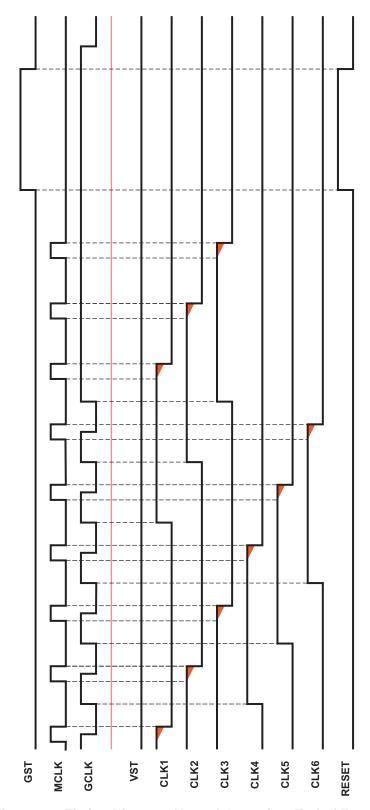

The BI-SCAN signal is used to select forward or reverse operation.

During forward operation (BI-SCAN=low), VGH\_F=high, VGH\_R=low and the clock signals are output in the following order:

(start of frame)

$$4-5-6-1-2-3-4-5-6-1-2-3.....4-5-6-1-2-3$$

(end of frame)

During reverse operation (BI-SCAN=high), VGH\_F=low, VGH\_R=high and the clock signals are output in the following order:

(start of frame)

$$3-2-1-6-5-4-3-2-1-6-5-4$$

(end of frame)

The BI-SCAN pin is internally pulled down by a  $100k\Omega$  (typical) resistor.

Figure 23. Timing Diagram: Normal Operation, Start of Frame

Figure 24. Timing Diagram: Normal Operation, End of Frame

Figure 25. Timing Diagram: Reverse Operation, Start of Frame

Figure 26. Timing Diagram: Reverse Operation, End of Frame

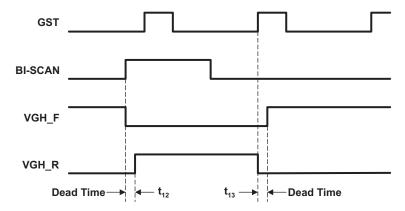

#### VGH F and VGH R

The VGH\_F and VGH\_R signals follow the BI-SCAN and GST inputs in accordance with Table 1.

**Table 1. Truth Table**

|          |         | INPUTS   |         | OUTPUTS     |       | NORMAL OCCURRENCE                       |

|----------|---------|----------|---------|-------------|-------|-----------------------------------------|

|          | BI-SCAN | GST      | Q       | VGH_F       | VGH_R |                                         |

|          | 1       | Х        | Х       | 0           | 1     | Reverse, power-up<br>Forward to reverse |

|          | 0       | Х        | 0       | 1           | 0     | Forward, power-up                       |

| Normal   | 0       | <b>↑</b> | 1       | 1           | 0     | Reverse to forward                      |

|          | 0       | 0        | 0       | 1           | 0     | Forward, power-down                     |

|          | 0       | 0        | 1       | 0           | 1     | Reverse, power-down                     |

| Abnormal |         | . 1      | Same as | Normal mode |       | •                                       |

The VGH\_F and VGH\_R outputs feature a dead time ( $t_{12}$  and  $t_{13}$ ) such that when BI-SCAN changes state VGH\_F and VGH\_R are temporarily both low before the active channel goes high (see Figure 27).

Figure 27. VGH\_F and VGH\_R Operation, Showing Dead Time

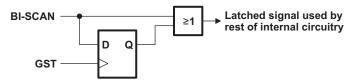

To ensure the VGH\_F and VGH\_R outputs remain valid during power-down (when the BI-SCAN signal may not be valid), the BI-SCAN signal is latched on every rising edge of GST (see Figure 28).

Figure 28. BI-SCAN Latching Scheme

The VGH\_F and VGH\_R channels follow a well defined characteristic during power-up and power-down (see Power Supply Sequencing).

#### **VST**

The VST signal follows the GST and GCLK input signals in accordance with the truth table below (see also Figure 23 to Figure 26).

|           | INF | UTS  | OUTPUT |

|-----------|-----|------|--------|

| OPERATION | GST | GCLK | VST    |

| Normal    | 1   | 0    | 1      |

|           | 1   | 1    | 0      |

|           | 0   | Х    | 0      |

|           | INP | INPUTS |     |

|-----------|-----|--------|-----|

| OPERATION | GST | GCLK   | VST |

| Abnormal  | Х   | Х      | 0   |

#### **RESET**

The RESET output is derived from the GST and GCLK signals in accordance with the truth table below (see also Figure 23 to Figure 26).

|           | INP | UTS  | OUTPUT |

|-----------|-----|------|--------|

| OPERATION | GST | GCLK | VST    |

| Normal    | 0   | Х    | 0      |

|           | 1   | 0    | 0      |

|           | 1   | 1    | 1      |

| Abnormal  | Х   | Х    | 0      |

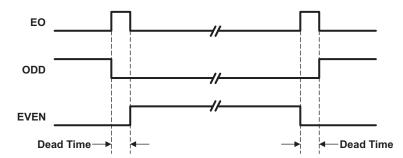

#### **ODD** and **EVEN**

The ODD and EVEN outputs toggle on the rising edge of the EO input signal in accordance with the truth table below. The pulse width of the EO signal defines a dead time during which both ODD and EVEN outputs are temporarily low (see Figure 29).

|           | INPUT | OUTPUTS               |                       |  |  |

|-----------|-------|-----------------------|-----------------------|--|--|

| OPERATION | EO    | EVEN                  | ODD                   |  |  |

| Power-Up  | X     | 1                     | 0                     |  |  |

| Normal    | 1     | toggle <sup>(1)</sup> | toggle <sup>(1)</sup> |  |  |

| Abnormal  | X     | 1                     | 0                     |  |  |

(1) With dead time

Figure 29. ODD and EVEN Generation, Showing Dead Time

#### **Abnormal Operation**

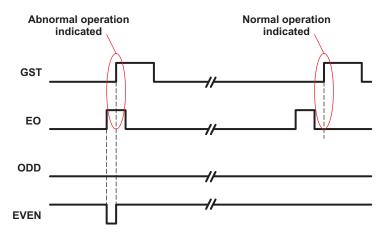

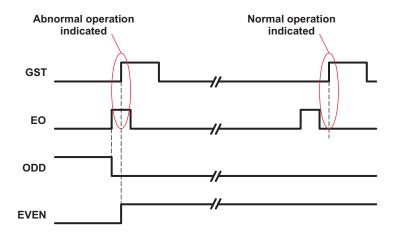

The TPS65198 supports abnormal operation. Abnormal operation is detected when EO is high during the rising edge of GST (see Figure 30), after which the level shifter outputs are forced to the following state:

- 1. CLK1-CLK6 low

- 2. VST, RESET low

Submit Documentation Feedback

- 3. ODD and EVEN in power-up state (EVEN high, ODD low) (2)

- 4. VGH F and VGH R not changed (outputs follow BI-SCAN input as in normal operation)

Normal operation is resumed the next time EO is low during the rising edge of GST. Upon exiting abnormal operation the state machine adopts its normal start-of-frame initial state.

Note that because of the dead time introduced by the EO signal during normal operation, a short low pulse may appear on the EVEN output when abnormal operation is detected (see Figure 30).

Figure 30. EO During Abnormal Operation, EVEN Initially High

Figure 31. EO During Abnormal Operation, EVEN Initially Low

### **CLK1 to CLK6**

The CLK outputs go high on the rising edge of GCLK and go low on the falling edge of MCLK. The CLK outputs' frequency is exactly one sixth of the GCLK and MCLK frequencies and adjacent CLK channels are separated by 60° phase difference.

The CLK outputs are generated in a specific order that depends on whether the device is operating in forward or reverse mode (see Figure 23 to Figure 26 and the section describing BI-SCAN operation).

#### **Gate Voltage Shaping**

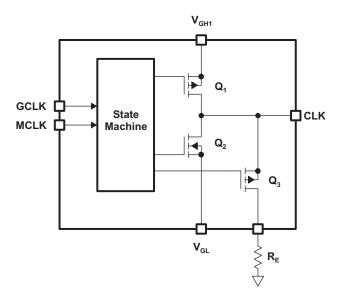

The clock outputs CLK1 to CLK6 support gate voltage shaping, which can help reduce image flickering in certain applications. A simplified block diagram of one of the clock channels is shown in Figure 32.

Figure 32. CLK Output Stage

- On the rising edge of the GCLK, the active channel's Q<sub>1</sub> is enabled and its Q<sub>2</sub> disabled; the output goes to V<sub>GH1</sub>.

- Gate voltage shaping starts on the rising edge of MCLK, which disables Q<sub>1</sub> and enables Q<sub>3</sub>. The LCD panel's pixel and storage capacitor now discharge through Q<sub>3</sub> at a rate determined by the external resistor R<sub>E</sub> (see Figure 33).

- On the falling edge of MCLK, Q<sub>3</sub> is disabled and Q<sub>2</sub> enabled; the output goes to V<sub>GL</sub>.

Figure 33. Gate Shaping Timing Diagram

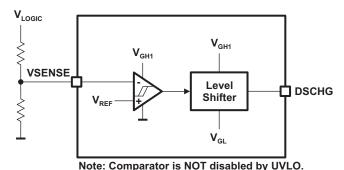

#### Panel Discharge

In addition to the 12 level shifter channels described above, the TPS65198 contains one output specifically intended for discharging the LCD panel during power-down (see Figure 34). The discharge channel uses the input signal connected to the VSENSE pin, which features a Schmitt trigger input stage. Figure 34 and Figure 35 show the discharge behavior during power-up and power-down.

Figure 34. Discharge Internal Block Diagram

When the discharge function is active, the level shifter outputs enter Abnormal Mode, as defined below.

#### Power Supply Sequencing (CLK1-CLK6, VST, RESET)

These outputs track  $V_{GL}$  when  $V_{GH1} < V_{UVLO}$  or  $V_{SENSE} < V_{REF}$  and operate normally when  $V_{GH1} > V_{UVLO}$  and  $V_{SENSE} > V_{REF}$  (see Figure 35 and Figure 36).

#### Power Supply Sequencing (ODD, EVEN)

EVEN tracks  $V_{GL}$  when  $V_{GH1} < V_{UVLO}$  and operates normally when  $V_{GH1} > V_{UVLO}$  and  $V_{SENSE} > V_{REF}$  (see Figure 35 and Figure 36). EVEN tracks  $V_{GH}$  when  $V_{SENSE} < V_{REF}$ .

ODD tracks  $V_{GL}$  when  $V_{GH1} < V_{UVLO}$  and operates normally when  $V_{GH1} > V_{UVLO}$  and  $V_{SENSE} > V_{REF}$  (see Figure 35 and Figure 36). ODD tracks  $V_{GL}$  when  $V_{SENSE} < V_{REF}$ .

#### Power Supply Sequencing (VGH\_F, VGH\_R)

VGH\_F and VGH\_R track  $V_{GL}$  when  $V_{GH1} < V_{UVLO}$  and operate normally when  $V_{GH1} > VUVLO$  (see Figure 35 and Figure 36).

During power-down these outputs remain in the state they were when the last rising edge of GST occurred.

#### **Power Supply Sequencing (Panel Discharge)**

- During power-up, when V<sub>SENSE</sub><V<sub>REF</sub>, DSCHG tracks V<sub>GL</sub>.

- During normal operation, when V<sub>SENSE</sub>>V<sub>REF</sub>, DSCHG tracks V<sub>GL</sub>.

- During power-down, when V<sub>SENSE</sub><V<sub>REF</sub>, DSCHG tracks V<sub>GH</sub>.

Figure 35. Power Supply Sequencing During Forward Operation

Figure 36. Power Supply Sequencing During Reverse Operation

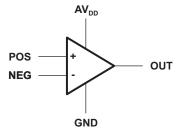

#### **Operational Amplifier**

The operational amplifier included in the TPS65198 has been optimized for buffering the  $V_{COM}$  voltage used in LCD panels. Its high slew rate, high output current and wide bandwidth enable it to drive the dynamic loads present on  $V_{COM}$ . Like most operational amplifiers, this amplifier may become unstable if a highly capacitive load is connected to its output. It is therefore recommended **not** to connect additional capacitance between  $V_{COM}$  and GND in an attempt to decouple it. Not only could this create stability problems, the high performance of the operational amplifier mean that such measures are unnecessary in typical applications.

Figure 37. Operational Amplifier Block Diagram

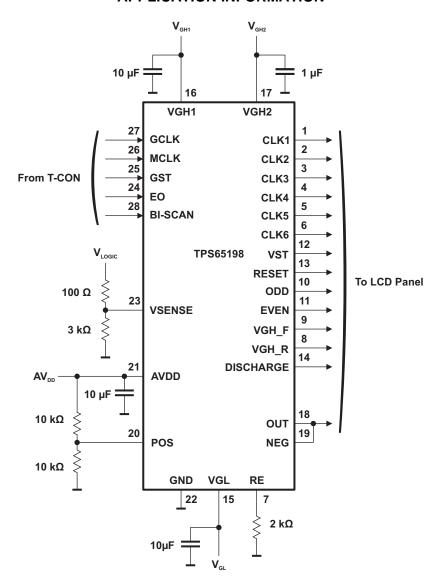

#### **APPLICATION INFORMATION**

Figure 38. Typical Application Circuit

### **REVISION HISTORY**

| Changes from Original (June 2011) to Revision A                                                                                                                                                            | Page |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| <ul> <li>Changed Condition statement of the Electrical Characaterisics table from T<sub>J</sub></li> <li>Changed Condition statement of the Electrical Characaterisics table from T<sub>J</sub></li> </ul> | **   |

| Added I <sub>PK</sub> spec to Elec Characteristics table.                                                                                                                                                  | 4    |

| Changes from Revision A (November 2011) to Revision B                                                                                                                                                      | Page |

| • Changed V <sub>IH</sub> spec from 2.0 MAX to 1.4 MAX in Typical Characteristics                                                                                                                          | 3    |

### PACKAGE OPTION ADDENDUM

28-Jan-2014

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|---------------------|--------------|----------------------|---------|

| TPS65198RUYR     | ACTIVE | WQFN         | RUY                | 28   | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | TPS<br>65198         | Samples |

| TPS65198RUYT     | ACTIVE | WQFN         | RUY                | 28   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | TPS<br>65198         | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

### **PACKAGE OPTION ADDENDUM**

28-Jan-2014

| In no event shall TI's liabili | ity arising out of such information | exceed the total purchase | price of the TI part(s) at issue | in this document sold by | TI to Customer on an annual basis. |

|--------------------------------|-------------------------------------|---------------------------|----------------------------------|--------------------------|------------------------------------|

|                                |                                     |                           |                                  |                          |                                    |

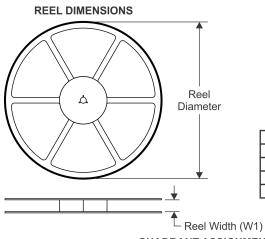

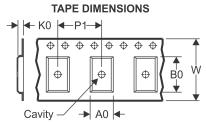

### **PACKAGE MATERIALS INFORMATION**

www.ti.com 22-Jan-2014

### TAPE AND REEL INFORMATION

| Α0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

|    | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| All differsions are normal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                     | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TPS65198RUYR               | WQFN            | RUY                | 28 | 3000 | 330.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

| TPS65198RUYT               | WQFN            | RUY                | 28 | 250  | 180.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

| TPS65198RUYT               | WQFN            | RUY                | 28 | 250  | 180.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

www.ti.com 22-Jan-2014

\*All dimensions are nominal

| 7 till difficilities are memilian |              |                 |      |      |             |            |             |

|-----------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                            | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| TPS65198RUYR                      | WQFN         | RUY             | 28   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS65198RUYT                      | WQFN         | RUY             | 28   | 250  | 210.0       | 185.0      | 35.0        |

| TPS65198RUYT                      | WQFN         | RUY             | 28   | 250  | 210.0       | 185.0      | 35.0        |

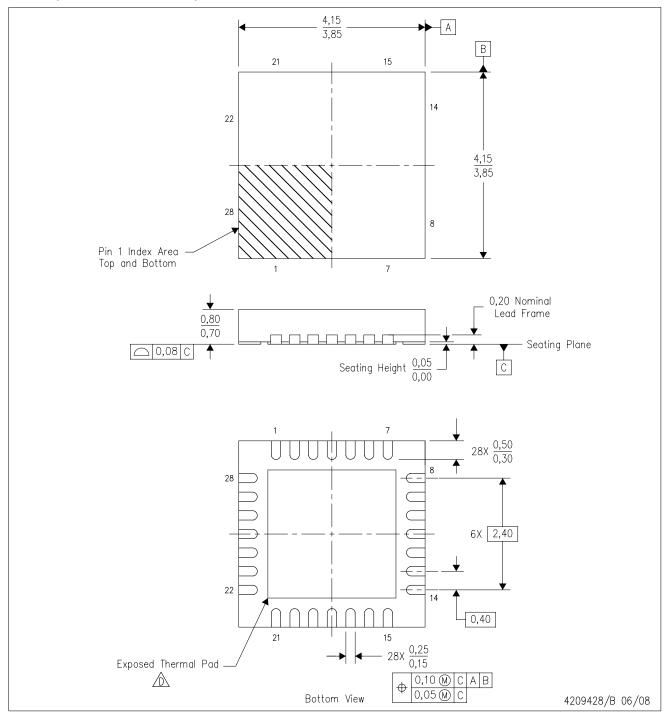

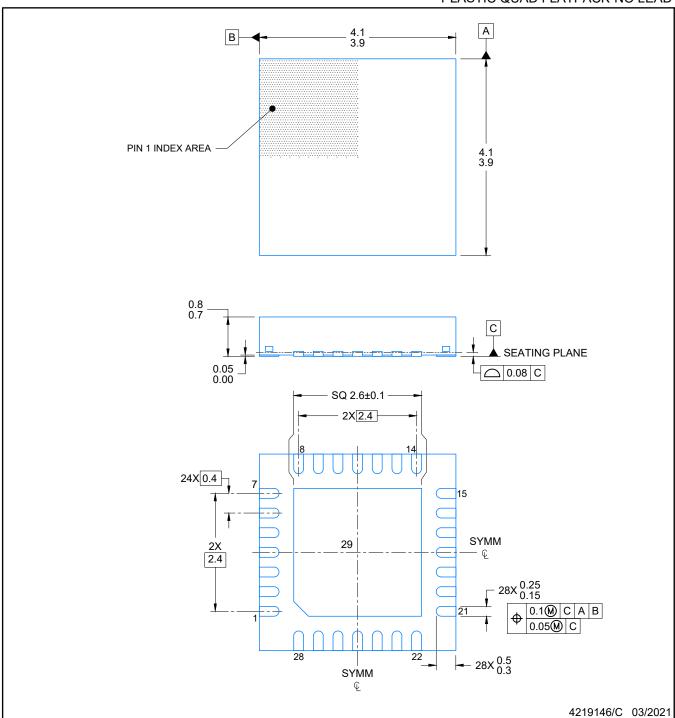

# RUY (S-PWQFN-N28)

### PLASTIC QUAD FLATPACK NO-LEAD

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994.

- B. This drawing is subject to change without notice.

- C. QFN (Quad Flatpack No-Lead) package configuration.

- The package thermal pad must be soldered to the board for thermal and mechanical performance. See the Product Data Sheet for details regarding the exposed thermal pad dimensions.

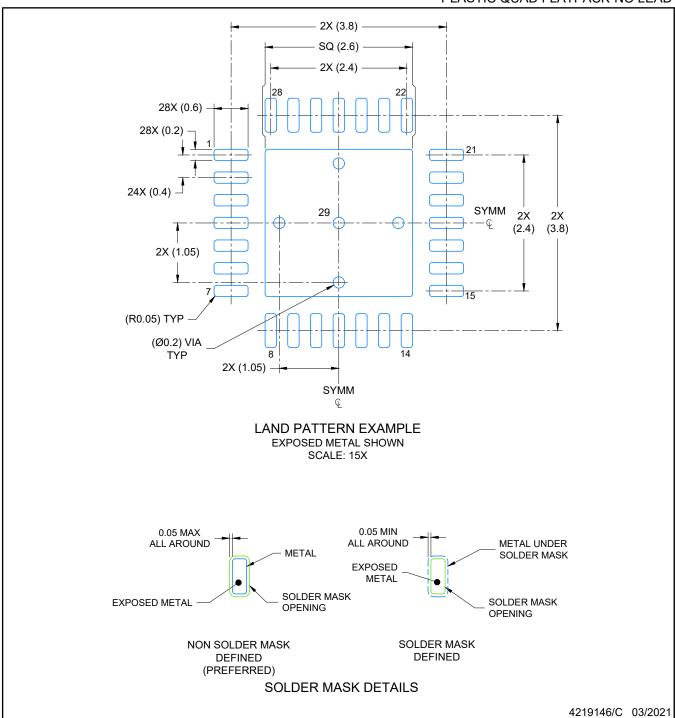

### RUY (S-PWQFN-N28)

PLASTIC QUAD FLATPACK NO-LEAD

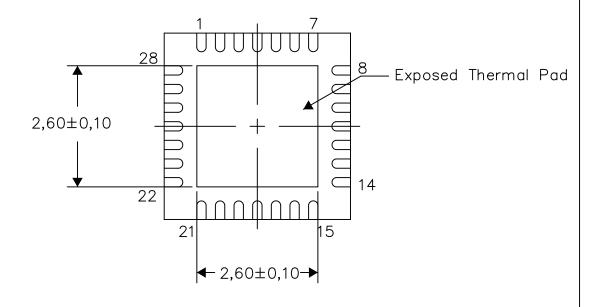

#### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No—Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Bottom View

Exposed Thermal Pad Dimensions

4209490/D 02/14

NOTE: All linear dimensions are in millimeters

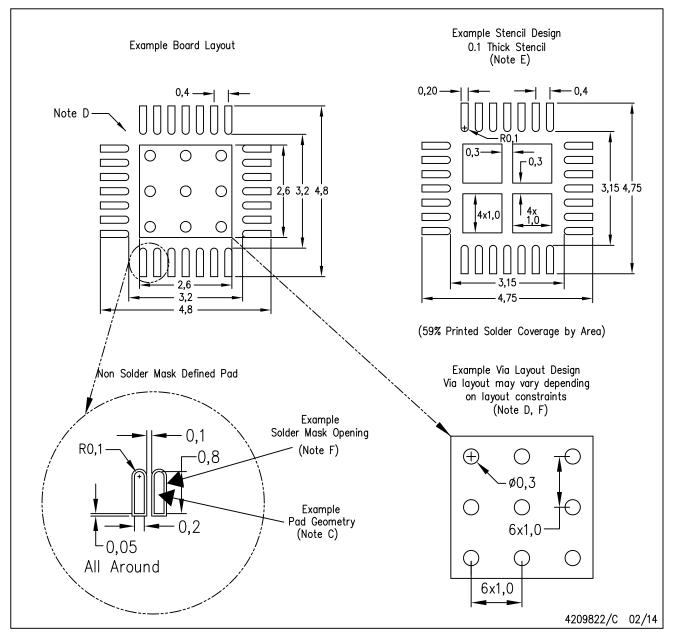

# RUY (S-PWQFN-N28)

### PLASTIC QUAD FLATPACK NO-LEAD

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat—Pack Packages, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for recommended solder mask tolerances and via tenting recommendations for vias placed in the thermal pad.

www.ti.com 9-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-----------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| TPS65198RUYR          | Active | Production    | WQFN (RUY)   28 | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | TPS<br>65198     |

| TPS65198RUYR.B        | Active | Production    | WQFN (RUY)   28 | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | TPS<br>65198     |

| TPS65198RUYT          | Active | Production    | WQFN (RUY)   28 | 250   SMALL T&R       | Yes             | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | TPS<br>65198     |

| TPS65198RUYT.B        | Active | Production    | WQFN (RUY)   28 | 250   SMALL T&R       | Yes             | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | TPS<br>65198     |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

- (3) RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

- (4) Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

- (5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

- (6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

### **PACKAGE OPTION ADDENDUM**

www.ti.com 9-Nov-2025

PLASTIC QUAD FLATPACK-NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

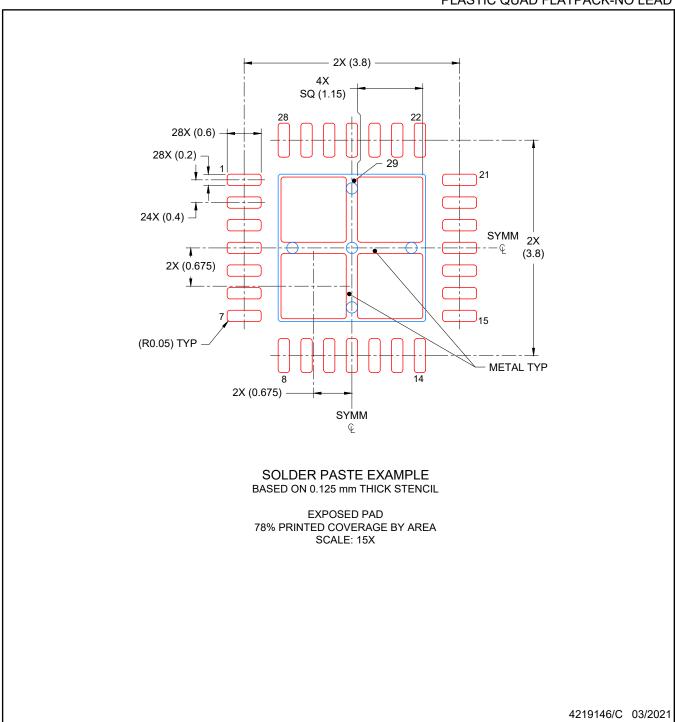

PLASTIC QUAD FLATPACK-NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUAD FLATPACK-NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025