# **JESD204B** Overview

#### **Texas Instruments High Speed Data Converter Training**

## Outline

- JESD204B Standard at a Glance

- Benefits / Cost

- Timing Signals

- Layers Overview (Transport, Link, Physical)

- Deterministic Latency

- Subclasses

## **JESD204B Standard at a Glance**

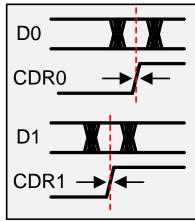

- A standardized serial interface between data converters (ADCs and DACs) and logic devices (FPGAs or ASICs)

- Serial data rates up to 12.5 Gbps

- Mechanism to achieve deterministic latency across the serial link

- Uses 8b/10b encoding for SerDes synchronization, clock recovery and DC balance

- JESD204B is a must for high density systems!

## **JESD204B Standard at a Glance**

| Feature                      | JESD204    | JESD204A   | JESD204B  |

|------------------------------|------------|------------|-----------|

| Introduction of Standard     | 2006       | 2008       | 2011      |

| Maximum Lane Rate            | 3.125 Gbps | 3.125 Gbps | 12.5 Gbps |

| Multiple Lane Support        | No         | Yes        | Yes       |

| Multi-Lane Synchronization   | No         | Yes        | Yes       |

| Multi-Device Synchronization | No         | Yes        | Yes       |

| Deterministic Latency        | No         | No         | Yes       |

| Harmonic Clocking            | No         | No         | Yes       |

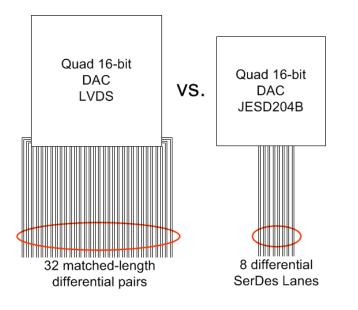

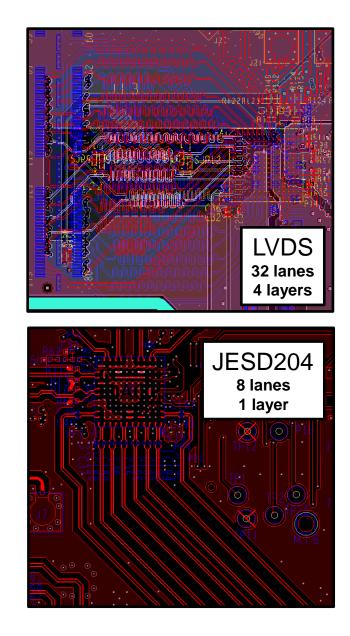

- Reduced/simplified PCB area

- Reduced package size

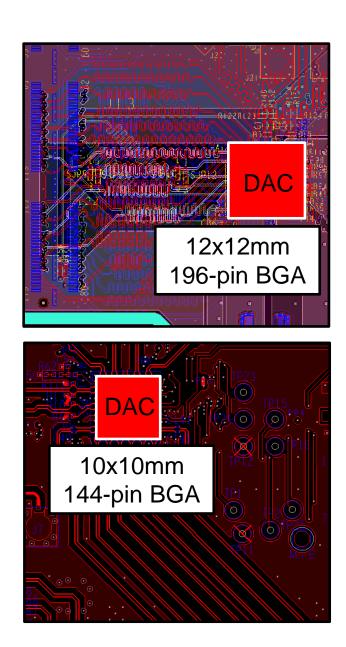

- Comparable power for large throughput

- Scalable to higher frequencies

- Simplified interface timing

- Standard interface

- Reduced/simplified PCB area

- Reduced package size

- Comparable power for large throughput

- Scalable to higher frequencies

- Simplified interface timing

- Standard interface

- Reduced/simplified PCB area

- Reduced package size

- Comparable power for large throughput

- Scalable to higher frequencies

- Simplified interface timing

- Standard interface

PLL

**50mA**

16mA

@ 10GB/s

**x4**

- Reduced/simplified PCB area

- Reduced package size

- Comparable power for large throughput

- Scalable to higher frequencies

- Simplified interface timing

- Standard interface

- Reduced/simplified PCB area

- Reduced package size

- Comparable power for large throughput

- Scalable to higher frequencies

- Simplified interface timing

- Standard interface

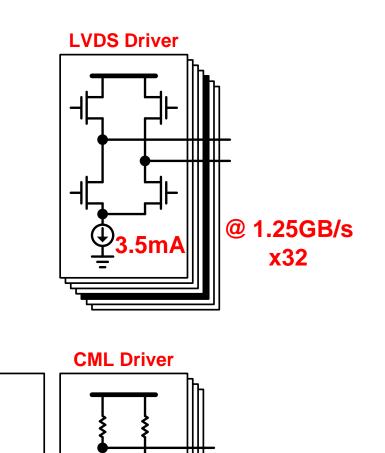

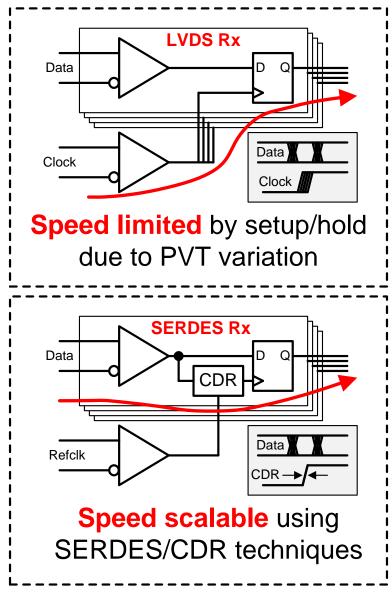

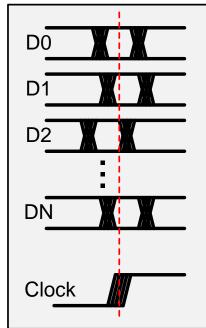

**SERDES Timing**

- Reduced/simplified PCB area

- Reduced package size

- Comparable power for large throughput

- Scalable to higher frequencies

- Simplified interface timing

- Standard interface

## **JESD204B Costs**

Increased interface latency

Increased FPGA firmware complexity / licensing

| File Edit Flow Tools Window Layout View Help                                    |           |                             |                                 | Q - Search commands         |             |

|---------------------------------------------------------------------------------|-----------|-----------------------------|---------------------------------|-----------------------------|-------------|

| 💐 😂   🕼 💷 급 🔛 🔌 🕨 法   🍪 🛞   ∑ 🇔 🖽 Defa                                          | lt Layout | - 🗶 🔆 📜                     | <b>(3</b>                       |                             | Read        |

| Project Manager - project_1                                                     |           |                             |                                 |                             | >           |

| Sources _ 🗆 🗠 ×                                                                 | : 🔊 ISI   | EImportLog 🗙 🔞 P2_TRA       | NS_Sub2_1ln_7p4G_LM97           | 837EVM_top.v × 	 •          |             |

| < 🔀 🖨 🔁 🔂 🤉 🖪                                                                   | E C:/     | Users/a0413779/Desktop/P3_1 | TRANS_Sub2_1ln_7p4G_LM978       | 37EVM_20121227/P3_TRANS_Sub | 52_1ln_7p4G |

| Design Sources (2)                                                              | 14        | 9                           |                                 |                             | -           |

| B W P2 TRANS Sub2 1In 7p4G LM97837EVM top (P2 TRANS                             | 15        | 0 jesd204_v2_1_rx_bloc      | k #(.C_S_AXI_BASE(0))           | i_jesd204_v2_1_rx_bloc      | :k (        |

| i_jesd204_v2_1_rx_block - jesd204_v2_1_rx_block                                 |           | 1 .refclk0p                 | (devclkAp),                     |                             |             |

| i_data_arrange_rx - data_arrange_rx                                             | 4, 15     | 2 .refclk0n                 | (devclkAn),                     |                             |             |

| i_odata_src_mux_rx - odata_src_mux_rx                                           | 15        |                             | (1'b0),                         |                             |             |

| i_gi_status_rx - status_rx<br>i_input_bufs_rx - input_bufs_rx (input_bufs_rx.v) | 12        |                             | (1'b0),                         |                             |             |

|                                                                                 | 15        |                             | (mreset_i),                     |                             |             |

| ⊕-                                                                              | × 15      |                             |                                 |                             |             |

| 🔃 🧰 Constraints (1)                                                             | // 15     |                             | (rxp),                          |                             |             |

| Gimulation Sources (1)                                                          | 15        | 8 .rxn                      | (rxn),                          |                             |             |

|                                                                                 |           |                             |                                 |                             |             |

| Hierarchy Libraries Compile Order                                               | 4.1       |                             | (devclkB_g),                    |                             |             |

| Sources 💡 Templates                                                             | a 16      |                             | (~mreset_i),<br>(32'h00000000), |                             |             |

| Source File Properties                                                          | 16        |                             | (1'b0),                         |                             |             |

|                                                                                 | - 10      |                             | (),                             |                             |             |

|                                                                                 | 16        |                             | (32'h00000000).                 |                             |             |

| 🛞 output_bufs_rx.v                                                              | 16        |                             | (4'b0000),                      |                             |             |

|                                                                                 | - 16      |                             | (1'b0),                         |                             |             |

| Location: C:/Users/a0413779/Desktop/P3_TRANS_Sub2_1ln_7p4G_LMS                  |           |                             | 0,                              |                             |             |

| Type: Verilog                                                                   | 2 16      | 9 .s_axi_bresp              | 0,                              |                             |             |

|                                                                                 | 17        | <pre>0 .s_axi_bvalid</pre>  | 0,                              |                             |             |

| Library: xil_defaultib                                                          | 17        | 1 .s_axi_bready             | (1'b0),                         |                             |             |

| Size: 14.7 KB                                                                   | 17        |                             | (32'h0000000),                  |                             |             |

| Modified: Thursday 12/27/12 04:51:36 PM +                                       | 17        |                             | (1'b0),                         |                             |             |

| ۰ III ۲                                                                         | 17        |                             | 0,                              |                             |             |

| General Properties                                                              | 17        | S saxindata                 |                                 |                             | •           |

|                                                                                 |           |                             |                                 |                             |             |

| 📟 🗭 🔍 Log                                                                       |           |                             |                                 |                             |             |

|                                                                                 |           |                             |                                 | 174:0 Insert                | Verilog     |

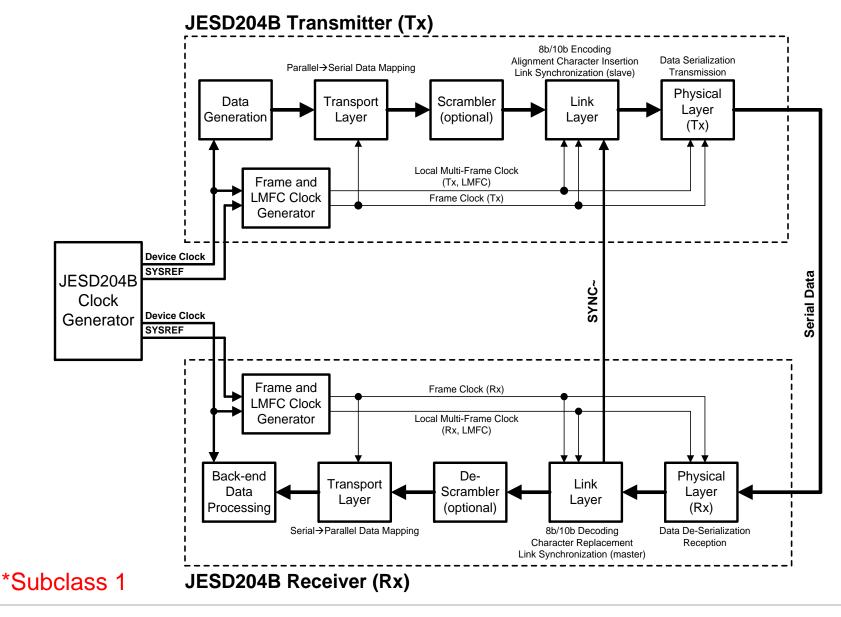

#### **JESD204B Link Data Flow and Protocol Layer Diagram**

# **JESD204 Timing Signals/Terminology**

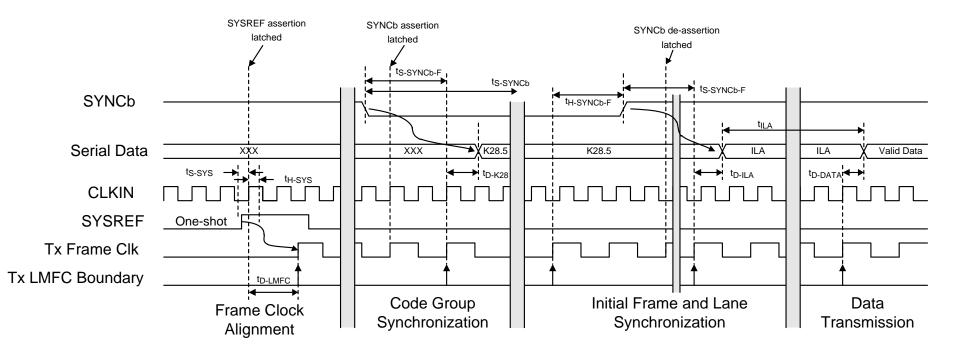

### Frame Clock

- Data frame of the transport layer is aligned to the frame clock

- Frame clock period in all the TX and RX devices must be identical

## Local Multi-Frame Clock (LMFC)

- Multi-Frame is composed of 'K' Frames

- LMFC is aligned to the multi-frame boundary

- Acts as a low-frequency reference to resolve frame clock phase ambiguity across multiple devices

- LMFC period in all TX and RX devices must be identical

# **JESD204 Timing Signals/Terminology**

### **Device Clock**

• System clock from which the device's frame, sampling, LMFC clocks are derived (externally applied)

## Sample Clock

- Internal conversion clock of data converter

- Derived from Device Clock (via multipliers or dividers)

- Relationship to frame clock depends on packing of data into frame

## SYSREF

- Timing phase reference from which LMFC clocks are generated in subclass 1 implementations (externally applied)

- Must be source synchronous with Device Clock

- Rising edge transition determines LMFC alignment

# **JESD204 Timing Signals/Terminology**

## SYNC

- Unidirectional, Receiver-to-Transmitter

- Active low signaling, often referred to as 'SYNC~' or 'SYNCb'

- Mainly used for device synchronization requests and error reporting

- Aligns LMFC phase in Subclass 2 devices

- Options available for distributing SYNC to multiple devices

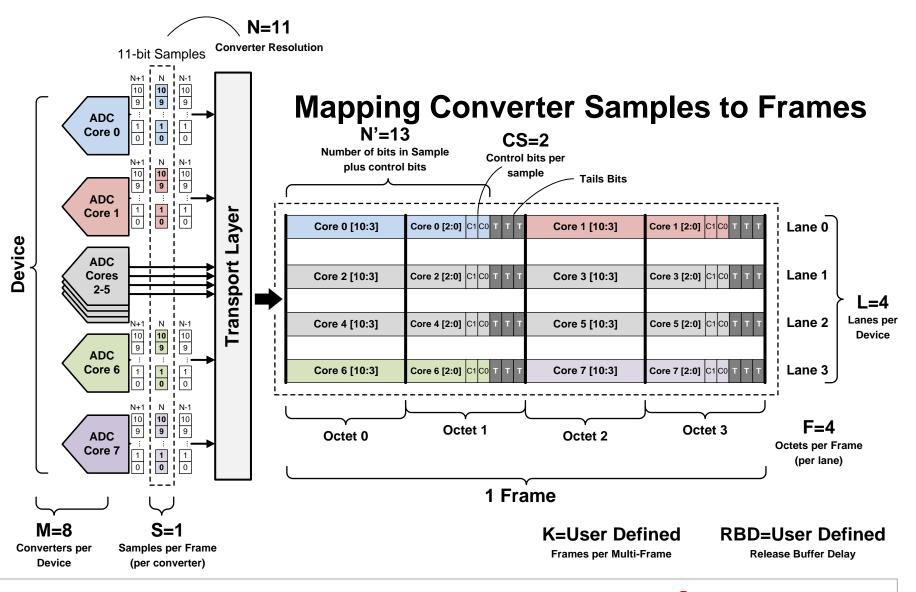

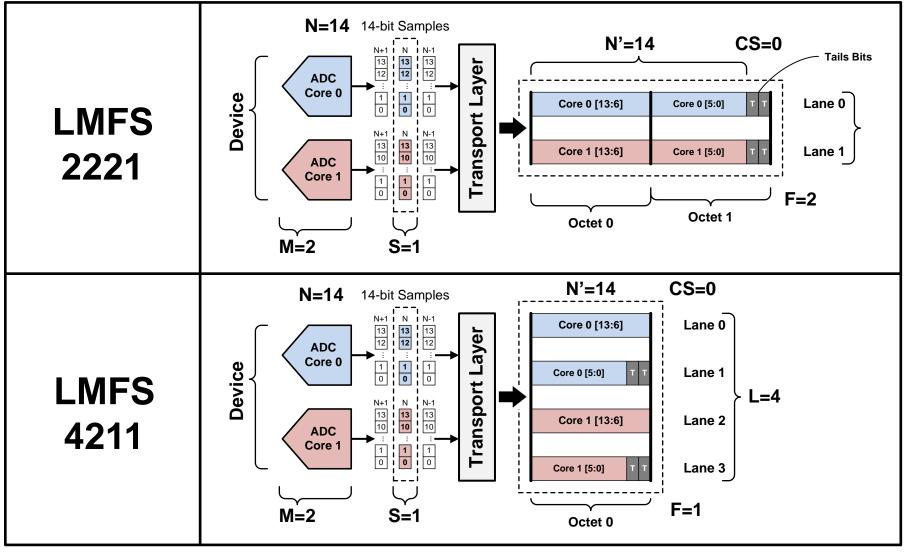

## **Transport Layer Overview**

- Maps the data  $\rightarrow$  octets  $\rightarrow$  frames consisting of multiple octets

- Adds optional control bits to samples if needed

- Distinguishes the possible combinations of device/links/lanes/etc.

- Important parameters associated with transport layer include:

- L # of lanes per converter device

- M # of converters per device

- F # of octets per frame (per lane)

- S # of samples per converter per frame clock cycle

- CS # of control bits per conversion sample

## **Transport Layer (Generic Example)**

## Transport Layer (ex. ADS42JB49)

Note: Actual ADS42JB49 implementation defines N'=16 and inserts 0's into LSBs instead of defining tail bits

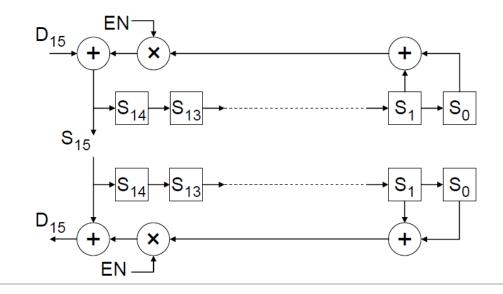

## Scrambling

- Scrambling randomizes data and spreads the spectral content to reduce spectral peaks that could cause EMI and interference problems

- Transport layer output may be optionally scrambled with the polynomial:  $1 + x^{14} + x^{15}$

- The RX descrambler self-synchronizes after receiving only two octets

- TX supports early-synchronization option that allows descrambler to self-synchronize during ILA

## **Data Link Layer**

- 8b/10b Encoding

- Link Establishment, including frame and lane alignment

- Link Monitoring using control symbols

## Data Link Layer: 8b/10b Encoding

- Encodes 8-bit "octets" into 10-bit symbols

- Octet to symbol mapping depends on running disparity (RD)

- Coding provides many bit-transitions to enable CDR techniques

- DC balancing enables AC coupling

|      | 5b/6b code |         |         |        |       |         |         |

|------|------------|---------|---------|--------|-------|---------|---------|

| h    | nput       | RD = -1 | RD = +1 | In     | put   | RD = -1 | RD = +1 |

|      | EDCBA      | abo     | dei     |        | EDCBA | abcdei  |         |

| D.00 | 00000      | 100111  | 011000  | D.16   | 10000 | 011011  | 100100  |

| D.01 | 00001      | 011101  | 100010  | D.17   | 10001 | 100     | 011     |

| D.02 | 00010      | 101101  | 010010  | D.18   | 10010 | 010     | 011     |

| D.03 | 00011      | 110     | 001     | D.19   | 10011 | 110     | 010     |

| D.04 | 00100      | 110101  | 001010  | D.20   | 10100 | 001     | 011     |

| D.05 | 00101      | 101     | 001     | D.21   | 10101 | 101010  |         |

| D.06 | 00110      | 011     | 001     | D.22   | 10110 | 011     | 010     |

| D.07 | 00111      | 111000  | 000111  | D.23 † | 10111 | 111010  | 000101  |

| D.08 | 01000      | 111001  | 000110  | D.24   | 11000 | 110011  | 001100  |

| D.09 | 01001      | 100     | 101     | D.25   | 11001 | 100     | 110     |

| D.10 | 01010      | 010     | 101     | D.26   | 11010 | 010     | 110     |

| D.11 | 01011      | 110     | 100     | D.27 † | 11011 | 110110  | 001001  |

| D.12 | 01100      | 001     | 101     | D.28   | 11100 | 001     | 110     |

| D.13 | 01101      | 101     | 100     | D.29 † | 11101 | 101110  | 010001  |

| D.14 | 01110      | 011     | 100     | D.30 † | 11110 | 011110  | 100001  |

| D.15 | 01111      | 010111  | 101000  | D.31   | 11111 | 101011  | 010100  |

|      |            |         |         | K.28   | 11100 | 001111  | 110000  |

| 3b/4b code |     |         |         |         |     |         |         |

|------------|-----|---------|---------|---------|-----|---------|---------|

| Inpu       | t   | RD = -1 | RD = +1 | Inpu    | ut  | RD = -1 | RD = +1 |

|            | HGF | fg      | hj      |         | HGF | fg      | hj      |

| D.x.0      | 000 | 1011    | 0100    | K.x.0   | 000 | 1011    | 0100    |

| D.x.1      | 001 | 10      | 01      | K.x.1‡  | 001 | 0110    | 1001    |

| D.x.2      | 010 | 01      | 0101    |         | 010 | 1010    | 0101    |

| D.x.3      | 011 | 1100    | 0011    | K.x.3‡  | 011 | 1100    | 0011    |

| D.x.4      | 100 | 1101    | 0010    | K.x.4   | 100 | 1101    | 0010    |

| D.x.5      | 101 | 10      | 10      | K.x.5‡  | 101 | 0101    | 1010    |

| D.x.6      | 110 | 01      | 10      | K.x.6‡  | 110 | 1001    | 0110    |

| D.x.P7 †   | 111 | 1110    | 0001    |         |     |         |         |

| D.x.A7 †   | 111 | 0111    | 1000    | K.x.7 † | 111 | 0111    | 1000    |

| Control symbols |     |     |           |             |             |  |  |

|-----------------|-----|-----|-----------|-------------|-------------|--|--|

| Input           |     |     |           | RD = -1     | RD = +1     |  |  |

|                 | DEC | HEX | HGF EDCBA | abcdei fghj | abcdei fghj |  |  |

| K.28.0          | 28  | 1C  | 000 11100 | 001111 0100 | 110000 1011 |  |  |

| K.28.1 †        | 60  | 3C  | 001 11100 | 001111 1001 | 110000 0110 |  |  |

| K.28.2          | 92  | 5C  | 010 11100 | 001111 0101 | 110000 1010 |  |  |

| K.28.3          | 124 | 7C  | 011 11100 | 001111 0011 | 110000 1100 |  |  |

| K.28.4          | 156 | 9C  | 100 11100 | 001111 0010 | 110000 1101 |  |  |

| K.28.5 †        | 188 | BC  | 101 11100 | 001111 1010 | 110000 0101 |  |  |

| K.28.6          | 220 | DC  | 110 11100 | 001111 0110 | 110000 1001 |  |  |

| K.28.7 ‡        | 252 | FC  | 111 11100 | 001111 1000 | 110000 0111 |  |  |

| K.23.7          | 247 | F7  | 111 10111 | 111010 1000 | 000101 0111 |  |  |

| K.27.7          | 251 | FB  | 111 11011 | 110110 1000 | 001001 0111 |  |  |

| K.29.7          | 253 | FD  | 111 11101 | 101110 1000 | 010001 0111 |  |  |

| K.30.7          | 254 | FE  | 111 11110 | 011110 1000 | 100001 0111 |  |  |

## **Data Link Layer: Link Establishment**

- Link Establishment accomplishes TX and RX synchronization

- Code Group Synchronization (CGS)

- Initial Frame Synchronization

- Initial Lane Synchronization

## **Physical Layer: Serial Lanes**

- Physical layer defines the electrical and timing characteristics of data transfer

- Point-to-point, unidirectional serial interface

- AC or DC compliance

- 3 signal speed-grade variants

- Performance limited by SERDES, CDR and driver/receiver blocks

| Parameter                      | LV-OIF-Sx15              | LV-OIF-6G-SR             | LV-OIF-11G-SR        |

|--------------------------------|--------------------------|--------------------------|----------------------|

| Data Rates                     | 312.5Mbps –<br>3.125Gbps | 312.5Mbps -<br>6.375Gbps | 312.5Mbps – 12.5Gbps |

| Differential Output<br>Voltage | 500 – 1000 (mV)          | 400 – 750 (mV)           | 360 – 770 (mV)       |

| Bit Error Rate (BER)           | ≤ 1e-12                  | ≤ 1e-15                  | ≤ 1e-15              |

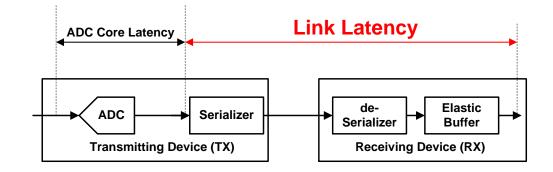

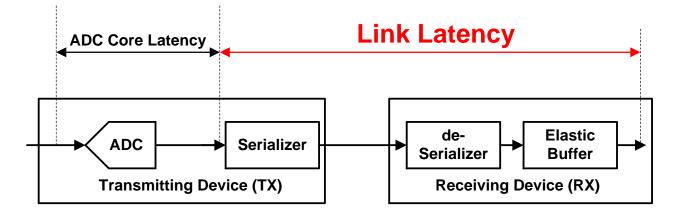

## **Deterministic Latency: Motivation**

- Applications are often sensitive to the variation of system latency

- Synchronous sampling

- Multi-channel phase array alignment

- Gain control loop stability

- JESD204 and JESD204A do not achieve known/constant latency across the link across temp/supply/reboot variation

- Providing support for devices with internal clock dividers introduces potential for even more latency uncertainty

## **Deterministic Latency: Achieved**

- JESD204B achieves deterministic latency: known/constant latency

- Subclass 0: DL not achieved

- Subclass 1: DL achieved using SYSREF with strict timing

- Subclass 2: DL achieved using SYNC~ with strict timing

- Deterministic Latency achieved with these architecture features

- SYSREF or SYNC~ are used to provide a deterministic reference phase to all devices for synchronization

- LMFC provides a low frequency reference to avoid frame clock phase ambiguity in the presence of link delay changes

- RX has an "elastic buffer" that absorbs link delay variation

- Texas Instruments recommends/supports subclass 1

- LMFC phase easier to control with source synchronous SYSREF than with system synchronous SYNC~

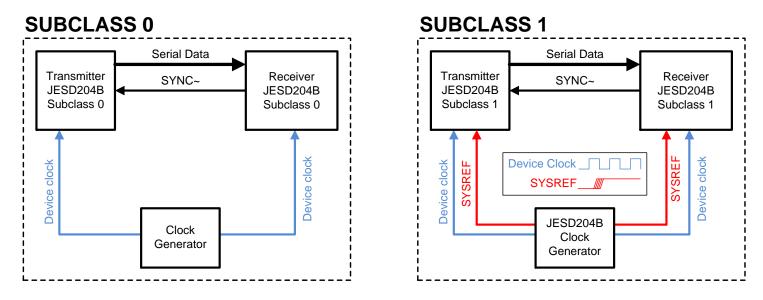

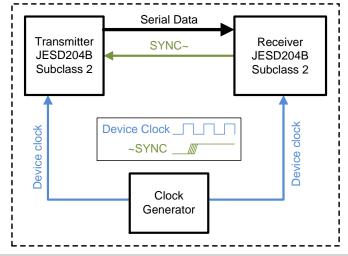

## **JESD204B Subclasses**

• Subclass distinction: Whether to, and how to achieve time reference alignment (as a requirement for deterministic link latency)

|                                             | Subclass 0 | Subclass 1                                                | Subclass 2                                               |

|---------------------------------------------|------------|-----------------------------------------------------------|----------------------------------------------------------|

| Deterministic<br>Latency<br>Supported?      | No         | Yes                                                       | Yes                                                      |

| How to achieve<br>Deterministic<br>Latency? | N/A        | Time reference<br>(LMFC) alignment<br>using <b>SYSREF</b> | Time reference<br>(LMFC) alignment<br>using <b>~SYNC</b> |

## **Subclass Signaling Requirements**

**SUBCLASS 2**

## **Choosing a Subclass**

|                                     | Subclass 0                                                                      | Subclass 1                      | Subclass 2                |  |

|-------------------------------------|---------------------------------------------------------------------------------|---------------------------------|---------------------------|--|

| JESD204A<br>Backward Compatible?    | Yes                                                                             | No                              | No                        |  |

| Deterministic Latency<br>Supported? | No                                                                              | Yes                             | Yes, but speed<br>limited |  |

| SYSREF Required?                    | No                                                                              | Yes                             | No                        |  |

| Clock and Sync Signals              | Device Clock<br>SYNC~                                                           | Device Clock<br>SYSREF<br>SYNC~ | Device Clock<br>SYNC~     |  |

| SYNC~ is Timing Critical?           | No                                                                              | No                              | Yes                       |  |

| Interface Hardware<br>Complexity    | Least                                                                           | Most                            | Moderate                  |  |

| Link Latency                        | 8-100 sample clocks (non-deterministic)<br>15-120 sample clocks (deterministic) |                                 |                           |  |

## **Subclass by Application Examples**

|                                                                                           | Subclass 0     | Subclass 1    | Subclass 2     |

|-------------------------------------------------------------------------------------------|----------------|---------------|----------------|

| Wireless Comms. Repeater<br>- Narrowband (<125 MSPS ADC)<br>- No DL requirements          |                |               |                |

| Software Defined Radio<br>- Wideband<br>- DL required                                     |                | >250 MSPS ADC | <=250 MSPS ADC |

| Radar, Imaging Sensor<br>- Wideband (>250 MSPS ADC)<br>- DL required + Multi-Device Sync. |                |               |                |

| <b>Oscilloscope, Spectrum Analyzer</b><br>- Wideband (> 250 MSPS ADC)                     | No DL Required | DL Required   |                |

Texas Instruments' JESD204B device all support subclass 1 while some support all 3 subclasses

## **Summary**

- JESD204: Standard serial data interface for data converters

- JESD204B subclasses offer 3 implementation variations

- Transport Layer defines data framing into serial lanes

- Link layer defines encoding, synchronization and data monitoring

- Physical layer defines the electrical and timing performance

- Deterministic latency achieved with subclasses 1, 2 and is required for known/constant latency through link

## **More Educational Resources**

#### www.ti.com/lsds/ti/data-converters/high-speed-adc-greater-10msps-jesd204b.page

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ctivity                       |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated