# FRAM – New Generation of Non-Volatile Memory

## What is FRAM?

FRAM, an acronym for ferroelectric random access memory, combines the fast read and write access of dynamic RAM (DRAM) with being non-volatile (the ability to retain data when power is turned off) and ultra-low power consumption (compared to EEPROM and Flash). In spite of the name, FRAM is not affected by magnetic fields because there is no ferrous material (iron) in the chip. FRAM is being used today in several applications including electronic metering, automotive (e.g. smart air bags), printers, instrumentation, medical equipment, industrial

microcontrollers and radio frequency identification.

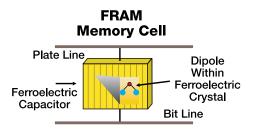

A FRAM memory cell consists of a capacitor connected to a plate and bit line. The orientation of the dipole within the capacitor determines whether a "1" or "0" is stored. The dipole orientation can be set and reversed by applying voltage across either line.

#### **FRAM** EEPROM Flash Time to write 64 bytes to memory 6,400 μs **1.6 μs** 2,200 µs 4.5 μs Time to read 64 bytes from memory **1.6 μs** 4.5 μs 100 trillion 100.000 Number of write cycles 500.000 10 to 14 V 10 to 14 V Voltage needed to write 1.5 V 3× >3× Manufacturing cycle time Resistance to gamma radiation Yes No No

For further information on Texas Instruments' FRAM technology: www.ti.com/fram

# Key Advantages

RUMENTS

- **Speed**—FRAM has fast access times – similar to DRAM. The actual write time is less than 50ns/word.This is ~1000× faster than EEPROM or Flash memory making universal memory reality.

- Low Power—Accesses to the FRAM occur at lower voltages (1.5 V) requiring very little power. EEPROM writes accesses need 10 to 14 V requiring much more power. Lower power memory enables more functionality at faster transactions speeds.

- Data Reliability—All the necessary power for FRAM is front-loaded at the beginning of data access eliminating "datatearing." FRAM experiences 100 trillion read/write cycles or greater – *practically unlimited*.

### **Comparison of Memory Attributes**

# FRAM Reliability Data 2008

| Test Description                      | Conditions                                                                                 | Samples / Fail |

|---------------------------------------|--------------------------------------------------------------------------------------------|----------------|

| High-temperature operating life test  | 1,000 hours at 125°C at maximum supply voltage                                             | 316 / 0        |

| Data retention                        | 1,000 hours at 125°C for same state; 85°C opposite state thermal depolarization            | 283 / 0        |

| Intrinsic data cycling                | $5.4\times10^{12}$ cycles, 25°C for 30 days at nominal supply voltage                      | 160 / 0        |

| Intrinsic data retention post cycling | 100 hours at 125°C same state; 85°C opposite state thermal depolarization                  | 158 / 0        |

| Extrinsic data cycling                | $1 \times 10^{8}$ cycles, 25°C for 30 days                                                 | 160 / 0        |

| High-temperature operating life test  | 100 hours at 125°C at maximum supply voltage                                               | 160 / 0        |

| Pre-conditioning                      | 24 hours at 125°C followed by 192 hours at 30°C / 60% relative humidity, 3 cycles at 260°C | 160 / 0        |

| Temperature cycle                     | 700 cycles, –55°C to 125°C                                                                 | 80 / 0         |

| HAST                                  | 168 hours at 130°C / 85% relative humidity                                                 | 79 / 0         |

| ESD / LU                              | $\pm 2{,}500$ V HBM, $\pm 800$ V, 2× maximum supply voltage at 90°C                        | 33 / 0         |

# FRAM Reliability

Texas Instruments' (TI) FRAM new generation of non-volatile memory is designed, manufactured and tested to meet the stringent requirements of today and tomorrow. The following tests, per JEDEC industry standard test specifications for non-volatile memory, guarantee **10 years of operation and data retention at 85°C**. These test results are a small portion of the testing done continuously at TI.

# FRAM Security

Studies by a leading security lab have concluded that FRAM's functional features could change the smart card security landscape compared to existing EEPROM technologies. FRAM is more resistant to data corruption via electric fields, radiation, etc. Also, the extremely fast write times and the small 130 nanometer (nm) process node make it more resistant to physical attacks. Furthermore, FRAM's much lower power consumption arguably makes it more difficult to attack with differential power analysis techniques.

# FRAM Data Read / Rewrite

A data read access from FRAM includes a rewrite of the data back to the same memory location. This is done within the memory block automatically. This read/ restore operation is similar to DRAM, commonly used in personal electronics. Since FRAM has an inexhaustible write endurance (>100 trillion write/read cycles), this is not a practical concern.

# FRAM Manufacturing

While the benefits of FRAM have been known for many years, productization at acceptable manufacturing yields has posed challenges to many companies.TI has been *successfully* producing FRAM memory at an advanced process node (130 nm) for over two years. TI's FRAM technology is the result of *over 10 years of manufacturing development with well over 200 issued patents*. For further information on TI's FRAM technology:

- T.S. Moise, et al., Demonstration of a 4Mb High-Sensity Ferroelectric Memory Embedded within a 130nm, 5LM Cu/ FSG Logic Process, *Int. Elec. Dev. Meet.*, 2002, p. 535.

- 2. J. Rodriguez, et al., Reliability Properties of Low-Voltage PZT Ferroelectric Capacitors and Memory Arrays, *IEEE Trans. On Dev. Mat. Reliability*, Vol. 4, No. 3, September 2004, p. 436.

- H.P. McAdams et al., A 64Mb Embedded FRAM Utilizing a 130nm 5LM Cu/FSG Logic Process, *IEEE J. Solid State Circ.*, Vol. 39, No.4, 2004., p. 667.

- 4. J. Rodriguez, et al., Reliability Demonstration Ferroelectric Random Access Memory Embedded within a 130nm CMOS Process, *Proceedings* of the IEEE Non-Volatile Memory Tech. Workshop, September 2007, pp. 64–66.