Chapter Excerpt from SLAU208

Chapter 1 SLAU398F–August 2012–Revised March 2018

# Cyclic Redundancy Check (CRC) Module

**NOTE:** This chapter is an excerpt from the *MSP430x5xx and MSP430x6xx Family User's Guide*. The most recent version of the full user's guide is available at <a href="http://www.ti.com/lit/pdf/slau208">http://www.ti.com/lit/pdf/slau208</a>.

The cyclic redundancy check (CRC) module provides a signature for a given data sequence. This chapter describes the operation and use of the CRC module.

**NOTE:** The CRC module on the MSP430F543x and MSP430F541x non-A versions does not support the bit-wise reverse feature described in this module description. Registers CRCDIRB and CRCRESR, along with their respective functionality, are not available.

#### Topic

#### Page

| 1.1 | Cyclic Redundancy Check (CRC) Module Introduction | 2 |

|-----|---------------------------------------------------|---|

| 1.2 | CRC Standard and Bit Order                        | 2 |

| 1.3 | CRC Checksum Generation                           | 3 |

| 1.4 | CRC Registers                                     | 6 |

Cyclic Redundancy Check (CRC) Module Introduction

www.ti.com

(1)

# 1.1 Cyclic Redundancy Check (CRC) Module Introduction

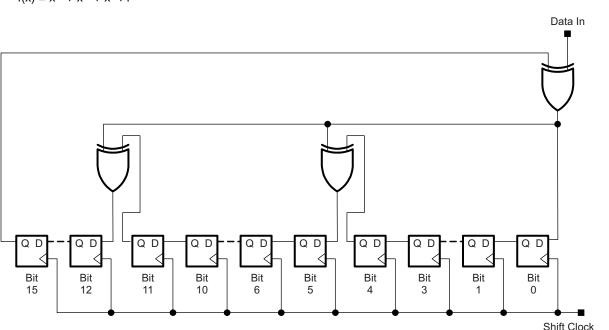

The CRC module produces a signature for a given sequence of data values. The signature is generated through a feedback path from data bits 0, 4, 11, and 15 (see Figure 1-1). The CRC signature is based on the polynomial given in the CRC-CCITT-BR polynomial (see Equation 1).

$f(x) = x^{16} + x^{12} + x^5 + 1$

# Figure 1-1. LFSR Implementation of CRC-CCITT Standard, Bit 0 is the MSB of the Result

Identical input data sequences result in identical signatures when the CRC is initialized with a fixed seed value, whereas different sequences of input data, in general, result in different signatures.

# 1.2 CRC Standard and Bit Order

The definitions of the various CRC standards were done in the era of main frame computers, and by convention bit 0 was treated as the MSB. Today, as in most microcontrollers such as the MSP430, bit 0 normally denotes the LSB. In Figure 1-1, the bit convention shown is as given in the original standards, where bit 0 is the MSB. The fact that bit 0 is treated for some as LSB, and for others as MSB, continues to cause confusion. The CRC16 module therefore provides a bit reversed register pair for CRC16 operations to support both conventions.

www.ti.com

# 1.3 CRC Checksum Generation

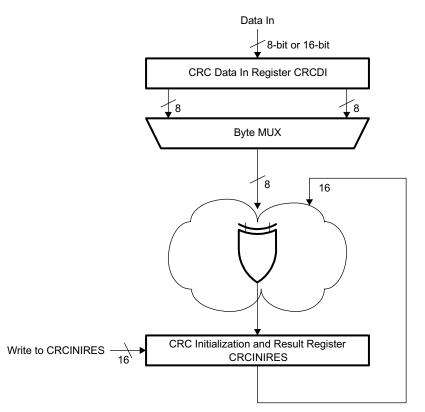

The CRC generator is first initialized by writing a 16-bit word (seed) to the CRC Initialization and Result (CRCINIRES) register. Any data that should be included into the CRC calculation must be written to the CRC Data Input (CRCDI or CRCDIRB) register in the same order that the original CRC signature was calculated. The actual signature can be read from the CRCINIRES register to compare the computed checksum with the expected checksum.

Signature generation describes a method on how the result of a signature operation can be calculated. The calculated signature, which is computed by an external tool, is called a checksum in the following text. The checksum is stored in the product's memory and is used to check the correctness of the CRC operation result.

# 1.3.1 CRC Implementation

To allow parallel processing of the CRC, the linear feedback shift register (LFSR) functionality is implemented with an XOR tree. This implementation shows the identical behavior as the LFSR approach after 8 bits of data are shifted in when the LSB is 'shifted' in first. The generation of a signature calculation has to be started by writing a seed to the CRCINIRES register to initialize the register. Software or hardware (for example, DMA) can transfer data to the CRCDI or CRCDIRB register (for example, from memory). The value in CRCDI or CRCDIRB is then included into the signature, and the result is available in the signature result registers at the next read access (CRCINIRES and CRCRESR). The signature can be generated using word or byte data.

If a word data is processed, the lower byte at the even address is used at the first clock (MCLK) cycle. During the second clock cycle, the higher byte is processed. Thus, it takes two clock cycles to process word data, while it takes only one clock (MCLK) cycle to process byte data.

Data bytes written to CRCDIRB in word mode or the data byte in byte mode are bit-wise reversed before the CRC engine adds them to the signature. The bits among each byte are reversed. Data bytes written to CRCDI in word mode or the data byte in byte mode are not bit reversed before use by the CRC engine.

If the checksum itself (with reversed bit order) is included into the CRC operation (as data written to CRCDI or CRCDIRB), the result in the CRCINIRES and CRCRESR registers must be zero.

## Figure 1-2. Implementation of CRC-CCITT Using the CRCDI and CRCINIRES Registers

## 1.3.2 Assembler Examples

. . .

### 1.3.2.1 General Assembler Example

This example demonstrates the operation of the on-chip CRC:

|    | PUSH | R4                | ; | Save registers            |

|----|------|-------------------|---|---------------------------|

|    | PUSH | R5                |   |                           |

|    | MOV  | #StartAddress,R4  | ; | StartAddress < EndAddress |

|    | MOV  | #EndAddress,R5    |   |                           |

|    | MOV  | &INIT, &CRCINIRES | ; | INIT to CRCINIRES         |

| L1 | MOV  | @R4+,&CRCDI       | ; | Item to Data In register  |

|    | CMP  | R5,R4             | ; | End address reached?      |

|    | JLO  | L1                | ; | No                        |

|    | MOV  | &Check_Sum,&CRCDI | ; | Yes, Include checksum     |

|    | TST  | &CRCINIRES        | ; | Result = 0?               |

|    | JNZ  | CRC_ERROR         | ; | No, CRCRES <> 0: error    |

|    |      |                   | ; | Yes, CRCRES=0:            |

|    |      |                   | ; | information ok.           |

|    | POP  | R5                | ; | Restore registers         |

|    | POP  | R4                |   |                           |

www.ti.com

#### 1.3.2.2 Reference Data Sequence

The details of the implemented CRC algorithm is shown by the following data sequences using word or byte accesses and the CRC data-in as well as the CRC data-in reverse byte registers:

```

#OFFFFh,&CRCINIRES ; initialize CRC

mov

mov.b

#00031h,&CRCDI L

; "1"

#00032h,&CRCDI_L

; "2"

mov.b

#00033h,&CRCDI_L

; "3"

mov.b

; "4"

mov.b

#00034h,&CRCDI_L

; "5"

mov.b

#00035h,&CRCDI_L

mov.b

#00036h,&CRCDI_L

; "6"

; "7"

mov.b

#00037h,&CRCDI L

mov.b

#00038h,&CRCDI_L

; "8"

; "9"

mov.b

#00039h,&CRCDI_L

cmp

#089F6h,&CRCINIRES ; compare result

; CRCRESR contains 06F91h

jeq

&Success

; no error

&Error

; to error handler

br

#OFFFFh,&CRCINIRES ; initialize CRC

mov

mov.w

#03231h,&CRCDI ; "1" & "2"

; "3" & "4"

#03433h,&CRCDI

mov.w

#03635h,&CRCDI

; "5" & "6"

mov.w

; "7" & "8"

#03837h,&CRCDI

mov.w

; "9"

#039h, &CRCDI_L

mov.b

#089F6h,&CRCINIRES ; compare result

cmp

; CRCRESR contains 06F91h

&Success

; no error

jeq

&Error

br

; to error handler

. . .

#OFFFFh,&CRCINIRES ; initialize CRC

mov

#00031h,&CRCDIRB_L ; "1"

mov.b

#00032h,&CRCDIRB_L ; "2"

mov.b

mov.b

#00033h,&CRCDIRB_L ; "3"

mov.b

#00034h,&CRCDIRB_L ; "4"

#00035h,&CRCDIRB_L ; "5"

mov.b

#00036h,&CRCDIRB L ; "6"

mov.b

#00037h,&CRCDIRB_L ; "7"

mov.b

#00038h,&CRCDIRB_L ; "8"

mov.b

#00039h,&CRCDIRB_L ; "9"

mov.b

#029B1h,&CRCINIRES ; compare result

cmp

; CRCRESR contains 08D94h

&Success

iea

; no error

&Error

; to error handler

br

. . .

#0FFFFh,&CRCINIRES ; initialize CRC

mov

#03231h,&CRCDIRB ; "1" & "2"

mov.w

mov.w

#03433h,&CRCDIRB ; "3" & "4"

#03635h,&CRCDIRB ; "5" & "6"

mov.w

; "7" & "8"

mov.w

#03837h,&CRCDIRB

#039h, &CRCDIRB_L ; "9"

mov.b

#029B1h,&CRCINIRES ; compare result

cmp

; CRCRESR contains 08D94h

jeq

&Success

; no error

; to error handler

br

&Error

```

# 1.4 CRC Registers

The CRC module registers are listed in Table 1-1. The base address can be found in the device-specific data sheet. The address offset is given in Table 1-1.

**NOTE:** All registers have word or byte register access. For a generic register *ANYREG*, the suffix "\_L" (*ANYREG\_L*) refers to the lower byte of the register (bits 0 through 7). The suffix "\_H" (*ANYREG\_H*) refers to the upper byte of the register (bits 8 through 15).

| Offset | Acronym     | Register Name                           | Туре       | Access | Reset | Section       |

|--------|-------------|-----------------------------------------|------------|--------|-------|---------------|

| 0000h  | CRCDI       | CRC Data In                             | Read/write | Word   | 0000h | Section 1.4.1 |

| 0000h  | CRCDI_L     |                                         | Read/write | Byte   | 00h   |               |

| 0001h  | CRCDI_H     |                                         | Read/write | Byte   | 00h   |               |

| 0002h  | CRCDIRB     | CRC Data In Reverse Byte <sup>(1)</sup> | Read/write | Word   | 0000h | Section 1.4.2 |

| 0002h  | CRCDIRB_L   |                                         | Read/write | Byte   | 00h   |               |

| 0003h  | CRCDIRB_H   |                                         | Read/write | Byte   | 00h   |               |

| 0004h  | CRCINIRES   | CRC Initialization and Result           | Read/write | Word   | FFFFh | Section 1.4.3 |

| 0004h  | CRCINIRES_L |                                         | Read/write | Byte   | FFh   |               |

| 0005h  | CRCINIRES_H |                                         | Read/write | Byte   | FFh   |               |

| 0006h  | CRCRESR     | CRC Result Reverse <sup>(1)</sup>       | Read only  | Word   | FFFFh | Section 1.4.4 |

| 0006h  | CRCRESR_L   |                                         | Read only  | Byte   | FFh   |               |

| 0007h  | CRCRESR_H   |                                         | Read only  | Byte   | FFh   |               |

#### Table 1-1. CRC Registers

<sup>(1)</sup> Not available on MSP430F543x and MSP430F541x non-A versions.

www.ti.com

# 1.4.1 CRCDI Register

CRC Data In Register

|       |      |      | Figure 1-3 | . CRCDI Regi | ster |      |      |  |

|-------|------|------|------------|--------------|------|------|------|--|

| 15    | 14   | 13   | 12         | 11           | 10   | 9    | 8    |  |

| CRCDI |      |      |            |              |      |      |      |  |

| rw-0  | rw-0 | rw-0 | rw-0       | rw-0         | rw-0 | rw-0 | rw-0 |  |

| 7     | 6    | 5    | 4          | 3            | 2    | 1    | 0    |  |

|       |      |      | CR         | CDI          |      |      |      |  |

| rw-0  | rw-0 | rw-0 | rw-0       | rw-0         | rw-0 | rw-0 | rw-0 |  |

## Table 1-2. CRCDI Register Description

\_ \_ \_ \_

| Bit  | Field | Туре | Reset | Description                                                                                                                                         |

|------|-------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-0 | CRCDI | RW   | 0h    | CRC data in. Data written to the CRCDI register is included to the present signature in the CRCINIRES register according to the CRC-CCITT standard. |

# 1.4.2 CRCDIRB Register

CRC Data In Reverse Register

## Figure 1-4. CRCDIRB Register

|         |      |      | 0    |      |      |      |      |  |  |

|---------|------|------|------|------|------|------|------|--|--|

| 15      | 14   | 13   | 12   | 11   | 10   | 9    | 8    |  |  |

| CRCDIRB |      |      |      |      |      |      |      |  |  |

| rw-0    | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 |  |  |

| 7       | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|         |      |      | CRC  | DIRB |      |      |      |  |  |

| rw-0    | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 | rw-0 |  |  |

## Table 1-3. CRCDIRB Register Description

| Bit  | Field   | Туре | Reset | Description                                                                                                                                                                                                                              |

|------|---------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-0 | CRCDIRB | RW   | 0h    | CRC data in reverse byte. Data written to the CRCDIRB register is included to the present signature in the CRCINIRES and CRCRESR registers according to the CRC-CCITT standard. Reading the register returns the register CRCDI content. |

CRC Registers

www.ti.com

# 1.4.3 CRCINIRES Register

CRC Initialization and Result Register

|           |      |      | Figure 1-5. C | RCINIRES Re | egister |      |      |  |

|-----------|------|------|---------------|-------------|---------|------|------|--|

| 15        | 14   | 13   | 12            | 11          | 10      | 9    | 8    |  |

| CRCINIRES |      |      |               |             |         |      |      |  |

| rw-1      | rw-1 | rw-1 | rw-1          | rw-1        | rw-1    | rw-1 | rw-1 |  |

| 7         | 6    | 5    | 4             | 3           | 2       | 1    | 0    |  |

|           |      |      | CRCII         | NIRES       |         |      |      |  |

| rw-1      | rw-1 | rw-1 | rw-1          | rw-1        | rw-1    | rw-1 | rw-1 |  |

## Table 1-4. CRCINIRES Register Description

| Bit  | Field     | Туре | Reset | Description                                                                                                                                                                                                                                                         |

|------|-----------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-0 | CRCINIRES | RW   | FFFFh | CRC initialization and result. This register holds the current CRC result (according to the CRC-CCITT standard). Writing to this register initializes the CRC calculation with the value written to it. The value just written can be read from CRCINIRES register. |

# 1.4.4 CRCRESR Register

CRC Reverse Result Register

## Figure 1-6. CRCRESR Register

| 15  | 14  | 13  | 12   | 11   | 10  | 9   | 8   |

|-----|-----|-----|------|------|-----|-----|-----|

|     |     |     | CRCI | RESR |     |     |     |

| r-1 | r-1 | r-1 | r-1  | r-1  | r-1 | r-1 | r-1 |

| 7   | 6   | 5   | 4    | 3    | 2   | 1   | 0   |

|     |     |     | CRCI | RESR |     |     |     |

| r-1 | r-1 | r-1 | r-1  | r-1  | r-1 | r-1 | r-1 |

## Table 1-5. CRCRESR Register Description

| Bit  | Field   | Туре | Reset | Description                                                                                                                                                                                                                                               |

|------|---------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-0 | CRCRESR | R    | FFFFh | CRC reverse result. This register holds the current CRC result (according to the CRC-CCITT standard). The order of bits is reversed (for example, CRCINIRES[15] = CRCRESR[0]) compared to the order of bits in the CRCINIRES register (see example code). |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated