Chapter Excerpt from SLAU208

Chapter 1 SLAU399F–August 2012–Revised March 2018

Page

# Watchdog Timer (WDT\_A)

The watchdog timer is a 32-bit timer that can be used as a watchdog or as an interval timer. This chapter describes the watchdog timer. The enhanced watchdog timer, WDT\_A, is implemented in all devices.

**NOTE:** This chapter is an excerpt from the *MSP430x5xx and MSP430x6xx Family User's Guide*. Click here to download the latest version of the full user's guide: **SLAU208**.

#### Topic

| 1.1 | WDT_A Introduction | 2   |

|-----|--------------------|-----|

|     |                    |     |

| 1.2 | WDT_A Operation    | 4   |

| 1.3 | WDT_A Registers    | 6   |

|     |                    | · · |

#### WDT\_A Introduction

# 1.1 WDT\_A Introduction

The primary function of the watchdog timer (WDT\_A) module is to perform a controlled system restart after a software problem occurs. If the selected time interval expires, a system reset is generated. If the watchdog function is not needed in an application, the module can be configured as an interval timer and can generate interrupts at selected time intervals.

Features of the watchdog timer module include:

- Eight software-selectable time intervals

- Watchdog mode

- Interval mode

- Password-protected access to Watchdog Timer Control (WDTCTL) register

- Selectable clock source

- Can be stopped to conserve power

- Clock fail-safe feature

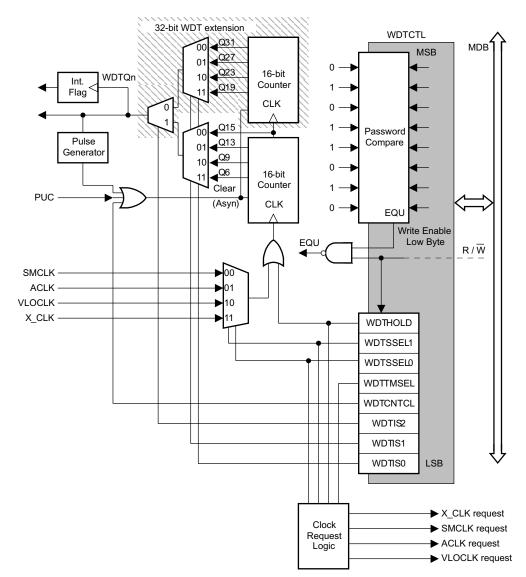

The watchdog timer block diagram is shown in Figure 1-1.

#### NOTE: Watchdog timer powers up active.

After a PUC, the WDT\_A module is automatically configured in the watchdog mode with an initial ~32-ms reset interval using the SMCLK. The user must setup or halt the WDT\_A prior to the expiration of the initial reset interval.

www.ti.com

WDT\_A Introduction

Figure 1-1. Watchdog Timer Block Diagram

#### WDT\_A Operation

### 1.2 WDT\_A Operation

The watchdog timer module can be configured as either a watchdog or interval timer with the WDTCTL register. WDTCTL is a 16-bit password-protected read/write register. Any read or write access must use word instructions and write accesses must include the write password 05Ah in the upper byte. Any write to WDTCTL with any value other than 05Ah in the upper byte is a password violation and triggers a PUC system reset, regardless of timer mode. Any read of WDTCTL reads 069h in the upper byte. Byte reads on WDTCTL high or low part result in the value of the low byte. Writing byte wide to upper or lower parts of WDTCTL results in a PUC.

# 1.2.1 Watchdog Timer Counter (WDTCNT)

The WDTCNT is a 32-bit up counter that is not directly accessible by software. The WDTCNT is controlled and its time intervals are selected through the Watchdog Timer Control (WDTCTL) register. The WDTCNT can be sourced from SMCLK, ACLK, VLOCLK, or X\_CLK on some devices. The clock source is selected with the WDTSSEL bits. The timer interval is selected with the WDTIS bits.

#### 1.2.2 Watchdog Mode

After a PUC condition, the WDT module is configured in the watchdog mode with an initial ~32-ms reset interval using the SMCLK. The user must setup, halt, or clear the watchdog timer prior to the expiration of the initial reset interval or another PUC is generated. When the watchdog timer is configured to operate in watchdog mode, either writing to WDTCTL with an incorrect password, or expiration of the selected time interval triggers a PUC. A PUC resets the watchdog timer to its default condition.

#### 1.2.3 Interval Timer Mode

Setting the WDTTMSEL bit to 1 selects the interval timer mode. This mode can be used to provide periodic interrupts. In interval timer mode, the WDTIFG flag is set at the expiration of the selected time interval. A PUC is not generated in interval timer mode at expiration of the selected timer interval, and the WDTIFG enable bit WDTIE remains unchanged.

When the WDTIE bit and the GIE bit are set, the WDTIFG flag requests an interrupt. The WDTIFG interrupt flag is automatically reset when its interrupt request is serviced, or it may be reset by software. The interrupt vector address in interval timer mode is different from that in watchdog mode.

#### NOTE: Modifying the watchdog timer

The watchdog timer interval should be changed together with WDTCNTCL = 1 in a single instruction to avoid an unexpected immediate PUC or interrupt. The watchdog timer should be halted before changing the clock source to avoid a possible incorrect interval.

#### 1.2.4 Watchdog Timer Interrupts

The watchdog timer uses two bits in the SFRs for interrupt control:

- WDT interrupt flag, WDTIFG, located in SFRIFG1.0

- WDT interrupt enable, WDTIE, located in SFRIE1.0

When using the watchdog timer in the watchdog mode, the WDTIFG flag sources a reset vector interrupt. The WDTIFG will self clear upon a watchdog timeout event. The SYSRSTIV can be read to determine if the reset was caused by a watchdog timeout event.

When using the watchdog timer in interval timer mode, the WDTIFG flag is set after the selected time interval and requests a watchdog timer interval timer interrupt if the WDTIE and the GIE bits are set. The interval timer interrupt vector is different from the reset vector used in watchdog mode. In interval timer mode, the WDTIFG flag is reset automatically when the interrupt is serviced, or can be reset with software.

www.ti.com

The WDT\_A provides a fail-safe clocking feature, ensuring the clock to the WDT\_A cannot be disabled while in watchdog mode. This means that the low-power modes may be affected by the choice for the WDT\_A clock.

If SMCLK or ACLK fails as the WDT\_A clock source, VLOCLK is automatically selected as the WDT\_A clock source.

When the WDT\_A module is used in interval timer mode, there is no fail-safe feature within WDT\_A for the clock source.

# 1.2.6 Operation in Low-Power Modes

The devices have several low-power modes. Different clock signals are available in different low-power modes. The requirements of the application and the type of clocking that is used determine how the WDT\_A should be configured. For example, the WDT\_A should not be configured in watchdog mode with a clock source that is originally sourced from DCO, XT1 in high-frequency mode, or XT2 via SMCLK or ACLK, if the user wants to use low-power mode 3. In this case, SMCLK or ACLK would remain enabled, increasing the current consumption of LPM3. When the watchdog timer is not required, the WDTHOLD bit can be used to hold the WDTCNT, reducing power consumption.

# 1.2.7 Software Examples

Any write operation to WDTCTL must be a word operation with 05Ah (WDTPW) in the upper byte:

```

; Periodically clear an active watchdog

MOV #WDTPW+WDTIS2+WDTIS1+WDTCNTCL,&WDTCTL

;

; Change watchdog timer interval

MOV #WDTPW+WDTCNTCL+SSEL,&WDTCTL

;

; Stop the watchdog

MOV #WDTPW+WDTHOLD,&WDTCTL

;

; Change WDT to interval timer mode, clock/8192 interval

MOV #WDTPW+WDTCNTCL+WDTTMSEL+WDTIS2+WDTIS0,&WDTCTL

```

# 1.3 WDT\_A Registers

The watchdog timer module registers are listed in Table 1-1. The base address for the watchdog timer module registers and special function registers (SFRs) can be found in device-specific data sheets. The address offset is given in Table 1-1.

# **NOTE:** All registers have word or byte register access. For a generic register *ANYREG*, the suffix "\_L" (*ANYREG\_L*) refers to the lower byte of the register (bits 0 through 7). The suffix "\_H" (*ANYREG\_H*) refers to the upper byte of the register (bits 8 through 15).

| Offset | Acronym  | Register Name          | Туре       | Access | Reset | Section       |

|--------|----------|------------------------|------------|--------|-------|---------------|

| 00h    | WDTCTL   | Watchdog Timer Control | Read/write | Word   | 6904h | Section 1.3.1 |

| 00h    | WDTCTL_L |                        | Read/write | Byte   | 04h   |               |

| 01h    | WDTCTL_H |                        | Read/write | Byte   | 69h   |               |

# Table 1-1. WDT\_A Registers

www.ti.com

# 1.3.1 WDTCTL Register

Watchdog Timer Control Register

| Figure 1-2. WDTCTL Register |          |      |          |          |      |       |      |

|-----------------------------|----------|------|----------|----------|------|-------|------|

| 15                          | 15 14 13 |      | 12       | 11       | 10   | 9     | 8    |

| WDTPW                       |          |      |          |          |      |       |      |

| 7                           | 6        | 5    | 4        | 3        | 2    | 1     | 0    |

| WDTHOLD                     | WDTSSEL  |      | WDTTMSEL | WDTCNTCL |      | WDTIS |      |

| rw-0                        | rw-0     | rw-0 | rw-0     | r0(w)    | rw-1 | rw-0  | rw-0 |

# Table 1-2. WDTCTL Register Description

| Bit  | Field    | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|------|----------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 15-8 | WDTPW    | RW   | 69h   | Watchdog timer password. Always read as 069h. Must be written as 5Ah; if any other value is written, a PUC is generated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 7    | WDTHOLD  | RW   | 0h    | Watchdog timer hold. This bit stops the watchdog timer. Setting WDTHOLD = 1<br>when the WDT is not in use conserves power.<br>0b = Watchdog timer is not stopped.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|      |          |      |       | 1b = Watchdog timer is stopped.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 6-5  | WDTSSEL  | RW   | Oh    | Watchdog timer clock source select<br>00b = SMCLK<br>01b = ACLK<br>10b = VLOCLK<br>11b = X_CLK; VLOCLK in devices that do not support X_CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 4    | WDTTMSEL | RW   | Oh    | Watchdog timer mode select<br>0b = Watchdog mode<br>1b = Interval timer mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 3    | WDTCNTCL | RW   | Oh    | Watchdog timer counter clear. Setting WDTCNTCL = 1 clears the count value to<br>0000h. WDTCNTCL is automatically reset.<br>0b = No action<br>1b = WDTCNT = 0000h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 2-0  | WDTIS    | RW   | 4h    | Watchdog timer interval select. These bits select the watchdog timer interval to<br>set the WDTIFG flag and/or generate a PUC.<br>000b = Watchdog clock source /( $2^{31}$ ) (18h:12m:16s at 32.768 kHz)<br>001b = Watchdog clock source /( $2^{27}$ ) (01h:08m:16s at 32.768 kHz)<br>010b = Watchdog clock source /( $2^{23}$ ) (00h:04m:16s at 32.768 kHz)<br>011b = Watchdog clock source /( $2^{19}$ ) (00h:00m:16s at 32.768 kHz)<br>100b = Watchdog clock source /( $2^{15}$ ) (1 s at 32.768 kHz)<br>100b = Watchdog clock source /( $2^{13}$ ) (250 ms at 32.768 kHz)<br>101b = Watchdog clock source /( $2^{9}$ ) (15.625 ms at 32.768 kHz)<br>111b = Watchdog clock source /( $2^{6}$ ) (1.95 ms at 32.768 kHz) |  |  |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated