### Chapter Excerpt from SLAU208

# Chapter 1

SLAU405F-August 2012-Revised March 2018

NOTE: This chapter is an excerpt from the MSP430x5xx and MSP430x6xx Family User's Guide.

The latest version of the full user's guide can be downloaded from

http://www.ti.com/lit/pdf/slau208.

The REF module is a general-purpose reference system that generates voltage references required for other subsystems on a given device such as digital-to-analog converters, analog-to-digital converters, or comparators. This chapter describes the REF module.

**Topic** Page

| 1.1 | REF Introduction       | 2  |

|-----|------------------------|----|

| 1.2 | Principle of Operation | 5  |

| 1.3 | REF Registers          | 11 |

REF Introduction www.ti.com

#### 1.1 REF Introduction

The reference module (REF) generates all critical reference voltages that can be used by various analog peripherals in a given device. These include, but are not necessarily limited to, the ADC10\_A, ADC12\_A, CTSD16, DAC12\_A, LCD\_B, and COMP\_B modules (availability of a given module depends on the particular device). The heart of the reference system is the bandgap from which all other references are derived by unity or noninverting gain stages. The REFGEN subsystem consists of the bandgap, the bandgap bias, and the noninverting buffer stage, which generates the three primary voltage reference available in the system, namely 1.5 V, 2.0 V, and 2.5 V. In addition, when enabled, a buffered bandgap voltage is also available.

#### Features of the REF include:

- Centralized factory-trimmed bandgap with excellent PSRR, temperature coefficient, and accuracy

- 1.5-V, 2.0-V, or 2.5-V user-selectable internal references

- Buffered bandgap voltage available to rest of system

- Power saving features

- Backward compatibility to existing reference system

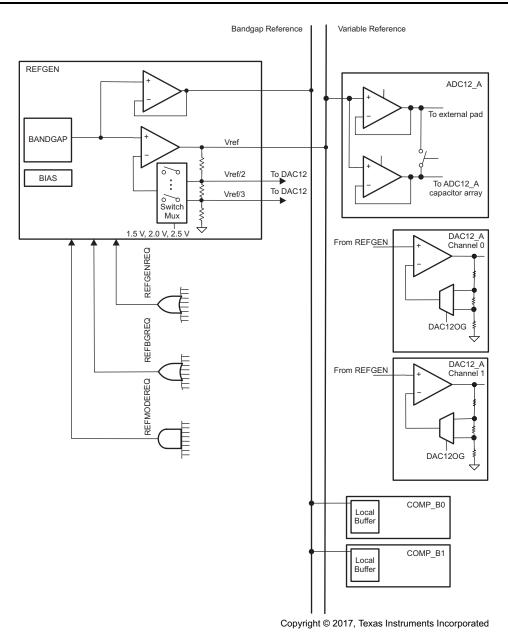

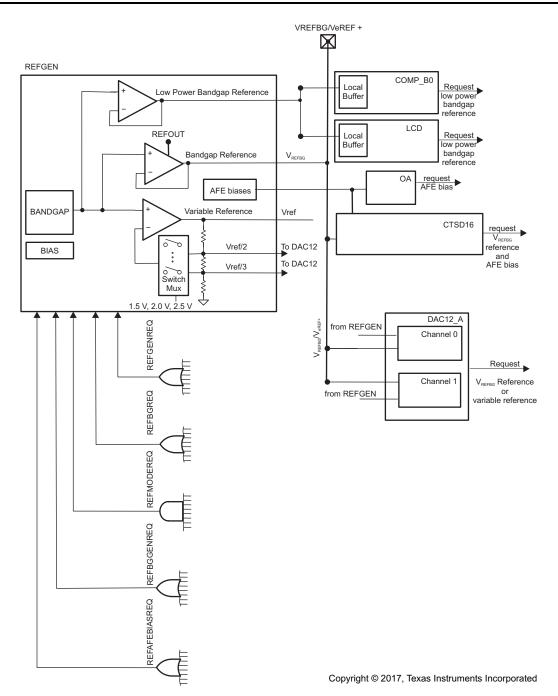

Figure 1-1 shows the block diagram of the REF module in an example device with ADC12\_A. Figure 1-2 shows the block diagram of the REF module in an example device with a CTSD16 module.

**NOTE:** For devices with the CTSD16 module, external reference  $V_{\text{eREF+}}$  cannot be applied while internal reference  $V_{\text{REFBG}}$  is being used by another module, because they share the same pin, and contention on the signal line will occur. Therefore, if the external reference is used, make sure that no modules request the internal reference  $V_{\text{REFBG}}$ .

Devices with ADC10\_A might not include the reference voltage output to an external pin. Refer to the device-specific data sheet.

www.ti.com REF Introduction

Figure 1-1. REF Block Diagram

TEXAS INSTRUMENTS

REF Introduction www.ti.com

Figure 1-2. REF Block Diagram for Devices With a CTSD16 Module

4

www.ti.com Principle of Operation

#### 1.2 Principle of Operation

The REF module provides all of the necessary voltage references to be used by various peripheral modules throughout the system. These peripherals include but are not limited to the ADC10\_A, ADC12\_A, CTSD16, DAC12\_A, LCD\_B, and COMP\_B.

The REFGEN subsystem contains a high-performance bandgap. This bandgap has very good accuracy (factory trimmed), low temperature coefficient, and high PSRR even while operating at low power. The bandgap voltage is used to generate three voltages (1.5 V, 2.0 V, and 2.5 V) through a noninverting amplifier stage. One voltage can be selected at a time.

One output of the REFGEN subsystem is the variable reference line. The variable reference line provides either 1.5 V, 2.0 V, or 2.5 V to the rest of the system.

A second output of the REFGEN subsystem provides a buffered bandgap reference line that can also be used by modules throughout the system. Devices with a CTSD16 module have a second buffered bandgap reference line, V<sub>REFBG</sub>, which is available internally as well as external to the device (refer to the device-specific data sheet for PxSEL.y bit requirements).

Additionally, the REFGEN supports the voltage references required for the DAC12\_A module, when available. Lastly, the REFGEN subsystem also includes the temperature sensor circuitry, because it is derived from the bandgap. The temperature sensor is used by an ADC to measure a voltage proportional to temperature.

Table 1-1 describes the difference reference voltages that are available and how to enable them.

| Table 1-1   | Reference   | Voltage              | Generation | for | Different  | Devices (1) |

|-------------|-------------|----------------------|------------|-----|------------|-------------|

| I able I-I. | 1/616161166 | v Oitau <del>c</del> | Generation | 101 | Dillelelit | DE AICES .  |

| REF<br>Voltage          | Voltage Available                                 | How to Enable on<br>Devices Without CTSD16    | How to Enable On<br>Devices With CTSD16                                                                                                                                                                                 | External Reference Input to Device (VeREF+) is Available                                  |

|-------------------------|---------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Low-power               | Internal on request from module                   | Module requests it                            | Module requests it                                                                                                                                                                                                      | Y                                                                                         |

| bandgap                 | Internal continuously                             | REFON = 1                                     | REFON = 1                                                                                                                                                                                                               | Y                                                                                         |

|                         | Internally on request from module                 | Module requests it, set<br>REFVSEL as desired | DAC requests it, set<br>REFVSEL as desired                                                                                                                                                                              | Y                                                                                         |

| V <sub>REF</sub> 1.5 V, | Internally continuously                           | REFON = 1, set REFVSEL as desired             | REFON = 1, set REFVSEL as desired                                                                                                                                                                                       | Y                                                                                         |

| 2.0 V, 2.5 V            | Internally and externally continuously            | REFOUT = 1, set<br>REFVSEL as desired         | NA                                                                                                                                                                                                                      | Not when VREF and<br>VeREF+ (external<br>reference input to device)<br>share a single pin |

| $V_{REFBG}$             | Internally and externally, on request from module | NA                                            | REFOUT = 1, Set PxSEL.y,<br>and request from module<br>V <sub>REFBG</sub> is always available<br>inside the device and on<br>the pin. If PxSEL.y is not<br>set, V <sub>REFBG</sub> is not available<br>inside the chip. | N <sup>(2)</sup>                                                                          |

|                         | Internally and externally continuously            | NA                                            | REFON = 1, REFOUT = 1,<br>and set PxSEL.y.<br>V <sub>REFBG</sub> is always available<br>inside the device and on<br>the pin. If PxSEL.y is not<br>set, V <sub>REFBG</sub> is not available<br>inside the chip.          | N <sup>(2)</sup>                                                                          |

<sup>(1)</sup> Refer to the block diagrams in this user's guide for each module to determine which reference voltages are available for each module.

<sup>(2)</sup> External reference V<sub>eREF+</sub> cannot be applied while internal reference V<sub>REFBG</sub> is being used by another module, because they share the same pin, and contention on the signal line will occur. Therefore, if the external reference is selected, make sure that no other modules are requesting internal reference V<sub>REFBG</sub>. V<sub>eREF+</sub> is available when V<sub>REFBG</sub> is not enabled.

Principle of Operation www.ti.com

### 1.2.1 Low-Power Operation

The REF module supports low-power applications such as LCD generation. Many of these applications do not require a very accurate reference, compared to data conversion, yet power is of prime concern. To support these kinds of applications, the bandgap can be used in a sampled mode. In sampled mode, the bandgap circuitry is clocked by the VLO at an appropriate duty cycle. This reduces the average power of the bandgap circuitry significantly, at the cost of accuracy. When not in sampled mode, the bandgap is in static mode. Its power is at its highest, but so is its accuracy.

Modules automatically can request static mode or sampled mode using their own individual request lines. In this way, the particular module determines which mode is appropriate for its proper operation and performance. If any one active module requests static mode, all other modules use static mode, even if another module requests sampled mode. In other words, static mode always has higher priority than sampled mode.

#### 1.2.2 REFCTL

The REFCTL registers provide a way to control the reference system from one centralized set of registers. By default, REFCTL is used as the primary control of the reference system.

#### 1.2.2.1 REFMSTR = 1

This mode is implemented in all devices with ADC10 A and CTSD16. Also all ADC12 A devices except for MSP430F5438 and MSP430F5438A support this mode.

Setting the reference master bit (REFMSTR = 1), allows the reference system to be controlled through the REFCTL register. This is the default setting.

Devices with ADC12 A: In this mode (REFMSTR = 1), the legacy control bits inside the ADC register set (ADC12REFON, ADC12REF2 5V, ADC12TCOFF, and ADC12REFOUT) are don't care. The ADC12SR and ADC12REFBURST are still controlled through the ADC12 A, because these are very specific to the ADC12 A module. If REFMSTR is cleared, all settings in the REFCTL are don't care and the reference system is controlled completely by the legacy control bits inside the ADC12\_A module.

Devices with ADC10 A: This is the only mode supported. REFMSTR must be set at all times. ADC10SR is controlled by the ADC10 A, because these are very specific to the ADC10 A module.

Devices with CTSD16: This is the only mode supported. REFMSTR must be set at all times.

Table 1-2 summarizes the REFCTL bits and their effect on the REF module for all devices except those with CTSD16. Table 1-3 summarizes the REFCTL bits and their effect on the REF module for devices with CTSD16.

Table 1-2. REF Control of Reference System (REFMSTR = 1) (Default) for Devices Without CTSD16

| REF Register<br>Setting | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFON                   | Setting this bit enables the REFGEN subsystem, which includes the bandgap, the bandgap bias circuitry, and the 1.5-V, 2.0-V, or 2.5-V buffer. Setting this bit causes the REFGEN subsystem to remain enabled regardless of whether or not any module has requested it. Clearing this bit disables the REFGEN subsystem only when there are no pending requests for REFGEN from any module. REFON must also be set to enable the temperature sensor when required. |

| REFVSEL                 | Selects 1.5 V, 2.0 V, or 2.5 V to be present on the variable reference line when REFON = 1 or REFGEN is requested by any module.                                                                                                                                                                                                                                                                                                                                  |

| REFOUT                  | Setting this bits enables the variable reference line voltage to be present external to the device through a buffer (external reference buffer).                                                                                                                                                                                                                                                                                                                  |

| REFTCOFF                | Setting this bit disables the temperature sensor (when available) to conserve power.                                                                                                                                                                                                                                                                                                                                                                              |

www.ti.com Principle of Operation

#### Table 1-3. REF Control of Reference System (REFMSTR = 1) (Default) for Devices With CTSD16

| REF Register<br>Setting | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFON                   | Setting this bit enables the REFGEN subsystem, which includes the bandgap, the bandgap bias circuitry, AFE biases, and the 1.5-V, 2.0-V, or 2.5-V buffer. Setting this bit causes the REFGEN subsystem to remain enabled regardless of whether or not any module has requested it. Clearing this bit disables the REFGEN subsystem only when there are no pending requests for REFGEN from any module. REFON must also be set to enable the temperature sensor when required. |

| REFVSEL                 | Selects 1.5 V, 2.0 V, or 2.5 V to be present on the variable reference line when REFON = 1.                                                                                                                                                                                                                                                                                                                                                                                   |

| REFOUT                  | Setting this bits enables the $V_{REFBG}$ voltage to be present internally and external to the device through a buffer when REFON = 1 or a module requests $V_{REFBG}$ .                                                                                                                                                                                                                                                                                                      |

| REFTCOFF                | Setting this bit disables the temperature sensor (when available) to conserve power.                                                                                                                                                                                                                                                                                                                                                                                          |

#### 1.2.2.2 REFMSTR = 0

Devices with ADC10\_A: Do not support this mode. REFMSTR bit must not be cleared.

Devices with CTSD16: Do not support this mode. REFMSTR bit must not be cleared.

Devices with ADC12\_A: This setting is applicable. On legacy devices, the ADC12\_A provided the control bits necessary to configure the reference system, namely ADC12REFON, ADC12REF2\_5V, ADC12TCOFF, ADC12REFOUT, ADC12SR, and ADC12REFBURST. The ADC12SR and ADC12REFBURST bits are very specific to the ADC12 operation and, therefore, are not included in REFCTL. All legacy control bits can still be used to configure the reference system, which allows for backward compatibility by clearing REFMSTR. In this case, the REFCTL register bits are don't care.

Table 1-4 summarizes the ADC12\_A control bits and their effect on the REF module. See the ADC12\_A module description for further details.

NOTE: Although the REF module supports using the ADC12\_A bits as control for the reference system, it is recommended that the use of the new REFCTL register be used and older code migrated to this methodology. This allows the logical partitioning of the reference system to be separate from the ADC12\_A system and forms a more natural partitioning for future products.

Table 1-4. Control of Reference System (REFMSTR = 0, ADC12 A Only)

| ADC12_A<br>Register<br>Setting | Function                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC12REFON                     | Setting this bit enables the REFGEN subsystem which includes the bandgap, the bandgap bias circuitry, and the 1.5-V, 2.0-V, or 2.5-V buffer. Setting this bit causes the REFGEN subsystem to remain enabled regardless of whether or not any module has requested it. Clearing this bit disables the REFGEN subsystem only when there are no pending requests for REFGEN from any module. |

| ADC12REF2_5<br>V               | Setting this bits causes 2.5 V to be present on the variable reference line when ADC12REFON = 1. Clearing this bit causes 1.5 V to be present on the variable reference line when ADC12REFON = 1.                                                                                                                                                                                         |

| ADC12REFOUT                    | Setting this bits enables the variable reference line voltage to be present external to the device through a buffer (external reference buffer).                                                                                                                                                                                                                                          |

| ADC12TCOFF                     | Setting this bit disables the temperature sensor to conserve power.                                                                                                                                                                                                                                                                                                                       |

As stated previously, the ADC12REFBURST has an effect on the reference system and can be controlled through the ADC12 A. This bit is in effect regardless of whether REFCTL or the ADC12 A is controlling the reference system. Setting ADC12REFBURST = 1 enables burst mode when REFON = 1 and REFMSTR = 1 or when ADC12REFON = 1 and REFMSTR = 0. In burst mode, the internal buffer (ADC12REFOUT = 0) or the external buffer (ADC12REFOUT = 1) is enabled only during a conversion and is disabled automatically to conserve power.

Principle of Operation www.ti.com

NOTE: The legacy ADC12\_A bit ADC12REF2\_5V only allows for selecting either 1.5 V or 2.5 V. To select 2.0 V, the REFVSEL control bits must be used (REFMSTR = 1).

#### 1.2.3 Reference System Requests

There are three basic reference system requests that are used by the reference system. Each module can use these requests to obtain the proper response from the reference system. The three basic requests are REFGENREQ, REFBGREQ, and REFMODEREQ. No interaction is required by the user code. The modules select the proper requests automatically.

A reference request signal, REFGENREQ, is available as an input into the REFGEN subsystem. This signal represents a logical OR of individual requests coming from the various modules in the system that require a voltage reference to be available on the variable reference line. When a module requires a voltage reference, it asserts its corresponding REFGENREQ signal. When the REFGENREQ is asserted, the REFGEN subsystem is enabled. After the specified settling time, the variable reference line voltage is stable and ready for use. The REFVSEL settings determine which voltage is generated on the variable reference line.

In addition to the REFGENREQ, a second reference request signal, REFBGREQ is available. The REFBGREQ signal represents a logical OR of requests coming from the various modules that require the bandgap reference line. When the REFBGREQ is asserted, the bandgap, along with its bias circuitry and local buffer, is enabled if it is not already enabled by a prior request.

The REFMODEREQ request signal is available that configures the bandgap and its bias circuitry to operate in a sampled or static mode of operation. The REFMODEREQ signal basically represents a logical AND of individual requests coming from the various analog modules. A REFMODEREQ occurs only if a REFGENREQ or REFBGQ is also asserted by a module, otherwise it is a don't care. When REFMODEREQ = 1, the bandgap operates in sampled mode. When a module asserts its corresponding REFMODEREQ signal, it is requesting that the bandgap operate in sampled mode. Because REMODEREQ is a logical AND of all individual requests, any modules that request static mode cause the bandgap to operate in static mode. The BGMODE bit can be read as an indicator of static or sampled mode of operation.

#### 1.2.3.1 Specifics for Devices With CTSD16

Devices with a CTSD16 module have two additional request signals.

The REFBGGENREQ signal represents a logical OR of individual requests coming from the various modules in the system that require the bandgap voltage reference  $V_{\text{REFBG}}$  to be available on the V<sub>REFBG</sub>/V<sub>eREF+</sub> signal line. When a module requires a bandgap voltage reference V<sub>REFBG</sub>, it asserts its corresponding REFBGGENREQ signal. When the REFBGGENREQ is asserted, the REFGEN subsystem required to generate the bandgap voltage is enabled. This is different from the bandgap reference line, labeled as low-power bandgap reference in the block diagram (Figure 1-2), which is requested with the REFGENREQ.

The second request signal specific to devices with a CTSD16 module is the REFAFEBIASREQ. This signal represents a logical OR of individual requests coming from the various modules in the system that require the AFE biases. When a module requires the AFE biases, it asserts its corresponding REFAFEBIASREQ signal. When the REFAFEBIASREQ is asserted, the REFGEN subsystem required to generate the AFE biases is enabled.

#### 1.2.3.2 REFBGACT, REFGENACT, REFGENBUSY

Any module that uses the variable reference line causes REFGENACT to be set inside the REFCTL register. This bit is read only and indicates whether the REFGEN is active or off. Similarly, the REFBGACT is active any time one or more modules is actively using the bandgap reference line and indicates whether the REFBG is active or off.

The REFGENBUSY signal is asserted to indicate that a module is using the reference and that reference settings cannot be changed. For example, during an active ADC12\_A conversion, the reference voltage level should not be changed.

R

www.ti.com Principle of Operation

REFGENBUSY is asserted when any of the following are true:

- There is an active ADC12 A conversion (ADC12BUSY = 1).

- The DAC12\_A is actively converting [DAC12AMPx > 1 and DAC12SREFx = 0 or on devices with CTSD16 if DAC12SREFx = {2,3} and REFOUT = 1 and REFON = 1 (or bandgap is requested)].

- The CTSD16 is actively converting (CTSD16SC = 1 and CTSD16REFS = 1).

REFGENBUSY when asserted, write protects the REFCTL register. This prevents the reference from being disabled or its level changed during any active conversion. Note that there is no such protection for the DAC12\_A if the ADC12\_A legacy control bits are used for the reference control. If the user changes the ADC12\_A settings and the DAC12\_A is using the reference, the DAC12\_A conversion is affected.

#### 1.2.3.3 ADC10 A

For devices that contain an ADC10\_A module, the ADC10\_A module contains only one local buffer. This buffer is required when using the internal reference voltage and must be enabled and stable prior to a conversion.

In devices without a reference output buffer, REFOUT must be written 0. Refer to the device-specific data sheet.

In devices with ADC10 A, the REFMSTR bit must be set at all times.

In devices with ADC10\_A, the REFON bit must be set if the internal reference voltage is used.

#### 1.2.3.4 ADC12 A

For devices that contain an ADC12\_A module, the ADC12\_A module contains two local buffers. The larger buffer can be used to drive the reference voltage, present on the variable reference line, external to the device. This buffer has larger power consumption due to a selectable burst mode as well as its need to drive larger DC loads that may be present outside the device. The large buffer is enabled continuously when REFON = 1, REFOUT = 1, and ADC12REFBURST = 0. When ADC12REFBURST = 1, the buffer is enabled only during an ADC conversion, shutting down automatically upon completion of a conversion to save power. In addition, when REFON = 1 and REFOUT = 1, the second smaller buffer is automatically disabled. In this case, the output of the large buffer is connected to the capacitor array through an internal analog switch. This ensures the same reference is used throughout the system. If REFON = 1 and REFOUT = 0, the internal buffer is used for ADC conversion and the large buffer remains disabled. The small internal buffer can operate in burst mode as well by setting ADC12REFBURST = 1.

#### 1.2.3.5 CTSD16

For devices that contain a CTSD16 module, the  $V_{REFBG}$  signal is driven external to the device even if it is only used internally and requires that PxSEL.y bit = 1. If PxSEL.y is not set,  $V_{REFBG}$  is not driven even internal to the chip. The  $V_{REFBG}$  signal is enabled continuously when REFON = 1 and REFOUT = 1. The CTSD16 module only requests  $V_{REFBG}$  during active conversions, when CTSD16SC = 1, and bursts the  $V_{REFBG}$  signal unless REFON = 1 and REFOUT = 1. The DAC12\_A similarly bursts the request for the voltage.

#### 1.2.3.6 DAC12 A

Some devices contain a DAC12\_A module. The DAC12\_A can use the 1.5 V, 2.0 V, or 2.5 V from the variable reference line, and on devices with a CTSD16 module, the DAC12\_A can use the 1.16 V from the  $V_{REFBG}$  reference line for its reference. The DAC12\_A can request its reference directly by the settings within the DAC12\_A module itself except the 1.16 V, which also requires REFOUT = 1. Therefore, if the DAC is enabled and the internal reference is selected, the DAC requests the reference voltage from the REF module. In addition, setting REFON = 1 (REFMSTR = 1) or ADC12REFON = 1 (REFMSTR = 0) can enable the variable reference line independent of the DAC12\_A control bits.

The REFGEN subsystem provides divided versions of the variable reference line for use in the DAC12\_A module. The DAC12\_A module requires either /2 or /3 of the variable reference. The selection of these depends on the control bits inside the DAC12\_A module (DAC12IR, DAC12OG) and is handled automatically by the REF module.

Principle of Operation www.ti.com

When the DAC12\_A selects  $AV_{cc}$  or  $V_{eREF+}$  or  $V_{REFBG}$  (if available) as its reference, the DAC12\_A has its own /2 and /3 resistor string available that scales the input reference appropriately based on the DAC12IR and DAC12OG settings.

#### 1.2.3.7 LCD\_B, LCD\_C

In devices that contain an LCD module, the LCD module requires a reference to generate the proper LCD voltages. The bandgap reference line from the REFGEN subsystem is used for this purpose. The LCD is enabled when LCDON = 1 of the LCD\_B or LCD\_C module. This causes a REFBGREQ from the LCD module to be asserted. The buffered bandgap is available on the bandgap reference line for use by the LCD module.

REF Registers www.ti.com

#### 1.3 **REF Registers**

The REF registers are listed in Table 1-5. The base address can be found in the device specific datasheet. The address offset is listed in Table 1-5.

NOTE: All registers have word or byte register access. For a generic register ANYREG, the suffix "\_L" (ANYREG\_L) refers to the lower byte of the register (bits 0 through 7). The suffix "\_H" (ANYREG\_H) refers to the upper byte of the register (bits 8 through 15).

Table 1-5. REF Registers

| Offset | Acronym   | Register Name          | Туре       | Access | Reset | Section       |

|--------|-----------|------------------------|------------|--------|-------|---------------|

| 00h    | REFCTL0   | REF Control Register 0 | Read/write | Word   | 0080h | Section 1.3.1 |

| 00h    | REFCTL0_L |                        | Read/write | Byte   | 80h   |               |

| 01h    | REFCTL0_H |                        | Read/write | Byte   | 00h   |               |

REF Registers www.ti.com

# 1.3.1 REFCTL0 Register (offset = 00h) [reset = 0080h]

REF Control Register 0

## Figure 1-3. REFCTL0 Register

| 15      | 14       | 13     | 12     | 11       | 10         | 9        | 8         |

|---------|----------|--------|--------|----------|------------|----------|-----------|

|         | Rese     | erved  |        | BGMODE   | REFGENBUSY | REFBGACT | REFGENACT |

| r0      | rO       | rO     | r0     | r-(0)    | r-(0)      | r-(0)    | r-(0)     |

| 7       | 6        | 5      | 4      | 3        | 2          | 1        | 0         |

| REFMSTR | Reserved | REF    | /SEL   | REFTCOFF | Reserved   | REFOUT   | REFON     |

| rw-(1)  | r0       | rw-(0) | rw-(0) | rw-(0)   | r0         | rw-(0)   | rw-(0)    |

Can be modified only when REFGENBUSY = 0.

## Table 1-6. REFCTL0 Register Description

| Bit   | Field      | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-12 | Reserved   | R    | 0h    | Reserved. Always reads as 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11    | BGMODE     | R    | Oh    | Bandgap mode. Read only.  0b = Static mode  1b = Sampled mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10    | REFGENBUSY | R    | Oh    | Reference generator busy. Read only.  0b = Reference generator not busy  1b = Reference generator busy                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 9     | REFBGACT   | R    | Oh    | Reference bandgap active. Read only.  0b = Reference bandgap buffer not active  1b = Reference bandgap buffer active                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8     | REFGENACT  | R    | Oh    | Reference generator active. Read only.  0b = Reference generator not active  1b = Reference generator active                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7     | REFMSTR    | RW   | 1h    | REF master control. ADC10_A and CTSD16 devices: Must be written 1.  0b = Reference system controlled by legacy control bits inside the ADC12_A module when available.  1b = Reference system controlled by REFCTL register. Common settings inside the ADC12_A module (if exists) are don't care.                                                                                                                                                                                                                                  |

| 6     | Reserved   | R    | 0h    | Reserved. Always reads as 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5-4   | REFVSEL    | RW   | Oh    | Reference voltage level select for devices  00b = 1.5 V available when reference requested or REFON = 1  01b = 2.0 V available when reference requested or REFON = 1  10b = 2.5 V available when reference requested or REFON = 1  11b = 2.5 V available when reference requested or REFON = 1                                                                                                                                                                                                                                     |

| 3     | REFTCOFF   | RW   | Oh    | Temperature sensor disabled  0b = Temperature sensor enabled  1b = Temperature sensor disabled to save power                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2     | Reserved   | R    | 0h    | Reserved. Always reads as 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1     | REFOUT     | RW   | Oh    | Reference output buffer. ADC10_A devices without reference output buffer: Must be written 0.  0b = Reference output not available externally  1b = Reference output available externally. If ADC12REFBURST = 0, or DAC12_A is enabled, output is available continuously. If ADC12REFBURST = 1, output is available only during an ADC12_A conversion.  For devices with CTSD16, REFON must also be set to 1 for V <sub>REFBG</sub> to be available continuously. Otherwise, V <sub>REFBG</sub> is only available externally when a |

www.ti.com REF Registers

# Table 1-6. REFCTL0 Register Description (continued)

| Bit | Field | Туре | Reset | Description                                                                                                               |

|-----|-------|------|-------|---------------------------------------------------------------------------------------------------------------------------|

| 0   | REFON | RW   | 0h    | Reference enable.                                                                                                         |

|     |       |      |       | ADC10_A: The ADC10_A does not support the reference request. REFON must be set if the internal reference voltage is used. |

|     |       |      |       | 0b = Disables reference if no other reference requests are pending.                                                       |

|     |       |      |       | 1b = Enables reference.                                                                                                   |

REF

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ("TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated