# Chapter 1

SLAU410F-August 2012-Revised March 2018

# Universal Serial Communication Interface - UART Mode

NOTE: This chapter is an excerpt from the MSP430x5xx and MSP430x6xx Family User's Guide.

The most recent version of the full user's guide is available from

http://www.ti.com/lit/pdf/slau208.

The universal serial communication interface (USCI) supports multiple serial communication modes with one hardware module. This chapter discusses the operation of the asynchronous UART mode.

Topic Page

| 1.1 | Universal Serial Communication Interface (USCI) Overview | 2  |

|-----|----------------------------------------------------------|----|

| 1.2 | USCI Introduction – UART Mode                            | 3  |

| 1.3 | USCI Operation – UART Mode                               | 5  |

| 1.4 | USCI_A UART Mode Registers                               | 22 |

|     |                                                          |    |

### 1.1 Universal Serial Communication Interface (USCI) Overview

The USCI modules support multiple serial communication modes. Different USCI modules support different modes. Each different USCI module is named with a different letter. For example, USCI\_A is different from USCI\_B, etc. If more than one identical USCI module is implemented on one device, those modules are named with incrementing numbers. For example, if one device has two USCI\_A modules, they are named USCI\_A0 and USCI\_A1. See the device-specific data sheet to determine which USCI modules, if any, are implemented on which devices.

# USCI\_Ax modules support:

- UART mode

- Pulse shaping for IrDA communications

- · Automatic baud-rate detection for LIN communications

- SPI mode

### USCI\_Bx modules support:

- I2C mode

- SPI mode

#### 1.2 USCI Introduction – UART Mode

In asynchronous mode, the USCI\_Ax modules connect the device to an external system via two external pins, UCAxRXD and UCAxTXD. UART mode is selected when the UCSYNC bit is cleared.

UART mode features include:

- 7- or 8-bit data with odd, even, or non-parity

- Independent transmit and receive shift registers

- · Separate transmit and receive buffer registers

- LSB-first or MSB-first data transmit and receive

- · Built-in idle-line and address-bit communication protocols for multiprocessor systems

- Receiver start-edge detection for auto wake up from LPMx modes (wake up from LPMx.5 is not supported)

- Programmable baud rate with modulation for fractional baud-rate support

- Status flags for error detection and suppression

- Status flags for address detection

- Independent interrupt capability for receive and transmit

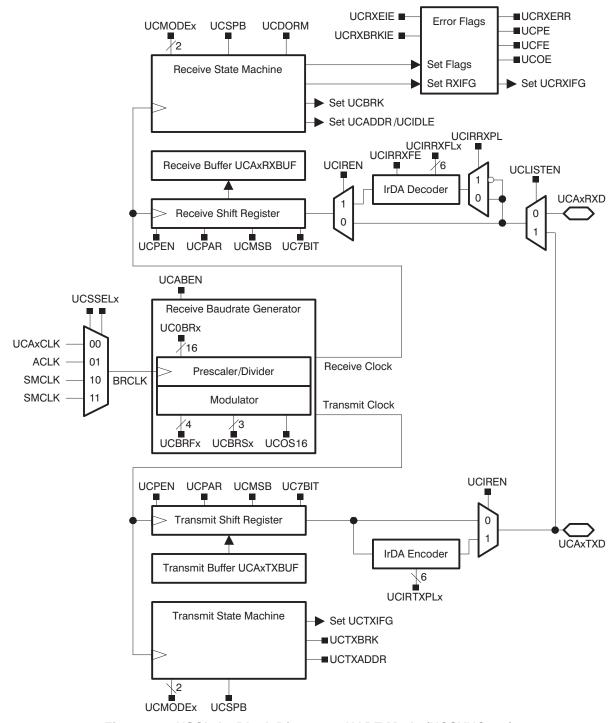

Figure 1-1 shows the USCI\_Ax when configured for UART mode.

Figure 1-1. USCI\_Ax Block Diagram – UART Mode (UCSYNC = 0)

### 1.3 USCI Operation – UART Mode

In UART mode, the USCI transmits and receives characters at a bit rate asynchronous to another device. Timing for each character is based on the selected baud rate of the USCI. The transmit and receive functions use the same baud-rate frequency.

#### 1.3.1 USCI Initialization and Reset

The USCI is reset by a PUC or by setting the UCSWRST bit. After a PUC, the UCSWRST bit is automatically set, keeping the USCI in a reset condition. When set, the UCSWRST bit resets the UCRXIE, UCTXIE, UCRXIFG, UCRXERR, UCBRK, UCPE, UCOE, UCFE, UCSTOE, and UCBTOE bits, and sets the UCTXIFG bit. Clearing UCSWRST releases the USCI for operation.

To avoid unpredictable behavior, configure or reconfigure the USCI\_A module only when UCSWRST is set.

#### NOTE: Initializing or reconfiguring the USCI module

The recommended USCI initialization/reconfiguration process is:

- Set UCSWRST (BIS.B #UCSWRST, &UCAXCTL1).

- 2. Initialize all USCI registers with UCSWRST = 1 (including UCAxCTL1).

- Configure ports.

- 4. Clear UCSWRST via software (BIC.B #UCSWRST, &UCAxCTL1).

- Enable interrupts (optional) via UCRXIE and/or UCTXIE.

#### 1.3.2 Character Format

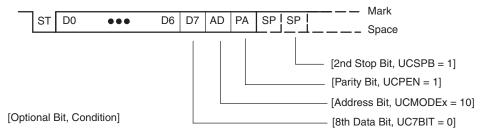

The UART character format (see Figure 1-2) consists of a start bit, seven or eight data bits, an even/odd/no parity bit, an address bit (address-bit mode), and one or two stop bits. The UCMSB bit controls the direction of the transfer and selects LSB or MSB first. LSB first is typically required for UART communication.

Figure 1-2. Character Format

# 1.3.3 Asynchronous Communication Format

When two devices communicate asynchronously, no multiprocessor format is required for the protocol. When three or more devices communicate, the USCI supports the idle-line and address-bit multiprocessor communication formats.

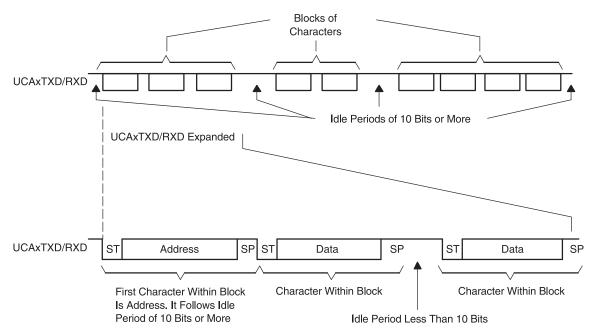

# 1.3.3.1 Idle-Line Multiprocessor Format

When UCMODEx = 01, the idle-line multiprocessor format is selected. Blocks of data are separated by an idle time on the transmit or receive lines (see Figure 1-3). An idle receive line is detected when ten or more continuous ones (marks) are received after the one or two stop bits of a character. The baud-rate generator is switched off after reception of an idle line until the next start edge is detected. When an idle line is detected, the UCIDLE bit is set.

The first character received after an idle period is an address character. The UCIDLE bit is used as an address tag for each block of characters. In idle-line multiprocessor format, this bit is set when a received character is an address.

Figure 1-3. Idle-Line Format

The UCDORM bit is used to control data reception in the idle-line multiprocessor format. When UCDORM = 1, all non-address characters are assembled but not transferred into the UCAxRXBUF, and interrupts are not generated. When an address character is received, the character is transferred into UCAxRXBUF, UCRXIFG is set, and any applicable error flag is set when UCRXEIE = 1. When UCRXEIE = 0 and an address character is received but has a framing error or parity error, the character is not transferred into UCAxRXBUF and UCRXIFG is not set.

If an address is received, user software can validate the address and must reset UCDORM to continue receiving data. If UCDORM remains set, only address characters are received. When UCDORM is cleared during the reception of a character, the receive interrupt flag is set after the reception completed. The UCDORM bit is not modified by the USCI hardware automatically.

For address transmission in idle-line multiprocessor format, a precise idle period can be generated by the USCI to generate address character identifiers on UCAxTXD. The double-buffered UCTXADDR flag indicates if the next character loaded into UCAxTXBUF is preceded by an idle line of 11 bits. UCTXADDR is automatically cleared when the start bit is generated.

#### 1.3.3.1.1 Transmitting an Idle Frame

The following procedure sends out an idle frame to indicate an address character followed by associated data:

- Set UCTXADDR, then write the address character to UCAxTXBUF. UCAxTXBUF must be ready for new data (UCTXIFG = 1).

- This generates an idle period of exactly 11 bits followed by the address character. UCTXADDR is reset automatically when the address character is transferred from UCAxTXBUF into the shift register.

- Write desired data characters to UCAxTXBUF. UCAxTXBUF must be ready for new data (UCTXIFG = 1).

The data written to UCAxTXBUF is transferred to the shift register and transmitted as soon as the shift register is ready for new data.

The idle-line time must not be exceeded between address and data transmission or between data transmissions. Otherwise, the transmitted data is misinterpreted as an address.

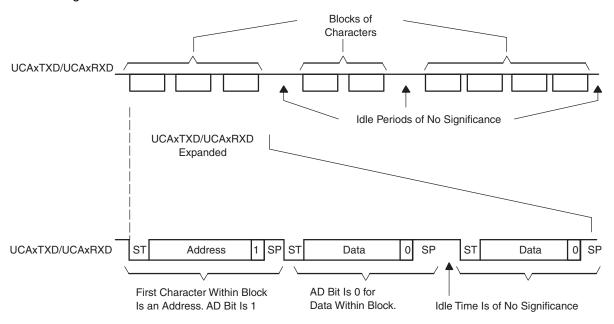

#### 1.3.3.2 Address-Bit Multiprocessor Format

When UCMODEx = 10, the address-bit multiprocessor format is selected. Each processed character contains an extra bit used as an address indicator (see Figure 1-4). The first character in a block of characters carries a set address bit that indicates that the character is an address. The USCI UCADDR bit is set when a received character has its address bit set and is transferred to UCAxRXBUF.

The UCDORM bit is used to control data reception in the address-bit multiprocessor format. When UCDORM is set, data characters with address bit = 0 are assembled by the receiver but are not transferred to UCAxRXBUF and no interrupts are generated. When a character containing a set address bit is received, the character is transferred into UCAxRXBUF, UCRXIFG is set, and any applicable error flag is set when UCRXEIE = 1. When UCRXEIE = 0 and a character containing a set address bit is received but has a framing error or parity error, the character is not transferred into UCAxRXBUF and UCRXIFG is not set.

If an address is received, user software can validate the address and must reset UCDORM to continue receiving data. If UCDORM remains set, only address characters with address bit = 1 are received. The UCDORM bit is not modified by the USCI hardware automatically.

When UCDORM = 0, all received characters set the receive interrupt flag UCRXIFG. If UCDORM is cleared during the reception of a character, the receive interrupt flag is set after the reception is completed.

For address transmission in address-bit multiprocessor mode, the address bit of a character is controlled by the UCTXADDR bit. The value of the UCTXADDR bit is loaded into the address bit of the character transferred from UCAxTXBUF to the transmit shift register. UCTXADDR is automatically cleared when the start bit is generated.

Figure 1-4. Address-Bit Multiprocessor Format

#### 1.3.3.2.1 Break Reception and Generation

When UCMODEx = 00, 01, or 10, the receiver detects a break when all data, parity, and stop bits are low, regardless of the parity, address mode, or other character settings. When a break is detected, the UCBRK bit is set. If the break interrupt enable bit (UCBRKIE) is set, the receive interrupt flag UCRXIFG is also set. In this case, the value in UCAxRXBUF is 0h, because all data bits were zero.

To transmit a break, set the UCTXBRK bit, then write 0h to UCAxTXBUF. UCAxTXBUF must be ready for new data (UCTXIFG = 1). This generates a break with all bits low. UCTXBRK is automatically cleared when the start bit is generated.

#### 1.3.4 Automatic Baud-Rate Detection

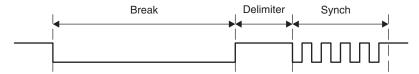

When UCMODEx = 11, UART mode with automatic baud-rate detection is selected. For automatic baud-rate detection, a data frame is preceded by a synchronization sequence that consists of a break and a synch field. A break is detected when 11 or more continuous zeros (spaces) are received. If the length of the break exceeds 21 bit times the break timeout error flag UCBTOE is set. The USCI can not transmit data while receiving the break/sync field. The synch field follows the break as shown in Figure 1-5.

Figure 1-5. Auto Baud-Rate Detection - Break/Synch Sequence

For LIN conformance, the character format should be set to eight data bits, LSB first, no parity, and one stop bit. No address bit is available.

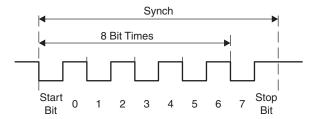

The synch field consists of the data 055h inside a byte field (see Figure 1-6). The synchronization is based on the time measurement between the first falling edge and the last falling edge of the pattern. The transmit baud-rate generator is used for the measurement if automatic baud-rate detection is enabled by setting UCABDEN. Otherwise, the pattern is received but not measured. The result of the measurement is transferred into the baud-rate control registers (UCAxBR0, UCAxBR1, and UCAxMCTL). If the length of the synch field exceeds the measurable time, the synch timeout error flag UCSTOE is set.

Figure 1-6. Auto Baud-Rate Detection - Synch Field

The UCDORM bit is used to control data reception in this mode. When UCDORM is set, all characters are received but not transferred into the UCAxRXBUF, and interrupts are not generated. When a break/synch field is detected, the UCBRK flag is set. The character following the break/synch field is transferred into UCAxRXBUF and the UCRXIFG interrupt flag is set. Any applicable error flag is also set. If the UCBRKIE bit is set, reception of the break/synch sets the UCRXIFG. The UCBRK bit is reset by user software or by reading the receive buffer UCAxRXBUF.

When a break/synch field is received, user software must reset UCDORM to continue receiving data. If UCDORM remains set, only the character after the next reception of a break/synch field is received. The UCDORM bit is not modified by the USCI hardware automatically.

When UCDORM = 0, all received characters set the receive interrupt flag UCRXIFG. If UCDORM is cleared during the reception of a character, the receive interrupt flag is set after the reception is complete.

The counter used to detect the baud rate is limited to 07FFFh (32767) counts. This means the minimum baud rate detectable is 488 baud in oversampling mode and 30 baud in low-frequency mode.

The automatic baud-rate detection mode can be used in a full-duplex communication system with some restrictions. The USCI can not transmit data while receiving the break/sync field and, if a 0h byte with framing error is received, any data transmitted during this time gets corrupted. The latter case can be discovered by checking the received data and the UCFE bit.

### 1.3.4.1 Transmitting a Break/Synch Field

The following procedure transmits a break/synch field:

- 1. Set UCTXBRK with UMODEx = 11.

- 2. Write 055h to UCAxTXBUF. UCAxTXBUF must be ready for new data (UCTXIFG = 1).

- This generates a break field of 13 bits followed by a break delimiter and the synch character. The length of the break delimiter is controlled with the UCDELIMx bits. UCTXBRK is reset automatically when the synch character is transferred from UCAxTXBUF into the shift register.

- 3. Write desired data characters to UCAxTXBUF. UCAxTXBUF must be ready for new data (UCTXIFG = 1).

The data written to UCAxTXBUF is transferred to the shift register and transmitted as soon as the shift register is ready for new data.

# 1.3.5 IrDA Encoding and Decoding

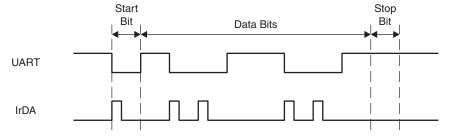

When UCIREN is set, the IrDA encoder and decoder are enabled and provide hardware bit shaping for IrDA communication.

#### 1.3.5.1 IrDA Encoding

The encoder sends a pulse for every zero bit in the transmit bitstream coming from the UART (see Figure 1-7). The pulse duration is defined by UCIRTXPLx bits specifying the number of one-half clock periods of the clock selected by UCIRTXCLK.

Figure 1-7. UART vs IrDA Data Format

To set the pulse time of 3/16 bit period required by the IrDA standard, the BITCLK16 clock is selected with UCIRTXCLK = 1, and the pulse length is set to six one-half clock cycles with UCIRTXPLx = 6 - 1 = 5.

When UCIRTXCLK = 0, the pulse length  $t_{PULSE}$  is based on BRCLK and is calculated as:

UCIRTXPLx =

$$t_{PULSE} \times 2 \times f_{BRCLK} - 1$$

When UCIRTXCLK = 0, the prescaler UCBRx must to be set to a value greater or equal to 5.

### 1.3.5.2 IrDA Decoding

The decoder detects high pulses when UCIRRXPL = 0. Otherwise, it detects low pulses. In addition to the analog deglitch filter, an additional programmable digital filter stage can be enabled by setting UCIRRXFE. When UCIRRXFE is set, only pulses longer than the programmed filter length are passed. Shorter pulses are discarded. The equation to program the filter length UCIRRXFLx is:

UCIRRXFLx =

$$(t_{PULSE} - t_{WAKE}) \times 2 \times f_{BRCLK} - 4$$

#### Where:

t<sub>PULSE</sub> = Minimum receive pulse width

$t_{\text{WAKE}}$  = Wake time from any low-power mode. Zero when the device is in active mode.

#### NOTE: Reliable reception of IrDA signals

To receive incoming IrDA signals reliably, make sure that at least one of the following procedures are implemented:

- Enable the digital filter stage with UCIRRXFE = 1.

- Use a parity bit to detect corrupted bytes.

- Check the correctness of received data frames using a checksum or CRC.

- With parity or CRC checks, use a protocol that acknowledges received data frame and resends data if the sender does not receive an acknowledgment.

#### 1.3.6 Automatic Error Detection

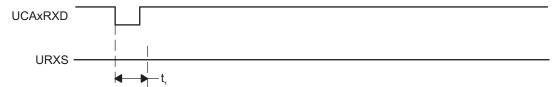

Glitch suppression prevents the USCI from being accidentally started. Any pulse on UCAxRXD shorter than the deglitch time t<sub>t</sub> (approximately 150 ns) is ignored (see the device-specific data sheet for parameters).

When a low period on UCAxRXD exceeds t<sub>t</sub>, a majority vote is taken for the start bit. If the majority vote fails to detect a valid start bit, the USCI halts character reception and waits for the next low period on UCAxRXD. The majority vote is also used for each bit in a character to prevent bit errors.

The USCI module automatically detects framing errors, parity errors, overrun errors, and break conditions when receiving characters. The bits UCFE, UCPE, UCOE, and UCBRK are set when their respective condition is detected. When the error flags UCFE, UCPE, or UCOE are set, UCRXERR is also set. The error conditions are described in Table 1-1.

Table 1-1. Receive Error Conditions

| Error Condition | Error Flag | Description                                                                                                                                                                                                                                                                           |

|-----------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Framing error   | UCFE       | A framing error occurs when a low stop bit is detected. When two stop bits are used, both stop bits are checked for framing error. When a framing error is detected, the UCFE bit is set.                                                                                             |

| Parity error    | UCPE       | A parity error is a mismatch between the number of 1s in a character and the value of the parity bit. When an address bit is included in the character, it is included in the parity calculation. When a parity error is detected, the UCPE bit is set.                               |

| Receive overrun | UCOE       | An overrun error occurs when a character is loaded into UCAxRXBUF before the prior character has been read. When an overrun occurs, the UCOE bit is set.                                                                                                                              |

| Break condition | UCBRK      | When not using automatic baud-rate detection, a break is detected when all data, parity, and stop bits are low. When a break condition is detected, the UCBRK bit is set. A break condition can also set the interrupt flag UCRXIFG if the break interrupt enable UCBRKIE bit is set. |

When UCRXEIE = 0 and a framing error or parity error is detected, no character is received into UCAxRXBUF. When UCRXEIE = 1, characters are received into UCAxRXBUF and any applicable error bit is set.

When any of the UCFE, UCPE, UCOE, UCBRK, or UCRXERR bit is set, the bit remains set until user software resets it or UCAxRXBUF is read. UCOE must be reset by reading UCAxRXBUF. Otherwise, it does not function properly. To detect overflows reliably the following flow is recommended. After a character was received and UCAxRXIFG is set, first read UCAxSTAT to check the error flags including the overflow flag UCOE. Read UCAxRXBUF next. This clears all error flags except UCOE, if UCAxRXBUF was overwritten between the read access to UCAxSTAT and to UCAxRXBUF. Therefore, the UCOE flag should be checked after reading UCAxRXBUF to detect this condition. Note that, in this case, the UCRXERR flag is not set.

#### 1.3.7 USCI Receive Enable

The USCI module is enabled by clearing the UCSWRST bit and the receiver is ready and in an idle state. The receive baud rate generator is in a ready state but is not clocked nor producing any clocks.

The falling edge of the start bit enables the baud rate generator and the UART state machine checks for a valid start bit. If no valid start bit is detected the UART state machine returns to its idle state and the baud rate generator is turned off again. If a valid start bit is detected, a character is received.

When the idle-line multiprocessor mode is selected with UCMODEx = 01 the UART state machine checks for an idle line after receiving a character. If a start bit is detected another character is received. Otherwise the UCIDLE flag is set after 10 ones are received and the UART state machine returns to its idle state and the baud rate generator is turned off.

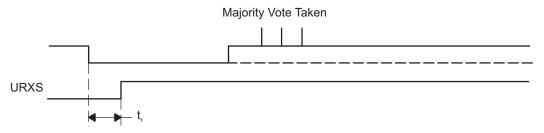

#### 1.3.7.1 Receive Data Glitch Suppression

Glitch suppression prevents the USCI from being accidentally started. Any glitch on UCAxRXD shorter than the deglitch time  $t_t$  (approximately 150 ns) is ignored by the USCI, and further action is initiated as shown in Figure 1-8 (see the device-specific data sheet for parameters).

Figure 1-8. Glitch Suppression, USCI Receive Not Started

When a glitch is longer than  $t_{t_i}$  or a valid start bit occurs on UCAxRXD, the USCI receive operation is started and a majority vote is taken (see Figure 1-9). If the majority vote fails to detect a start bit, the USCI halts character reception.

Figure 1-9. Glitch Suppression, USCI Activated

### 1.3.8 USCI Transmit Enable

The USCI module is enabled by clearing the UCSWRST bit and the transmitter is ready and in an idle state. The transmit baud-rate generator is ready but is not clocked nor producing any clocks.

A transmission is initiated by writing data to UCAxTXBUF. When this occurs, the baud-rate generator is enabled, and the data in UCAxTXBUF is moved to the transmit shift register on the next BITCLK after the transmit shift register is empty. UCTXIFG is set when new data can be written into UCAxTXBUF.

Transmission continues as long as new data is available in UCAxTXBUF at the end of the previous byte transmission. If new data is not in UCAxTXBUF when the previous byte has transmitted, the transmitter returns to its idle state and the baud-rate generator is turned off.

#### 1.3.9 UART Baud-Rate Generation

The USCI baud-rate generator is capable of producing standard baud rates from nonstandard source frequencies. It provides two modes of operation selected by the UCOS16 bit. The baud-rate is generate using the BRCLK that can be sourced by the external clock UCAxCLK, or the internal clocks ACLK or SMCLK depending on the UCSSELx settings.

# 1.3.9.1 Low-Frequency Baud-Rate Generation

The low-frequency mode is selected when UCOS16 = 0. This mode allows generation of baud rates from low frequency clock sources (for example, 9600 baud from a 32768-Hz crystal). By using a lower input frequency, the power consumption of the module is reduced. Using this mode with higher frequencies and higher prescaler settings causes the majority votes to be taken in an increasingly smaller window and, thus, decrease the benefit of the majority vote.

In low-frequency mode, the baud-rate generator uses one prescaler and one modulator to generate bit clock timing. This combination supports fractional divisors for baud-rate generation. In this mode, the maximum USCI baud rate is one-third the UART source clock frequency BRCLK.

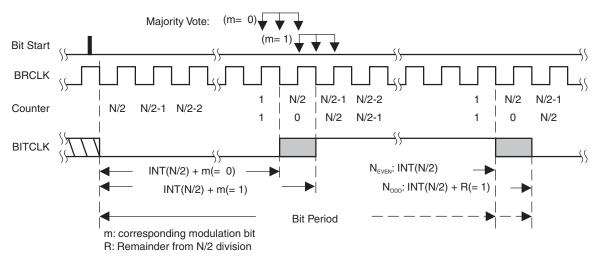

Timing for each bit is shown in Figure 1-10. For each bit received, a majority vote is taken to determine the bit value. These samples occur at the N/2 - 1/2, N/2, and N/2 + 1/2 BRCLK periods, where N is the number of BRCLKs per BITCLK.

Figure 1-10. BITCLK Baud-Rate Timing With UCOS16 = 0

Modulation is based on the UCBRSx setting (see Table 1-2). A 1 in the table indicates that m = 1 and the corresponding BITCLK period is one BRCLK period longer than a BITCLK period with m = 0. The modulation wraps around after eight bits but restarts with each new start bit.

Table 1-2. BITCLK Modulation Pattern

| UCBRSx | Bit 0<br>(Start Bit) | Bit 1 | Bit 2 | Bit 3 | Bit 4 | Bit 5 | Bit 6 | Bit 7 |

|--------|----------------------|-------|-------|-------|-------|-------|-------|-------|

| 0      | 0                    | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 1      | 0                    | 1     | 0     | 0     | 0     | 0     | 0     | 0     |

| 2      | 0                    | 1     | 0     | 0     | 0     | 1     | 0     | 0     |

| 3      | 0                    | 1     | 0     | 1     | 0     | 1     | 0     | 0     |

| 4      | 0                    | 1     | 0     | 1     | 0     | 1     | 0     | 1     |

| 5      | 0                    | 1     | 1     | 1     | 0     | 1     | 0     | 1     |

| 6      | 0                    | 1     | 1     | 1     | 0     | 1     | 1     | 1     |

| 7      | 0                    | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

# 1.3.9.2 Oversampling Baud-Rate Generation

The oversampling mode is selected when UCOS16 = 1. This mode supports sampling a UART bitstream with higher input clock frequencies. This results in majority votes that are always 1/16 of a bit clock period apart. This mode also easily supports IrDA pulses with a 3/16 bit time when the IrDA encoder and decoder are enabled.

This mode uses one prescaler and one modulator to generate the BITCLK16 clock that is 16 times faster than the BITCLK. An additional divider and modulator stage generates BITCLK from BITCLK16. This combination supports fractional divisions of both BITCLK16 and BITCLK for baud-rate generation. In this mode, the maximum USCI baud rate is 1/16 the UART source clock frequency BRCLK. When UCBRx is set to 0 or 1, the first prescaler and modulator stage is bypassed and BRCLK is equal to BITCLK16 – in this case, no modulation for the BITCLK16 is possible and, thus, the UCBRFx bits are ignored.

Modulation for BITCLK16 is based on the UCBRFx setting (see Table 1-3). A 1 in the table indicates that the corresponding BITCLK16 period is one BRCLK period longer than the periods m = 0. The modulation restarts with each new bit timing.

Modulation for BITCLK is based on the UCBRSx setting (see Table 1-2) as previously described.

Number of BITCLK16 Clocks After Last Falling BITCLK Edge **UCBRFx** 00h 01h n 02h 03h 04h 05h 06h 07h 08h 09h 0Ah 0Bh 0Ch 0Dh 0Eh 0Fh

Table 1-3. BITCLK16 Modulation Pattern

### 1.3.10 Setting a Baud Rate

For a given BRCLK clock source, the baud rate used determines the required division factor N:

$N = f_{BRCLK}/Baudrate$

The division factor N is often a noninteger value, thus, at least one divider and one modulator stage is used to meet the factor as closely as possible.

If N is equal or greater than 16, the oversampling baud-rate generation mode can be chosen by setting UCOS16.

#### 1.3.10.1 Low-Frequency Baud-Rate Mode Setting

In low-frequency mode, the integer portion of the divisor is realized by the prescaler:

$$UCBRx = INT(N)$$

and the fractional portion is realized by the modulator with the following nominal formula:

$$UCBRSx = round[(N - INT(N)) \times 8]$$

Incrementing or decrementing the UCBRSx setting by one count may give a lower maximum bit error for any given bit. To determine if this is the case, a detailed error calculation must be performed for each bit for each UCBRSx setting.

# 1.3.10.2 Oversampling Baud-Rate Mode Setting

In the oversampling mode, the prescaler is set to:

$$UCBRx = INT(N/16)$$

and the first stage modulator is set to:

$$UCBRFx = round([(N/16) - INT(N/16)] \times 16)$$

When greater accuracy is required, the UCBRSx modulator can also be implemented with values from 0 to 7. To find the setting that gives the lowest maximum bit error rate for any given bit, a detailed error calculation must be performed for all settings of UCBRSx from 0 to 7 with the initial UCBRFx setting, and with the UCBRFx setting incremented and decremented by one.

#### 1.3.11 Transmit Bit Timing

The timing for each character is the sum of the individual bit timings. Using the modulation features of the baud-rate generator reduces the cumulative bit error. The individual bit error can be calculated using the following steps.

#### 1.3.11.1 Low-Frequency Baud-Rate Mode Bit Timing

In low-frequency mode, calculate the length of bit i T<sub>bit.Tx</sub>[i] based on the UCBRx and UCBRSx settings:

$$T_{\text{bit TX}}[i] = (1/f_{\text{BRCLK}})(\text{UCBRx} + m_{\text{UCBRSx}}[i])$$

Where:

$m_{UCBRSx}[i] = Modulation of bit i from Table 1-2$

# 1.3.11.2 Oversampling Baud-Rate Mode Bit Timing

In oversampling baud-rate mode, calculate the length of bit i T<sub>bit,TX</sub>[i] based on the baud-rate generator UCBRx, UCBRFx and UCBRSx settings:

$$T_{\text{bit,TX}}[i] = \frac{1}{f_{\text{BRCLK}}} \left( (16 + m_{\text{UCBRSx}}[i]) \times \text{UCBRx} + \sum_{j=0}^{15} m_{\text{UCBRFx}}[j] \right)$$

Where:

$$\sum_{j=0}^{15} m_{\text{UCBRFx}}[j] = \text{Sum of ones from the corresponding row in Table 1-3}$$

$m_{UCBRSx}[i] = Modulation of bit i from Table 1-2$

This results in an end-of-bit time thit TX[i] equal to the sum of all previous and the current bit times:

$$\mathsf{T}_{\mathsf{bit},\mathsf{TX}}[\mathsf{i}] = \sum_{\mathsf{j}\,=\,0}^{\mathsf{I}}\,\mathsf{T}_{\mathsf{bit},\mathsf{TX}}[\mathsf{j}]$$

To calculate bit error, this time is compared to the ideal bit time t<sub>bit.ideal.TX</sub>[i]:

$$t_{bit.ideal.TX}[i] = (1/Baudrate)(i + 1)$$

This results in an error normalized to one ideal bit time (1/baudrate):

$$Error_{TX}[i] = (t_{bit,TX}[i] - t_{bit,ideal,TX}[i]) \times Baudrate \times 100\%$$

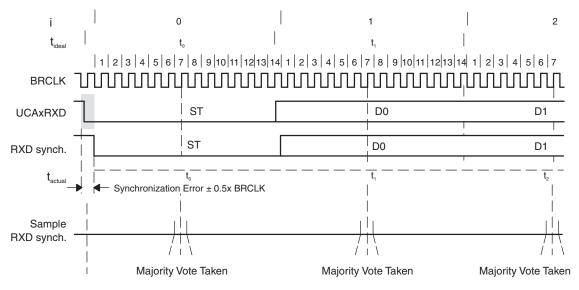

### 1.3.12 Receive Bit Timing

Receive timing error consists of two error sources. The first is the bit-to-bit timing error similar to the transmit bit timing error. The second is the error between a start edge occurring and the start edge being accepted by the USCI module. Figure 1-11 shows the asynchronous timing errors between data on the UCAxRXD pin and the internal baud-rate clock. This results in an additional synchronization error. The synchronization error  $t_{\text{SYNC}}$  is between -0.5 BRCLKs and +0.5 RCLKs, independent of the selected baud-rate generation mode.

Figure 1-11. Receive Error

The ideal sampling time  $t_{\text{bit,ideal,RX}}[i]$  is in the middle of a bit period:

$$t_{bit,ideal,RX}[i] = (1/Baudrate)(i + 0.5)$$

The real sampling time,  $t_{bit,RX}[i]$ , is equal to the sum of all previous bits according to the formulas shown in the transmit timing section, plus one-half BITCLK for the current bit i, plus the synchronization error  $t_{SYNC}$ .

This results in the following  $t_{\text{bit},RX}[i]$  for the low-frequency baud-rate mode:

$$t_{\text{bit,RX}}[i] = t_{\text{SYNC}} + \sum_{i=0}^{i-1} T_{\text{bit,RX}}[j] + \frac{1}{f_{\text{BRCLK}}} \left( \text{INT}(\frac{1}{2}\text{UCBRx}) + m_{\text{UCBRSX}}[i] \right)$$

Where:

$$T_{bit,RX}[i] = (1/f_{BRCLK})(UCBRx + m_{UCBRSx}[i])$$

$m_{UCBRSx}[i] = Modulation of bit i from Table 1-2$

For the oversampling baud-rate mode, the sampling time  $t_{\text{bit},RX}[i]$  of bit i is calculated by:

$$t_{\text{bit,RX}}[i] = t_{\text{SYNC}} + \sum_{j=0}^{i-1} T_{\text{bit,RX}}[j] + \frac{1}{f_{\text{BRCLK}}} \Big( (8 + m_{\text{UCBRSx}}[i]) \times \text{UCBRx} \\ \times \sum_{j=0}^{i-1} T_{\text{bit,RX}}[i] \Big)$$

Where:

$$T_{\text{\tiny bit,RX}}[i] = \frac{1}{f_{\text{\tiny BRCLK}}} \Big( (16 + m_{\text{\tiny UCBRSx}}[i]) \times \text{\tiny UCBRX} + \sum_{j=0}^{15} m_{\text{\tiny UCBRFx}}[j] \Big)$$

$$\sum_{j=0}^{7+m_{\text{UCBRFx}}[i]} m_{\text{UCBRFx}}[j] = \text{Sum of ones from columns 0 to } (7+m_{\text{UCBRSx}}[i]) \text{ from the corresponding row in Table 1-3.}$$

$m_{UCBRSx}[i] = Modulation of bit i from Table 1-2$

This results in an error normalized to one ideal bit time (1/baudrate) according to the following formula:

$$Error_{RX}[i] = (t_{bit,RX}[i] - t_{bit,ideal,RX}[i]) \times Baudrate \times 100\%$$

# 1.3.13 Typical Baud Rates and Errors

Standard baud-rate data for UCBRx, UCBRSx, and UCBRFx are listed in Table 1-4 and Table 1-5 for a 32,768-Hz crystal sourcing ACLK and typical SMCLK frequencies. Make sure that the selected BRCLK frequency does not exceed the device-specific maximum USCI input frequency (see the device-specific data sheet).

The receive error is the accumulated time versus the ideal scanning time in the middle of each bit. The worst-case error is given for the reception of an 8-bit character with parity and one stop bit including synchronization error.

The transmit error is the accumulated timing error versus the ideal time of the bit period. The worst-case error is given for the transmission of an 8-bit character with parity and stop bit.

Table 1-4. Commonly Used Baud Rates, Settings, and Errors, UCOS16 = 0

| BRCLK<br>Frequency<br>(Hz) | Baud Rate<br>(baud) | UCBRx | UCBRSx | UCBRFx |       | n TX Error<br>%) |       | RX Error<br>%) |

|----------------------------|---------------------|-------|--------|--------|-------|------------------|-------|----------------|

| 32 768                     | 1200                | 27    | 2      | 0      | -2.8  | 1.4              | -5.9  | 2.0            |

| 32 768                     | 2400                | 13    | 6      | 0      | -4.8  | 6.0              | -9.7  | 8.3            |

| 32 768                     | 4800                | 6     | 7      | 0      | -12.1 | 5.7              | -13.4 | 19.0           |

| 32 768                     | 9600                | 3     | 3      | 0      | -21.1 | 15.2             | -44.3 | 21.3           |

| 1 000 000                  | 9600                | 104   | 1      | 0      | -0.5  | 0.6              | -0.9  | 1.2            |

| 1 000 000                  | 19200               | 52    | 0      | 0      | -1.8  | 0                | -2.6  | 0.9            |

| 1 000 000                  | 38400               | 26    | 0      | 0      | -1.8  | 0                | -3.6  | 1.8            |

| 1 000 000                  | 57600               | 17    | 3      | 0      | -2.1  | 4.8              | -6.8  | 5.8            |

| 1 000 000                  | 115200              | 8     | 6      | 0      | -7.8  | 6.4              | -9.7  | 16.1           |

| 1 048 576                  | 9600                | 109   | 2      | 0      | -0.2  | 0.7              | -1.0  | 0.8            |

| 1 048 576                  | 19200               | 54    | 5      | 0      | -1.1  | 1.0              | -1.5  | 2.5            |

| 1 048 576                  | 38400               | 27    | 2      | 0      | -2.8  | 1.4              | -5.9  | 2.0            |

| 1 048 576                  | 57600               | 18    | 1      | 0      | -4.6  | 3.3              | -6.8  | 6.6            |

| 1 048 576                  | 115200              | 9     | 1      | 0      | -1.1  | 10.7             | -11.5 | 11.3           |

| 4 000 000                  | 9600                | 416   | 6      | 0      | -0.2  | 0.2              | -0.2  | 0.4            |

| 4 000 000                  | 19200               | 208   | 3      | 0      | -0.2  | 0.5              | -0.3  | 0.8            |

| 4 000 000                  | 38400               | 104   | 1      | 0      | -0.5  | 0.6              | -0.9  | 1.2            |

| 4 000 000                  | 57600               | 69    | 4      | 0      | -0.6  | 0.8              | -1.8  | 1.1            |

| 4 000 000                  | 115200              | 34    | 6      | 0      | -2.1  | 0.6              | -2.5  | 3.1            |

| 4 000 000                  | 230400              | 17    | 3      | 0      | -2.1  | 4.8              | -6.8  | 5.8            |

| 4 194 304                  | 9600                | 436   | 7      | 0      | -0.3  | 0                | -0.3  | 0.2            |

Table 1-4. Commonly Used Baud Rates, Settings, and Errors, UCOS16 = 0 (continued)

| BRCLK<br>Frequency<br>(Hz) | Baud Rate<br>(baud) | UCBRx | UCBRSx | UCBRFx |       | n TX Error<br>%) |       | RX Error<br>%) |

|----------------------------|---------------------|-------|--------|--------|-------|------------------|-------|----------------|

| 4 194 304                  | 19200               | 218   | 4      | 0      | -0.2  | 0.2              | -0.3  | 0.6            |

| 4 194 304                  | 57600               | 72    | 7      | 0      | -1.1  | 0.6              | -1.3  | 1.9            |

| 4 194 304                  | 115200              | 36    | 3      | 0      | -1.9  | 1.5              | -2.7  | 3.4            |

| 8 000 000                  | 9600                | 833   | 2      | 0      | -0.1  | 0                | -0.2  | 0.1            |

| 8 000 000                  | 19200               | 416   | 6      | 0      | -0.2  | 0.2              | -0.2  | 0.4            |

| 8 000 000                  | 38400               | 208   | 3      | 0      | -0.2  | 0.5              | -0.3  | 0.8            |

| 8 000 000                  | 57600               | 138   | 7      | 0      | -0.7  | 0                | -0.8  | 0.6            |

| 8 000 000                  | 115200              | 69    | 4      | 0      | -0.6  | 0.8              | -1.8  | 1.1            |

| 8 000 000                  | 230400              | 34    | 6      | 0      | -2.1  | 0.6              | -2.5  | 3.1            |

| 8 000 000                  | 460800              | 17    | 3      | 0      | -2.1  | 4.8              | -6.8  | 5.8            |

| 8 388 608                  | 9600                | 873   | 7      | 0      | -0.1  | 0.06             | -0.2  | 0.1            |

| 8 388 608                  | 19200               | 436   | 7      | 0      | -0.3  | 0                | -0.3  | 0.2            |

| 8 388 608                  | 57600               | 145   | 5      | 0      | -0.5  | 0.3              | -1.0  | 0.5            |

| 8 388 608                  | 115200              | 72    | 7      | 0      | -1.1  | 0.6              | -1.3  | 1.9            |

| 12 000 000                 | 9600                | 1250  | 0      | 0      | 0     | 0                | -0.05 | 0.05           |

| 12 000 000                 | 19200               | 625   | 0      | 0      | 0     | 0                | -0.2  | 0              |

| 12 000 000                 | 38400               | 312   | 4      | 0      | -0.2  | 0                | -0.2  | 0.2            |

| 12 000 000                 | 57600               | 208   | 2      | 0      | -0.5  | 0.2              | -0.6  | 0.5            |

| 12 000 000                 | 115200              | 104   | 1      | 0      | -0.5  | 0.6              | -0.9  | 1.2            |

| 12 000 000                 | 230400              | 52    | 0      | 0      | -1.8  | 0                | -2.6  | 0.9            |

| 12 000 000                 | 460800              | 26    | 0      | 0      | -1.8  | 0                | -3.6  | 1.8            |

| 16 000 000                 | 9600                | 1666  | 6      | 0      | -0.05 | 0.05             | -0.05 | 0.1            |

| 16 000 000                 | 19200               | 833   | 2      | 0      | -0.1  | 0.05             | -0.2  | 0.1            |

| 16 000 000                 | 38400               | 416   | 6      | 0      | -0.2  | 0.2              | -0.2  | 0.4            |

| 16 000 000                 | 57600               | 277   | 7      | 0      | -0.3  | 0.3              | -0.5  | 0.4            |

| 16 000 000                 | 115200              | 138   | 7      | 0      | -0.7  | 0                | -0.8  | 0.6            |

| 16 000 000                 | 230400              | 69    | 4      | 0      | -0.6  | 0.8              | -1.8  | 1.1            |

| 16 000 000                 | 460800              | 34    | 6      | 0      | -2.1  | 0.6              | -2.5  | 3.1            |

| 16 777 216                 | 9600                | 1747  | 5      | 0      | -0.04 | 0.03             | -0.08 | 0.05           |

| 16 777 216                 | 19200               | 873   | 7      | 0      | -0.09 | 0.06             | -0.2  | 0.1            |

| 16 777 216                 | 57600               | 291   | 2      | 0      | -0.2  | 0.2              | -0.5  | 0.2            |

| 16 777 216                 | 115200              | 145   | 5      | 0      | -0.5  | 0.3              | -1.0  | 0.5            |

| 20 000 000                 | 9600                | 2083  | 2      | 0      | -0.05 | 0.02             | -0.09 | 0.02           |

| 20 000 000                 | 19200               | 1041  | 6      | 0      | -0.06 | 0.06             | -0.1  | 0.1            |

| 20 000 000                 | 38400               | 520   | 7      | 0      | -0.2  | 0.06             | -0.2  | 0.2            |

| 20 000 000                 | 57600               | 347   | 2      | 0      | -0.06 | 0.2              | -0.3  | 0.3            |

| 20 000 000                 | 115200              | 173   | 5      | 0      | -0.4  | 0.3              | -0.8  | 0.5            |

| 20 000 000                 | 230400              | 86    | 7      | 0      | -1.0  | 0.6              | -1.0  | 1.7            |

| 20 000 000                 | 460800              | 43    | 3      | 0      | -1.4  | 1.3              | -3.3  | 1.8            |

Table 1-5. Commonly Used Baud Rates, Settings, and Errors, UCOS16 = 1

| BRCLK<br>Frequency<br>(Hz) | Baud Rate<br>(baud) | UCBRx | UCBRSx | UCBRFx |      | TX Error<br>%) |       | RX Error<br>%) |

|----------------------------|---------------------|-------|--------|--------|------|----------------|-------|----------------|

| 1 000 000                  | 9600                | 6     | 0      | 8      | -1.8 | 0              | -2.2  | 0.4            |

| 1 000 000                  | 19200               | 3     | 0      | 4      | -1.8 | 0              | -2.6  | 0.9            |

| 1 048 576                  | 9600                | 6     | 0      | 13     | -2.3 | 0              | -2.2  | 0.8            |

| 1 048 576                  | 19200               | 3     | 1      | 6      | -4.6 | 3.2            | -5.0  | 4.7            |

| 4 000 000                  | 9600                | 26    | 0      | 1      | 0    | 0.9            | 0     | 1.1            |

| 4 000 000                  | 19200               | 13    | 0      | 0      | -1.8 | 0              | -1.9  | 0.2            |

| 4 000 000                  | 38400               | 6     | 0      | 8      | -1.8 | 0              | -2.2  | 0.4            |

| 4 000 000                  | 57600               | 4     | 5      | 3      | -3.5 | 3.2            | -1.8  | 6.4            |

| 4 000 000                  | 115200              | 2     | 3      | 2      | -2.1 | 4.8            | -2.5  | 7.3            |

| 4 194 304                  | 9600                | 27    | 0      | 5      | 0    | 0.2            | 0     | 0.5            |

| 4 194 304                  | 19200               | 13    | 0      | 10     | -2.3 | 0              | -2.4  | 0.1            |

| 4 194 304                  | 57600               | 4     | 4      | 7      | -2.5 | 2.5            | -1.3  | 5.1            |

| 4 194 304                  | 115200              | 2     | 6      | 3      | -3.9 | 2.0            | -1.9  | 6.7            |

| 8 000 000                  | 9600                | 52    | 0      | 1      | -0.4 | 0              | -0.4  | 0.1            |

| 8 000 000                  | 19200               | 26    | 0      | 1      | 0    | 0.9            | 0     | 1.1            |

| 8 000 000                  | 38400               | 13    | 0      | 0      | -1.8 | 0              | -1.9  | 0.2            |

| 8 000 000                  | 57600               | 8     | 0      | 11     | 0    | 0.88           | 0     | 1.6            |

| 8 000 000                  | 115200              | 4     | 5      | 3      | -3.5 | 3.2            | -1.8  | 6.4            |

| 8 000 000                  | 230400              | 2     | 3      | 2      | -2.1 | 4.8            | -2.5  | 7.3            |

| 8 388 608                  | 9600                | 54    | 0      | 10     | 0    | 0.2            | -0.05 | 0.3            |

| 8 388 608                  | 19200               | 27    | 0      | 5      | 0    | 0.2            | 0     | 0.5            |

| 8 388 608                  | 57600               | 9     | 0      | 2      | 0    | 2.8            | -0.2  | 3.0            |

| 8 388 608                  | 115200              | 4     | 4      | 7      | -2.5 | 2.5            | -1.3  | 5.1            |

| 12 000 000                 | 9600                | 78    | 0      | 2      | 0    | 0              | -0.05 | 0.05           |

| 12 000 000                 | 19200               | 39    | 0      | 1      | 0    | 0              | 0     | 0.2            |

| 12 000 000                 | 38400               | 19    | 0      | 8      | -1.8 | 0              | -1.8  | 0.1            |

| 12 000 000                 | 57600               | 13    | 0      | 0      | -1.8 | 0              | -1.9  | 0.2            |

| 12 000 000                 | 115200              | 6     | 0      | 8      | -1.8 | 0              | -2.2  | 0.4            |

| 12 000 000                 | 230400              | 3     | 0      | 4      | -1.8 | 0              | -2.6  | 0.9            |

| 16 000 000                 | 9600                | 104   | 0      | 3      | 0    | 0.2            | 0     | 0.3            |

| 16 000 000                 | 19200               | 52    | 0      | 1      | -0.4 | 0              | -0.4  | 0.1            |

| 16 000 000                 | 38400               | 26    | 0      | 1      | 0    | 0.9            | 0     | 1.1            |

| 16 000 000                 | 57600               | 17    | 0      | 6      | 0    | 0.9            | -0.1  | 1.0            |

| 16 000 000                 | 115200              | 8     | 0      | 11     | 0    | 0.9            | 0     | 1.6            |

| 16 000 000                 | 230400              | 4     | 5      | 3      | -3.5 | 3.2            | -1.8  | 6.4            |

| 16 000 000                 | 460800              | 2     | 3      | 2      | -2.1 | 4.8            | -2.5  | 7.3            |

| 16 777 216                 | 9600                | 109   | 0      | 4      | 0    | 0.2            | -0.02 | 0.3            |

| 16 777 216                 | 19200               | 54    | 0      | 10     | 0    | 0.2            | -0.05 | 0.3            |

| 16 777 216                 | 57600               | 18    | 0      | 3      | -1.0 | 0.2            | -1.0  | 0.3            |

| 16 777 216                 | 115200              | 9     | 0      | 2      | 0    | 2.8            | -0.2  | 3.0            |

| 20 000 000                 | 9600                | 130   | 0      | 3      | -0.2 | 0              | -0.2  | 0.04           |

| 20 000 000                 | 19200               | 65    | 0      | 2      | 0.2  | 0.4            | -0.03 | 0.4            |

| 20 000 000                 | 38400               | 32    | 0      | 9      | 0    | 0.4            | 0     | 0.4            |

| 20 000 000                 | 57600               | 21    | 0      | 11     | -0.7 | 0.4            | -0.7  | 0.3            |

| 20 000 000                 | 115200              | 10    | 0      | 14     | 0    | 2.5            | -0.7  | 2.6            |

| 20 000 000                 | 230400              | 5     | 0      | 7      | 0    | 2.5            | 0     | 3.5            |

Table 1-5. Commonly Used Baud Rates, Settings, and Errors, UCOS16 = 1 (continued)

| BRCLK<br>Frequency<br>(Hz) | Baud Rate<br>(baud) | UCBRx | UCBRSx | UCBRFx | Maximum<br>(% | TX Error<br>6) |      | RX Error<br>6) |

|----------------------------|---------------------|-------|--------|--------|---------------|----------------|------|----------------|

| 20 000 000                 | 460800              | 2     | 6      | 10     | -3.2          | 1.8            | -2.8 | 4.6            |

### 1.3.14 Using the USCI Module in UART Mode With Low-Power Modes

The USCI module provides automatic clock activation for use with low-power modes. When the USCI clock source is inactive because the device is in a low-power mode, the USCI module automatically activates it when needed, regardless of the control-bit settings for the clock source. The clock remains active until the USCI module returns to its idle condition. After the USCI module returns to the idle condition, control of the clock source reverts to the settings of its control bits.

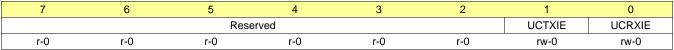

### 1.3.15 USCI Interrupts in UART Mode

The USCI has only one interrupt vector that is shared for transmission and for reception. USCI\_Ax and USC\_Bx do not share the same interrupt vector.

# 1.3.15.1 UART Transmit Interrupt Operation

The UCTXIFG interrupt flag is set by the transmitter to indicate that UCAxTXBUF is ready to accept another character. An interrupt request is generated if UCTXIE and GIE are also set. UCTXIFG is automatically reset if a character is written to UCAxTXBUF.

UCTXIFG is set after a PUC or when UCSWRST = 1. UCTXIE is reset after a PUC or when UCSWRST = 1.

#### 1.3.15.2 UART Receive Interrupt Operation

The UCRXIFG interrupt flag is set each time a character is received and loaded into UCAxRXBUF. An interrupt request is generated if UCRXIE and GIE are also set. UCRXIFG and UCRXIE are reset by a system reset PUC signal or when UCSWRST = 1. UCRXIFG is automatically reset when UCAxRXBUF is read.

Additional interrupt control features include:

- When UCAxRXEIE = 0, erroneous characters do not set UCRXIFG.

- When UCDORM = 1, nonaddress characters do not set UCRXIFG in multiprocessor modes. In plain UART mode, no characters are set UCRXIFG.

- When UCBRKIE = 1, a break condition sets the UCBRK bit and the UCRXIFG flag.

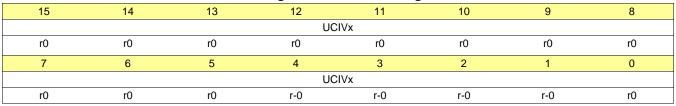

#### 1.3.15.3 UCAxIV, Interrupt Vector Generator

The USCI interrupt flags are prioritized and combined to source a single interrupt vector. The interrupt vector register UCAxIV is used to determine which flag requested an interrupt. The highest-priority enabled interrupt generates a number in the UCAxIV register that can be evaluated or added to the program counter to automatically enter the appropriate software routine. Disabled interrupts do not affect the UCAxIV value.

Any access, read or write, of the UCAxIV register automatically resets the highest-pending interrupt flag. If another interrupt flag is set, another interrupt is immediately generated after servicing the initial interrupt.

### 1.3.15.3.1 UCAxIV Software Example

The following software example shows the recommended use of UCAxIV. The UCAxIV value is added to the PC to automatically jump to the appropriate routine. The following example is given for USCI\_A0.

```

USCI_UART_ISR

ADD

&UCAOIV, PC ; Add offset to jump table

RETI

; Vector 0: No interrupt

JMP

RXIFG_ISR

; Vector 2: RXIFG

TXIFG ISR

; Vector 4: TXIFG

; Task starts here

RETI

; Return

RXIFG_ISR

; Vector 2

; Task starts here

. . .

RETI

; Return

```

### 1.3.16 DMA Operation

In devices with a DMA controller, the eUSCI module can trigger DMA transfers when the transmit buffer UCAxTXBUF is empty or when data was received in the UCAxRXBUF buffer. The DMA trigger signals correspond to the UCTXIFG transmit interrupt flag and the UCRXIFG receive interrupt flag, respectively. The interrupt functionality must be disabled for the selected DMA triggers with UCTXIE = 0 and UCRXIE = 0.

A DMA read access to UCAxRXBUF has the same effects as a CPU (software) read: all error flags (UCRXERR, UCFE, UCPE, UCOE, and UCBRK) are cleared after the read. Thus these errors might go unnoticed.

# 1.4 USCI\_A UART Mode Registers

The USCI registers applicable in UART mode listed in Table 1-6. The base address can be found in the device-specific data sheet. The address offsets are listed in Table 1-6.

Table 1-6. USCI\_A UART Mode Registers

| Offset | Acronym    | Register Name                  | Туре       | Access | Reset | Section        |

|--------|------------|--------------------------------|------------|--------|-------|----------------|

| 00h    | UCAxCTLW0  | USCI_Ax Control Word 0         | Read/write | Word   | 0001h |                |

| 00h    | UCAxCTL1   | USCI_Ax Control 1              | Read/write | Byte   | 01h   | Section 1.4.2  |

| 01h    | UCAxCTL0   | USCI_Ax Control 0              | Read/write | Byte   | 00h   | Section 1.4.1  |

| 06h    | UCAxBRW    | USCI_Ax Baud Rate Control Word | Read/write | Word   | 0000h |                |

| 06h    | UCAxBR0    | USCI_Ax Baud Rate Control 0    | Read/write | Byte   | 00h   | Section 1.4.3  |

| 07h    | UCAxBR1    | USCI_Ax Baud Rate Control 1    | Read/write | Byte   | 00h   | Section 1.4.4  |

| 08h    | UCAxMCTL   | USCI_Ax Modulation Control     | Read/write | Byte   | 00h   | Section 1.4.5  |

| 09h    |            | Reserved - reads zero          | Read       | Byte   | 00h   |                |

| 0Ah    | UCAxSTAT   | USCI_Ax Status                 | Read/write | Byte   | 00h   | Section 1.4.6  |

| 0Bh    |            | Reserved - reads zero          | Read       | Byte   | 00h   |                |

| 0Ch    | UCAxRXBUF  | USCI_Ax Receive Buffer         | Read/write | Byte   | 00h   | Section 1.4.7  |

| 0Dh    |            | Reserved - reads zero          | Read       | Byte   | 00h   |                |

| 0Eh    | UCAxTXBUF  | USCI_Ax Transmit Buffer        | Read/write | Byte   | 00h   | Section 1.4.8  |

| 0Fh    |            | Reserved - reads zero          | Read       | Byte   | 00h   |                |

| 10h    | UCAxABCTL  | USCI_Ax Auto Baud Rate Control | Read/write | Byte   | 00h   | Section 1.4.11 |

| 11h    |            | Reserved - reads zero          | Read       | Byte   | 00h   |                |

| 12h    | UCAxIRCTL  | USCI_Ax IrDA Control           | Read/write | Word   | 0000h |                |

| 12h    | UCAxIRTCTL | USCI_Ax IrDA Transmit Control  | Read/write | Byte   | 00h   | Section 1.4.9  |

| 13h    | UCAxIRRCTL | USCI_Ax IrDA Receive Control   | Read/write | Byte   | 00h   | Section 1.4.10 |

| 1Ch    | UCAxICTL   | USCI_Ax Interrupt Control      | Read/write | Word   | 0000h |                |

| 1Ch    | UCAxIE     | USCI_Ax Interrupt Enable       | Read/write | Byte   | 00h   | Section 1.4.12 |

| 1Dh    | UCAxIFG    | USCI_Ax Interrupt Flag         | Read/write | Byte   | 00h   | Section 1.4.13 |

| 1Eh    | UCAxIV     | USCI_Ax Interrupt Vector       | Read       | Word   | 0000h | Section 1.4.14 |

# 1.4.1 UCAxCTL0 Register

USCI\_Ax Control Register 0

# Figure 1-12. UCAxCTL0 Register

| 7     | 6     | 5     | 4      | 3     | 2    | 1    | 0      |

|-------|-------|-------|--------|-------|------|------|--------|

| UCPEN | UCPAR | UCMSB | UC7BIT | UCSPB | UCM  | ODEx | UCSYNC |

| rw-0  | rw-0  | rw-0  | rw-0   | rw-0  | rw-0 | rw-0 | rw-0   |

Can be modified only when UCSWRST = 1.

# Table 1-7. UCAxCTL0 Register Description

| Bit | Field   | Туре | Reset | Description                                                                                                                                                               |

|-----|---------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | UCPEN   | RW   | 0h    | Parity enable                                                                                                                                                             |

|     |         |      |       | 0b = Parity disabled                                                                                                                                                      |

|     |         |      |       | 1b = Parity enabled. Parity bit is generated (UCAxTXD) and expected (UCAxRXD). In address-bit multiprocessor mode, the address bit is included in the parity calculation. |

| 6   | UCPAR   | RW   | 0h    | Parity select. UCPAR is not used when parity is disabled.                                                                                                                 |

|     |         |      |       | 0b = Odd parity                                                                                                                                                           |

|     |         |      |       | 1b = Even parity                                                                                                                                                          |

| 5   | UCMSB   | RW   | 0h    | MSB first select. Controls the direction of the receive and transmit shift register.                                                                                      |

|     |         |      |       | 0b = LSB first                                                                                                                                                            |

|     |         |      |       | 1b = MSB first                                                                                                                                                            |

| 4   | UC7BIT  | RW   | 0h    | Character length. Selects 7-bit or 8-bit character length.                                                                                                                |

|     |         |      |       | 0b = 8-bit data                                                                                                                                                           |

|     |         |      |       | 1b = 7-bit data                                                                                                                                                           |

| 3   | UCSPB   | RW   | 0h    | Stop bit select. Number of stop bits.                                                                                                                                     |

|     |         |      |       | 0b = One stop bit                                                                                                                                                         |

|     |         |      |       | 1b = Two stop bits                                                                                                                                                        |

| 2-1 | UCMODEx | RW   | 0h    | USCI mode. The UCMODEx bits select the asynchronous mode when UCSYNC = 0.                                                                                                 |

|     |         |      |       | 00b = UART mode                                                                                                                                                           |

|     |         |      |       | 01b = Idle-line multiprocessor mode                                                                                                                                       |

|     |         |      |       | 10b = Address-bit multiprocessor mode                                                                                                                                     |

|     |         |      |       | 11b = UART mode with automatic baud-rate detection                                                                                                                        |

| 0   | UCSYNC  | RW   | 0h    | Synchronous mode enable                                                                                                                                                   |

|     |         |      |       | 0b = Asynchronous mode                                                                                                                                                    |

|     |         |      |       | 1b = Synchronous mode                                                                                                                                                     |

# 1.4.2 UCAxCTL1 Register

USCI\_Ax Control Register 1

# Figure 1-13. UCAxCTL1 Register

| 7       | 6              | 5       | 4         | 3      | 2        | 1       | 0       |  |

|---------|----------------|---------|-----------|--------|----------|---------|---------|--|

| UCSSELx |                | UCRXEIE | UCBRKIE   | UCDORM | UCTXADDR | UCTXBRK | UCSWRST |  |

| rw-0    | rw-0 rw-0 rw-0 |         | rw-0 rw-0 |        | rw-0     | rw-0    | rw-1    |  |

Can be modified only when UCSWRST = 1.

# Table 1-8. UCAxCTL1 Register Description

| Bit | Field    | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                    |

|-----|----------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-6 | UCSSELx  | RW   | 0h    | USCI clock source select. These bits select the BRCLK source clock.  00b = UCAxCLK (external USCI clock)  01b = ACLK  10b = SMCLK  11b = SMCLK                                                                                                                                                                                                                                 |

| 5   | UCRXEIE  | RW   | Oh    | Receive erroneous-character interrupt enable  0b = Erroneous characters rejected and UCRXIFG is not set.  1b = Erroneous characters received set UCRXIFG.                                                                                                                                                                                                                      |

| 4   | UCBRKIE  | RW   | Oh    | Receive break character interrupt enable  0b = Received break characters do not set UCRXIFG.  1b = Received break characters set UCRXIFG.                                                                                                                                                                                                                                      |

| 3   | UCDORM   | RW   | 0h    | Dormant. Puts USCI into sleep mode.  0b = Not dormant. All received characters set UCRXIFG.  1b = Dormant. Only characters that are preceded by an idle-line or with address bit set UCRXIFG. In UART mode with automatic baud-rate detection, only the combination of a break and synch field sets UCRXIFG.                                                                   |

| 2   | UCTXADDR | RW   | Oh    | Transmit address. Next frame to be transmitted is marked as address, depending on the selected multiprocessor mode.  0b = Next frame transmitted is data.  1b = Next frame transmitted is an address.                                                                                                                                                                          |

| 1   | UCTXBRK  | RW   | 0h    | Transmit break. Transmits a break with the next write to the transmit buffer. In UART mode with automatic baud-rate detection, 055h must be written into UCAxTXBUF to generate the required break/synch fields. Otherwise, 0h must be written into the transmit buffer.  0b = Next frame transmitted is not a break.  1b = Next frame transmitted is a break or a break/synch. |

| 0   | UCSWRST  | RW   | 1h    | Software reset enable  0b = Disabled. USCI reset released for operation.  1b = Enabled. USCI logic held in reset state.                                                                                                                                                                                                                                                        |

# 1.4.3 UCAxBR0 Register

USCI\_Ax Baud Rate Control Register 0

#### Figure 1-14. UCAxBR0 Register

| 7     | 6  | 5  | 4  | 3  | 2  | 1  | 0  |  |

|-------|----|----|----|----|----|----|----|--|

| UCBRx |    |    |    |    |    |    |    |  |

| rw    | rw | rw | rw | rw | rw | rw | rw |  |

Can be modified only when UCSWRST = 1.

### Table 1-9. UCAxBR0 Register Description

| Bit | Field | Type | Reset         | Description                                                                                                                                    |

|-----|-------|------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | UCBRx | RW   | undefine<br>d | Low byte of clock prescaler setting of the baud-rate generator. The 16-bit value of (UCAxBR0 + UCAxBR1 x 256) forms the prescaler value UCBRx. |

# 1.4.4 UCAxBR1 Register

USCI\_Ax Baud Rate Control Register 1

### Figure 1-15. UCAxBR1 Register

| 7                 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------------------|---|---|---|---|---|---|---|--|--|

| UCBRx             |   |   |   |   |   |   |   |  |  |

| rw rw rw rw rw rw |   |   |   |   |   |   |   |  |  |

Can be modified only when UCSWRST = 1.

# Table 1-10. UCAxBR1 Register Description

| Bit | Field | Туре | Reset     | Description                                                                                                                                     |

|-----|-------|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | UCBRx | RW   | undefined | High byte of clock prescaler setting of the baud-rate generator. The 16-bit value of (UCAxBR0 + UCAxBR1 × 256) forms the prescaler value UCBRx. |

# 1.4.5 UCAxMCTL Register

USCI\_Ax Modulation Control Register

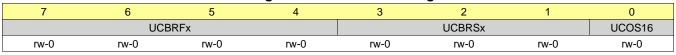

#### Figure 1-16. UCAxMCTL Register

Can be modified only when UCSWRST = 1.

### Table 1-11. UCAxMCTL Register Description

| Bit | Field  | Туре | Reset | Description                                                                                                                                                               |

|-----|--------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4 | UCBRFx | RW   | 0h    | First modulation stage select. These bits determine the modulation pattern for BITCLK16 when UCOS16 = 1. Ignored with UCOS16 = 0. Table 1-2 shows the modulation pattern. |

| 3-1 | UCBRSx | RW   | 0h    | Second modulation stage select. These bits determine the modulation pattern for BITCLK. Table 1-2 shows the modulation pattern.                                           |

| 0   | UCOS16 | RW   | Oh    | Oversampling mode enabled 0b = Disabled 1b = Enabled                                                                                                                      |

# 1.4.6 UCAxSTAT Register

USCI\_Ax Status Register

# Figure 1-17. UCAxSTAT Register

| 7        | 6    | 5    | 4    | 3     | 2       | 1                 | 0      |

|----------|------|------|------|-------|---------|-------------------|--------|

| UCLISTEN | UCFE | UCOE | UCPE | UCBRK | UCRXERR | UCADDR/<br>UCIDLE | UCBUSY |

| rw-0     | rw-0 | rw-0 | rw-0 | rw-0  | rw-0    | rw-0              | r-0    |

Can be modified only when UCSWRST = 1.

# **Table 1-12. UCAxSTAT Register Description**

| Bit | Field         | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-----|---------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | UCLISTEN      | RW   | 0h    | Listen enable. The UCLISTEN bit selects loopback mode.  0b = Disabled  1b = Enabled. UCAxTXD is internally fed back to the receiver.                                                                                                                                                                                                          |  |  |  |

| 6   | UCFE          | RW   | Oh    | Framing error flag. UCFE is cleared when UCAxRXBUF is read.  0b = No error  1b = Character received with low stop bit                                                                                                                                                                                                                         |  |  |  |

| 5   | UCOE          | RW   | Oh    | Overrun error flag. This bit is set when a character is transferred into UCAxRXBUF before the previous character was read. UCOE is cleared automatically when UCxRXBUF is read, and must not be cleared by software. Otherwise, it does not function correctly.  Ob = No error  1b = Overrun error occurred                                   |  |  |  |

| 4   | UCPE          | RW   | 0h    | Parity error flag. When UCPEN = 0, UCPE is read as 0. UCPE is cleared when UCAxRXBUF is read.  0b = No error  1b = Character received with parity error                                                                                                                                                                                       |  |  |  |

| 3   | UCBRK         | RW   | Oh    | Break detect flag. UCBRK is cleared when UCAxRXBUF is read.  0b = No break condition  1b = Break condition occurred                                                                                                                                                                                                                           |  |  |  |

| 2   | UCRXERR       | RW   | 0h    | Receive error flag. This bit indicates a character was received with error(s).  When UCRXERR = 1, on or more error flags, UCFE, UCPE, or UCOE is also set. UCRXERR is cleared when UCAxRXBUF is read.  0b = No receive errors detected  1b = Receive error detected                                                                           |  |  |  |

| 1   | UCADDR/UCIDLE | RW   | 0h    | UCADDR: Address received in address-bit multiprocessor mode. UCADDR is cleared when UCAxRXBUF is read.  0b = Received character is data.  1b = Received character is an address.  UCIDLE: Idle line detected in idle-line multiprocessor mode. UCIDLE is cleared when UCAxRXBUF is read.  0b = No idle line detected  1b = Idle line detected |  |  |  |

| 0   | UCBUSY        | R    | 0h    | USCI busy. This bit indicates if a transmit or receive operation is in progress.  0b = USCI inactive  1b = USCI transmitting or receiving                                                                                                                                                                                                     |  |  |  |

# 1.4.7 UCAxRXBUF Register

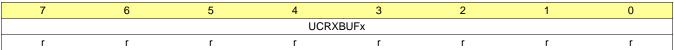

USCI\_Ax Receive Buffer Register

# Figure 1-18. UCAxRXBUF Register

# Table 1-13. UCAxRXBUF Register Description

| Bit | Field    | Туре | Reset     | Description                                                                                                                                                                                                                                                                              |

|-----|----------|------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | UCRXBUFx | R    | undefined | The receive-data buffer is user accessible and contains the last received character from the receive shift register. Reading UCAxRXBUF resets the receive-error bits, the UCADDR or UCIDLE bit, and UCRXIFG. In 7-bit data mode, UCAxRXBUF is LSB justified and the MSB is always reset. |

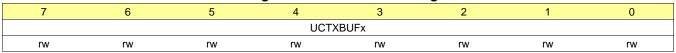

# 1.4.8 UCAxTXBUF Register

USCI\_Ax Transmit Buffer Register

# Figure 1-19. UCAxTXBUF Register

# Table 1-14. UCAxTXBUF Register Description

| Bit | Field    | Туре | Reset     | Description                                                                                                                                                                                                                                                       |

|-----|----------|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | UCTXBUFx | RW   | undefined | The transmit data buffer is user accessible and holds the data waiting to be moved into the transmit shift register and transmitted on UCAxTXD. Writing to the transmit data buffer clears UCTXIFG. The MSB of UCAxTXBUF is not used for 7-bit data and is reset. |

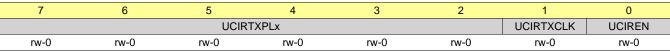

# 1.4.9 UCAxIRTCTL Register

USCI\_Ax IrDA Transmit Control Register

# Figure 1-20. UCAxIRTCTL Register

Can be modified only when UCSWRST = 1.

# Table 1-15. UCAxIRTCTL Register Description

| Bit | Field     | Туре | Reset | Description                                                                                                    |

|-----|-----------|------|-------|----------------------------------------------------------------------------------------------------------------|

| 7-2 | UCIRTXPLx | RW   | 0h    | Transmit pulse length. Pulse length $t_{PULSE} = (UCIRTXPLx + 1) / (2 \times f_{IRTXCLK})$                     |

| 1   | UCIRTXCLK | RW   | 0h    | IrDA transmit pulse clock select 0b = BRCLK 1b = BITCLK16 when UCOS16 = 1. Otherwise, BRCLK.                   |

| 0   | UCIREN    | RW   | Oh    | IrDA encoder and decoder enable  0b = IrDA encoder and decoder disabled  1b = IrDA encoder and decoder enabled |

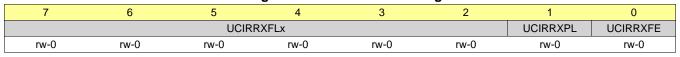

# 1.4.10 UCAxIRRCTL Register

USCI\_Ax IrDA Receive Control Register

### Figure 1-21. UCAxIRRCTL Register

Can be modified only when UCSWRST = 1.

# Table 1-16. UCAxIRRCTL Register Description

| Bit | Field     | Туре | Reset | Description                                                              |

|-----|-----------|------|-------|--------------------------------------------------------------------------|

| 7-2 | UCIRRXFLx | RW   | 0h    | Receive filter length. The minimum pulse length for receive is given by: |

|     |           |      |       | $t_{MIN} = (UCIRRXFLx + 4) / (2 \times f_{BRCLK})$                       |

| 1   | UCIRRXPL  | RW   | 0h    | IrDA receive input UCAxRXD polarity                                      |

|     |           |      |       | 0b = IrDA transceiver delivers a high pulse when a light pulse is seen.  |

|     |           |      |       | 1b = IrDA transceiver delivers a low pulse when a light pulse is seen.   |

| 0   | UCIRRXFE  | RW   | 0h    | IrDA receive filter enabled                                              |

|     |           |      |       | 0b = Receive filter disabled                                             |

|     |           |      |       | 1b = Receive filter enabled                                              |

# 1.4.11 UCAxABCTL Register

USCI\_Ax Auto Baud Rate Control Register

# Figure 1-22. UCAxABCTL Register

| 7   | 6     | 5    | 4         | 3 | 2      | 1        | 0       |

|-----|-------|------|-----------|---|--------|----------|---------|

| Res | erved | UCDE | UCDELIMx  |   | UCBTOE | Reserved | UCABDEN |

| r-0 | r-0   | rw-0 | rw-0 rw-0 |   | rw-0   | r-0      | rw-0    |

Can be modified only when UCSWRST = 1.

# Table 1-17. UCAxABCTL Register Description

| Bit | Field    | Туре | Reset | Description                                                                                                                                                                                                                                           |  |

|-----|----------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|