# TUSB211 to TUSB212 Changes

# **ABSTRACT**

This document defines pinout differences between the TUSB211 and the TUSB212 and highlights the schematic changes needed to convert existing system designs from using the TUSB211 to the TUSB212.

This document also applies to the TUSB214 which shares the same pinout and pin functions of the TUSB212.

#### Contents

|   | ***************************************   |   |

|---|-------------------------------------------|---|

| 1 | Pinout Comparison                         | 2 |

| 2 | VCC and GND                               | 2 |

| 3 | USB Data Pins                             | 2 |

| 4 | RSTN, EQ, and VREG Pins                   | 2 |

| 5 | Test and CD Pins                          | 3 |

| 6 | DC_BOOST/ENA_HS                           |   |

| 7 | Reference Schematic                       | 3 |

|   | List of Figures                           |   |

| 1 | Reference Schematic                       | 3 |

|   | Lint of Tables                            |   |

|   | List of Tables                            |   |

| 1 | TUSB211 to TUSB212 Pinout Changes         |   |

| 2 | TUSB212 Equalization Control Pin Settings | 2 |

| 3 | TUSB212 DC_BOOST Control Pin Settings     | 3 |

# **Trademarks**

All trademarks are the property of their respective owners.

Pinout Comparison www.ti.com

# 1 Pinout Comparison

Table 1 lists the changes in the pin definitions of the TUSB211 and TUSB212 devices, and highlights pin configurations that may require change when using the TUSB212 to replace the TUSB211 in an existing system.

Table 1. TUSB211 to TUSB212 Pinout Changes

| Pin | TUSB211 | TUSB212         | TUSB211 to TUSB212 Change Notes                                                                         |

|-----|---------|-----------------|---------------------------------------------------------------------------------------------------------|

| 1   | D1M     | D1M             | No change required                                                                                      |

| 2   | D1P     | D1P             | No change required                                                                                      |

|     |         |                 | GPIO mode: no change required                                                                           |

| 3   | TEST    | SDA             | I <sup>2</sup> C mode: add a 4.7-k pullup to VCC; connect to master SCL.                                |

|     |         |                 | No change required                                                                                      |

| 4   | CD      |                 | I <sup>2</sup> C mode: add a 4.7-k pulup to VCC; connect to master SDA.                                 |

| 5   | RSTN    | RSTN            | No change required                                                                                      |

| 6   | EQ      | EQ              | No change required                                                                                      |

| 7   | D2P     | D2P             | No change required                                                                                      |

| 8   | D2M     | D2M             | No change required                                                                                      |

| 9   | ENA_HS  | DC_BOOST/ENA_HS | 43-k pullup to VCC for high boost<br>Leave floating for mid boost<br>43-k pulldown to GND for low boost |

| 10  | GND     | GND             | No change required                                                                                      |

| 11  | VREG    | VREG            | No change required                                                                                      |

| 12  | VCC     | VCC             | No change required                                                                                      |

# 2 VCC and GND

No changes are required for VCC and GND pins.

# 3 USB Data Pins

No changes are required for D1P, D1M, D2P, or D2M pins.

# 4 RSTN, EQ, and VREG Pins

No changes are required for RSTN, EQ, or VREG pins.

**Table 2. TUSB212 Equalization Control Pin Settings**

| Pin | Description | AC Boost Level | Typical Pulldown Resistor<br>Value |

|-----|-------------|----------------|------------------------------------|

|     |             | 0              | 100 Ω                              |

| EQ  | AC Boost    | 1              | 1.7 kΩ                             |

| EQ  | AC BOOSI    | 2              | 3.8 kΩ                             |

|     |             | 3              | 10 kΩ                              |

www.ti.com Test and CD Pins

# 5 Test and CD Pins

The Test and CD pins have changed from the TUSB211 to the TUSB212, these pins are dual-function pins in the TUSB212 for the I²C interface. If the TUSB212 is not configured to use I²C, then there are no changes needed for these pins. If the TUSB212 is configured to use I²C, the Test pin acts as the I2C SDA pin and CD acts as the I2C SCL pin. Both SDA and SCL should have a 4.7-k $\Omega$  pullup to VCC.

#### 6 DC BOOST/ENA HS

The DC\_BOOST pin was added to the TUSB212, this pin is muxed with the ENA\_HS pin. The state of the DC\_BOOST pin is sampled after Power-On Reset or de-assertion of the RSTN pin and selects the amount of DC Boost added to the differential signal. After the DC\_BOOST input is sampled, the pin function changes to being the ENA\_HS output signal.

|  | Pin               | Description | Logic State | Boost Setting      |

|--|-------------------|-------------|-------------|--------------------|

|  | DC_BOOST/ENA_HS [ |             | Low         | Low boost (40 mV)  |

|  |                   | DC Boost    | Floating    | Mid boost (60 mV)  |

|  |                   |             | High        | High boost (80 mV) |

Table 3. TUSB212 DC\_BOOST Control Pin Settings

#### 7 Reference Schematic

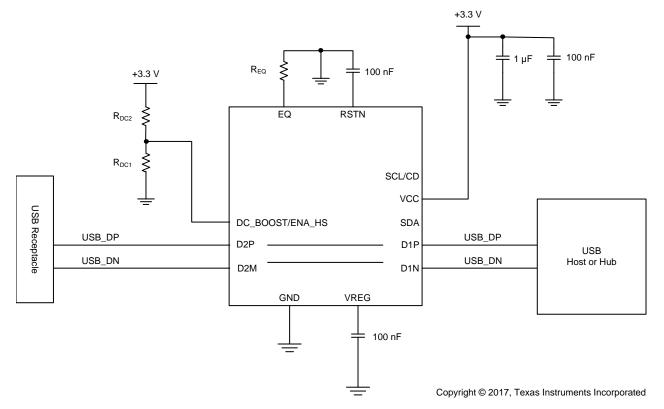

Figure 1 can be referenced for a dual design using the TUSB211 or TUSB212. Resistor REQ selects the AC Boost configuration, resistors RDC1 and RDC2 select the DC\_BOOST configuration (can be left unpopulated for TUSB211). Please refer to the appropriate data sheet for complete pin configuration information.

Figure 1. Reference Schematic

Revision History www.ti.com

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Date           | Revision | Description     |

|----------------|----------|-----------------|

| September 2017 | *        | Initial release |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ("TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated