# 2004/05 POWER SUPPLY DESIGN SEMINAR

## TABLE of CONTENTS

| TOPIC 1                                                                       |

|-------------------------------------------------------------------------------|

| Safety Considerations in Power Supply Design1-1                               |

| TOPIC 2                                                                       |

| Sequencing Power Supplies in Multiple Voltage Rail Environments2-1            |

| TOPIC 3                                                                       |

| Design Review: A Step-by-Step Approach to AC Line-Powered Converters3-1       |

| TOPIC 4                                                                       |

| Constructing Your Power Supply – Layout Considerations                        |

| TOPIC 5                                                                       |

| Interleaving Contributes Unique Benefits to Forward and Flyback Converters5-1 |

| TOPIC 6                                                                       |

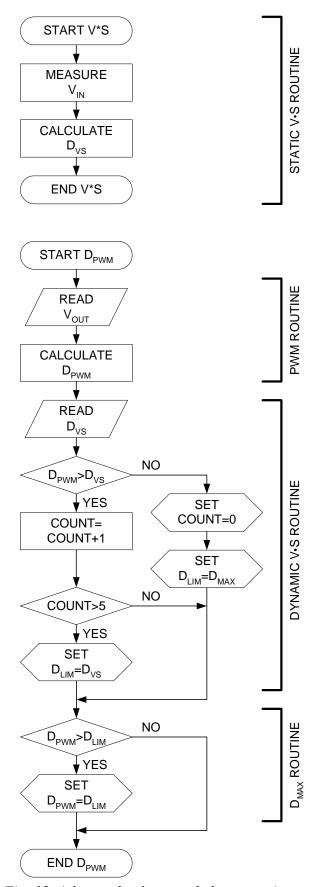

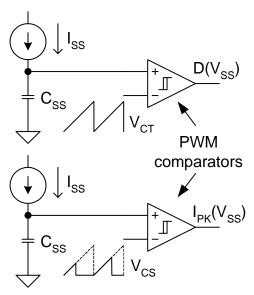

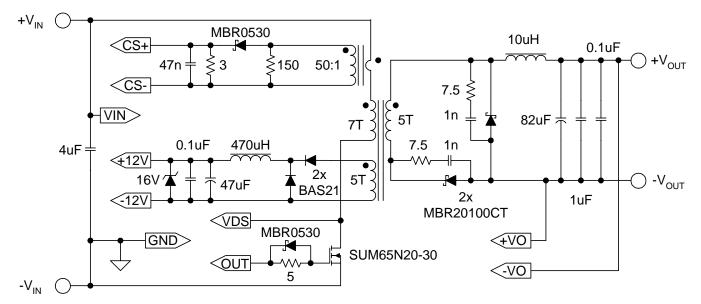

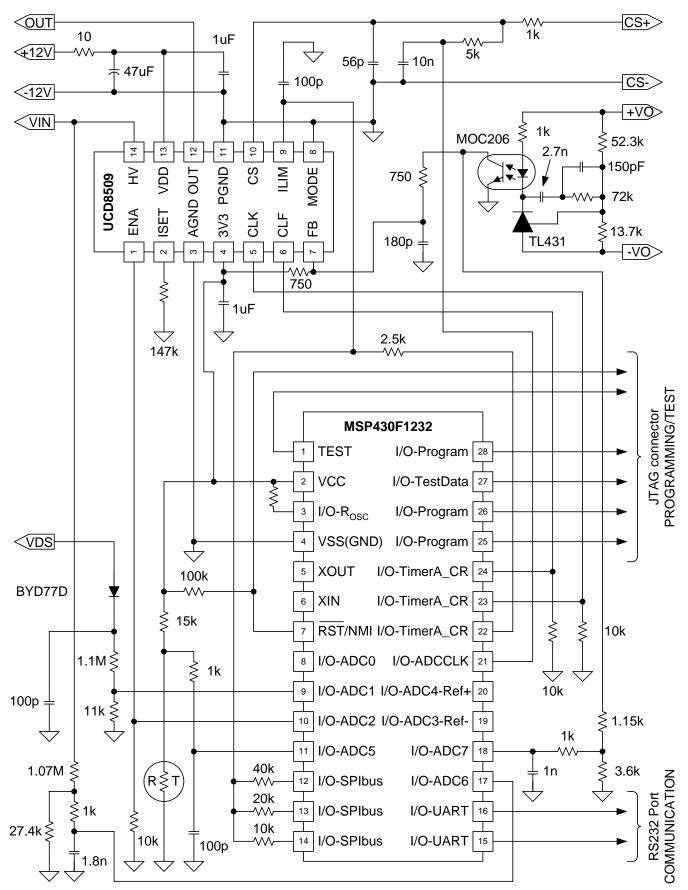

| A Practical Introduction to Digital Power Supply Control                      |

| TOPIC 7                                                                       |

| Compensating DC/DC Converters with Ceramic Output Capacitors                  |

To view or download past seminar topics referenced in this manual, please go to: **power.ti.com** *click:* **Support/Training/Seminar Materials**

All trademarks are the property of their respective owners.® 2004 Texas Instruments Incorporated

### **Topic 1**

**Safety Considerations in Power Supply Design**

### Safety Considerations in Power Supply Design

Bob Mammano, Texas Instruments Lal Bahra, Underwriters Laboratories

#### **ABSTRACT**

Increasingly, the responsibilities of a power supply designer extend beyond merely meeting a functional specification, with designing to meet safety standards an important collateral task. Since all commercial and home-use supplies must eventually be certified as to safety, knowledge of the requirements should be a part of every designer's repertoire. This simplified overview has been prepared with the collaboration of Underwriters Laboratories, Inc. to provide a basic introduction to the issues and design solutions implicit in assuring the safety for both the user and service personnel of your power supply products, as well as easing the certification process.

#### I. Introduction

It should come as no surprise that safety is an important issue in the design of any electrical equipment which is liable to come into contact with a human operator or servicing individual. And this issue should be even more obvious when the equipment is designed to operate from a source of power which could experience or deliver voltage levels that could be hazardous to the human body. Recognizing this, a large collection of design standards and certification processes have been developed to define the requirements for insuring the safety of power A thorough treatment information takes much more space and time than available within the context of this seminar program – it is a subject more commonly taught with the dedication of one to two full days of presentation – however it is hoped that the brief overview provided herein will be useful in describing the basics both for designers who may have in-house resources with more detailed expertise, or who plan to follow up with attendance at a more in-depth program as those presented by Underwriters Laboratories, Inc.

Note that UL60950-1 (including Annexes P and Q) was used as the source for all numbers quoted here but many of the conditions and contingencies have been excluded in the interests of simplicity. Reference to the complete and latest revision of the appropriate standard should be made for any and all design decisions.

#### II. PRINCIPLES OF SAFETY

While one would expect that a safety standard for power supplies would be dominated by consideration of electrical hazards, this is not the only aspect of power supply design affected. A more complete listing of safety issues could include the following:

- **Electric Shock:** This is the shock hazard resulting from the passage of electric current through the human body. The physiological effects can range from perception or a startle involuntary movement, all the way to ventricular fibrillation or, ultimately, death.

- Energy Hazards: Even at voltages too low to produce a shock, burns can be caused when metallic objects such as tools, jewelry, etc. get very hot or melt and splash when they bridge sources with high VA potential (typically 240 VA or more).

- Fire: Fire is normally considered as a secondary effect from overload, abnormal operating conditions, or fault in some system component. However induced, it should not spread to adjacent components or equipment.

- Heat Related Hazards: High temperatures on accessible surfaces or components under normal operating conditions.

- **Mechanical:** Injury or damage resulting from contact with sharp edges or corners, moving parts, or physical instability.

While not usually associated with power supplies, other hazards that might need consideration could include the effects of radiation, chemicals, or hazardous vapors.

There are at least two types of persons whose safety needs must be considered: users (or operators) of the equipment, and service personnel. Users are not expected to identify hazards, and must not be allowed contact with hazardous parts. This is normally accomplished through the use of such means as enclosures or other protective shielding. Service personnel, on the other hand, are assumed to have access to all parts of the system and for their safety, the requirement is to identify the hazardous components or areas and to ensure against inadvertent contact with a hazardous surface, or bridging a tool between parts with high energy levels while working in another part of the equipment.

In addition to the types of personnel coming into contact with the equipment, there is an additional consideration as to the end use for a power supply. Power supplies can typically be divided into two categories:

- whether the supply is to be sold as a standalone item, or

- as a component to be installed into a specific system or equipment.

In either case, however, it is the end use conditions that apply and it is the end use standards that must be considered with respect to safety.

In additional principle of safety is that designers must consider not only normal operating conditions, but also likely faults, foreseeable misuse, external influences and environments, and overvoltages that might occur on input or output lines.

#### III. SAFETY STANDARDS FOR POWER SUPPLIES

Safety standards, like most standards affecting electrical equipment, were originally very specialized and unique to a given country. The driving force for a unified standard was primarily the information technology industry whose efforts led to the first international standard for safety, IEC950, prepared by the International Electrotechnical Commission (IEC). With the release in the late 1980s of UL1950, UL expanded the scope of IEC950 to include electrical business equipment along with ITE, but excluded standard telecommunication equipment. In the meantime, however, a working group of the IEC (TC-74) had generated a harmonized standard, IEC60950 (third edition), to cover products from all three industries and, upon its release in 1999, it was quickly adopted by most countries and is today the primary standard for safety for most, but certainly not all, users of power supplies. In addition to IEC, designations of this standard can be found as EN (European Union), UL (United States), and CSA (Canada). In the USA, the plan is to withdraw approvals to all earlier standards by July, 2006. The US National Standard, as of this writing, is UL60950-1, first edition, published in November, 2003.

While UL60950-1 is the most widely applied standard for power supplies today, it is intended for use with information technology, business, and telecom equipment. Other standards exist for other industries, such as IEC 60065 for audio and video, IEC 60601 for medical, IEC 61010 for laboratory supplies, and others. Further efforts at harmonization are under way with a subcommittee of the IEC (SC22E) proposing a new standard, IEC 61204-7, which is intended for use with power supplies sold into multiple industries. This standard is currently under development.

The point to remember here is that safety standards, like most things high-tech, represent an evolving field. While UL 60950-1 has been used to prepare this subject, one of the first tasks in any new design activity should be to identify the standards, including recent revisions, which applies to the intended end use.

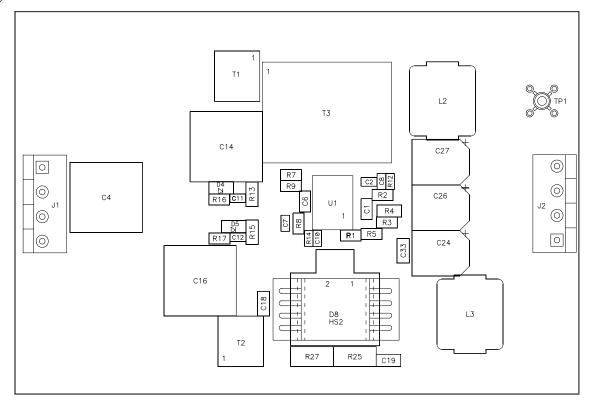

#### IV. ELEMENTS OF A POWER SUPPLY

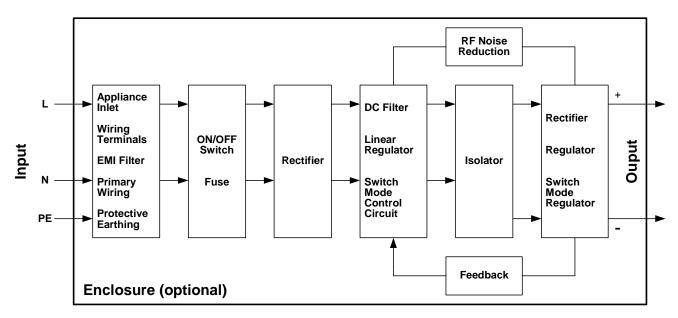

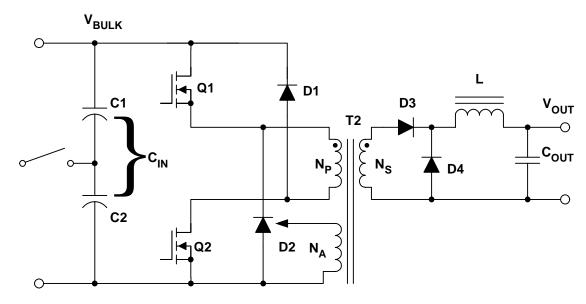

A block diagram for a typical power supply is shown in Fig. 1 where the blocks have been defined in a way to ease the consideration of safety implications. While this figure illustrates an AC-line powered unit which, of course, is clearly an application where hazardous voltage levels could be present or internally generated, a similar blocking of functions could be derived for other designs, i.e., battery chargers or dc-to-dc converters.

The task of certifying a design for safety is made easier by the identification and use of as many components which, in themselves, are already qualified to an appropriate IEC safety standard. Many such power supply components are available, including:

- Power cords and/or input terminal assemblies

- Protective devices (fuses, clamps, etc.)

- EMI filters

- Power switches

- Wiring, PWBs, chassis

- Isolators (optocouplers)

- Transformers

- Rectifier assemblies

- Output connectors or terminals

- Cooling devices

- And many others...

Components which are already certified as conforming to the applicable standards need be evaluated only individually as to their application within their ratings, and then indirectly as a part of the complete power supply or end use application. Non-qualified components may need additional testing to the appropriate standard at the component level. Since this can add a significant amount of time and cost in the qualification process, it is highly advantageous to pick components which have already achieved prior approval.

#### V. CONSIDERATIONS FOR ELECTRICAL SAFETY

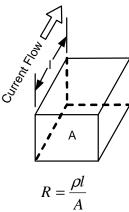

The prevention of electric shock is clearly a major safety goal. The impact on a human body is defined by the flow of current which, in turn, is affected by the body's resistance. The accepted value for the body's resistance is approximately 2000  $\Omega$  at a voltage of 110 Vdc; however this value decreases with increasing voltage. Another factor that affects resistance is the amount of surface area of contact. This has been quantized by defining two classifications of skin contact as:

• Full contact, meaning full contact by hand which has a typical area of about 8000 mm<sup>2</sup>, but is simulated by a metal contact surface of 20 cm by 10 cm.

Fig. 1. The elements of a typical power supply.

• Limited contact is described as contact by finger tip and simulated by a metal contact surface of 10 mm<sup>2</sup>. A standardized "finger probe" is defined to test for contact in tight regions or through enclosure openings.

In any case, it is current that affects the body and the effects have been categorized according to the table of threshold values in Table 1.

TABLE 1. THRESHOLD VALUES

| Current (mA) | Effect                                    |  |

|--------------|-------------------------------------------|--|

| 0.0 to 0.5   | Perception, minimal reaction              |  |

| 0.5 to 3.5   | Startle reaction, but ability to tolerate |  |

| 3.5 to 10    | Muscles contract, inability to let go     |  |

| 10 to 50     | Fibrillation, cell damage                 |  |

The acceptable limit for current is 2.0 mA dc, 0.7 mA pk ac and 0.5 mArms at frequencies up to 60 Hz. High-frequency current is less harmful to the human body and the permitted current is calculated by multiplying the 50/60 Hz threshold by the frequency in kHz, but with a maximum of 70 mA at all frequencies above 100 kHz. However, these limits can still cause burns if one touches a sharp edge or corner, as current density may be high.

Since it is the circuit voltage that drives this current, UL60950-1 categorizes circuits within a power supply as either hazardous or safe according to the maximum voltage or the maximum current possible at all points within the circuit, during both normal operating conditions and under any single fault. Within this criterion, there are three classifications of safe circuits

- Limited Current Circuits (LCC) where the maximum available current cannot exceed 2.0 mA dc, 0.7 mA peak ac, or 0.5 mA rms under both normal and single-fault conditions. There are also limits on allowable capacitance.

- Safety Extra Low Voltage (SELV) circuits where voltage levels cannot exceed 42.4 V pk ac or 60 Vdc, under both normal and single-fault conditions.

Telecommunication Network Voltage (TNV) voltages may exceed SELV limits but are constrained by either accessibility or duration. The normal operating voltage can be up to 71 V peak ac or 120 V dc where the accessible contact area is limited to that of a connector pin. The voltages under a single fault can be higher for a short duration but must return to normal limits within 200 ms. Higher transient levels (up to 1500 V, but of short duration) are possible from the public switching telecom network.

Note that although all three of the above designations are considered as safe, only SELV and LCC circuits allow the operator unrestricted access to bare circuit components.

Classifications for circuits which are considered as unsafe and which must be protected against operator contact include:

- Hazardous Voltage circuits, where voltages above SELV limits can appear on bare components, or which contain components without adequate insulation from a potential high voltage source.

- Extra Low Voltage (ELV) circuits, which defines a circuit that meets SELV voltage limits under normal operating conditions but is not safe with a single fault.

Two other circuit classifications are defined by their location within a power supply's architecture:

- **Primary circuits**, where there is a direct connection to the ac mains voltage and clearly have the potential to reach hazardous voltage levels, and

- **Secondary circuits**, which have no direct connection to the primary circuits but may experience hazardous voltage levels.

#### VI. PROTECTION WITH INSULATION

UL60950-1 defines five categories of insulation.

#### A. Types of Insulation

- **Functional insulation** is that which is only necessary for circuit operation. It is assumed to provide no safety protection.

- Basic insulation provides basic protection against electric shock with a single level; however this category does not have a minimum thickness specification for solid insulation and is assumed to be subject to pinholes. Safety is provided by a second level of protection such as Supplementary insulation or protective earthing.

- **Supplementary insulation** is normally used in conjunction with Basic insulation to provide a second level of protection in the event that the Basic level fails. A single layer of insulating material must have a minimum thickness of 0.4 mm to be considered Supplementary insulation.

- Double insulation is a two-level system, usually consisting of Basic insulation plus Supplementary insulation.

- **Reinforced insulation** is a single-insulation system equivalent to Double insulation. It also requires a minimum thickness of 0.4 mm for use in a single layer.

Electric circuits rely upon insulation for operator protection, but designing for safety requires the premise that anything can fail. Therefore safety standards demand a redundant system with at least two levels of protection under the assumption that any single level may experience a failure but the chance of two simultaneous failures in the same spot is so improbable as to represent an acceptable risk. It should be noted that while two random failures need not be considered, the possibility of a second failure as a consequence of a first failure is something that the designer must evaluate if the two together would result in a total breakdown.

Fig. 2. Safety requires a Double barrier for redundant protection.

The general requirements are that a single level of insulation is acceptable if the circuit is not accessible, but wherever there are accessible components, they must be insulated from hazardous voltages by a Double-level system, and each level must meet the insulation specifications appropriate to the application. One qualification to this statement is that one level of protection could be protective earth provided by a conductive grounded enclosure.

#### B. Class Categories

Categories are used to define different classes of circuits and the type of insulation needed for each, as:

- Class I Equipment: Systems which use protective earthing (e.g., a grounded metal enclosure) as one level of protection and thus require only Basic insulation between the enclosure and any part at hazardous voltage

- Class II Equipment: The use of Double or Reinforced insulation to eliminate the need for a grounded metal enclosure as well as a grounded power plug.

- Class III Equipment: Powered from a SELV source and with no potential for generation of hazardous voltages internally, and therefore requiring only Functional insulation.

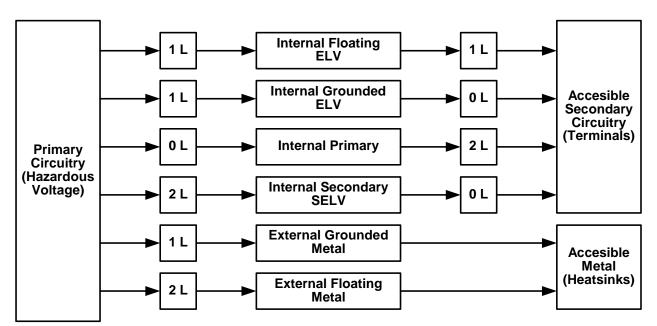

The for defining insulation process requirements starts with identifying each circuit block within the system according to the categories described above: LCC, SELV, TNV, ELV, or Hazardous. Then, with this knowledge, the appropriate insulation type and number of levels can be defined for use between blocks and between internal components and the user. A guide to insulation planning for a simple power supply example is shown in Fig. 3, which illustrates that there must always be two levels of protection between a hazardous voltage (on the left) and components accessible to the user (on the right).

For example, the path through a floating ELV circuit must have two levels, and at least one of those must be between the ELV and the user as an ELV could become unsafe with a single fault. However, if the ELV has grounded protection (providing one level), then only one additional level is needed. Similarly, external metal, (typically heatsinks or the power supply's enclosure), must isolate the user from the hazardous voltage with two levels of protection, unless one level is provided by grounding the metal.

Fig. 3. Insulation coordination for a typical line-powered supply.

#### VII. WORKING VOLTAGE

With the insulation levels defined, specific requirements for the insulating medium must be considered. This medium can be either a solid material (such as plastic molding); or air (as in the space between components), and the requirements for both are affected by the voltage stress across the medium. Typically, a power supply is evaluated to determine the highest voltage levels possible at all points in the circuitry and under all operating conditions. The highest measured voltage between any two points then defines the working voltage for those two points. The working voltage between a primary circuit and a secondary circuit, or between the primary and ground, is taken as the upper limit of the rated voltage range for the supply.

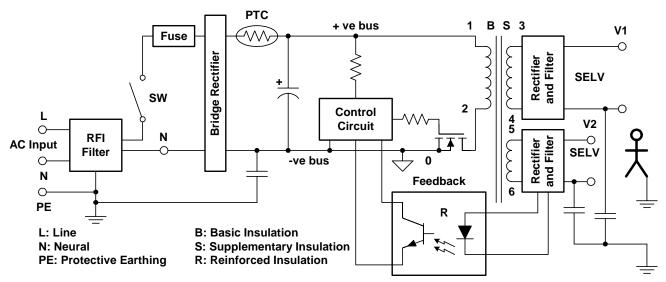

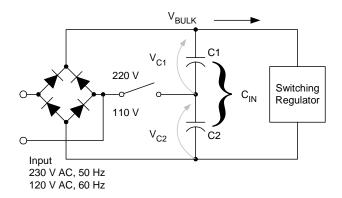

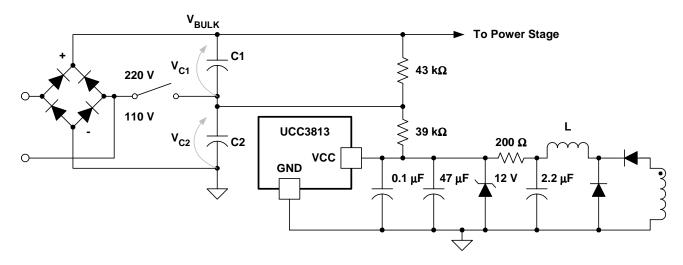

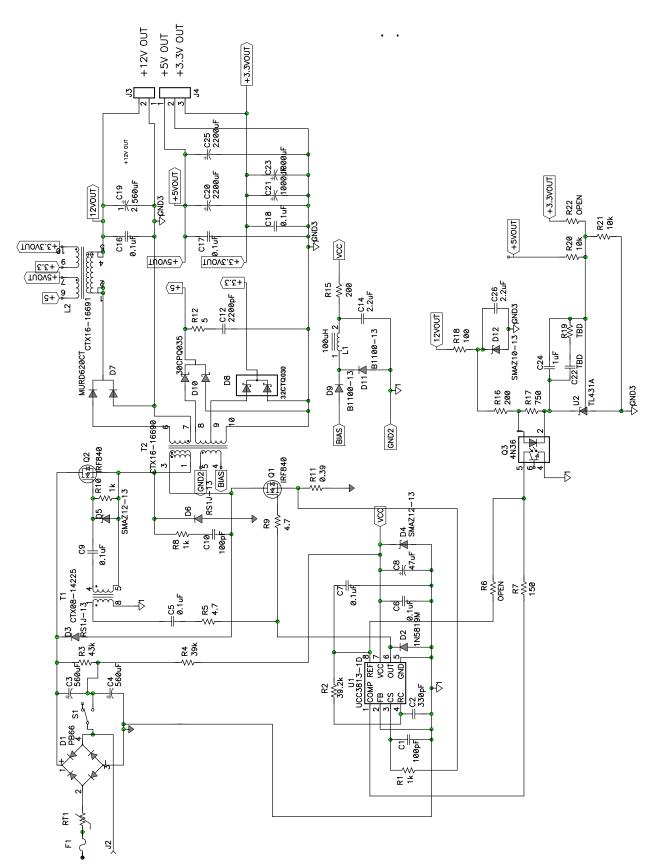

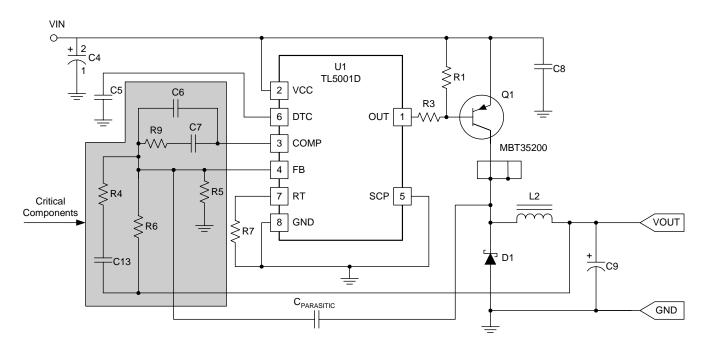

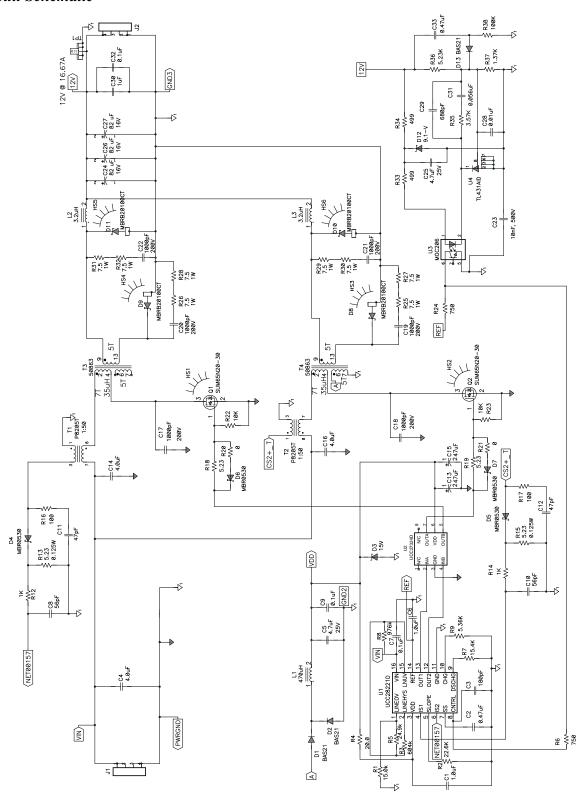

An example is illustrated in Fig. 4 showing the schematic for a simple off-line power supply in which protective isolation is provided in both the transformer and the optocoupler. With all points on the primary referenced to either the line or the neutral power connections, hazardous voltage levels with respect to earth are assumed to be possible at any point on the primary side. The individual working voltages within the primary circuitry are evaluated as the maximum rated or measured voltage (whichever is higher) between any circuit element and either earth or any point on the secondary side of the transformer.

As shown in Fig. 4, the highest working voltages would normally be found on points labeled 0, 1, and 2 on the primary side of the transformer, and these points would then each be measured with respect to both earth and all secondary points labeled 3, 4, 5, and 6 with the condition that when one end of a secondary winding is used as a reference point, then the other end is to be connected to earth. These measurements - dc, rms, or peak - are evaluated to determine the highest value, which then establishes the minimum working voltage requirement for the protective insulation.

Fig. 4. Measurement points to determine the working voltage in the primary circuitry.

#### VIII. INSULATING MATERIALS

#### A. Solid Insulation

The choice and application of solid insulating material must consider, in addition to working voltage, the needs for electrical, thermal, and mechanical strength, as well as the operating environment. Only non-hygroscopic and flame resistant materials may be used. With particular respect to wiring insulation, it should be noted that some material compounds may contain plasticizers, intended to make them more flexible but with a side effect of increased flammability.

Semiconductor devices and other components that are molded in solid insulating material typically are independently qualified and inspected in the manufacturing process.

Solid insulation material in sheet form must also conform to the following thickness requirements:

- If a single sheet of insulation is provided, the minimum thickness is 0.4 mm.

- With two sheets together, there is no thickness requirement but each sheet must meet the required electric strength value.

- With three or more sheets, there is also no minimum thickness but every combination of two sheets must have adequate electric strength.

- There is no thickness requirement for Functional or Basic insulation.

#### B. Air Insulation

The use of air as an insulation medium introduces concerns both about the "quality" of the air and the spacing between electrically conducting components. The potential for conduction through is affected air temperature, pressure, humidity, and pollution, with "pollution" being defined according to the operating environment the following by categories:

- Pollution Degree 1 Components and assemblies which are sealed to exclude dust and moisture.

- Pollution Degree 2 General office or home environment.

- Pollution Degree 3 Equipment where the internal environment is subject to conductive pollution or possible moisture condensation.

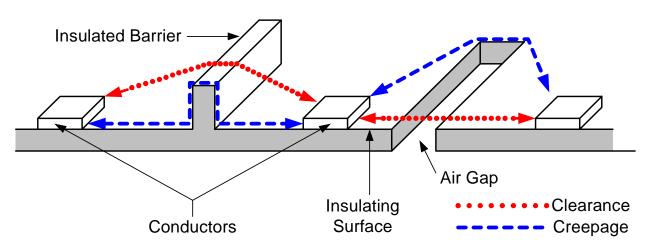

The spacing distance between components that are required to withstand a given working voltage is specified in terms of Clearance and Creepage. A visual representation of the distinction between these terms, and their applicability to board-mounted components, is shown in Fig. 5

Fig. 5. Definitions of Creepage and Clearance.

#### IX. CLEARANCE AND CREEPAGE

In the discussion that follows, the tables presented show quantitative values for spacing requirements, in millimeters, which are listed as a function of the voltage, material, environment. An additional distinction is the category of insulation system of which these are part, i.e., Functional, spacings a Basic/Supplementary, or Reinforced. In other words, if the spacing between components is not needed for safety, the "F" column may be used; if only one level of safety insulation is needed because a second level is provided elsewhere, the "B/S" column is applicable; and for the equivalent of a complete 2-level safety insulation, the "R" column should be used.

#### A. Clearance

Clearance is defined as the shortest distance through air between two conductive parts. Breakdown along a Clearance path is a fast phenomenon where damage can be caused by a very short duration impulse. Therefore, it is the maximum peak voltage, including transients, that is used to determine the required Clearance spacing according to charts given in the standard. A sample of one of these is shown in Table 2 where the spacing in millimeters required for different levels of insulation is given as a function of working voltage. Additional variables of ac mains voltage and the quality of the air within the space are indicated in this illustration but are applied more quantitatively in additional charts given in the complete standard.

#### B. Creepage.

Creepage is defined as the shortest distance between two conductive parts along the surface of any insulating material common to both parts. While the path is in the air, it is heavily influenced by the surface condition of the insulating material. Breakdown of the Creepage distance is a slow phenomenon, determined by dc or rms voltage levels rather than peak events. Inadequate Creepage spacing may last for days, weeks, or months before it fails. A sample of a table of Creepage requirements is given as Table 3 where the spacings are given as a

function of the steady-state working voltage with additional variables of insulation type, material composition, and content of the air.

TABLE 2. PARTIAL CLEARANCE DIMENSIONS (MM) FROM UL60950-1, SECTION 2.10.3, TABLE 2H

| Working V | oltage/ | AC Mains < 150 V<br>(Transient to 1500 V)<br>Pollution levels 1 and 2 |     |     | AC Mains < 300 V<br>(Transient to 2500 V)<br>(Pollution levels 1 and 2 |     |     |

|-----------|---------|-----------------------------------------------------------------------|-----|-----|------------------------------------------------------------------------|-----|-----|

| Peak dc V | rms V   | F                                                                     | B/S | R   | F                                                                      | B/S | R   |

| 71        | 50      | 0.4                                                                   | 1.0 | 2.0 | 1.0                                                                    | 2.0 | 4.0 |

| 210       | 150     | 0.5                                                                   | 1.0 | 2.0 | 1.4                                                                    | 2.0 | 4.0 |

| 420       | 300     | 1.5                                                                   | 2.0 | 4.0 | 1.5                                                                    | 2.0 | 4.0 |

| 840       | 600     | 3.0                                                                   | 3.2 | 6.4 | 3.0                                                                    | 3.2 | 6.4 |

TABLE 3. SAMPLE CREEPAGE DIMENSIONS (MM) FROM UL60950-1, SECTION 2.10.4, TABLE 2L

| Working<br>Voltage |     | Pollution Level 1 Pollution Level 2 Pollution Level 3 Material Group III Material Group III Material Group III |     |     |     |      |     |     |     |

|--------------------|-----|----------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|-----|-----|-----|

| dc or rms          | F   | B/S                                                                                                            | R   | F   | B/S | R    | F   | B/S | R   |

| < 50 V             | 0.4 | 0.7                                                                                                            | 1.4 | 1.2 | 1.2 | 2.4  | 1.9 | 1.9 | 3.8 |

| < 150 V            | 0.6 | 0.9                                                                                                            | 1.8 | 1.6 | 1.6 | 3.2  | 2.5 | 2.5 | 5.0 |

| < 300 V            | 1.6 | 1.9                                                                                                            | 3.8 | 3.2 | 3.2 | 6.4  | 5.0 | 5.0 | 10  |

| < 600 V            | 3.2 | 3.2                                                                                                            | 5.0 | 6.3 | 6.3 | 12.6 | 10  | 10  | 20  |

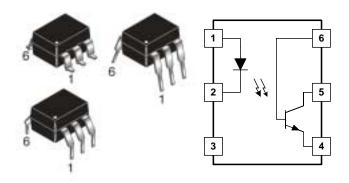

Semiconductor components, particularly optocouplers, do not typically have Clearance or Creepage requirements. Clearance and Creepage distances do not exist if the component is completely filled with an insulating compound or molded in solid insulating material, and the component is independently qualified inspected in the manufacturing Creepage, however, can become important with respect to the boards upon which these devices are mounted. This often dictates a requirement for spreading the package pins to maintain the required board spacing.

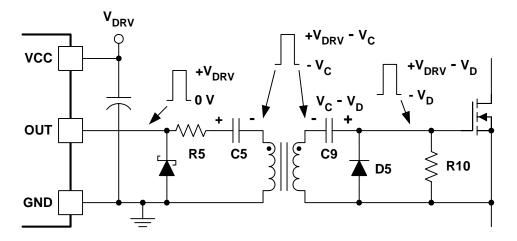

Fig. 6 illustrates some alternative pin configurations available with the popular 4N25 series of optocouplers. Note that with a surface mount configuration, the shape of the leads allows a board spacing close to 8 mm while with through-hole mounting, meeting an equivalent Creepage spacing would require either a wider lead bend or a slot cut in the PC board between the input and output rows of pins.

Fig. 6. Three pin configurations are offered with the popular 4N25 optocoupler to accommodate varying Creepage requirements for PCB mounting pads.

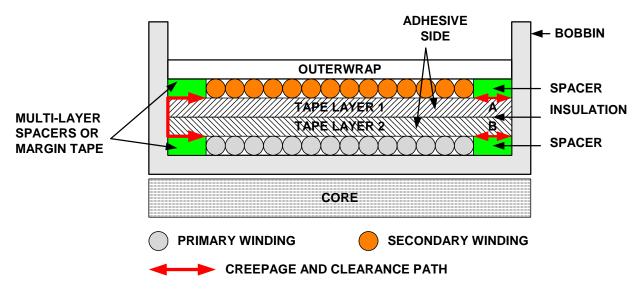

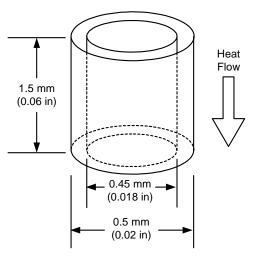

#### C. Transformer Construction

Fig. 7 shows a cross-section view of a typical isolating transformer where primary and secondary windings are wound on a common bobbin. Where hazardous voltages are involved, the insulation between primary and secondary must be at least Double or Reinforced with a minimum of two layers to allow for a single-element failure. Any enamel coating on the wire is not counted as an insulation level, although what is called "triple-insulated winding" wire meets Supplementary or Reinforced status depending upon the number of layers and their method of construction.

Unless the transformer is tested and qualified as a solid structure, completely filled with a solid insulating material, it is always assumed that there is a small amount of air present between the layers, even though there may be adhesive on one side of the insulating tape. In most transformer structures, Clearance and Creepage are the same and are shown in the figure as the sum of distances A and B. (The thickness of the tape is generally not taken into account.)

Transformer leads, as well as all other wires or cables must meet their own specifications and standards. Wire insulation must be PVC, neoprene, TFE, PTFE, or polyimide, or tested for flammability. Usually, insulating materials are required to meet one of the following classifications:

- V-1. Material is self-extinguishing upon removal of an external flame. Any flaming particles which drop do not ignite a cheese cloth fabric placed underneath.

- V-2. Material is self-extinguishing but cheese cloth may be charred or ignited from dropped flaming particles. V-2 material may only be used within an enclosure having no bottom openings.

Fig. 7. Definitions insulation requirements for isolating transformers.

#### XI. DESIGNING FOR SAFETY

Clearly, there are many decisions in the design process where a knowledge of safety requirements and the application of their principles can go a long way toward easing the time and cost of the safety certification process. Particularly if a failure in safety testing requires a redesign effort late in the program. Anticipating the testing which may be required and designing accordingly certainly pays off at the end of the day. While definitely not allinclusive, a summary of some of the design considerations is given below:

#### A. Materials

Pick components and materials which have prior safety certification. With certified components, the safety engineer looks only to see that they have been applied correctly and physical testing is done only as a complete Without system. certified components, additional component-level testing excessively conservative design techniques could be required. As an example, the Y capacitor in an input EMI noise filter would be accepted as a certified device, but otherwise might require two capacitors in series to allow a safety test to short one of them, plus the additional testing of the capacitors themselves.

#### B. Mechanical

The safety engineer looks for rigid construction with all components securely attached and no sharp edges or corners. All areas containing hazardous voltages have been protected from access by the user, including through any openings in the enclosure. Openings in the enclosure are examined to ensure that there is no user access to hazardous voltage, sharp edges, hot components, fan blades, or any other item that might cause injury. A specified "finger probe" is used to probe all openings. Positive earthing connections and bonding straps must be provided where necessary.

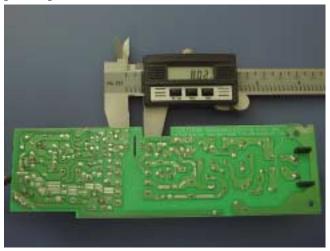

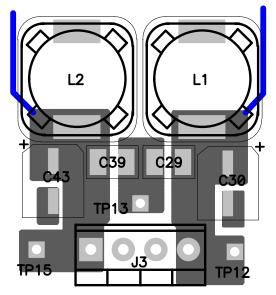

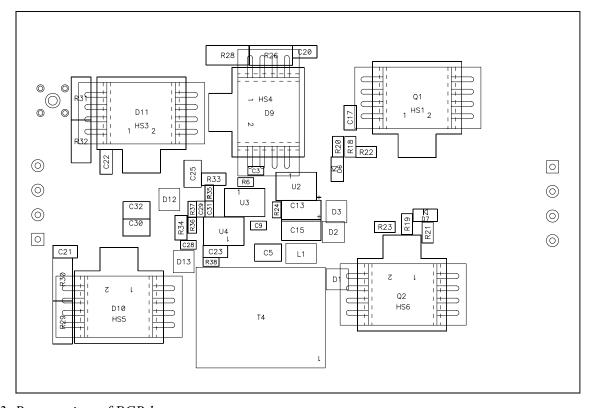

#### C. Layout

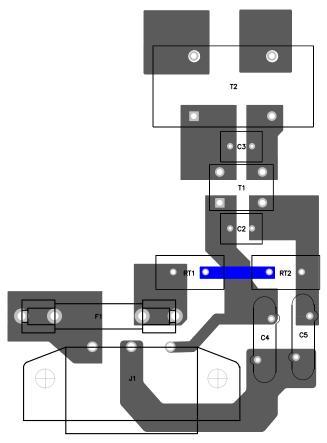

An appropriate isolation strategy must be defined and rigidly applied throughout the design. Creepage and Clearance spacings must separate all hazardous voltages from user accessible points. There should be a very clear channel between primary and secondary circuits, similar to that illustrated in Fig. 8. It should be noted that hazardous voltage levels may be present on some secondary circuits where a low voltage output might be generated from a low duty-cycle, high peak voltage, PWM power pulse.

Fig. 8. PCB layout view clearly showing the Clearance spacing and Creepage slot under the optocoupler. between primary and secondary circuitry.

#### D. Design

Remember that hazardous conditions may also exist on low-voltage outputs where high power is possible (>240 VA). As a minimum, effective current limiting may be required. The power supply should also be able to withstand an overload test consisting of blocking the air vents, stopping the fan, and overloading or shorting the output until the condition becomes stabilized or the ultimate result is achieved. Failure would certainly include flame and smoke, excessive heating of components, flying shrapnel from an exploding component, or failure to pass an appropriate HiPot test.

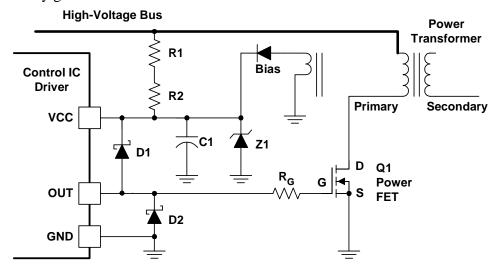

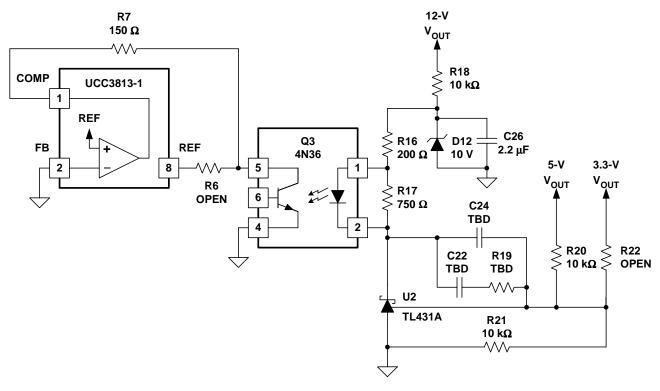

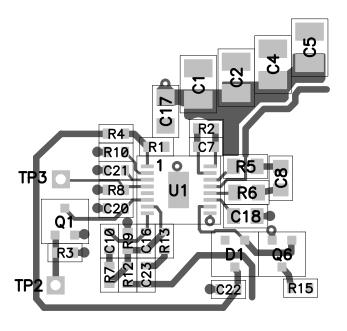

The design must also ensure that no single failure causes any of the above hazardous conditions. The safety engineer randomly and selectively opens or shorts any component with flame-detecting cheese cloth draped around the unit under test. Anticipating these tests and designing for them is a necessary task. As an example, Fig. 9 shows a typical application of a low-voltage controller for an off-line supply, but modified in two simple ways. First, the start-up resistor to initially power the IC controller has been divided into two resistors, R1 and R2, allowing either to be shorted while still limiting current from the high-voltage bus. And secondly, anticipating a short applied between drain and gate of the power FET, the designer has used a fusible resistor for Rg, and added D1 to shunt excessive current around the IC and to ground through Z1.

In anticipation of these safety tests to simulate failures by shorting components, consideration should be given to insuring that either the input fuse blows (which is acceptable) or that, at least, dramatic failures (such as exploding capacitors) are prevented. Placing devices MOV protection across electrolytic capacitors is a common way to limit over-voltage. Where voltage is not an issue, two capacitors in series may allow one to be safely shorted - a technique useful when adding a noise-reducing bypass capacitor between primary and secondary grounds.

#### XII. POWER SUPPLY CERTIFICATION

While testing procedures may vary according to test agency, type of power supply, and application or end use, they typically include the following steps:

- A construction analysis on open or unsealed test samples, checking:

- Insulation coordination

- Clearances, Creepage, and solid insulation dimensions

- Accessibility

- Protective earthing

- Strain relief

- Mechanical evaluation

- Determination, using both analysis and physical measurement, of internal working voltage limits

- Worst-case operational testing, exercising both input voltage and load variations.

- Single fault and overload testing including short circuits

- Heating tests under normal operating conditions

- Humidity

- Hi Pot leakage current measurements

- Flame tests

- And whatever additional specialized testing is deemed necessary

Fig. 9. An example of start-up circuitry with components R2 and D1 added in the interests of safety.

The certification process starts with the submittal of an application and documentation package to completely describe the power supply and all its component parts and materials. A number of units for testing are also provided, often five without an enclosure and five in completed form, together with a purchase order for the cost which typically ranges between \$6000 and \$8000 for the average small power supply. The certification process can take as little as 6 to 8 weeks, but with a product containing design deficiencies, can go much longer.

#### XIII. ACKNOWLEDGEMENT

Texas Instruments recognizes and appreciates the technical material and support provided by Underwriters Laboratories in the preparation of this seminar topic. For additional information on this subject or about the specialized seminars presented by UL, use the following contact information.

The UL website: <a href="http://www.ul.com">http://www.ul.com</a>

E-mail: CustomerService.NBK@us.ul.com

Phone in North America: 1-877-UL-HELPS

### **Topic 2**

Sequencing Power Supplies in Multiple Voltage Rail Environments

# Sequencing Power Supplies in Multiple Voltage Rail Environments

David Daniels Dirk Gehrke Mike Segal

#### **ABSTRACT**

Designers must consider timing and voltage differences during power up and power down in systems where multiple power rails are involved. A simple example would be a single DSP with its core and I/O voltages, requiring power supply sequencing. The possibility for a latch-up failure or excessive current draw exists when power supply sequencing is not designed properly. The trigger for latch-up may occur if power supplies are applied at different potentials of the core and I/O interfaces. This paper addresses some of the more common sequencing requirements of digital signal processing (DSPs), field programmable gate arrays (FPGAs), application-specific integrated circuits (ASICs) and microprocessors, and proposes a variety of practical solutions implemented with power management devices. These techniques take advantage of the reset, power good, enable and soft-start features available on many types of power management devices ranging from low drop out (LDO) regulators to plug-in power modules.

#### I. Introduction

High-performance signal processing devices, such as FPGAs, ASICs, PLDs and DSPs require multiple power supplies that generate different voltages for the core and I/O voltages. The order in which these voltages power up and power down can prove critical to device operation and long term reliability. This paper addresses some of the reasons devices require the different types of power supply sequencing and offers examples of practical supply sequencing solutions.

#### II. WHY SEQUENCE POWER SUPPLIES?

Designing a system without proper power supply sequencing may introduce potential risks, including compromised reliability and immediate faults. Long term reliability is sacrificed when an out-of-bounds condition persists on a multisupply device for extended periods of time. The risk comes when there is an active power supply rail and an inactive supply on a device for long periods. This condition can electrostatic discharge (ESD) protection and other internal circuits that interface between the different voltages. The amount of time the device can be stressed before potential damage occurs under these conditions may be measured in months, but it is the cumulative exposure to these conditions that determines the usable life of the product. While a few poorly controlled power-up and power-down cycles are unlikely to damage a device, a system that is power cycled time after time without proper power supply sequencing can eventually fall victim to this failure mode.

Another risk of improper power supply sequencing in a system can cause immediate damage to a device. This failure is often a result of excessive current flow into a pin or excessive voltage differential across pins that stress internal components. The causes of these immediate failures are similar to those of the reliability failures. The difference is how the device is affected by the stresses.

#### A. Latch-Up

Since most multi-supply devices are fabricated in CMOS technology, the devices are susceptible to an electrical failure mode called latch-up. Latch-up can occur when voltage and current levels beyond the normal operating level stress pins of a powered device. When latch-up occurs, the device draws unusually high supply current which may render the device inoperable and/or cause permanent damage to the device.

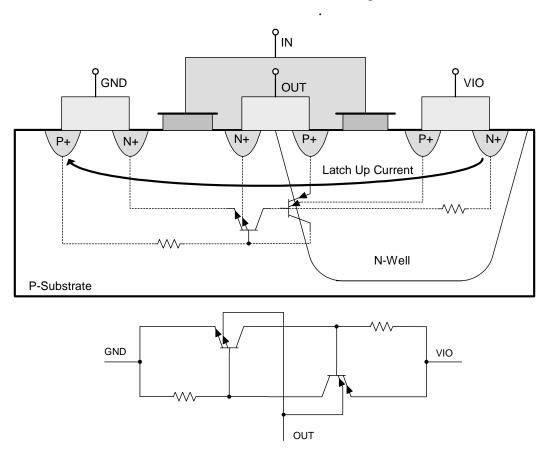

Fig. 1 depicts a cross section of a CMOS inverter with the parasitic bipolar transistors overlaying the illustration.[1][2] The source of the N-channel MOS device serves as emitter, the N-well as collector, and substrate as base of the parasitic bipolar NPN transistor. Similarly, the source of the P-channel MOS device serves as emitter, the N-well as base, and the substrate as collector of the parasitic bipolar PNP. These parasitic bipolar transistors comprise a PNPN structure commonly known as a siliconcontrolled rectifier (SCR). The PN junctions of the parasitic transistors are normally reversebiased. However, a PN junction of the parasitic SCR may become forward-biased due to disturbances resulting **SCR** electrical in conduction which may result in device failure. Among electrical disturbances which may cause latch-up are voltages on pins beyond the supply voltage rails, large DC currents in the substrate or N-well, and displacement currents in the N-well substrate or resulting from transitioning internal nodes.

Fig. 1. Cross-section of CMOS inverter.

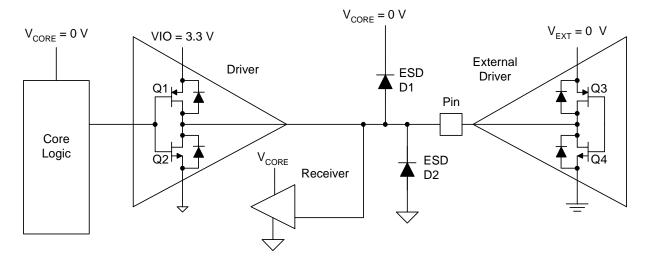

Fig. 2 represents the architecture of a multivoltage device, such as a programmable logic device (PLD), interfacing to an external driver.[3] To illustrate some of the problems with sequencing power supplies, the system consists of three power supplies:  $V_{CORE}$ ,  $V_{IO}$ , and  $V_{EXT}$  at 5 V, 3.3 V and 3.3 V, respectively.

Consider the following scenario: V<sub>IO</sub> supply is active, V<sub>CORE</sub> is inactive, and the driver input is not initialized. Since the driver is not in a known state, Q1 could be biased on, sourcing current through ESD diode D1. The magnitude of the current depends on the impedance of O1, D1 and the inactive supply. Latch-up may occur as current flows through the ESD diode when the core supply ramps up. Whether this current causes a catastrophic latch-up failure, latent reliability issue, or neither, depends robustness of the device design. In other words, damage may not occur if magnitude of the current is sufficiently low that the silicon can conduct the current without compromising reliability.

A potential latch-up issue arises when peripheral devices, such as data converters and memory, are coupled to the I/O pins of a multisupply device and powered from a different supply that is ramping. Fig. 2 shows an external driver coupled to the I/O pin that has a "sneak path" through the anti-parallel body diode of Q3 when the  $V_{\rm EXT}$  pin voltage is lower than  $V_{\rm IO}$ . This issue can easily be resolved by connecting the  $V_{\rm EXT}$  and  $V_{\rm IO}$  pins to the same power supply.

When  $V_{EXT}$  is active and the external driver sources current into the pin when  $V_{CORE}$  or  $V_{IO}$  is ramping, the potential for latch-up in the multisupply device exists.

Trends in the semiconductor industry include increasing device speed, including more features, reducing power consumption, and reducing device size, all the while shortening product development cycle times. To meet these goals, design teams pack more components into a smaller area by using smaller device geometries, thinner well structures, and lighter substrate and well concentrations. Unfortunately, these design techniques increase the ohmic resistance and gain (or "beta") of the parasitic PNP and NPN transistors which, in turn, increases the likelihood of latch-up. Design techniques to prevent latchup include using protection circuits and "guard rings". Protection circuits are used on input and output pads to safely shunt current and guard rings are used around wells to provide lowresistance. Both these prevention techniques come at the penalty of device size and cost.

The device's core voltage, susceptibility to latch-up, and supply sequencing order are, all too often, determined after pre-production silicon is available and device characterization and qualification are performed. With the emphasis on meeting cost and customer timetables for the latest product, if only minor issues are found with a device (such as a preference for supply sequencing), the issues are documented and the device released to market.

Fig. 2. Close-up of a multi-voltage device.

#### B. System-Level Bus Contention

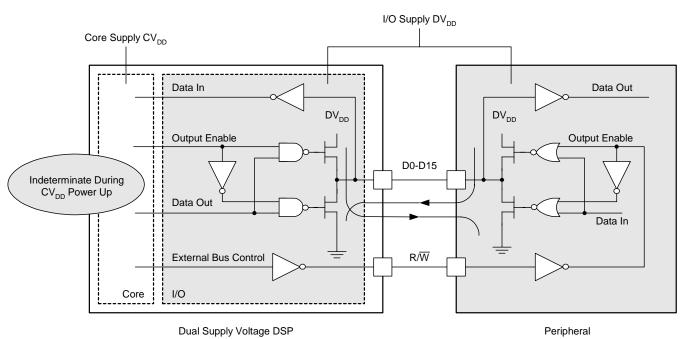

Power supply sequencing may be required to prevent system-level bus contention, in which the bidirectional I/O pins of a DSP and external peripheral device oppose each other. Since the bus control logic originates in the core section of the DSP, powering I/O prior to the core may result in both the DSP and peripheral simultaneously configured as outputs. If the data values on each side are opposing, then the output drivers contend for control, as shown in Fig. 3.

Excessive current flows in one of the paths shown, depending on the opposing data-out patterns. The outputs contend for control and excessive current flows when the data values are opposing. This excessive current may damage the bidirectional I/O ports. Following the recommendation to power the core at the same time or before the I/O prevents undefined logic states on the bus control signals. [4]

#### III. SEQUENCING SCHEMES

There are three distinct schemes to power-up and power-down multi-rail power supplies: sequential, ratio-metric, and simultaneous [5]. The appropriate sequencing scheme is dependent on device requirements. The manufacturer's data sheet does not explicitly name which power sequencing scheme to implement, but rather outlines voltage and timing conditions that cannot be exceeded on power supply pins. Note that some devices allow out-of-bounds conditions for a short period of time. Using the pin conditions and the waveforms in the following section, a sequencing methodology can be chosen to meet the processor requirements.

Fig. 3. System-level bus contention.

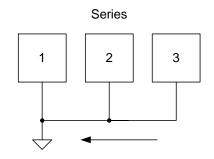

#### A. Sequential Sequencing

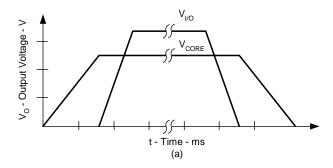

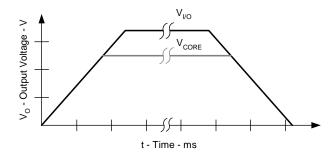

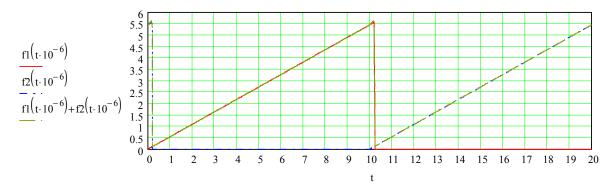

The sequential scheme of power supply sequencing is best described as one power supply ramping and settling to its final regulation voltage and then the second power supply ramping after a time delay. This method is used to initialize certain circuitry to a known state before activating another supply rail. An example applying the core supply rail prior to the I/O supply starting is shown in Fig. 4a.

Fig. 4. Sequential sequencing schemes.

The following is an excerpt from a footnote in a device specification with recommendations best suited to using sequential power supply sequencing:

"System-level concerns such as bus contention may require supply sequencing to be implemented. In this case, the core supply should be powered up at the same time as or prior to the I/O buffers and then powered down after the I/O buffers." [6]

An alternative power supply sequence order would call for the I/O supply to power up first and the core supply to start after the I/O power supply reaches regulation, see Fig. 4b. In the particular example [7], this method meets the recommended power sequencing for the device as long as the delay time for the start up of the

core supply is less than 100 ms. As presented later in this topic, a typical hardware implementation employs an output voltage monitor to develop a power good (PG) signal for the first power supply, which then connects to the enable (EN) function of the second power supply.

#### B. Ratio-Metric Sequencing

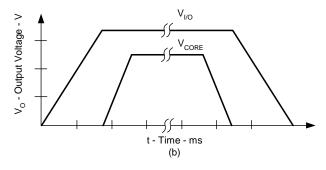

For a dual power supply implementing ratiometric sequencing, both power supply outputs ramp at the same time and in proportion until regulation is reached. Fig. 5a illustrates ratiometric power sequencing where the core and I/O supply reach regulation at approximately the same instant. During power-up the core supply is a percentage of the I/O supply until regulation is reached. Similarly, during power-down the core is a specific percentage of the I/O supply voltage. Another example of ratio-metric sequencing may find the core supply voltage slightly greater than the I/O supply during the power-up and down, see Fig. 5b. In this particular case, to ensure the I/O buffers have valid inputs, the core rail is powered slightly before the I/O rail to eliminate problems with bus contention. [8]

Fig. 5. Ratio-metric sequencing.

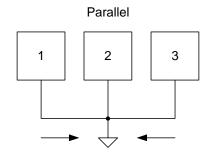

#### C. Simultaneous Sequencing

The simultaneous power sequencing method is similar to ratio-metric sequencing in that both power supply outputs ramp at the same time. However, in simultaneous sequencing, objective is to minimize the voltage difference between the two supply rails during power up and down, as shown in Fig. 6, until regulation is reached for the core supply. This sequencing method is useful for devices that have "sneak paths" between supply pins or draw excessive current during startup if internal logic has not transitioned to a stable state. Reference [9] recommends simultaneous sequencing to minimize transient start-up currents.

Fig. 6. Simultaneous sequencing.

The following sections show many examples of power sequencing implemented with:

- Diodes

- Low-dropout (LDO) linear regulators

- Supply voltage supervisors (SVS)

- Power distribution switches

- Hot-swap controllers

- Microcontrollers

- Switch-mode controllers (power FETs external)

- Switch-mode converters (power FETs internal)

- Plug-in power modules

### IV. SEQUENCING IMPLEMENTATIONS ILLUSTRATED WITH LDOS

#### A. Diodes

Diodes are often used to facilitate sequencing requirements. Though diodes alone cannot achieve true sequential, ratio-metric or simultaneous sequencing, they can help maintain proper relation between various supply voltages.

Fig. 7 illustrates use of a Schottky diode to limit voltage differential between the core and I/O rail. The Schottky diode further reduces potential stress on devices by bootstrapping the I/O supply and shortening the delay between supply ramps. [5]

Fig. 7. Schottky diode limits voltage differential.

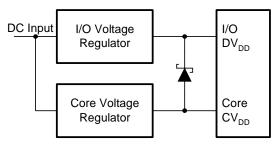

Fig. 8 shows rectifiers in combination to help meet these microprocessor requirements:

- "V<sub>IN</sub> must not exceed V<sub>DDH</sub> by more than

2.5 V at any time, including during power-on reset

- V<sub>DDH</sub> must not exceed V<sub>DD</sub>/V<sub>CCSYN</sub> by more than 1.6 V at any time, including during power-on reset.

- $V_{DD}/V_{CCSYN}$  must not exceed  $V_{DDH}$  by more than 0.4 V at any time, including during power-on reset." [17]

Fig. 8. Combination of diodes limits voltage differential.

"Note: There are internal diodes connected serially between VDDH and VDD, and vice-versa for ESD protection. If one of the voltages (VDD or VDDH) is applied and the other power pins are not driven, then the internal diodes pull up these pins. However, a problem could occur if one of the voltages (VDD or VDDH) is applied and the other voltage is forced to GND. In this case, the ESD diodes might be destroyed." [17]

To achieve *true* sequential, ratio-metric or simultaneous sequencing, enlist the capabilities of a wide range of active devices, as discussed in the following sections.

### B. LDO Enable Via Supply Voltage Supervisor (SVS)

Sequential Sequencing

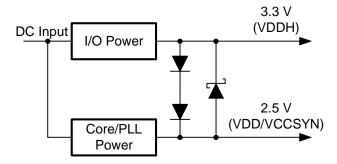

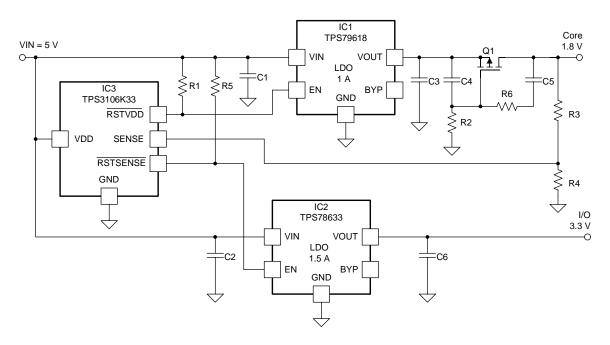

Fig. 9 shows an implementation of a supply voltage supervisor (SVS) to realize a sequential sequencing scenario. The load of this power supply is an FPGA which requires sequential sequencing. The power solution shown employs a 5-V input supply voltage rail. The core voltage is powered up first and, once the core voltage has ramped, the I/O voltage rail is enabled. Advantages of a linear regulator over a switch-mode approach typically include lower noise, reduced board space and cost. A key disadvantage is lower efficiency and, as a result, increased power dissipation.

Fig. 9. Sequential sequencing using SVS.

This solution is based on two LDOs, IC1 to supply core voltage and IC2 for the I/O voltage rail, along with an SVS, IC3. The dual SVS, with trip point threshold voltage of 2.941 V (typical), monitors the input voltage rail. Once the input voltage rail has reached the threshold of 2.941 V, the SVS reset output transitions from low to high impedance state after a delay of 130 ms, enabling LDO IC1. Once LDO IC1 is enabled, the core voltage ramps up towards its final value of 1.8 V. To ensure that the input voltage rail does not drop due to the high inrush current demand of the capacitor bank and the FPGA, a current-limiting circuit has been implemented. Without this current-limit circuit, the input voltage could potentially droop during the switch-on cycle. This current-limit circuitry, consisting of O1, C4, R2, R6 and C5, provides smooth charging of the load during power-up.

Core voltage is monitored via a comparator incorporated in SVS IC3. Voltage divider R3 and R4 adjusts the threshold voltage to the particular needs of the application. In this case, it has been adjusted to a threshold voltage of 1.7 V. Once the core voltage reaches the threshold voltage, IC3 enables LDO IC2, which provides the I/O voltage to the system, and the I/O voltage ramps to its final value of 3.3 V.

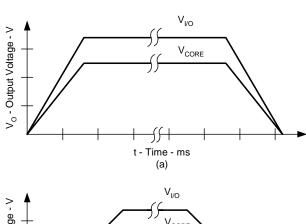

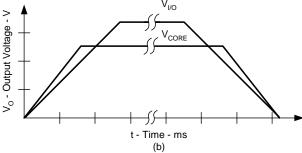

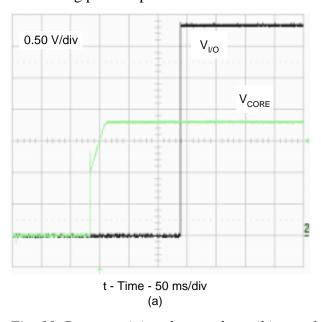

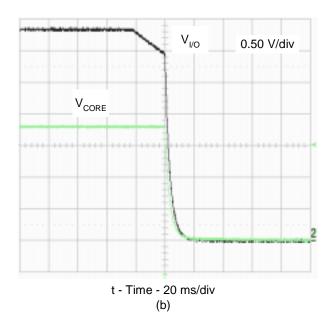

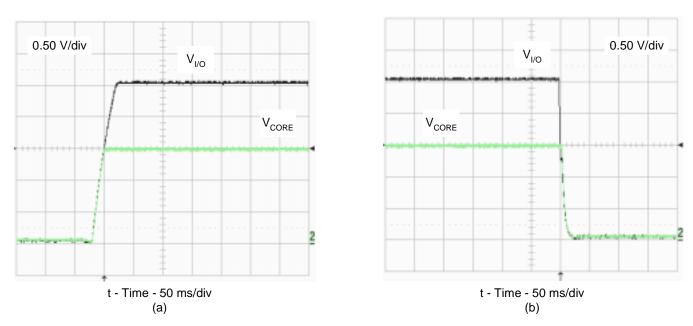

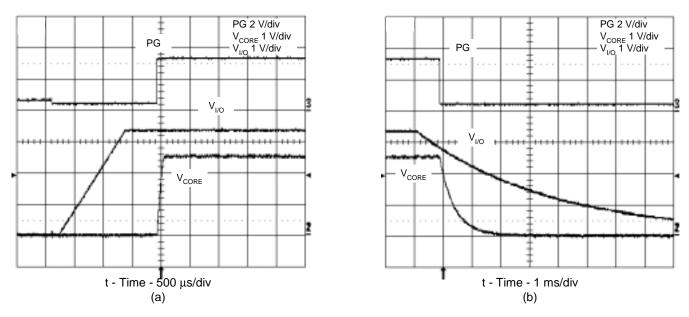

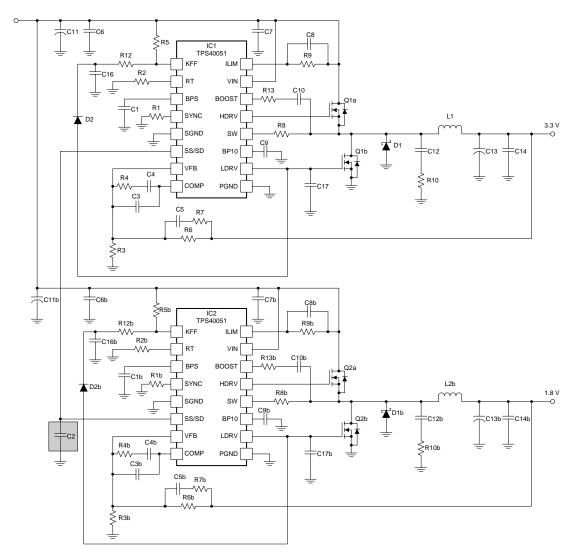

The power-up and power-down waveforms of this implementation appear in Fig. 10.

Fig. 10. Ramp-up (a) and ramp-down (b) waveforms for circuit of Fig. 9.

Simultaneous Sequencing

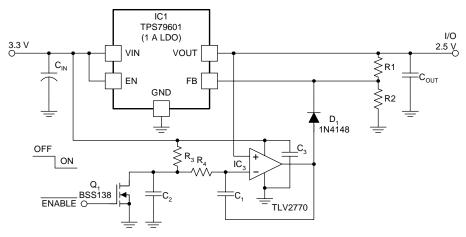

Some applications require either a specific slew rate or a maximum inrush current during power-up and power-down, which can be realized with the circuit in Fig. 11.

The power-up and power-down sequencing circuit employs network R3 and C2 to generate a ramp-up slope. This network is the slew rate reference for the output of the LDO during power-up and power-down. The operational amplifier compares the output voltage at its noninverting input with the voltage applied to its inverting input. It then adjusts the output voltage to match the slew rate determined by the RC network. When ENABLE transitions low, Q1 is switched off, and R3 starts to charge C2 to the input voltage rail level. When V<sub>OUT</sub> reaches 2.5 V, set by R1 and R2, the voltage at the operational amplifier inverting input continues to rise, causing the operational amplifier output to decrease. This reverse-biases D1, removing power-up and power-down the sequencing circuit from the feedback loop. R4 and C1 ensure a smooth voltage rise during power-up.

In this example, the output voltage set point can be calculated as follows:

$$R1 = R2 \times \left[ \left( \frac{V_{OUT}}{V_{REF}} \right) - 1 \right]$$

where  $V_{REF} = 1.224 \text{ V}$  for the LDO shown.

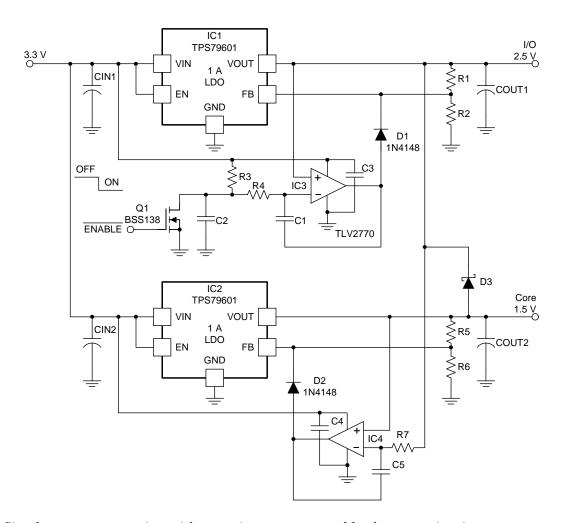

Fig. 12 features simultaneous sequencing circuitry that programs a required slew rate during power-up and power-down using IC2 as a tracking LDO.

The power-up and power-down sequencing circuit is using the same basic circuit as described above with programmable slope. In this example, the core voltage must track the I/O voltage during power-up and power-down. Additionally, the I/O voltage must be within 600 mV of the core voltage during power-up and power-down. If these conditions are violated, the processor could be damage due to forward-biasing of the substrate diode.

During power-up and power-down, IC4 provides active tracking to ensure that the voltage difference between I/O and core voltage is far less than the required 600 mV. Schottky diode D3 provides an additional level of protection.

During power-up, IC1's output voltage increases with the applied slope ramp at the inverting node of IC3. Operational amplifier IC4 derives the ramp-up and ramp-down slope from the 2.5-V I/O output voltage rail. During powerup, the I/O voltage slowly increases, and this voltage is applied to the inverting node of IC4. The non-inverting node detects the core voltage. which is the output of linear regulator IC2. When the core voltage reaches 1.5 V, set by R5 and R6, the inverting input of operational amplifier IC4 continues to rise, causing the operational amplifier output to decrease. This reverse biases D2, removing the tracking circuit from the feedback loop. Fig. 13 displays power-up and power-down waveforms, respectively.

Fig. 11. Capacitor-programmable slew rate circuit.

Fig. 12. Simultaneous sequencing with capacitor-programmable slew rate circuit.

Fig. 13. Power-up (a) and power-down (b) waveforms for circuit of Fig. 12.

#### C. LDO and Power Distribution Switch

Sequential Sequencing

Some applications challenge the designer to apply core voltage prior to I/O voltage, even though the input source voltage is already at the I/O voltage level. A high-side power distribution switch can be used to disable the I/O supply until the core voltage is powered up and stable. Fig. 14

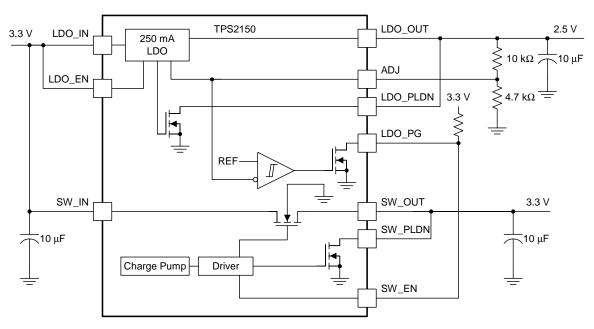

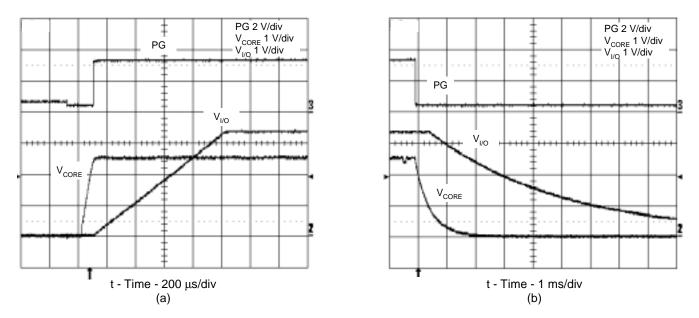

shows a sequential power supply sequencing implementation using the TPS2150, which integrates a high-side power switch with an LDO.

The TPS2150 uses the power good function of the LDO to enable the power switch, resulting in the power-up waveforms of Fig. 15a. The power switch and LDO feature pull down MOSFETs to discharge the bulk capacitance when the devices are disabled (Fig. 15b).

Fig. 14. Sequencing with combination LDO/high-side switch (core then I/O).

Fig. 15. Power-up (a) and power-down (b) of circuit in Fig. 14.

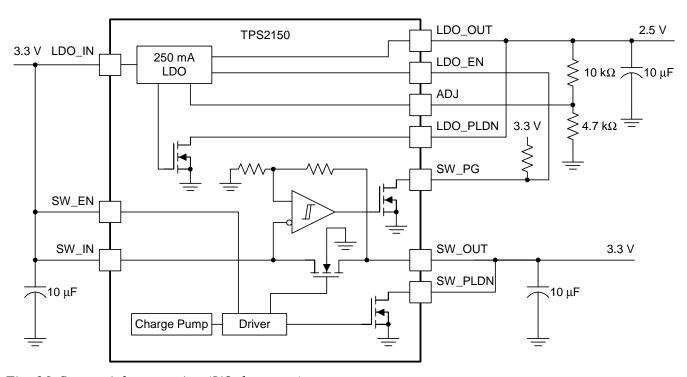

Fig. 16 implements the opposite configuration, in which the I/O voltage is applied before the core at turn-on. Corresponding waveforms are shown in Fig. 17.

Fig. 16. Sequential sequencing (I/O then core).

Fig. 17. Power-up (a) and power-down (b) waveforms for circuit of Fig. 16.

#### D. Hot-Swap Control

Simultaneous Sequencing

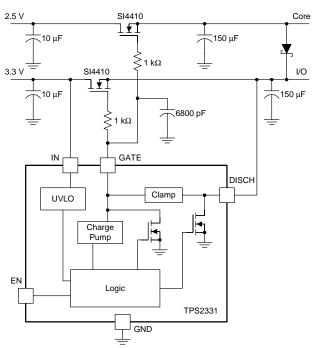

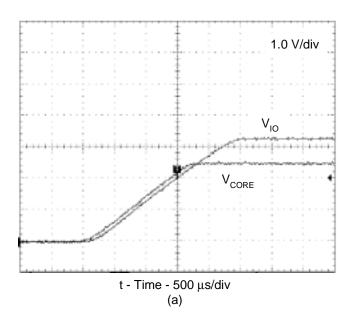

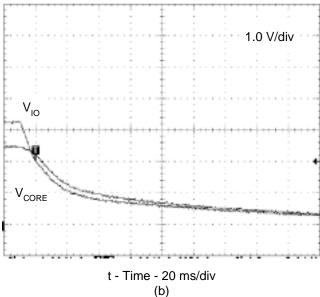

Another method to power-up and power-down with minimum voltage difference between the power supply rails is to use MOSFETs between the supply and load. Fig. 18 shows a simplified schematic using two MOSFETs and a TPS2331 hot swap controller to provide simultaneous start-up sequencing. By driving the gates of the MOSFETs with the same gate driver, the power supply rails effectively ramp together (Fig. 19a). The TPS2331 features an integrated pull-down transistor to discharge the bulk output capacitors, see Fig. 19b. The Schottky diode clamps the core supply during power-down.

Fig. 18. Simultaneous sequencing with hot-swap controller.

Fig. 19. Power-up (a) and power-down (b) waveforms for circuit of Fig. 18.

#### E. Microcontroller

Microcontrollers are among the most versatile devices available for sequencing. If the power supplies to be controlled feature enable pins, then controlling them is a simple matter of using general purpose input and output (GPIO) lines. If the enable function is not available, an in-line MOSFET or power distribution switch can be used to control the power supply, either with a GPIO or PWM signal.

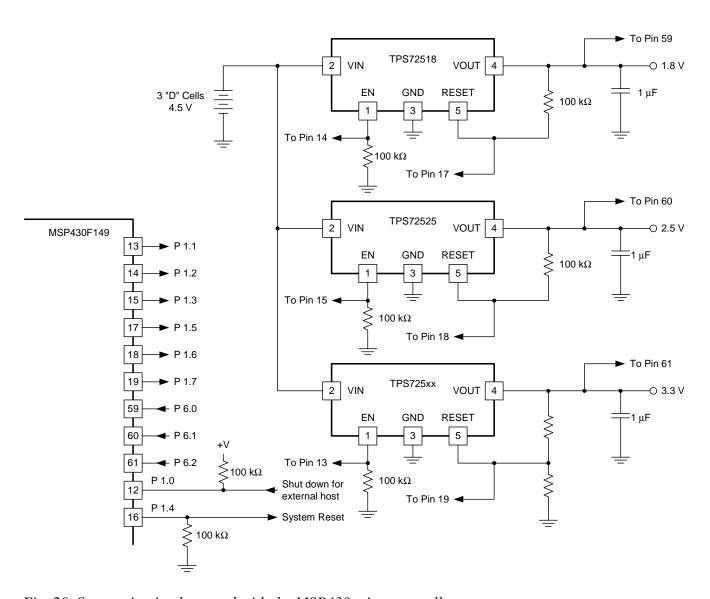

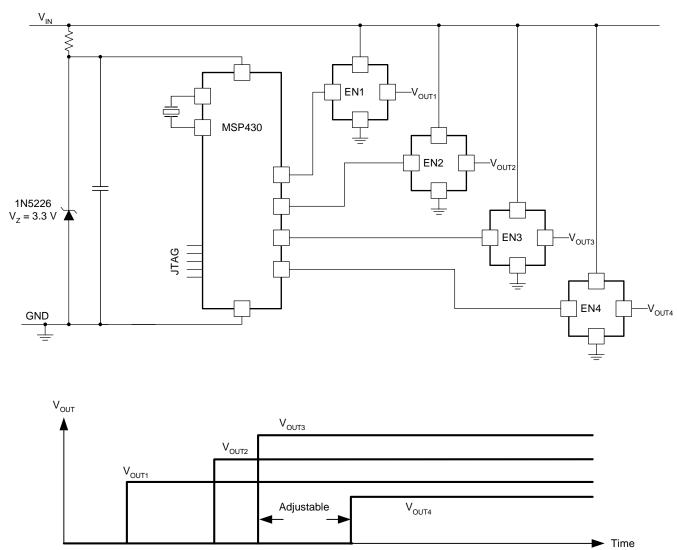

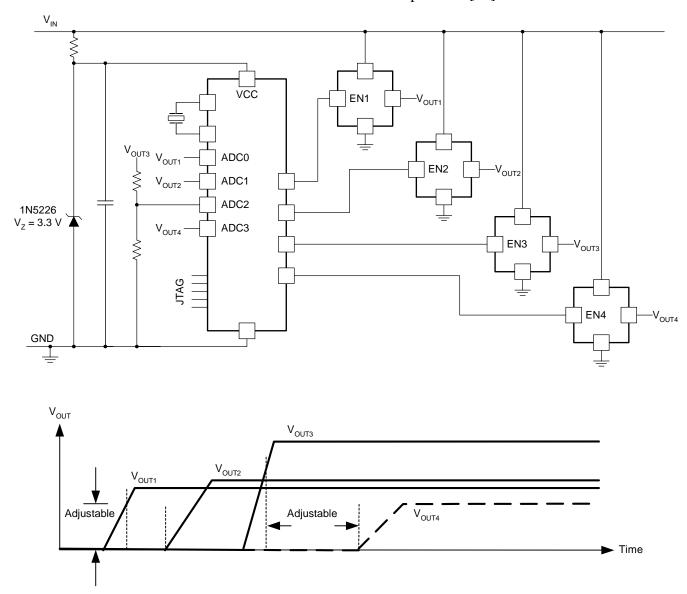

Use of a microcontroller is illustrated with the MSP430, a 16-bit RISC processor featuring several analog peripherals and a JTAG interface. The circuit of Fig. 20 uses the TPS725xx family of LDOs to provide 3.3 V, 2.5 V and 1.8 V from an input DC source. These LDOs have an enable pin and reset function. This circuit can easily be expanded to any number of voltage rails. The MSP430 monitors a control variable to determine when each rail should be activated. For power sequencing applications, the two most commonly controlled variables are time and voltage.

Fig. 20. Sequencing implemented with the MSP430 microcontroller.

#### Sequential Sequencing

When time is the control variable the first rail is enabled then, at a specific time thereafter, the next rail is enabled. Some time after that the next rail is enabled and so on, until all rails have been enabled. The MSP430 provides the timing sequence and the control signals to turn on the power supplies (Fig. 21).

If voltage is the control variable, then the first voltage rail is activated and its rise is monitored via an analog-to-digital converter (ADC). When the first voltage rail has reached a specific voltage level, the next voltage rail is enabled and its rise is monitored until it has reached a specified voltage level, at which point the next voltage rail is enabled and monitored. This continues until all voltage rails have been enabled (Fig. 22). When using voltage as the control variable, either a GPIO or PWM signal can be used as the enable signal, depending on whether rail tracking is required. Of course, a combination of voltage and timing control can also be used.

Fig. 21. Sequential sequencing with microcontroller (time as the control variable).

Once the MSP430 has turned on all the voltage rails and applied the system reset, it enters the monitor mode. It continually checks the output voltages, via the reset or output pins, depending on whether time or voltage is the control variable. If a fault occurs, the MSP430 enters an error routine. The most obvious fault would be the loss of a voltage rail, but other faults such as over- or under-voltage could also be monitored. The actions taken in the error

routine are completely application-dependent. The simplest action is to power down all rails, but programmability offers the user complete control.

Power-down sequencing can be just the opposite of the power up sequence, or any sequence required to meet system demands. One addition to the power-down sequence could be turning on dummy loads to discharge the output filter capacitors. [16]

Fig. 22. Sequential sequencing with microcontroller with voltage as the control variable.

### V. SEQUENCING WITH SWITCH-MODE CONTROLLERS, CONVERTERS AND MODULES

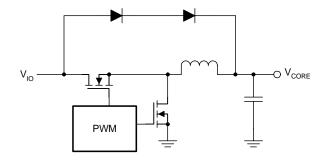

### A. Pre-Bias Start-Up and Synchronous Rectifier

Many switch-mode power stages employ synchronous rectification to improve efficiency, as illustrated by the simplified synchronous buck converter shown in Fig. 23. In this example, VIO comes up first, and applies core voltage through the series diodes before the core's converter is enabled. Defining this as a pre-bias condition, in which voltage is applied at the converter output before the converter is enabled. When the converter's PWM controller is enabled, it softstarts the high-side FET, and its duty cycle (D) ramps gradually from zero to that required for regulation. However, if during soft-start the synchronous rectifier (SR) FET is on when the high-side FET is off (SR FET duty cycle = 1-D), the SR sinks current from the output (through the inductor), tending to cause both the core and I/O voltages to drop. It is for this reason that PWM controllers with pre-bias start-up have been introduced, which disable SR drive during startup. Until drive to the SR is enabled, inductor current flows through the parasitic body diode of the SR FET rather than through the channel. Once the soft-start time is complete, drive to the SR is enabled.

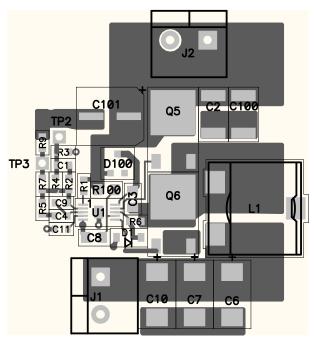

Fig. 23. Example of pre-bias condition.

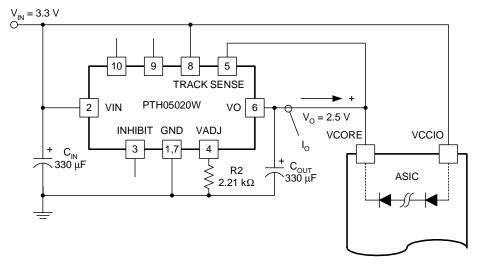

The need for synchronous converters with pre-bias start-up also arises when using a sequential power-up technique with some ASICs, in which a leakage path within the device causes some I/O voltage to appear on the core voltage before the core converter is enabled. Fig. 24 uses a PTH series power module for illustration. The PTH power modules incorporate synchronous rectification, so can sink current under normal operating conditions, but the 3.3-V and 5-V input versions do not do so during power-up, or whenever the module is turned off via the Inhibit pin. In Fig. 24, module U1 (PTH05020W) produces 2.5 V for the core.

Fig. 24. Pre-bias example with PTH power module.

Fig. 25 shows the waveforms of the circuit after input power is applied. It shows  $V_O$  rising along with VIN once VIN forward-biases the leakage path within the ASIC. Note that output current ( $I_O$ ) is negligible until  $V_O$  rises above the pre-bias voltage (point A). From hereon, the waveform of  $I_O$  exhibits a positive output current. [19]

Fig. 25. Power-up waveforms with pre-bias.

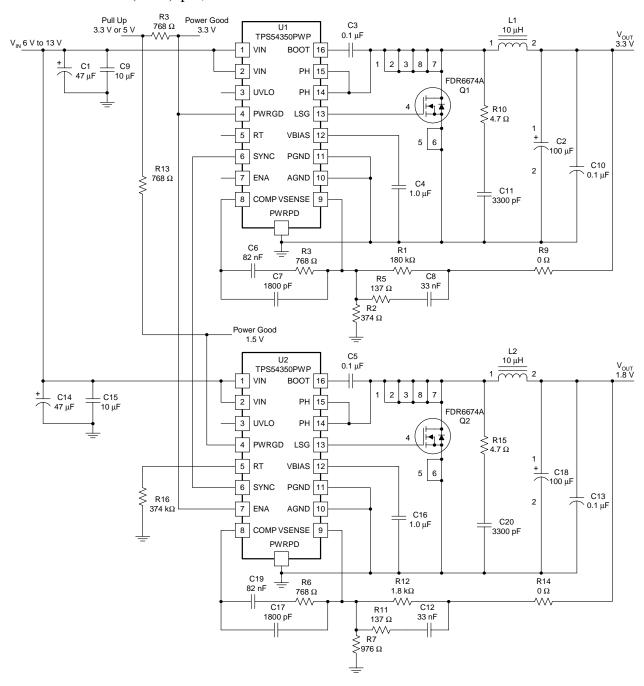

#### B. DC-DC Controllers

Ratio-Metric Sequencing

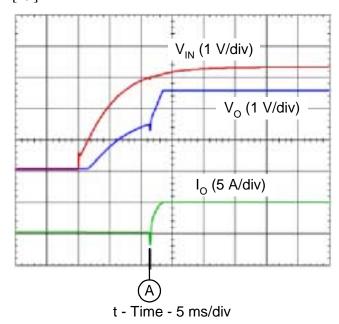

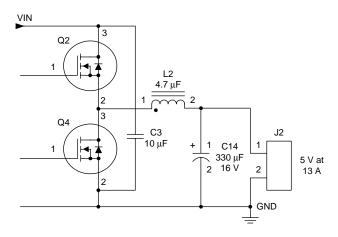

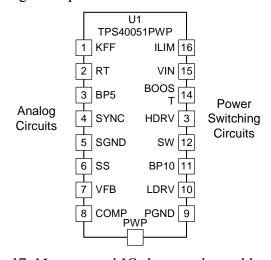

In ratio-metric sequencing, multiple output power rails start ramping at the same time and in proportion. This function can be accomplished with multiple controllers sharing a common soft-start capacitor. The solution in Fig. 26 (waveforms in Fig. 27) is based on two TPS40051 synchronous buck controllers with a wide input voltage range of 8 V to 40 V. These controllers drive synchronous rectifiers and feature feed-forward voltage-mode control. In this example, I/O voltage is 3.3 V and core voltage is 1.8 V.

Soft-start is programmed by charging external capacitor C2 via an incorporated current source of 2.3 µA. The voltage rise on C2 is then fed into a separate non-inverting input to the error amplifier (in addition to the feedback voltage and the 700-mV reference voltage). Once voltage on C2 exceeds 700 mV, the internal reference voltage is used to establish regulation. To ensure a controlled ramp of the output voltage, the soft-start time should be greater than the output inductor and output capacitor time constant.

So, in this example,

$$t_{START} \ge 2 \pi \sqrt{L1 \times C13}$$

(seconds)

and the soft-start capacitance calculates as:

$$C2 = 2 \times \left(\frac{2.3 \,\mu\text{A}}{0.7 \,V}\right) \times t_{START}$$

(Farads),

since the current feeding the soft-start capacitor is  $2.3 \mu A$  per controller. [20]

Fig. 26. Ratio-metric sequencing with common soft-start capacitor.

Fig. 27. Power-up (a) and power-down (b) waveforms for Fig. 26.

#### C. DC-DC Converters

Simultaneous Sequencing

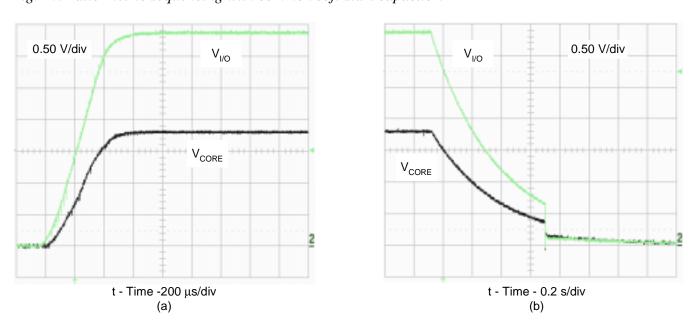

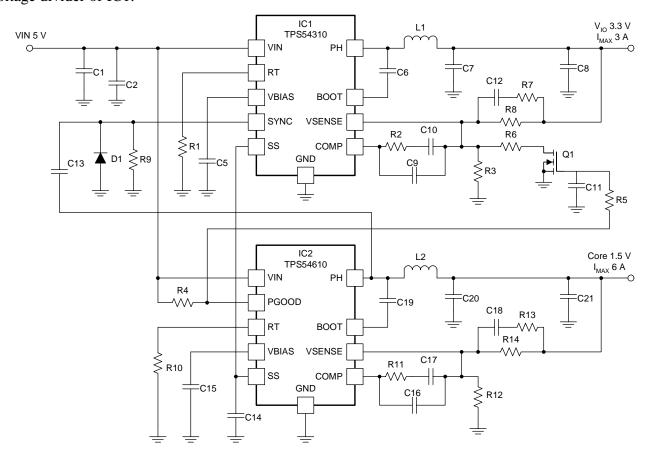

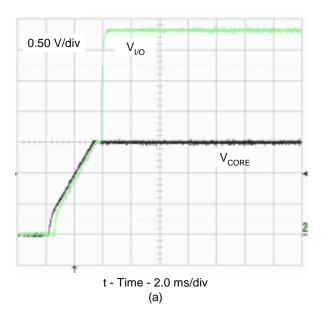

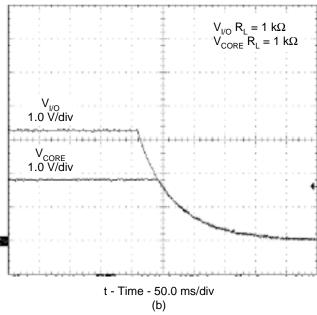

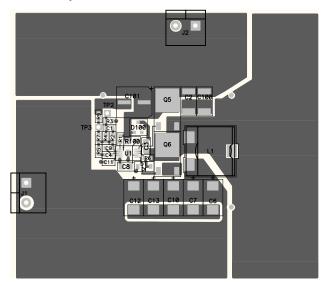

As previously mentioned, the objective of simultaneous sequencing is to minimize the potential difference between voltage rails as they ramp. Fig. 28 illustrates such an implementation using switcher with integrated FET (SWIFT) converters that integrate both high-side and synchronous rectifier FETs. IC1 provides I/O voltage of 3.3 V, while IC2 provides core voltage of 1.5 V. The converters share one soft-start capacitor (C14) to ensure the outputs ramp at the same slope. Note that these are voltage-mode controlled converters. IC2 acts as master controller. Its output voltage is programmed at 1.5 V via voltage divider R14 and R12. Additionally, power-good (PGOOD) comparator is used as a master flag to release the voltage divider of IC1.

During power up (Fig. 29a), both converter output voltages rise with the ramp of the softstart capacitor to an output voltage of 1.5 V. This is due to voltage dividers R14 and R12 at IC2, and R8 and R3 at IC1. During power-up, the power good (PGOOD) pin of IC2 is active low, holding Q1 off so that the output voltages track during power up until IC2 reaches 90% of its final value. Once IC2 detects an output voltage level of 90% or greater, PGOOD goes high impedance, and pull-up resistor R4 drives the gate of Q1 on via RC network R5 and C11. Once the gate threshold voltage of Q1 reaches 1.6V (typical), it starts to conduct and switches R6 in parallel to R3. This parallel combination changes the output voltage set point of IC1 to program 3.3-V output.

Fig. 28. SWIFT converters configured for simultaneous sequencing.

Fig. 29. Power-up (a) and power-down (b) waveforms for Fig. 28.

In this implementation, a general purpose BSS138 FET is used with a typical threshold voltage of  $V_{GSth}=1.6$  V. This FET features  $R_{DS(on)} < 10~\Omega$  (negligible compared to the values of R3 and R6), so does not affect the calculated output voltage set point value.

The set point resistor values can be calculated as follows:

A. Equation for  $V_{CORE}$

$$R3 = \frac{V_{REF} \times R8}{V_{CORE} - V_{REF}}$$

$$V_{CORE} = 1.5 \text{ V}, V_{REF} = 0.891 \text{ V}$$

$$Choose R8 = 27.4 \text{ k}\Omega$$

$$then R3 = 40.2 \text{ k}\Omega$$

B. Equation for  $V_{LO}$

$$R_{X} = \frac{V_{REF} \times R_{8}}{V_{I/O} - V_{REF}}$$

where R<sub>X</sub> is R<sub>3</sub> || R<sub>6</sub>

$$V_{I/O} = 3.3 \text{ V}$$

so R<sub>X</sub> = 10.22 kΩ

C. Equation for R6

$$1/R_{X} = 1/R3 + 1/R6$$

so,

$$R6 = \frac{1}{1/R_{X} - 1/R3}$$

$$R6 = 13.7 \text{ k}\Omega$$

PGOOD of IC2 transitions low when V<sub>CORE</sub> falls under 90% of its initial value during power-down (Fig. 29b). This discharges C11 and the gate of Q1 via R5. Once the gate of Q1 falls below its threshold voltage level (1.6 V typical), R6 is removed from the feedback divider. Thus IC1's output voltage set point drops to 1.5 V and the I/O voltage ramps down along with the core voltage. Note during power-down the voltages do not track each other due to differing output capacitor energy storage and load levels. The tracking version of the SWIFT converters can be used to address this issue.

A noteworthy feature of this implementation is that the converters are running at the same switching frequency. IC2 is the master device programmed to a switching frequency of 700 kHz. IC1 starts at a lower initial switching frequency of roughly 630 kHz, 10% below the switching frequency of IC2. Once IC2 begins to operate, it synchronizes IC1 via the SYNC pin. Diode D1 limits negative voltage spike amplitude at the SYNC input.

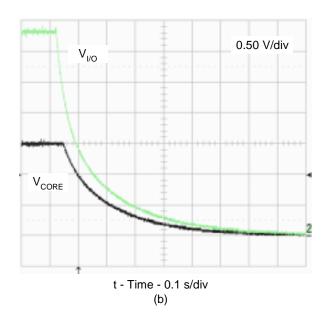

#### Sequential Sequencing

Fig. 30 shows a dual power supply design with sequential power-up using the TPS54350 dc/dc converter. The circuit uses the power good function of the I/O supply to activate the enable of the core supply. Once the I/O supply is up and stable, the power good pin (PWRGD) transitions from active low to high impedance (see Fig. 31). The TPS54350 has an internal pull-up current source on the enable (ENA) pin, so an external

pull-up resistor is not required to enable the core supply. As discussed in the last section, the challenge with using this power good and enable technique is the power-down sequence. It is preferred to power down the supply rails in the reverse order of power up. Because of supply loading and the disabling of the I/O supply and core supply at the same time, this order is not guaranteed.

Fig. 30. Sequential sequencing with TPS54350 converters.

Fig. 31. Power-up waveforms of Fig. 30.

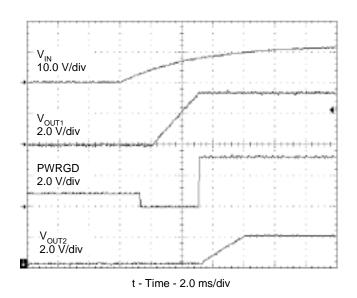

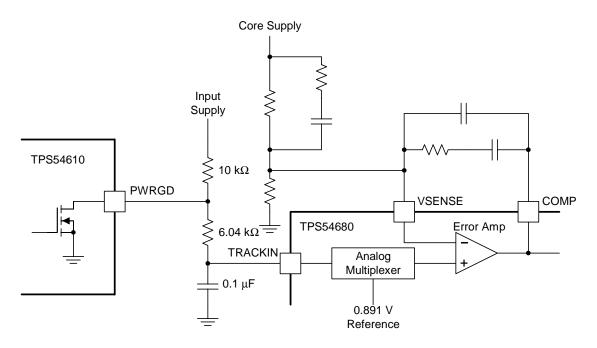

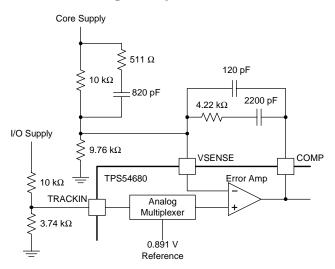

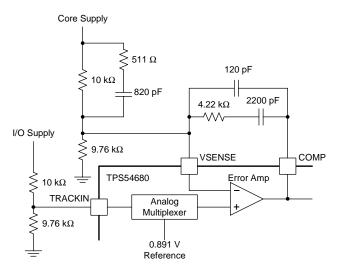

Another technique to implement sequential sequencing is implemented by connecting the power good function to the TRACKIN pin of a TPS54680 Sequencing SWIFT converter using resistors and a capacitor (Fig. 32) [10]. The TPS54680 was designed for applications that have critical power supply sequencing requirements. The device has a TRACKIN pin to facilitate the various sequencing methods. The TRACKIN pin is the input to an analog multiplexer that compares a 0.891-V internal voltage reference to the voltage on the TRACKIN pin, and connects the lower of the voltages to the non-inverting node of the error amplifier. When the TRACKIN pin voltage is lower than the internal voltage reference, the TRACKIN pin voltage is effectively the reference for the power supply. The power-up and power-down waveforms are shown Fig. 33.

Fig. 32. Sequential sequencing with TPS54680 track input.

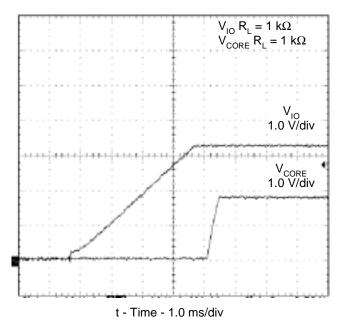

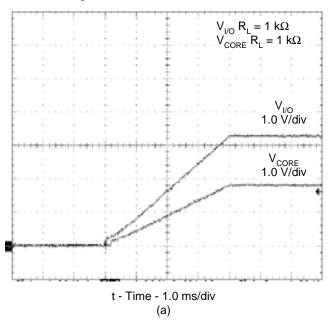

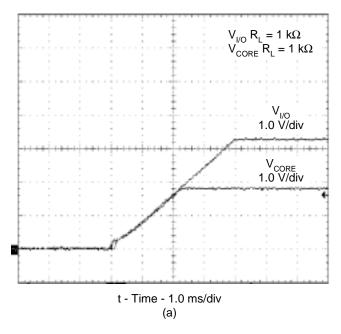

Fig. 33. Power-up (a) and power-down (b) waveforms of Fig. 32.

As shown in Fig. 33a, the 3.3-V I/O supply ramps first. When the I/O supply reaches its final 3.3-V steady state value, the open drain output of the PWRGD pin releases the TRACKIN pin, and the core supply rises at the rate of the RC time constant. The 0.1-µF capacitor is used to minimize the inrush current during startup of the core supply. The PWRGD pin asserts, pulling the TRACKIN pin low, when the SSENA pin is pulled low on the TPS54610 or when the I/O voltage is below 90% of the desired regulated voltage. Ideally, the I/O and core supplies power down in opposite order of power-up. If there is no load or a light load on the core when the I/O rail powers down, the TPS54680 device has the ability to sink current and transfers the energy stored in the output capacitor to the input capacitor. Fig. 33b shows power-down with  $1-k\Omega$ loads on both outputs.

#### \_Ratio-Metric Sequencing

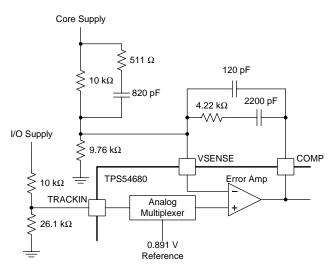

Fig. 34 Ratio-metric sequencing with TPS54680 track input.

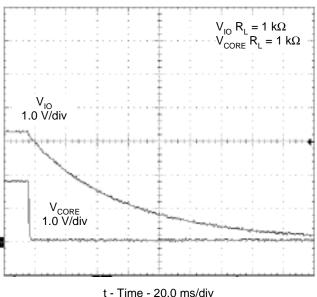

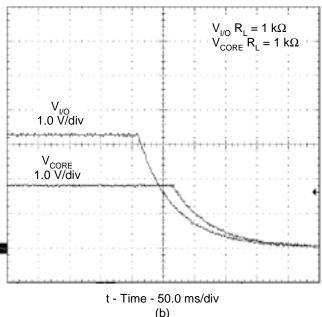

The analog multiplexer on the TPS54680 can also provide ratio-metric power sequencing by setting the divider ratio on the TRACKIN pin to a different value than that of the feedback compensation. Fig. 34 shows a simplified schematic with the TRACKIN voltage divider set to program lower voltage than the feedback divider, resulting in the core powering-up and down in proportion to the I/O voltage. The waveforms for the core and I/O supplies are shown in Fig. 35a and 35b.

Fig. 35. Power-up (a) and power-down (b) waveforms of Fig. 34.

If the core supply must power up slightly before the I/O supply, the TRACKIN voltage divider ratio should be set to program higher voltage than that of the feedback divider (sample schematic and waveforms in Fig. 36 and 37). For an equation on the selection of the TRACKIN resistors see reference [10].

Fig. 36. Ratio-metric sequencing (core up first).

Fig. 37. Power-up (a) and power-down (b) waveforms of Fig. 36.

#### Simultaneous Sequencing

To minimize voltage differences between supply rails during power-up and down, the TPS54680 can be configured for simultaneous sequencing as shown in Fig. 38. By selecting the TRACKIN voltage divider to have the same ratio the voltage divider in the feedback compensation loop, the core and I/O supplies power up and down with waveforms similar to Fig. 39. As before, the outputs of the regulators are loaded with 1-k $\Omega$  resistors. It can be observed from the waveforms that the voltage difference between the rails is minimal during power down. If the I/O supply is heavily loaded and the core supply is lightly loaded during power down, there may be a voltage difference between the rails. This is because the core supply cannot sink current as fast as the I/O supply is falling. This can be countered by adding more bulk capacitance on the I/O output.

Fig. 38. Simultaneous sequencing with TPS54680 track input.

Fig. 39. Power-up (a) and power-down (b) waveforms of Fig. 38.

#### VI. SUMMARY

Design of a multi-rail power system often involves much more than simply converting input voltages to output voltages and currents. As has been discussed, the power-up and power-down sequencing of these voltages can significantly impact proper system operation and reliability. Three distinct power sequencing schemes have been defined (sequential, ratio-metric simultaneous) and implementations have been illustrated with a breadth of power devices, ranging from LDOs to PWM controllers and converters to power modules. We've also enlisted control and monitoring devices including supply voltage supervisors and a microcontroller. Of course, these devices can be applied in combination as needed to meet the power sequencing requirements of any given system.

#### VII. ACKNOWLEDGEMENTS

The authors wish to thank Joe DiBartolomeo and Chris Thornton for their generous contributions to this work.

#### REFERENCES

- [1] Gray, Paul and Meyer, Robert Analysis and Design of Analog Integrated Circuits third edition, John Wiley & Sons, Inc., New York, 1993, Chapter 2

- [2] O'Connor, Chris and Weiss, Gary, *Looking* for Latch-up?, Test & Measurement World, pages 31-34, September 2003

- [3] XC9500 CPLD Power Sequencing, Application Note, (XAPP110) Version 1.0, February 16, 1998 Xilinx

- [4] Power Supply Sequencing Solutions for Dual Supply Voltage DSPs, (SLVA073A), Texas Instruments

- [5] Rush, Brian, *Power Supply Sequencing for Low Voltage Processors*, EDN, September 1, 2000, pp. 115-118

- [6] TMS320VC5402 Data Sheet, (SPRS079E), Texas Instruments

- [7] MPC8260EC/D (HiP3) Hardware Specification, Motorola, page 5, May 5, 2002

- [8] TMS320VC6203B Data Sheet, (SPRS086K), Texas Instruments

- [9] Power Up Behavior of ProASIC 500  $k\Omega$ Devices, Application Note, Actel

Corporation

- [10] Sequencing with TPS54x80 and TPS54x73 DC/DC Converters, (SLVA007), Texas Instruments

- [11] TPS2140 Data Sheet, Texas Instruments (SLVS399)

- [12] C.S. Mittlere, *Active Inrush Current Limiting Using MOSFETs*, Application Note, (AN1542), Motorola

- [13] Power Management Reference Guide for Xilinx<sup>®</sup>, Texas Instruments (SLPB008)

- [14] Wide Range Input TPS40051 Converter Delivers 5 V at 2 Amps, Application Note, (SLUU163), Texas Instruments

- [15] Circuit Manages Power-Up Sequencing, Martin Galinski, Micrel Semiconductor, EDN October 2002

- [16] DiBartolomeo, Joe, *Microcontroller Directs* Supply Sequencing and Control, EDN, May 29, 2003, pp. 73-74

- [17] Minimum MPC8260 PowerQUICC II System Configuration, (AN1819), Motorola.

- [18] Chris Thornton, Auto-Track<sup>TM</sup> Voltage Sequencing Simplifies Power-Up and Power-Down, Analog Applications Journal, (SLYT047A), Texas Instruments

- [19] Chris Thornton, New Power Modules Include Supply Voltage Sequencing and Margin Test Capabilities, ChipCenter's Analog Avenue September 1, 2003

- [20] TPS40051 Data Sheet, (SLUS540), Texas Instruments

## APPENDIX A LIST OF MATERIALS FOR FIG. 9.

| Reference | Count | Description                                       | Manufacturer | Part Number       |

|-----------|-------|---------------------------------------------------|--------------|-------------------|

| IC1       | 1     | LDO, 1.80 V, 1.0 A                                | TI           | TPS79618KTT       |

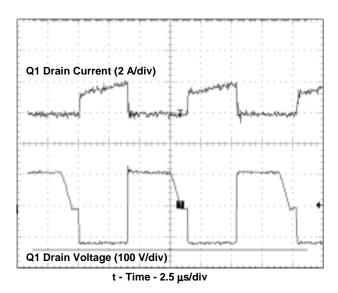

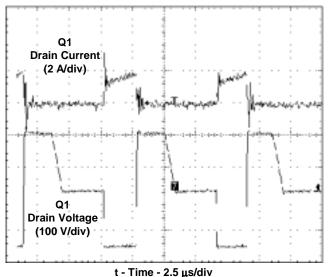

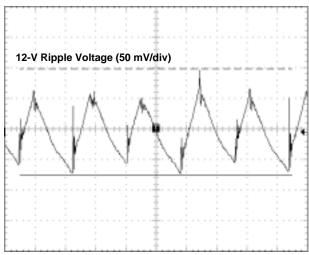

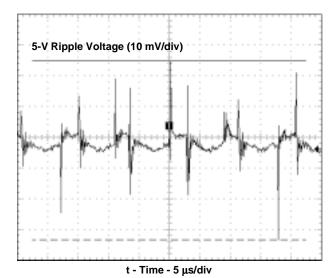

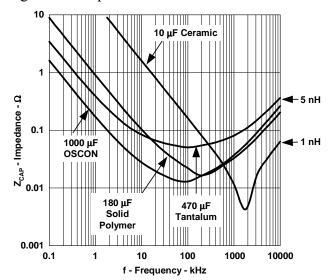

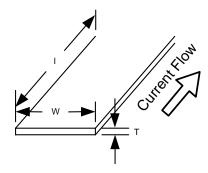

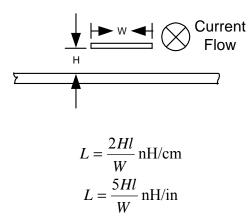

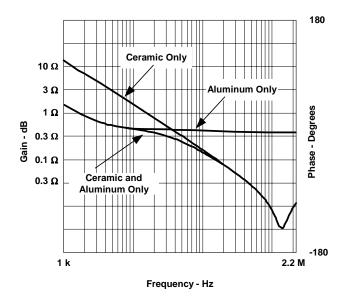

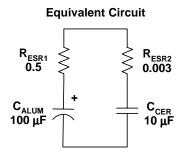

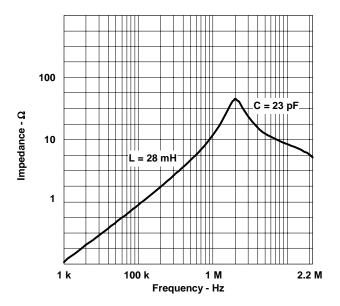

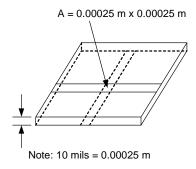

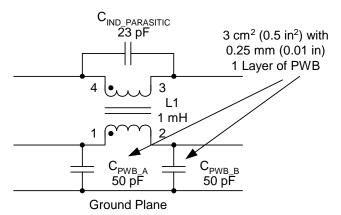

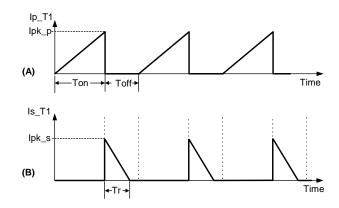

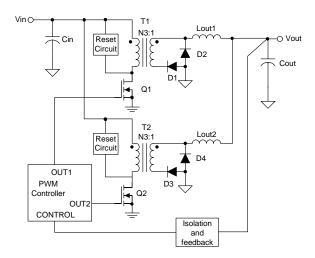

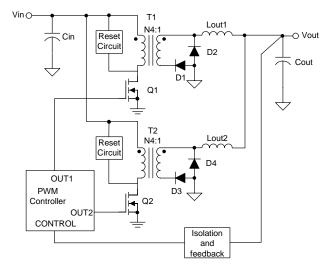

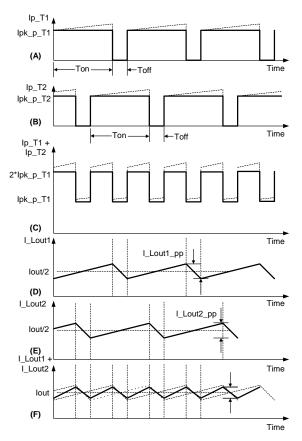

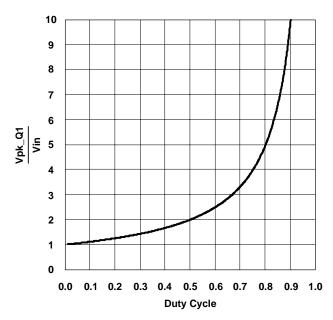

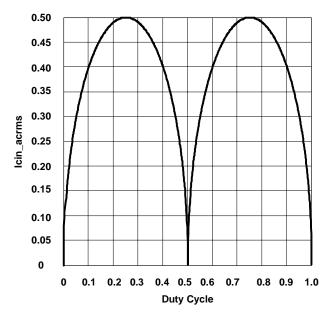

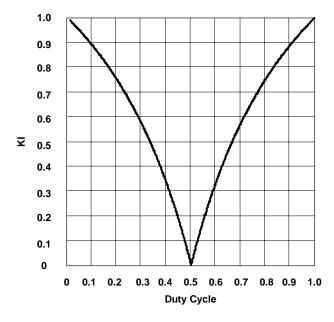

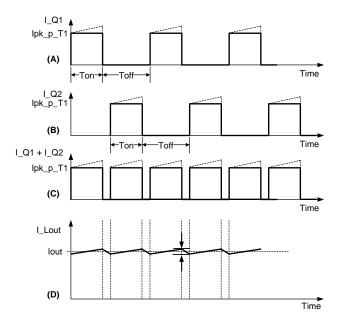

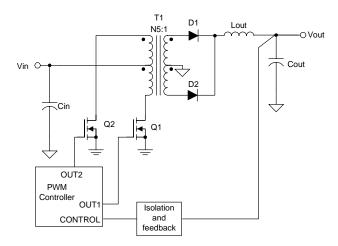

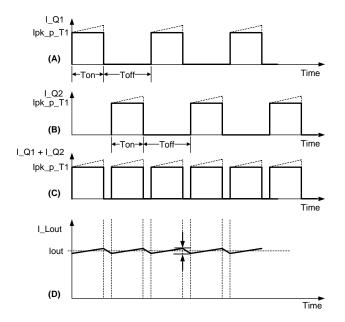

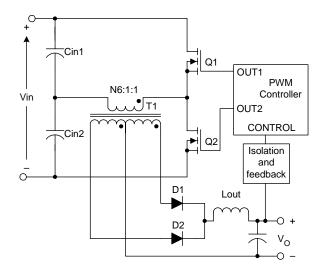

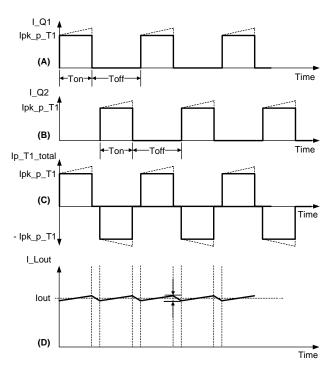

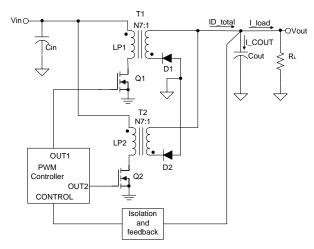

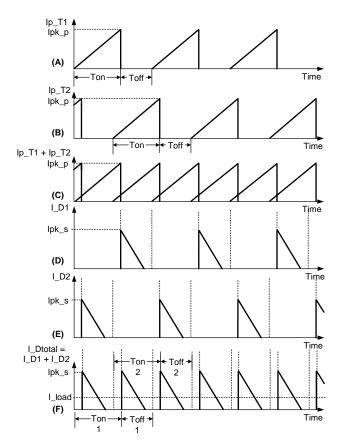

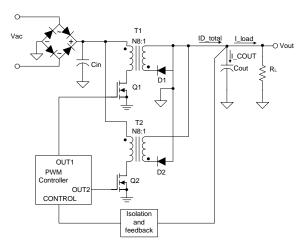

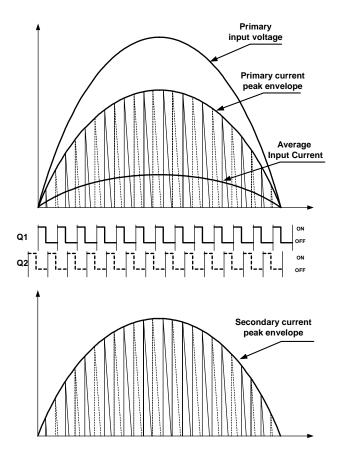

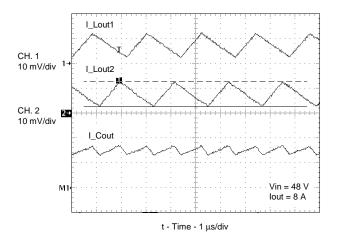

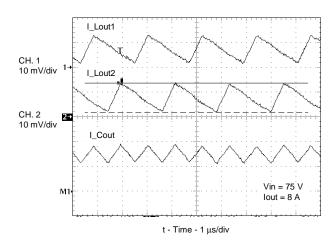

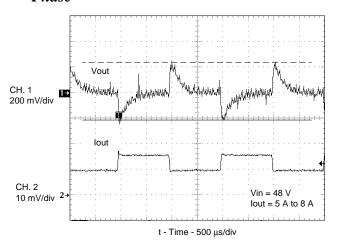

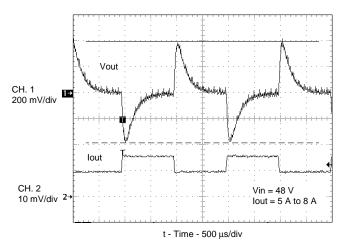

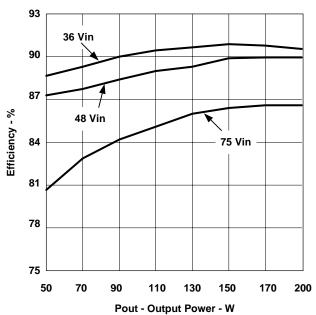

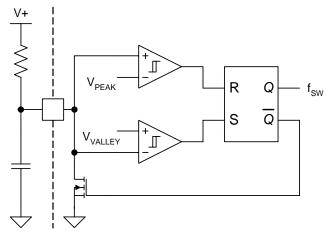

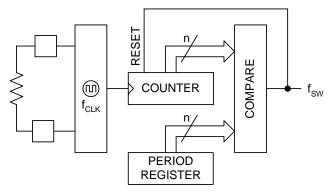

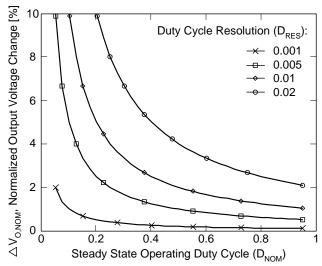

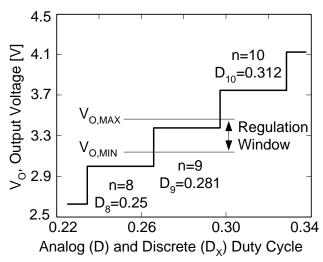

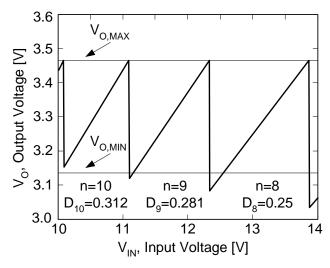

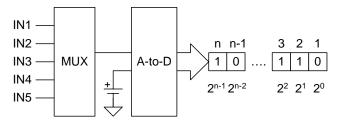

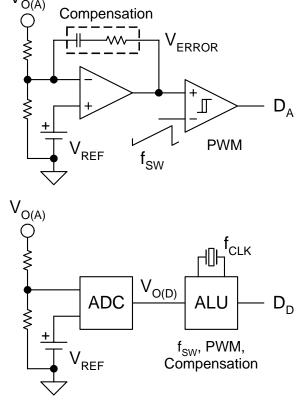

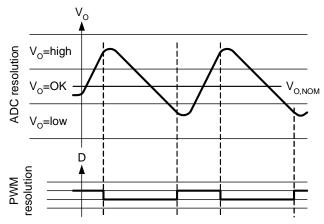

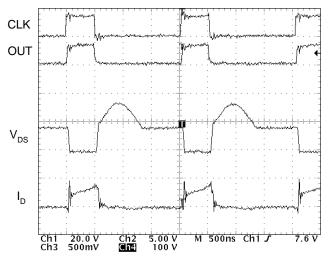

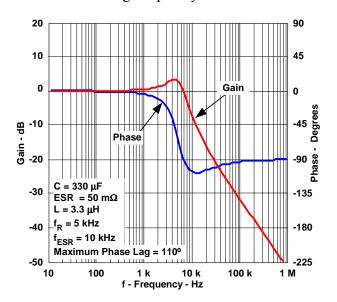

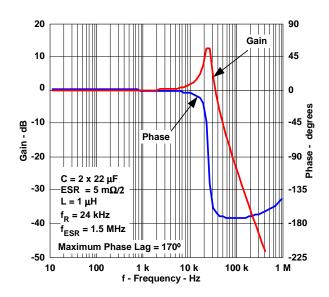

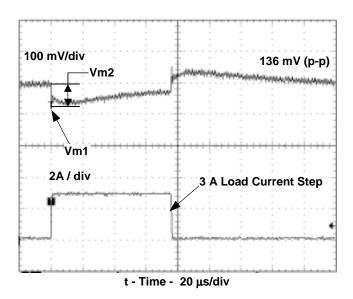

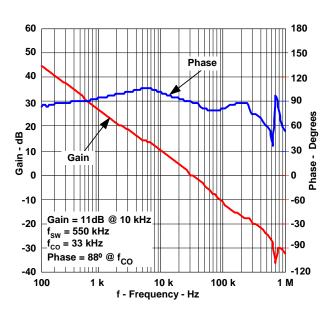

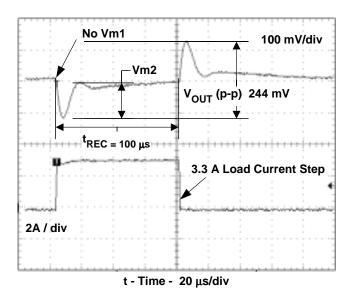

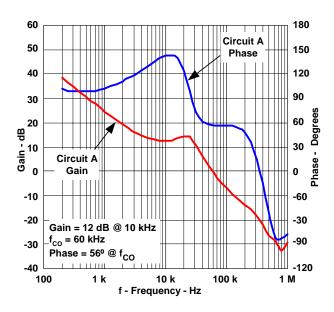

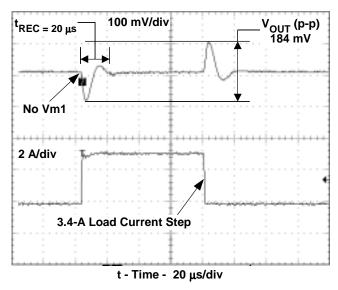

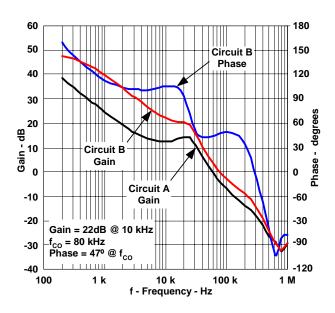

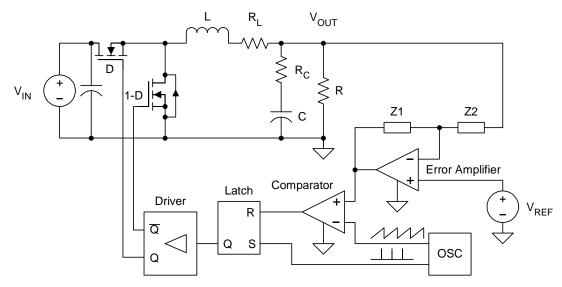

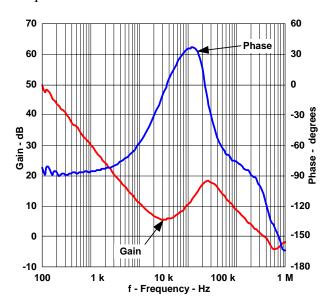

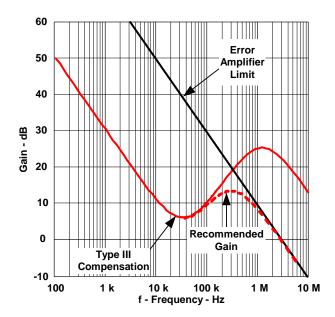

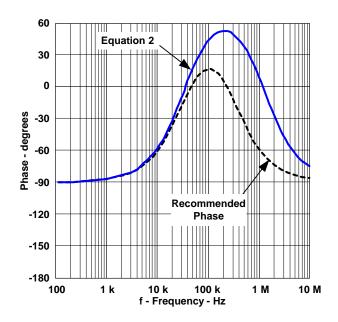

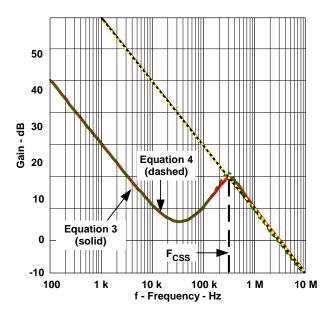

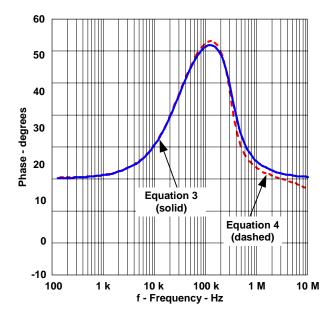

| IC2       | 1     | LDO, 3.3 V, 1.5 A                                 | TI           | TPS78633KTT       |