# Interfacing TPS57xxx-Q1,TPS65320-Q1 Family, and TPS65321-Q1 Devices With Low Impendence External Clock Drivers

Krishnamurthy Hegde, Carsten Thiele

### ABSTRACT

This application report describes methods to interface TPS57xxx-Q1, TPS65320-Q1 Family, and TPS65321-Q1 devices to an external system clock. It proposes a new AC-coupled interface circuit avoiding any DC-bias conditions on the RT/CLK pin. This document also discusses important design details and provides optimizations of existing clock-interface circuits.

#### Contents

| 1 | Introduction                                    | 2 |

|---|-------------------------------------------------|---|

| 2 | Device Operation                                | 2 |

| 3 | Existing Interface Circuits and Their Drawbacks | 2 |

| 4 | Proposed Clock Interface Circuit                | 4 |

| 5 | Measurement Results                             | 5 |

| 6 | Conclusion                                      | 8 |

### List of Figures

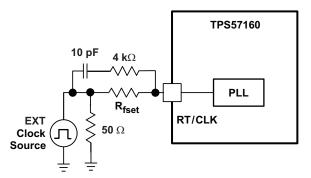

| 1  | Synchronizing to an External Clock With a 50-Ω Termination Resistor                               | 2 |

|----|---------------------------------------------------------------------------------------------------|---|

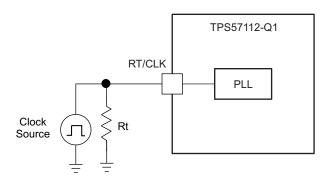

| 2  | Synchronizing to an External Clock With a High-Impedance Clock Source                             | 3 |

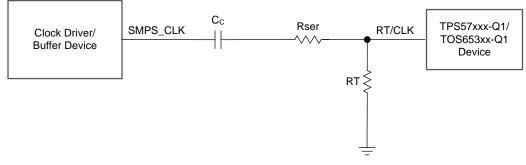

| 3  | Not Recommended - Interfacing an External Clock With an AC-Coupling Capacitor and Series Resistor | 3 |

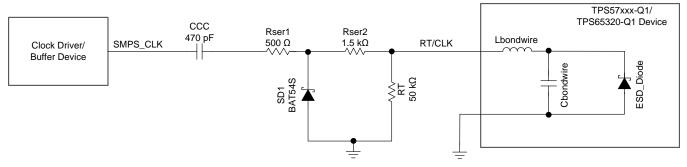

| 4  | Interfacing an External Clock With an AC-Coupling Capacitor, Series Resistor, and Schottky Diode  | 4 |

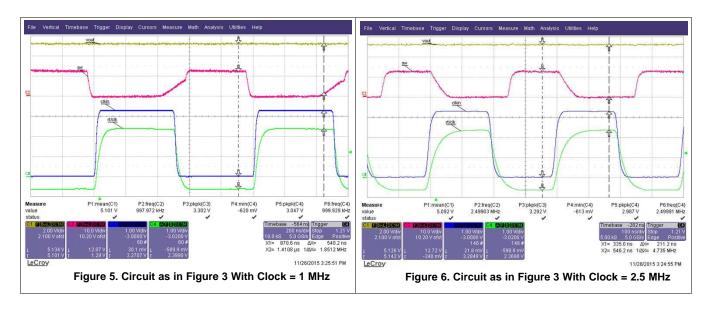

| 5  | Circuit as in Figure 3 With Clock = 1 MHz                                                         | 5 |

| 6  | Circuit as in Figure 3 With Clock = 2.5 MHz                                                       | 5 |

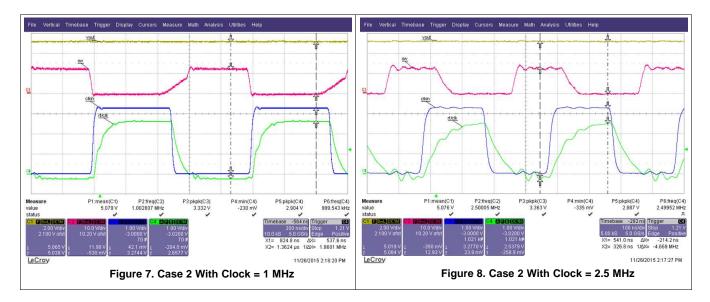

| 7  | Case 2 With Clock = 1 MHz                                                                         | 6 |

| 8  | Case 2 With Clock = 2.5 MHz                                                                       | 6 |

| 9  | Case 3 With Clock = 1 MHz                                                                         | 6 |

| 10 | Case 3 With Clock = 2.5 MHz                                                                       | 6 |

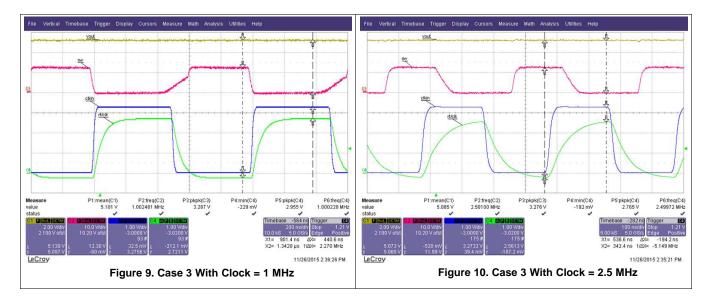

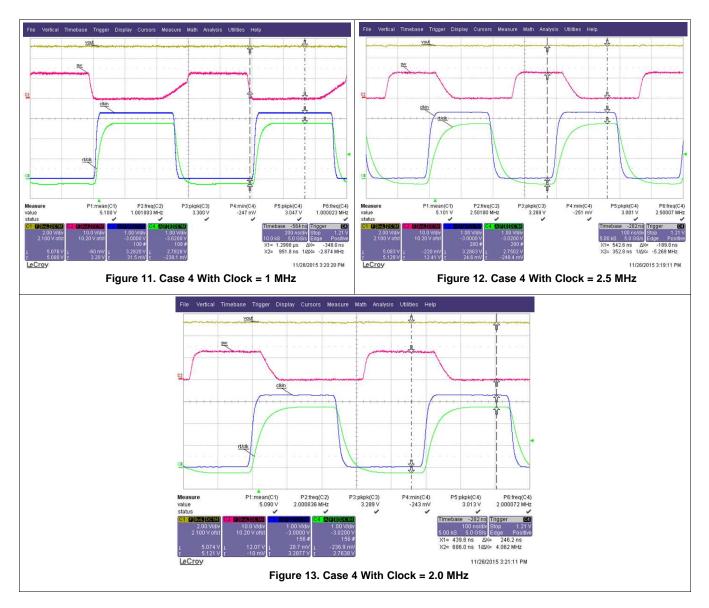

| 11 | Case 4 With Clock = 1 MHz                                                                         | 7 |

| 12 | Case 4 With Clock = 2.5 MHz                                                                       | 7 |

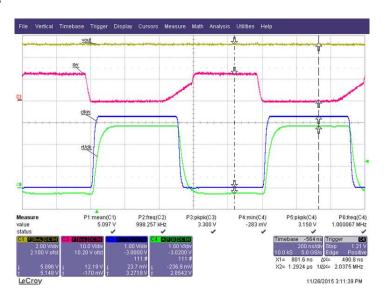

| 13 | Case 4 With Clock = 2.0 MHz                                                                       | 7 |

| 14 | Case 5 With Clock = 1.0 MHz                                                                       | 8 |

|    | List of Tables                                                                                    |   |

### 1 Measurement Results ...... 5

All trademarks are the property of their respective owners.

2

### 1 Introduction

The RT/CLK pin of TPS57xxx-Q1, TPS65320-Q1 Family, and TPS65321-Q1 devices can synchronize the regulators to an external system clock. These devices have a built-in phase-locked loop (PLL), which can track the external clock very accurately. The RT/CLK pin can also set the default or initial switching frequency. A resistor connected to GND determines the switching frequency. Different clock-interface circuits are proposed in different datasheets. This document addresses potential issues with these circuits and proposes a new clock-interface circuit, which can be used with different types of CMOS logic driver/buffer interfaces.

### 2 Device Operation

To implement the synchronization feature, apply a square wave to the RT/CLK pin. The square wave amplitude must meet the datasheet electrical specifications (VIL and VIH). The minimum on/off time and frequency specifications should be met. Design the external synchronization circuit in such a way that the device has the default-frequency set resistor connected from the RT/CLK pin to ground if the synchronization signal turns off. Also, the DC high/low signal on the RT/CLK pin during startup and shutdown could cause regulator output voltage instability.

### 3 Existing Interface Circuits and Their Drawbacks

Typically, the external clock is applied after power up of the device. With the method proposed in the TPS57160-Q1 datasheet, <u>SLVSAP1</u>, (see Figure 1) the device works fine only if the clock source has a high-output impedance or GND during startup. The initial switching frequency is determined by the RT/CLK resistance to GND according to the corresponding datasheet formulas. Usually, CMOS logic drivers/buffers are used, which may start up with low or high DC-voltage levels if no clock is applied. A high DC-voltage level will prevent startup.

Also, with this circuit, there is a possibility of degraded clock-amplitude levels at the RT/CLK pin as standard logic cannot drive the  $50-\Omega$  termination resistor. This is more suited for driving with RF-clock sources. The  $50-\Omega$  termination resistor can be changed to  $1-k\Omega$  if needed.

Bus Buffer Gates, with a 3-State Output like buffer gates, such as SN74LVC1G125-Q1, SN74LVC1G125A-Q1, SN74LVC1G126-Q1, and SN74LVC1G126A-Q1 can be used. These devices ensure a high-impedance state during power up or power down when OE is tied to  $V_{CC}$  through a pullup resistor.

The method proposed in the TPS57112-Q1 datasheet, <u>SLVSAL8</u>, (see Figure 2) can also be used with the above buffer-gate logic or guaranteed High-Z driver stage during startup, but it is recommended to use the Figure 1 circuit as a 4-k $\Omega$  series resistor helps in reducing the phase jitter in heavy load applications when synchronizing to an external clock and when transitioning from EXTERNAL CLOCK mode to RT/CLK mode.

Figure 1. Synchronizing to an External Clock With a 50- $\Omega$  Termination Resistor

### Figure 2. Synchronizing to an External Clock With a High-Impedance Clock Source

An AC-coupling to the external-clock driver is necessary to avoid any DC-bias conditions on the RT/CLK pin. The example circuit in Figure 3 is not recommended. Due to the AC-coupling effect, +Vclk/2 and -Vclk/2 are generated on the device side and the negative side (-Vclk/2) gets clamped due to the device internal-ESD clamping-diode structure. Therefore, at the device pin, around -0.6 V is seen, which is a violation of the datasheet absolute maximum rating specification of -0.3 V on this pin. This injects as well current/energy through the internal-ESD clamping-diode structure present on the RT/SYNC pin, which might be tolerable if  $C_c$  is small enough and Rser is used to limit the current. But the allowed current is not specified in the datasheet, thus there is no assurance of this.

Figure 3. Not Recommended - Interfacing an External Clock With an AC-Coupling Capacitor and Series Resistor

### Proposed Clock Interface Circuit

### 4 **Proposed Clock Interface Circuit**

Figure 3 is modified by splitting the series resistor and adding a Schottky diode as shown in Figure 4, so a negative voltage below -0.3 V at RT/CLK pin can be avoided. A very-low forward voltage (less than 0.3 V) and a fast-switching Schottky diode must be used. Resistor Rser1 (500  $\Omega$ ) limits current through this diode and Rser2 (1.5 K $\Omega$ ) ensures that the internal ESD diode will not conduct as it offers a higher resistance compared to the external Schottky diode. Additionally, Rser2 makes a low-pass filter with the RT/CLK-pin parasitic capacitance and during transient conditions the external Schottky diode conducts before the internal ESD diode. The Schottky diode also shifts the RT/CLK voltage level by around 0.2 V, which helps achieve the VIH level quickly.

# Figure 4. Interfacing an External Clock With an AC-Coupling Capacitor, Series Resistor, and Schottky Diode

A very-low forward-voltage Schottky with low-leakage current and fast-transient response must be used. A Schottky diode with large forward-voltage drop may not solve the issue of a negative voltage of -0.3 V at the RT/CLK pin and a Schottky diode with higher-leakage current may impact the startup behavior with INTERNAL CLOCK mode. The BAT54 diode has been verified in the lab and is found to work fine for the test conditions. A BAS40 diode may be slightly better as it has a lower-leakage current compared to the BAT54 device.

### 5 Measurement Results

The TPS57160EVM was used to perform the measurements in the lab to verify the functionality of the circuits in Figure 3 and Figure 4. Though the testing is done only on the TPS57160-Q1 device, these results can be applied to other TPS57xxx-Q1, TPS65320-Q1, and TPS65321-Q1 devices, because the clock interface is similar for these devices. See for the tests and corresponding waveforms.

| TEST                                                                                                                                                                                         | COMPONENTS                                                                                                 | FIGURE<br>REFERENCES                   | RESULTS                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------|

| Case 1: Show the effect of AC coupling without the external Schottky diode (as in Figure 3).                                                                                                 | No Schottky diode, CCC = 470 pF,<br>Rser1 = 1.5 k $\Omega$ , and RT = 120 k $\Omega$                       | Figure 5 and Figure 6                  | Voltage at RT/CLK pin is around –0.6 V.                                                             |

| Case 2: Show results for two different clock frequencies. Schottky diode, $RT = 50 \text{ k}\Omega$ , $CCC = 470 \text{ pF}$ , $Rser1 = 1 \text{ k}\Omega$ , and $Rser2 = 3 \text{ k}\Omega$ |                                                                                                            | Figure 7 and Figure 8                  | This circuit has poor amplitude levels at the RT/CLK pin.                                           |

| Case 3: Show the results for three different clock frequencies.                                                                                                                              | Schottky diode, RT = 50 k $\Omega$ ,<br>CCC = 1 nF, Rser1 = 1 k $\Omega$ , and Rser2<br>= 3 k $\Omega$     | Figure 9 and Figure 10                 | This circuit has poor amplitude levels at the RT/CLK pin                                            |

| Case 4: Show the results for three different clock frequencies.                                                                                                                              | Schottky diode, RT = 50 k $\Omega$ ,<br>CCC = 470 pF, Rser1 = 500 $\Omega$ , and<br>Rser2 = 1.5 k $\Omega$ | Figure 11, Figure 12,<br>and Figure 13 | This circuit has good results and is the proposed new circuit.                                      |

| Case 5: Shows the results using a higher value of CCC.                                                                                                                                       | Schottky diode, RT = 50 k $\Omega$ ,<br>CCC = 1 nF, Rser1 = 500 $\Omega$ , and<br>Rser2 = 1.5 k $\Omega$   | Figure 14                              | Shows the results with and this shows a slightly higher-clamp voltage due to a higher value of CCC. |

### **Table 1. Measurement Results**

# 5.1 Case 1 Test Results

Measurement Results

# 5.2 Case 2 Results

# 5.3 Case 3 Results

### 5.4 Case 4 Results

### 5.5 Case 5 Results

Figure 14. Case 5 With Clock = 1.0 MHz

### 6 Conclusion

8

Based on the measurement results, using an external Schottky diode and current limiting resistors (Figure 4), the RT/CLK pin can be interfaced to external clock sources, which are not high impedance during start up and shutdown. Results shown are based on one measurement taken on one device at room temperature. Customers need to take measurements on their board and adjust the external components accordingly to avoid the violation of datasheet specifications, as results may vary depending on the external components and also on PCB parasitics. A very-low forward-voltage Schottky with low-leakage current and fast-transient response must be used and place this diode close to the clock source for better performance.

### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ctivity                       |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2015, Texas Instruments Incorporated