# TI Designs: TIDA-01458 Low-Noise, Fixed Drop-Out, ±2.5- to ±12-V<sub>OUT</sub>, 3-A Power Supply Reference Design for Ultrasound CW Pulser

# Texas Instruments

# Description

This reference design allows a digitally programmable power supply to power an ultrasound transmit circuit for continuous wave (CW) mode from a 24-V bus. There are two outputs adjustable from ±2.5 to ±12 V under user software control. These outputs can provide up to 2 A with very low ripple and noise on both positive and negative regulator outputs. The power supply is scalable for higher output currents up to 3 A by adding more regulators in parallel. The power supplies can also be synchronized to an external clock.

### Resources

| TIDA-01458 | Design Folder  |

|------------|----------------|

| TIDA-01352 | Design Folder  |

| LMR14050   | Product Folder |

| LM73605    | Product Folder |

| TPS7A47    | Product Folder |

| TPS7A33    | Product Folder |

| TLV2171    | Product Folder |

| TL431A     | Product Folder |

|            |                |

# Features

- Separate and Independent Positive and Negative Voltage Power Supplies for CW Mode in Ultrasonic Pulsar

- Comprises Two High-Performance Buck Regulators for Creating Adjustable Outputs

- To Reduce Ripple at Outputs High Performance, Low Noise LDOs are Operated as Power Filters to Obtain Lowest Ripple With Minimum Heat Dissipation in LDO (< 100 µV at 1.6-A Load)</li>

- Adaptive Drop on LDO, Special Circuit Keeps LDO Output Always 1 V Below LDO Input

- Reduces Power Dissipation in LDO

- Capable of Switching Frequency Synchronization With Ultrasound Master or System Clock Frequency

- Helps in Better Harmonics Rejection

- Modular Design Allowing More Regulator Blocks to be Added

### Applications

- Medical Ultrasound Scanners

- Sonar Imaging Equipment

- Nondestructive Evaluation Equipment

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

#### 1 System Description

This design guide describes a power supply for continuous wave (CW) mode. These typically need  $\pm 2.5$  to  $\pm 12$  V under software control. Budget a current delivery up to 3 A at outputs of DC-DC converters. In addition, the power supplies must have a very low level of ripple and noise at the output voltage.

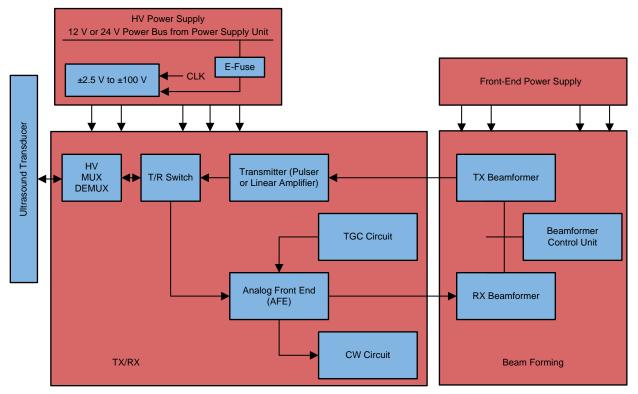

# 1.1 Basic Ultrasound System

In an ultrasound system, the transmitter that generates high-voltage signals to excite a transducer is one of the most critical components in the entire ultrasonic diagnostic system. There are semiconductor devices available that can generate high-voltage signals to ensure the penetration depth of ultrasonic signals. A generic system-level block diagram for a cart-based ultrasound scanner is shown in Figure 1.

Figure 1. System-Level Block Diagram for Cart-Based Ultrasound Scanners

The high-voltage pulses (to be transmitted inside human body to get information about blood, organs, tissues, and so on) are bipolar in nature and are transmitted by transmitters (TXs). There are two modes in general:

- 1. Pulse (also known as brightness, or B) mode where high-voltage pulses (-100 V and 100 V, typically) are transmitted for a particular short time only.

- 2. CW mode where low-voltage (±2.5 to ±10 V, typically) pulses are continuously transmitted.

# 1.2 Key System Specifications

Table 1 shows the key system specifications.

| Table 1. | Key | System | Specifications |

|----------|-----|--------|----------------|

|----------|-----|--------|----------------|

| PARAMETER                                       | SPECIFICATIONS                   |

|-------------------------------------------------|----------------------------------|

| Input voltage (V <sub>IN</sub> )                | 24 V ±10%                        |

| V <sub>BUCK</sub> positive output voltage range | 2.5 to 12 V                      |

| Load current capacity positive buck             | 3 A                              |

| V <sub>BUCK</sub> negative output voltage range | -2.5 to -12 V                    |

| Load current capacity negative buck             | 3 A                              |

| LDO $(V_{IN} - V_O)$ drop across the LDO        | 1 V (adjustable through pre-set) |

| External clock synchronization                  | Yes                              |

| External sync frequency                         | 400 kHz                          |

| LDO output current capacity                     | 2 x 1 A positive                 |

| LDO output current capacity                     | 2 × 1 A negative                 |

| Scalability                                     | Yes                              |

TEXAS INSTRUMENTS

www.ti.com

System Overview

#### 2 System Overview

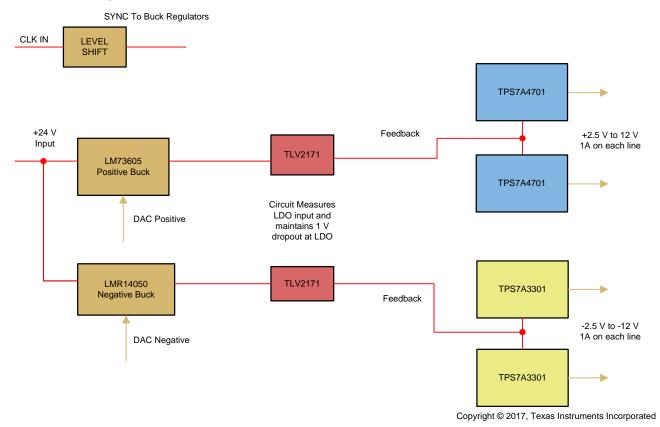

#### 2.1 Block Diagram

Figure 2. System Block Diagram

### **Positive Regulator Block**

This reference design uses the LM73605 DC-DC converter as a synchronous buck regulator. The output is varied by changing the feedback factor of the regulator in response to a DC control voltage the output can vary from 2.5 to 12 V and the device can deliver load currents up to 5 A. To eliminate the ripple on the buck, the TPS7A4701 low-noise LDO is used as a power filter. The voltage drop (Vin-Vo) across the LDO is kept at 1 V. This drop is above the dropout of the regulator and thus the LDO can have low power dissipation as well as good PSRR performance. This drop across the LDO is maintained for all output voltage settings of the buck. This is done by an op amp feedforward circuit that monitors the DC voltage at the input of the LDO and adjusts the feedback pin of the LDO to keep a fixed Vin-Vo across the regulator.

#### **Negative Regulator Block**

This reference design uses the LMR14050 DC-DC converter setup as an inverting regulator. The output is varied by changing the feedback factor of the regulator in response to a DC control voltage. The output can vary from -2.5 to -12 V and the device can deliver load currents up to 3 A. To eliminate the ripple on the buck, the TPS7A3301 low-noise LDO is used as a power filter. The voltage drop (Vin-Vo) across the LDO is kept at 1 V. This drop is above the dropout of the regulator and thus the LDO can have low power dissipation as well as good PSRR performance. This drop across the LDO is maintained for all output voltage settings of the buck. This is done by an op amp feedforward circuit that monitors the DC voltage at the input of the LDO and adjusts the feedback pin of the LDO to keep a fixed Vin-Vo across the regulator.

The system is modular. More DC-DC converter sections that are identical to the ones demonstrated can be added to increase output current capacity. All sections are driven with the same DC control waveform as well as the sync waveform.

Presets in the board can adjust the dropout to values other than 1 V by the designer.

#### 2.2 Highlighted Products

#### 2.2.1 LM73605

The LM73605 device is a synchronous step-down DC-DC converter capable of driving 5 A from a supply voltage from 3.5- to 36-V DC. It has high efficiency and a high-output accuracy in a small solution size. Peak current mode control is employed. The device has an adjustable frequency and also allows frequency synchronization.

#### 2.2.2 LMR14050

The LMR14050 device is an integrated 40-V, 5-A step-down regulator with an integrated switching FET. The device has an ultra-low quiescent current of 1  $\mu$ A in sleep mode. It has an adjustable switching frequency range and internal loop compensation .It also has cycle-by-cycle current limit, thermal sensing, and shutdown.

### 2.2.3 TPS7A4701

The TPS7A4701 device is a positive voltage (36 V), ultra-low-noise (4  $\mu$ V<sub>RMS</sub>) low-dropout linear regulator (LDO) capable of sourcing a 1-A load.

#### 2.2.4 TPS7A3301

The TPS7A3301 device is a negative voltage (–36 V), ultra-low-noise (16- $\mu$ V<sub>RMS</sub>, 72-dB PSRR) linear regulator capable of sourcing a maximum load of 1 A.

#### 2.2.5 TLV2171

The 36-V TLV2171 device provides a low-power option for cost-conscious industrial and personal electronics systems requiring an electromagnetic interference (EMI)-hardened, low-noise, single-supply operational amplifier (op amp) that operates on supplies ranging from 2.7 V (±1.35 V) to 36 V (±18 V).

System Overview

# 2.3 System Design Theory

This section explains the design theory and equations for each of the devices used in this reference design.

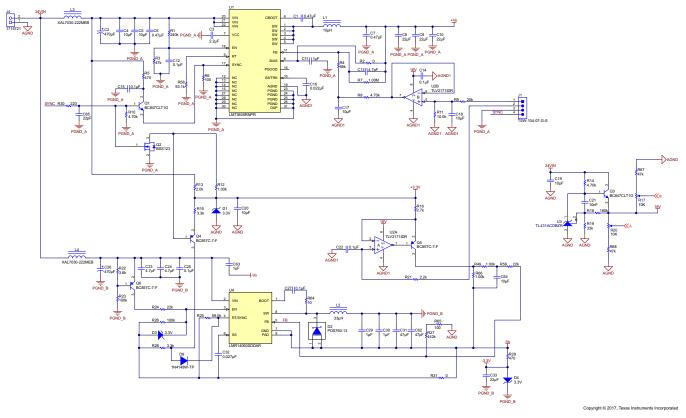

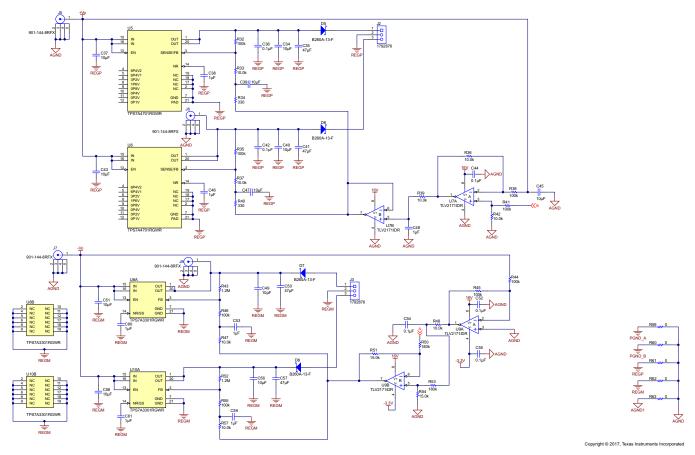

Figure 3. DC-DC Converters Schematic

(3)

#### 2.3.1 Positive Switching Regulators

The LM73605 (U1) is a synchronous buck regulator that can drive 5 A of current. The output voltage is typically set up by R7 and R4. The feedback pin is normally regulated to 1 V. A DC control voltage between 0 and 3.3 V applied to Pin 1 of J1 is used to modify the output of the buck regulator from 2.5 to 15 V. This voltage is applied to U2B. This is an op amp buffer and its output is connected to a low-pass filter comprising of R8 and C17. The low-pass filter ensures that a pure DC voltage is applied to the feedback pin. Assume that the control voltage on Pin 1 of J1 is 0 V. The output of op amp U2B is also 0 V.

$$V_{O} = \frac{R4}{(R7 + R4)} = 1 V$$

$$V_{O} = \frac{1 V (1M + 68 k)}{68 k} = 15.7 \text{-V maximum output voltage}$$

(1)

Assume now that 3-V DC is applied on Pin 1 of J1. The output of the op amp is now 1-V DC. Applying the superposition theorem on the feedback pin:

$$\frac{V_{O} \times R4}{(R7 + R4)} + \frac{1 \, V \times R7}{(R7 + R4)} = 1 \, V$$

$$\frac{V_{O} \times 68k}{(1M + 68k)} + \frac{1 \, V \times 1 \, M}{(1M + 68k)} = 1 \, V$$

(2)

Therefore, for a DAC control range of 0 3 V, the output voltage varies from 1 to 15.7 V.

$$V_O = 15.7 - 15 \times V_{CON}$$

This is an approximate equation describing the behavior given the resistors placed R58 on pin 9 of U1 sets the operating frequency of the DC-DC converter.

System Overview

www.ti.com

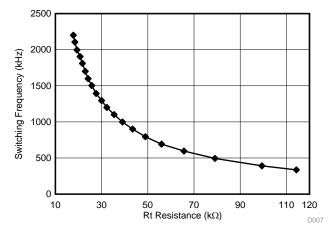

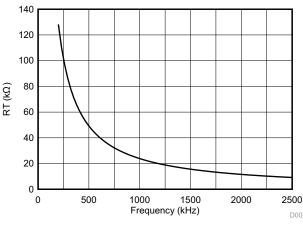

Figure 4 shows that a frequency of 400k is set for a 93k resistor. Transistor Q1 is set up as a buffer and is used to couple the sync signal to the sync pin. With no sync input, the sync pin is ground with a 10k resistor.

Figure 4. R<sub>T</sub> Resistance versus Frequency

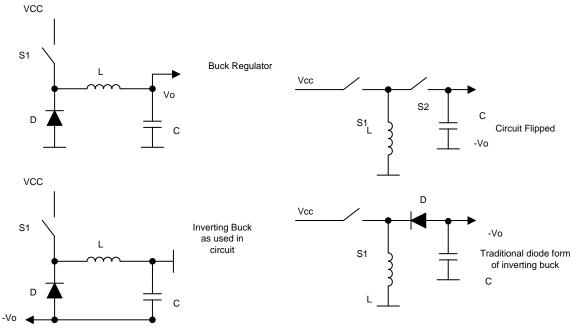

U4 (LMR14050) is a 5-A non-synchronous buck regulator. This regulator is set up as an inverting regulator. As shown in Figure 5, to set up a buck regulator in inverting mode, the bottom of S2 is connected as a negative output. The output end of the inductor L is grounded. The circuit now looks like a traditional negative regulator.

# Figure 5. Basic Functionality of Negative Switching Regulators

Note that the maximum voltage that the device sees is as calculated using Equation 4:

$V_{\text{STRESS}} = (V_{\text{IN}} + V_{\text{OMAX}})$

8

(4)

For  $V_{IN} = 24$  v and  $V_O = -15$  V, the device sees 39 V, which is very close to the absolute maximum rating of the device. Therefore, a maximum of -12 V can be kept at the output.

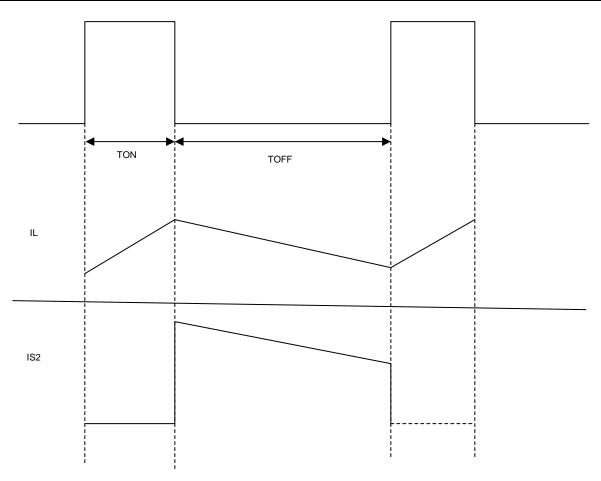

Regarding Figure 6, assume TON is the time S1 conducts and TOFF is the time S2 conducts.  $V \times TON = |V_O| \times TOFF$

$$\left| \mathsf{V}_{\mathsf{O}} \right| = \frac{\mathsf{V} \times \mathsf{D}}{(\mathsf{1} - \mathsf{D})}$$

Note that  $I_0$  = Average of IS2.

$$I_{O} = \frac{I_{MAX} \times TOFF}{T}$$

$$I_{O} = I_{MAX} \times (1 - D)$$

(6)

Therefore, if  $V_0 = -15$  V, D = 0.36,  $I_0$  maximum = 3 A for a 5-A buck switcher. Resistors R27 and R56 are used to set the output voltage. The LMR14050 has a feedback voltage of 0.75 V.

$$\frac{V_{O} \times R56}{(R27 + R56)} = 0.75 \text{ V}$$

$$\frac{V_{O} \times 22 \text{ k}}{(22\text{ k} + 442 \text{ k})} = 0.75$$

$$V_{O} = -15 \text{ V}$$

(7)

To adjust the negative output, apply a DC control voltage between 0 and 3 V to Pin 2 of J1.

9

(5)

System Overview

www.ti.com

The collector of Q5 adds a voltage to the feedback pin of the LMR14050. When this voltage from the feedback pin to the device ground equals 0.75 V, the output of the negative converter drops to zero. The 0.75 V is obtained through the op amp current source. When the DC voltage applied to pin 3, U2A is 0 V. The current in Q5 = 3.3/R16 or 3.3/3K3 = 1 mA. R66 × 1 mA = 1 V. This is more than the 0.75 V needed to bring the output voltage to zero.

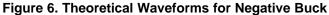

Figure 7. R<sub>T</sub> versus Frequency

| Table 2. | Typical | Frequency | Setting | R <sub>T</sub> Resistance |

|----------|---------|-----------|---------|---------------------------|

|----------|---------|-----------|---------|---------------------------|

| f <sub>sw</sub> (kHz) | R <sub>τ</sub> (kΩ) |

|-----------------------|---------------------|

| 200                   | 127.0               |

| 350                   | 71.5                |

| 500                   | 49.9                |

| 750                   | 32.4                |

| 1000                  | 23.7                |

| 1500                  | 15.8                |

| 2000                  | 11.5                |

| 2200                  | 10.5                |

This is an approximate equation describing the behavior given the resistors placed R25 is used to set the oscillator frequency at 400k.

Transistor Q4 is used to couple the sync signals to the  $R_T$  pin. When there is no sync signal, the transistor is cut off. The Enable pin is driven by transistor Q6. This transistor acts as a level shifter as the Enable pin is referenced to  $-V_0$ . Resistors R22 and R23 act as a voltage divider and at a minimum supply voltage turn the PNP transistor on

$$\frac{V_{MIN} \times R22}{(R22 + R23)} = 0.65 \text{ V}$$

$$V_{MIN} = \frac{0.65 \times 103.6 \text{ k}}{3.6 \text{ k}} = 18 \text{ V}$$

(8)

#### 2.3.2 Linear Regulators

Figure 8. Linear Regulators Schematic

The LDO section filters out the ripple content in the switching regulators and leaves a very ripple-free and low-noise output to feed the CW power. It relies on the fact that a linear regulator is an active filter and can reduce the ripple seen at its input due to its excellent PSRR performance. For this to work well, the LDO must be in the active region well beyond the dropout; however, operating a regulator in the active region results in power dissipation [I × ( $V_{IN} - V_{O}$ )]. Therefore, to prevent dissipation, it is best to run the regulator just outside its minimum dropout. Because the input voltage of the regulator varies as it is set by software, the hardware circuitry on the board continuously monitors the input voltage, removes the ripple, and adjusts the feedback voltage so that the output voltage is always 1 V lower than input whatever input is present.

System Overview

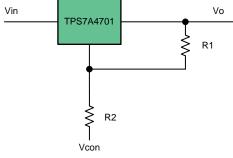

Figure 9 shows a positive LDO with a control voltage applied to R2.

Copyright © 2017, Texas Instruments Incorporated

#### Figure 9. Positive LDO Controlled Using V<sub>CON</sub>

Case 1: When  $V_{CON} = 0$  V, let the maximum output voltage be 15 V ( $V_{FBK} = 1.4$  V).  $\frac{V_{OMAX} \times R2}{(R1 + R2)} = 1.4 \text{ V}$ (9)  $V_{OMAX} = \frac{1.4 \times 110 \text{ k}}{10 \text{ k}} = 15 \text{ V}$ Case 2: With  $V_{CON}$  applied with R1 = 100K, R2 = 10K:  $\frac{V_{O} \times R2}{(R1+R2)} + \frac{V_{CON} \times R1}{(R1+R2)}$  $\frac{V_O}{11} + \frac{V_{CON} \times 10}{11} = 1.4 \ V$  $V_O~+~V_{CON}\times10=15.4~V$ (10)Assume  $V_0 = V_{IN} - 1$  and apply in Equation 11:  $V_{IN} - 1 + V_{CON} \times 10 = 15.4$ (11) $V_{CON} = \frac{\left(16.4 - V_{IN}\right)}{10}$

Equation 11 can be implemented in a differential amplifier: one input is a DC voltage of 16.4 V, the other being the regulator input voltage. The differential amp is set up with a gain of 1/10. In the schematic, U7A is the differential amplifier. R36, R38, R41, and R42 set up a differential gain of 1/10. R39 and C48 form a low-pass filter that removes any ripple on this line and leaves a DC equal to the average value of voltage at the input. U7B is a buffer and the output of this drives the feedback pin. This system is a feedforward system and must not face any stability issues.

For example: If  $V_{IN} = 10$  V, then the differential amplifier output  $V_{CON} = (16.4 - 10)/10 = 0.64$  V. Now:

- $V_0 + 0.64 \times 10 = 15.4$

- $V_0 = 15.4 6.4 = 9 V$

- $V_0 V_{IN} = 1 V$

(13)

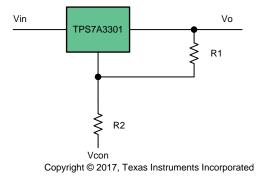

Figure 10 assumes a negative LDO with a control voltage applied to R2.

# Figure 10. Negative LDO Controlled Using $V_{\mbox{\scriptsize CON}}$

Case 1: When  $V_{\text{CON}}$  = 0, let the maximum output voltage be –15 V,  $V_{\text{FB}}$  = –1.13 V.

$$\frac{V_{OMAX} \times R2}{(R1 + R2)} = -1.13 \text{ V}$$

$$V_{OMAX} = \frac{-1.13 \times 1.3M}{100k}$$

Case 2: With V<sub>CON</sub> applied and with R1 = 1200k, R2 = 110k:

$$\frac{V_O \times R2}{(R1 + R2)} + \frac{V_{CON} \times R1}{(R1 + R2)} = -1.13 \text{ V}$$

$$\frac{V_O \times 110k}{(1.2M + 110k)} + \frac{V_{CON} \times 1.2M}{(1.2M + 110k)} = -1.13 \text{ V}$$

$$V_O + V_{CON} \times 10.9 = -13.45 \text{ V}$$

(12)

Assume V\_O = V\_{IN} + 1 and apply in Equation 13:

$$V_{IN} + 1 + V_{CON} \times 10.9 = -13.45$$

$$V_{CON} = \frac{(-14.45 - V_{IN})}{10.9}$$

(13)

Texas Instruments

System Overview

www.ti.com

Equation 13 can be implemented in a differential amplifier: one input is a DC voltage of 15.7 V, the other being the regulator input voltage. U9A is a differential amplifier with a gain of -1. This converts the negative input voltage to a positive output level. U9B is a differential amplifier with a gain 1/10.9 that compares the positive output voltage seen on U9A with a fixed DC voltage of -14.45 V. For example: If the V<sub>IN</sub> of the regulator is -10 V, pin 1 of U9A would be 10 V as U9A is an inverting amplifier with a gain of 1. The output of U9B that is a differential amplifier with an attenuation of 1/12 would be as follows:

• From Equation 13:

$$V_{CON} = \frac{-(14.45 - (-10))}{10.9} = -0.408 \text{ V}$$

• From Equation 12:

$\begin{array}{l} V_{O} \,+\, V_{CON} \times 10.9 = -\,13.45 \ V \\ V_{O} \,-\,0.475 \times 10.9 = -\,13.45 \ V \\ V_{O} \,= -\,9 \ V \end{array}$

This is  $V_{IN}$  + 1. The drop across the LDO is 1 V. Therefore, the drop across the differential amplifier needs to be -0.4 V. The differential amplifier implements

$$\frac{(10-14.45)}{10.9} = -0.4 \text{ V}$$

$$V_0 = 14.69 - 0.475 \times 12 = -9 \text{ V}$$

(14)

R47 and C53 form a low-pass filter that removes any ripple present on the input of the LDO. ORing diodes D5, D6, D7, and D8 are used to connect the output with the high-voltage supply. The diodes would block the high voltages from reaching the regulators. The control loop is common to all the LDOs, and it is possible to place many LDOs on the same control loop to share the currents.

# 3 Hardware, Testing Requirements, and Test Results

# 3.1 Required Hardware

| REFERENCE | DESCRIPTION                   | PINOUT                                                                   |

|-----------|-------------------------------|--------------------------------------------------------------------------|

| J4        | 24-V input                    | 24-V<br>GNDA                                                             |

| J1        | V <sub>CON</sub> + Sync       | V <sub>CON</sub> positive<br>V <sub>CON</sub> negative<br>Sync<br>PGND_A |

| J2        | Positive regulator output     | Out_1<br>Reg_P<br>Out_2                                                  |

| J3        | Negative regulator output     | out_1B<br>Reg_M<br>Out_2B                                                |

| J5        | +V <sub>o</sub> SMA           | +V <sub>o</sub>                                                          |

| J7        | –V <sub>o</sub> SMA           | -V <sub>0</sub>                                                          |

| J6        | SMA regulator positive output | —                                                                        |

| J8        | SMA regulator positive output | _                                                                        |

# Table 3. Connectors, Fuses, and Test Points on Board

# 3.1.1 TIDA-01458 Board Images

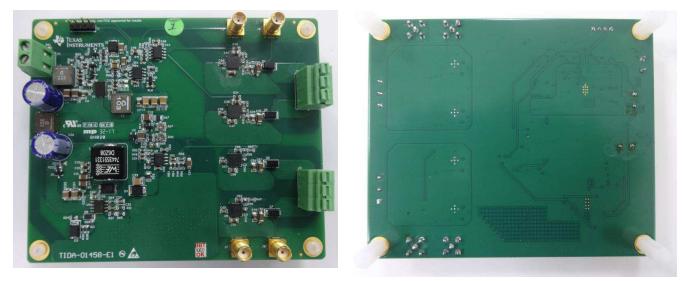

Figure 11 and Figure 12 show the top and bottom views of TIDA-01358 PCB, respectively.

Figure 11. Top View

Figure 12. Bottom View

#### 3.2 Testing and Results

To test the board, use the following equipment:

- 24-V DC input supply rated at 5 A

- 5-V variable DC source to provide a control signal to adjust the output voltages

- $15-\Omega$  power resistors as well as an electronic load is also needed

- 5-V pulses frequency source capable of generating frequencies from 300 to 500 kHz

- Oscilloscope (100 MHz)

- Spectrum analyzer

- Thermal camera

# 3.2.1 Test 1: Output Voltages as a Function of Control Voltage-Negative Power Supply

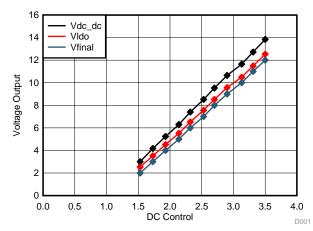

A load of 0.8 A is put on the output of the LDO, and the output voltage is observed as a function of DC control voltage.

Figure 13. Output Voltage as Function of DC Control-Negative

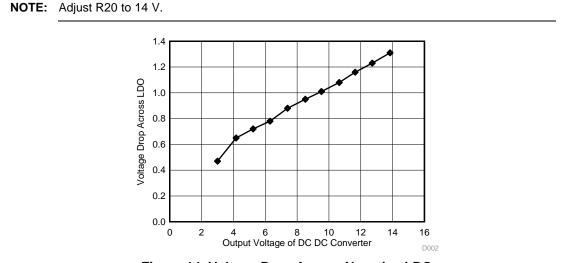

### 3.2.2 Test 2: Voltage Drop Across Negative LDO as a Function of Control Voltage

A load of 0.8 A is put on the output of the LDO, and the voltage drop across the LDO is observed for varying DC-DC converter outputs.

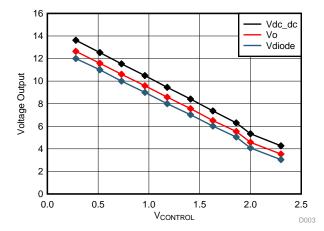

# 3.2.3 Test 3: Output Voltages as a Function of Control Voltage-Positive Power Supply

A load of 0.8 A is put on the output of the LDO, and the output voltage is observed as a function of DC control voltage.

Figure 15. Output Voltage as Function of DC Control-Positive

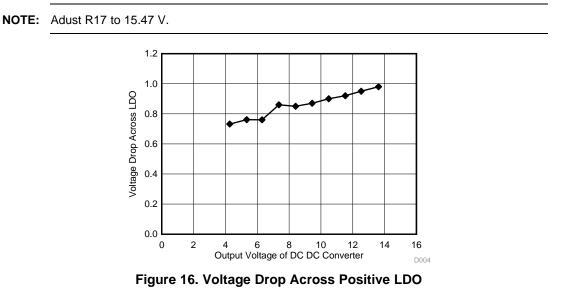

### 3.2.4 Test 4: Voltage Drop Across Positive LDO as a Function of Control Voltage

A load of 0.8 A is put on the output of the LDO, and the voltage drop across the LDO is observed for varying DC-DC converter outputs.

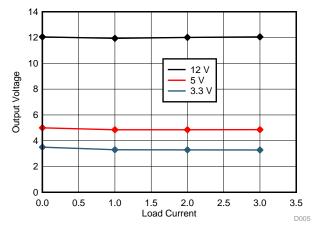

#### 3.2.5 Test 5: Load Regulation Positive DC-DC

The load regulation is given in Figure 17 and Table 4 for different load currents and output voltages.

Figure 17. Load Regulation Positive DC-DC

#### Table 4. Load Regulation Positive DC-DC Data

| CURRENT | 12 V  | 5 V  | 3.3 V |

|---------|-------|------|-------|

| 0       | 12.05 | 5.00 | 3.50  |

| 1       | 11.94 | 4.85 | 3.30  |

| 2       | 12.01 | 4.85 | 3.29  |

| 3       | 12.05 | 4.86 | 3.28  |

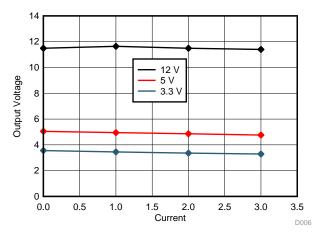

### 3.2.6 Test 6: Load Regulation Negative DC-DC Converter

The load regulation is given in Figure 18 and Table 5 for different load currents and output voltages.

Figure 18. Load Regulation Negative DC-DC

| CURRENT | 12 V  | 5 V  | 3.3 V |

|---------|-------|------|-------|

| 0       | 11.49 | 5.05 | 3.56  |

| 1       | 11.64 | 4.95 | 3.45  |

| 2       | 11.49 | 4.86 | 3.36  |

| 3       | 11.40 | 4.76 | 3.29  |

Low-Noise, Fixed Drop-Out, ±2.5-Design for Ultrasound CW Pulser

18

Low-Noise, Fixed Drop-Out, ±2.5- to ±12-V<sub>OUT</sub>, 3-A Power Supply Reference

TIDUD98–September 2017 Submit Documentation Feedback

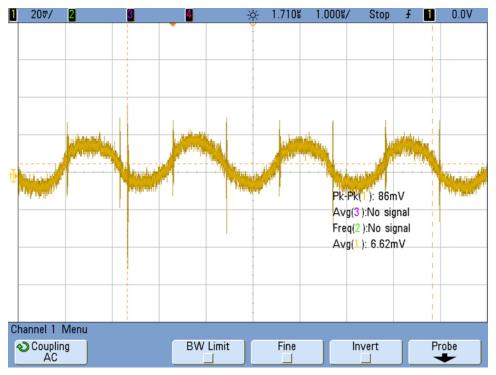

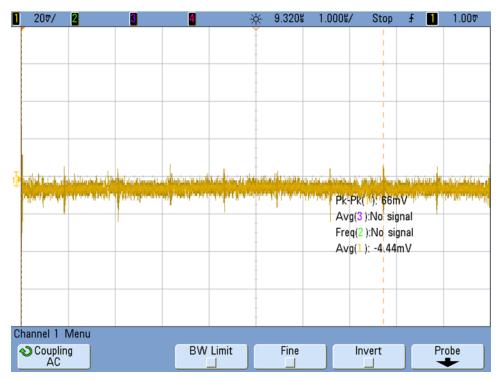

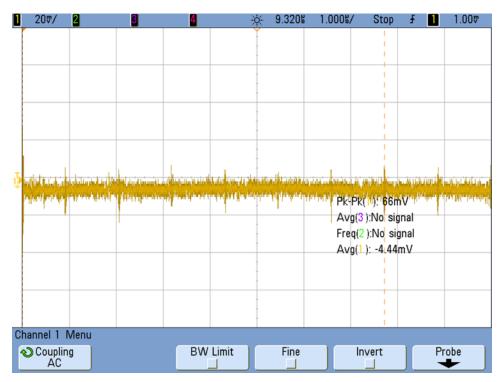

# 3.2.7 Test 7: Voltage Ripple of Positive Power Supply

Load current of 0.8 A from the LDO, 12-V output on the LDO

Figure 19. Voltage Ripple at Positive DC-DC Output

Figure 20. Voltage Ripple at Positive LDO Output

Hardware, Testing Requirements, and Test Results

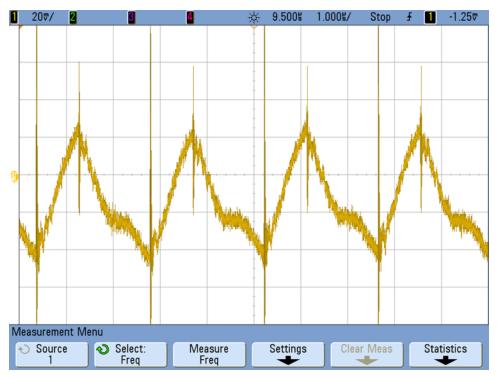

### 3.2.8 Test 8: Voltage Ripple of Negative Power Supply

This test shows the output ripple on the DC-DC converter output as well as LDO output with a load of 0.8 A on the LDO output.

Figure 21. Voltage Ripple at Negative DC-DC Input

Figure 22. Voltage Ripple at Negative LDO Output

Hardware, Testing Requirements, and Test Results

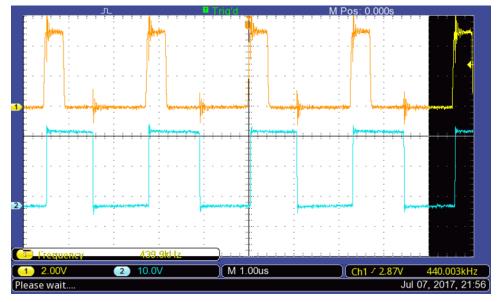

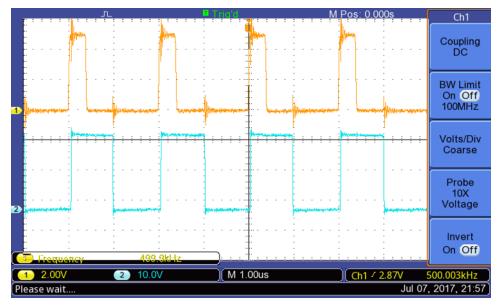

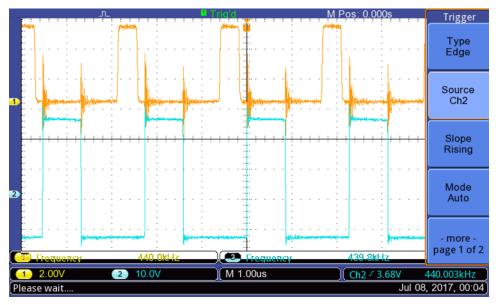

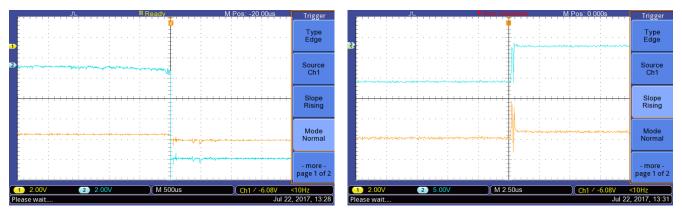

#### 3.2.9 Test 9: Synchronization Test Positive DC-DC

This test applies an external sync waveform of 3.3-V amplitude to the sync input of the DC-DC converter. The test also observes the switching node of the buck and the sync waveform.

Output voltage for this test is at 12 V with a 2-A load drawn direct on the DC-DC converter.

Figure 23. Sync and Output Switching Waveform of Positive DC-DC at 440 kHz

Figure 24. Sync and Output Switching Waveform of Positive DC-DC at 500 kHz

Hardware, Testing Requirements, and Test Results

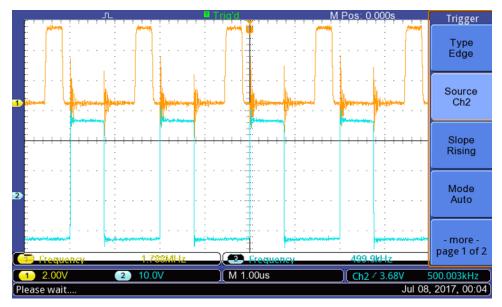

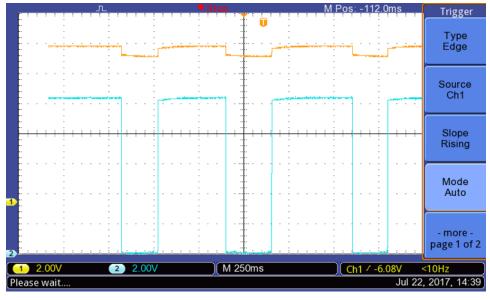

#### 3.2.10 Test 10: Synchronization Test Negative DC-DC

This test applies an external sync waveform of 3.3-V amplitude to the sync input of the DC-DC converter. The test also observes the switching node of the buck and the sync waveform.

Output voltage for this test is at -12 V with a 2-A load drawn direct on the DC-DC converter.

Figure 25. Sync and Output Switching Waveform of Negative DC-DC at 440 kHz

Figure 26. Sync and Output Switching Waveform of Negative DC-DC at 500 kHz

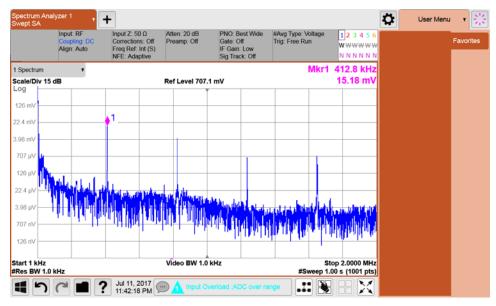

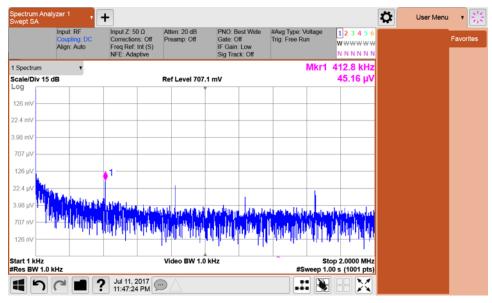

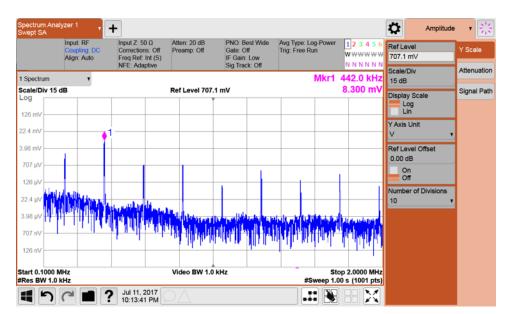

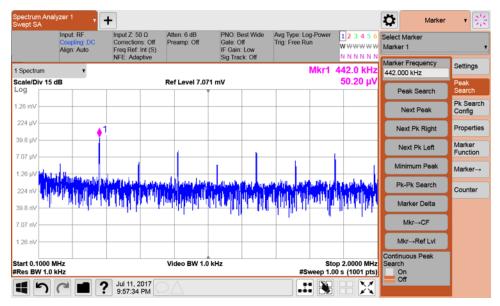

#### 3.2.11 Test 11: Spectrum Analyzer

The following waveforms are plots on a spectrum analyzer. This test measures the level of the switching waveform on the output of the DC-DC converters as well as the LDOs. These plots are for both positive and negative sections. A load of 1 A is applied on the LDO output and the LDO is maintained at a dropout of 1 V for both positive and negative circuits.

Figure 27. Spectral Plot of Negative DC-DC Output

Figure 28. Spectral Plot of Negative LDO Output

$PSRR = 20 \times log(V_{IN} LDO/V_{OUT} LDO)$  $PSRR = 20 \times log(15.8 \text{ mv}/45.16 \mu\text{V}) = 50.8 \text{ dB}$

Figure 29. Spectral Plot of Positive DC-DC Output

Figure 30. Spectral Plot of Positive LDO Output

$PSRR = 20 \times log(V_{IN} LDO/V_{OUT} LDO)$

$PSRR = 20 \times log(8.3 \text{ mv}/442 \mu \text{V}) = 44.04 \text{ dB}$

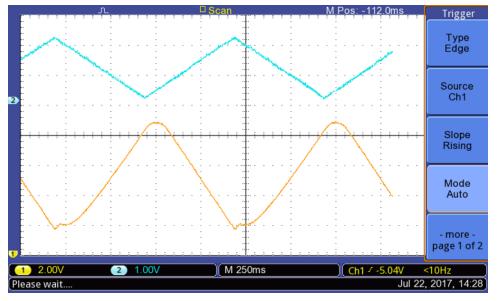

### 3.2.12 Test 12: Ramp of Control Voltage and Output Voltage LDO-Positive

A signal generator is used to give a ramp waveform on the DC control voltage input. The variation in the output voltage on the LDO was seen. A load resistance of 10  $\Omega$  was placed on the LDO output.

Figure 31. Ramp Waveform on Control Voltage-Positive DC-DC

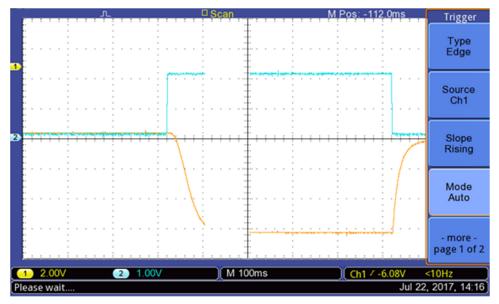

A signal generator is used to give a square waveform on the DC control voltage input. The variation in the output voltage on the LDO is seen. A load resistance of 10  $\Omega$  is placed on the LDO output.

Figure 32. Square Waveform on Control Voltage-Positive DC-DC

#### 3.2.13 Test 13: Ramp of Control Voltage and Output Voltage LDO-Negative

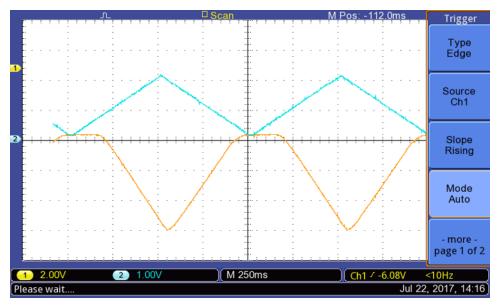

A signal generator is used to give a ramp waveform on the DC control voltage input. The variation in the output voltage on the LDO is seen. A load resistance of 10  $\Omega$  is placed on the LDO output.

Figure 33. Ramp Waveform on Control Voltage-Negative LDO

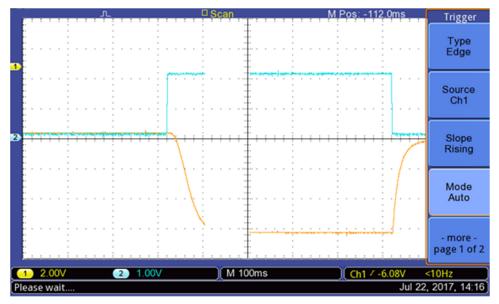

A signal generator is used to give a ramp waveform on the DC control voltage input. The variation in the output voltage on the LDO is seen. A load resistance of 10  $\Omega$  is placed on the LDO output.

Figure 34. Square Waveform on Control Voltage-Negative LDO

# 3.2.14 Test 14: Load Switching of 1-A Load at LDO Output

A 10- $\Omega$  load is switched on and off at the LDO output periodically. The output voltage is 9 V.

Figure 35. Load Switching-Positive LDO

A 10- $\Omega$  load is switched on and off at the LDO output periodically. The output voltage was –9 V.

Figure 36. Load Switching-Negative LDO-A

Figure 37. Load Switching-Negative LDO-B

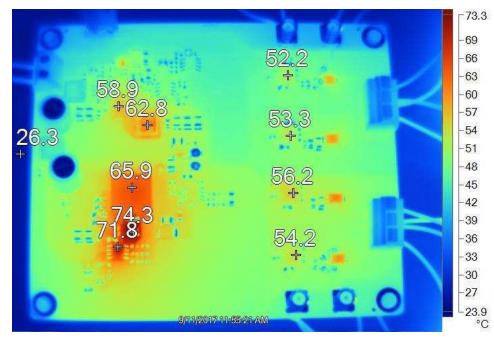

#### 3.2.15 Test 15: Temperature Test

This test applies 12 V and 0.8 A on each of the two positive LDOs and -12 V and 0.8 A on each of the two negative LDOs.

This test also applies a 0.5-V drop on the positive LDO and a 0.5-V drop across the negative LDO.

Figure 38. Temperature Test

# 4 Design Files

### 4.1 Schematics

To download the schematics, see the design files at TIDA-01458.

# 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01458.

# 4.3 PCB Layout Recommendations

### 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01458.

### 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-01458.

### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01458.

### 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01458.

# 5 Related Documentation

This reference design did not use any related documentation.

### 5.1 Trademarks

All trademarks are the property of their respective owners.

### 6 About the Author

**SANJAY DIXIT** is a system architect in the Industrial Systems-Medical Healthcare and Fitness Sector at Texas Instruments, where he is responsible for specifying reference designs.

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated