## IMPROVED NOISE PERFORMANCE OF THE ACF2101 SWITCHED INTEGRATOR

By Bonnie C. Baker (602) 746-7984

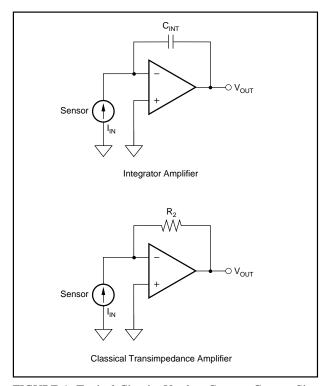

The signal-to-noise ratio and bandwidth of the combination of the ACF2101 dual, switched integrator and a low-level input current is exceptional when compared to the performance of a classical transimpedance amplifier (Figure 1). To further improve the ACF2101 signal-to-noise ratio, a resistor can be added in series with the input sensor.

FIGURE 1. Typical Circuits Used to Convert Current Signals to Voltage.

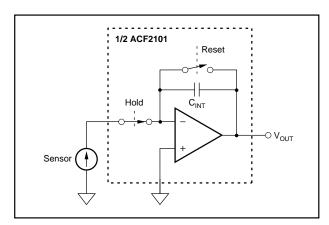

The ACF2101 is a dual switched integrator, as shown in Figure 2. The current from the sensor is integrated by the capacitor ( $C_{\text{INT}}$ ) in the feedback loop of the amplifier. Since the inverting input of the amplifier is kept at a virtual ground, the output of the integrator changes in a negative direction over time. The resulting transfer function of the switched integrator is:

$$V_{OUT} = \frac{-1}{C_{INT}} \int_{O}^{t} I_{IN} dt$$

## Where:

$V_{\text{OUT}} = \text{output voltage of op amp}$   $C_{\text{INT}} = \text{integration capacitor}$

$I_{IN}$  = sensor current

The output of the ACF2101 switched integrator is a time averaged representation of the input.

FIGURE 2. The ACF2101 Switched Integrator Block Diagram.

Once the ACF2101 has integrated the input signal over a predetermine period, the HOLD switch is opened, allowing the user to read the output of the switched integrator at a held voltage. The HOLD switch performs a sample/hold function on the signal. Once the signal is read, the RESET switch is closed in order to discharge the integration capacitor,  $C_{\rm INT}$ , and bring the output back to the same potential as the inverting input of the amplifier. Once the output returns to ground, the RESET switch is opened. Shortly after the RESET switch is opened, the HOLD switch closes to start the integration cycle again.

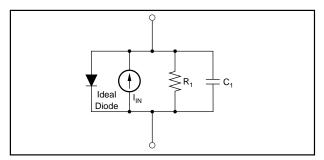

Typically, a photodiode is used as the sensor for both circuits shown in Figure 1. A photodiode can be modeled using the sensor model shown in Figure 3. This model includes a current source ( $I_{\rm IN}$ ), parasitic resistor ( $R_1$ ), and parasitic capacitor ( $C_1$ ). Typical values of  $R_1$  range from  $100k\Omega$  to  $100G\Omega$ . Typical values of  $C_1$  range from 20pF to 1000pF.  $C_1$  can be higher if the sensor is placed at a remote location, and a cable, with parasitic capacitance to ground, is used to transmit the signal to the input of the switched integrator.

FIGURE 3. Photodiode Model Used in Noise Analysis.

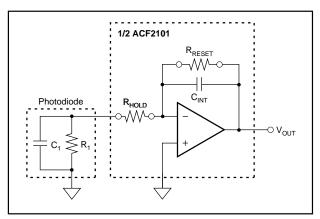

The noise model for the complete photodiode/switched integrator application is shown in Figure 4. In most applications the switched integrator is in the integrate mode for most of the total integration cycle. The model in Figure 4 represents the ACF2101 with the HOLD switch closed and the RESET switch opened. The typical on-resistance of the HOLD switch is  $1.5k\Omega$ , and the typical open-resistance of the RESET switch is  $1000G\Omega$ .

FIGURE 4. ACF2101 Switched Integrator and Photodiode Model Used for Noise Analysis.

FIGURE 5. Noise Gain of the ACF2101, Switched Integrator.

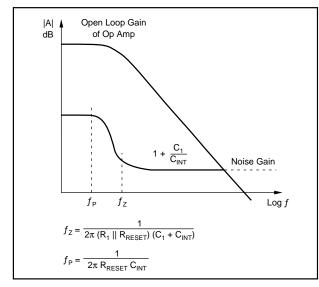

The three dominate sources of noise at the output of the switched integrator are the gained op amp noise, the charge injection noise of the switches and the  $^{\rm KT}/_{\rm C}$  noise of the integration capacitor. A bode plot of the op amp noise gain of the switched integrator is shown in Figure 6. The low-frequency pole of the noise gain is equal to:

$$f_{p} = \frac{1}{2\pi R_{RESET} C_{INT}}$$

This pole is usually found at very low frequencies. For example, if  $R_{\text{RESET}}=1000G\Omega$  and  $C_{\text{INT}}=100\text{pF}$ , the pole would occur at 0.00159Hz.

The zero of the noise gain plot is equal to:

$$f_{Z} = \frac{1}{2\pi(R_{1}||R_{RESET})(C_{1} + C_{INT})}$$

This zero is also usually found at very low frequencies. For example, if  $R_1 = 100 M\Omega$ ,  $C_1 = 50 pF$ ,  $R_{RESET} = 1000 G\Omega$ , and  $C_{INT} = 100 pF$ ,  $f_Z$  would equal 10.6Hz.

As a consequence, the op amp output noise of the switched integrator is dominated by the high frequency op amp noise multiplied by:

High frequency noise gain =

$$\left(1 + \frac{C_1}{C_{INT}}\right)$$

The total rms noise can be estimated as equal to:

NOISE <sub>OP AMP</sub> =

$$10\left(1 + \frac{C_1}{C_{INT}}\right) \mu Vrms$$

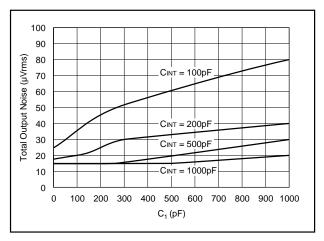

The charge injection noise of the switches and the integration capacitor noise both have broad band noise equivalent to  $10\mu Vrms$ . The total characterized noise of the ACF2101 switched integrator with various input capacitance and integration capacitance is shown in Figure 6.

FIGURE 6. Total Output Noise of the ACF2101 Switched Integrator vs Parasitic Photodiode Capacitance,  $C_1$ , and the ACF2101 Integration Capacitor,  $C_{\rm INT}$ .

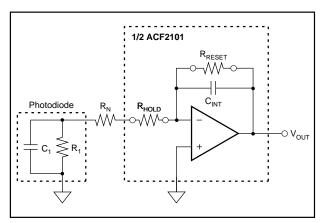

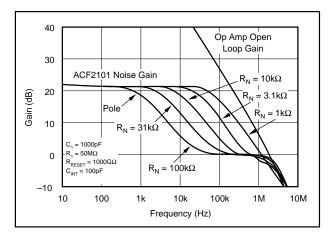

To further improve the signal-to-noise ratio of the ACF2101 switched integrator, a resistor can be added in series with the sensor, as shown in Figure 7. This additional resistor,  $R_{\text{N}}$ , in series with  $R_{\text{HOLD}}$ , adds a pole/zero pair at higher frequencies. When  $R_{\text{N}}$  equals  $0\Omega$ , the pole/zero pair generated by HOLD switch on-resistance ( $R_{\text{HOLD}}=1.5k\Omega$ ) occurs at frequencies close to the open loop gain of the amplifier. As shown in the bode plot in Figure 8,  $R_{\text{N}}$  plus  $R_{\text{HOLD}}$  attenuates high frequency noise.

FIGURE 7. The ACF2101 Switched Integrator with an Additional Resistor, R<sub>N</sub>, Added in Series with the Photodiode to Reduce Noise.

FIGURE 8. Noise Gain Plots of ACF2101 with an Additional Resistor,  $R_N$ , in Series with the Photodiode.

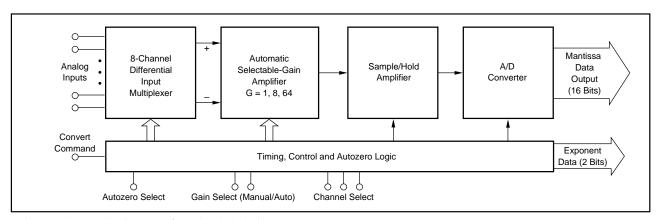

An application example is shown in Figure 9. The photodiode is modeled with a parasitic capacitance of 1000pF and parasitic resistance of  $50M\Omega$ . The integration capacitor used in the feedback loop of the op amp in the ACF2101 is equal to 100pF. The 20-bit, 40kHz ADC750 A/D converter block diagram is shown in Figure 10. Extreme care should be taken to properly guard the high impedance input pins of the ACF2101 in order to reduce the possibility of coupled noise into the signal.

The design trade-off for improved noise performance of the switched integrator is a slight degradation in the linearity performance of the photodetector. The current from the sensing device will cause an IR drop across  $R_{\rm N}$ . This IR drop will impress a voltage across the sensor, causing a small degree of dark current to start to conduct. As shown in Figure 8, the pole generated by the additional resistor,  $R_{\rm N}$ , is equal to:

Pole =

$$\frac{R_{N} + R_{1} + R_{HOLD}}{2 \pi R_{1} (R_{N} + R_{HOLD}) C_{1}}$$

The pole is directly affected by the value of  $R_{\rm N}$  and  $C_{\rm 1}$  (photodetector parasitic capacitance). Higher values for  $C_{\rm 1}$  will reduce the noise without compromising the linearity performance of the photodetector. The overall circuit performance is best optimized when the photodetector parasitic capacitance,  $C_{\rm 1}$ , is 200pF or greater.

The ACF2101 switched integrator is optimized for good noise and bandwidth performance for low-level input currents. The addition of a resistor in series with the photodiode further improves the noise performance without sacrificing bandwidth.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

FIGURE 9. Circuit and Timing Diagram used to Test the Noise Performance of the ACF2101 with and without  $R_{\rm N}$ .

FIGURE 10. Block Diagram of ADC750 A/D Converter.

## **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated