# 🔱 Texas Instruments

# **Design Goals**

| Input 1            |                    | Input 2            |                    | Output            |                   | Freq. | Supply          |                 |

|--------------------|--------------------|--------------------|--------------------|-------------------|-------------------|-------|-----------------|-----------------|

| V <sub>i1Min</sub> | V <sub>i1Max</sub> | V <sub>i2Min</sub> | V <sub>i2Max</sub> | V <sub>oMin</sub> | V <sub>oMax</sub> | f     | V <sub>cc</sub> | V <sub>ee</sub> |

| -2.5V              | 2.5V               | –250mV             | 250mV              | -4.9V             | 4.9V              | 10kHz | 5V              | -5V             |

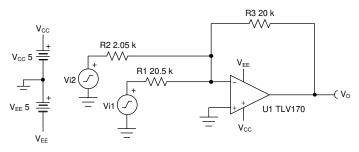

# **Design Description**

This design sums (adds) and inverts two input signals,  $V_{i1}$  and  $V_{i2}$ . The input signals typically come from lowimpedance sources because the input impedance of this circuit is determined by the input resistors,  $R_1$  and  $R_2$ . The common-mode voltage of an inverting amplifier is equal to the voltage connected to the non-inverting node, which is ground in this design.

# **Design Notes**

- 1. Use the op amp in a linear operating region. Linear output swing is usually specified under the A<sub>OL</sub> test conditions. The common-mode voltage in this circuit does not vary with input voltage.

- 2. The input impedance is determined by the input resistors. Make sure these values are large when compared to the output impedance of the source.

- 3. Using high-value resistors can degrade the phase margin of the circuit and introduce additional noise in the circuit.

- 4. Avoid placing capacitive loads directly on the output of the amplifier to minimize stability issues.

- 5. Small-signal bandwidth is determined by the noise gain (or non-inverting gain) and op amp gain-bandwidth product (GBP). Additional filtering can be accomplished by adding a capacitor in parallel to R<sub>3</sub>. Adding a capacitor in parallel with R<sub>3</sub> will also improve stability of the circuit if high-value resistors are used.

- 6. Large signal performance may be limited by slew rate. Therefore, check the maximum output swing versus frequency plot in the data sheet to minimize slew-induced distortion.

- 7. For more information on op amp linear operating region, stability, slew-induced distortion, capacitive load drive, driving ADCs, and bandwidth please see the *Design References* section.

1

# **Design Steps**

The transfer function for this circuit is given below.

$$V_o = V_{i1} \times \left(-\frac{R_3}{R_1}\right) + V_{i2} \times \left(-\frac{R_3}{R_2}\right)$$

1. Select a reasonable resistance value for R<sub>3</sub>.

$$R_3 = 20 \ k\Omega$$

2. Calculate gain required for V<sub>i1</sub>. For this design, half of the output swing is devoted to each input.

$$|G_{Vi1}| = \left| \frac{\frac{V_{oMax} - V_{oMin}}{2}}{V_{i1Max} - V_{i1Min}} \right| = \left| \frac{\frac{4.9 V - (-4.9 V)}{2}}{2.5 V - (-2.5 V)} \right| = 0.98 \frac{V}{V} = -0.175 \, dB$$

3. Calculate the value of R<sub>1</sub>.

$$|G_{Vi1}| = \frac{R_3}{R_1} \to R_1 = \frac{R_3}{|G_{Vi1}|} = \frac{20 \ k\Omega}{0.98 \ \frac{V}{V}} = 20.4 \ k\Omega \approx 20.5 \ k\Omega \ (Standard Value)$$

4. Calculate gain required for Vi2. For this design, half of the output swing is devoted to each input.

$$|G_{Vi2}| = \left| \frac{\frac{V_{oMax} - V_{oMin}}{2}}{V_{i2Max} - V_{i2Min}} \right| = \left| \frac{\frac{4.9 \, V - (-4.9 \, V)}{2}}{250 \, mV - (-250 \, mV)} \right| = 9.8 \frac{V}{V} = 19.82 \, dB$$

5. Calculate the value of R<sub>2</sub>.

$GBP_{OPA170} = 1.2 MHz$

$|G_{Vi2}| = \frac{R_3}{R_2} \rightarrow R_2 = \frac{R_3}{|G_{Vi2}|} = \frac{20 \, k\Omega}{9.8 \, \frac{V}{V}} = 2.04 \, k\Omega \approx 2.05 \, k\Omega \, (StandardValue)$

Calculate the small signal circuit bandwidth to ensure it meets the 10-kHz requirement. Be sure to use the noise gain (NG), or non-inverting gain, of the circuit. When calculating the noise gain note that R<sub>1</sub> and R<sub>2</sub> are in parallel.

$$NG = 1 + \frac{R_3}{R_1 ||R_2} = 1 + \frac{20 \ k\Omega}{1.86 \ k\Omega} = 11.75 \frac{V}{V} = 21.4 \ dB \tag{8}$$

$$BW = \frac{GBP}{NG} = \frac{1.2 \ MHz}{11.75 \ \frac{V}{V}} = 102 \ kHz \tag{9}$$

This requirement is met because the closed-loop bandwidth is 102kHz and the design goal is 10kHz.

7. Calculate the minimum slew rate to minimize slew-induced distortion.

$$V_{p} = \frac{SR}{2 \times \pi \times f} \rightarrow SR > 2 \times \pi \times f \times V_{p}$$

$$SR > 2 \times \pi \times 10 \ kHz \times 4.9 \ V = 307.87 \ \frac{kV}{s} = 0.31 \ \frac{V}{\mu s}$$

(11)

- $SR_{OPA170}=0.4V/\mu s$ , therefore it meets this requirement.

- 8. To avoid stability issues ensure that the zero created by the gain setting resistors and input capacitance of the device is greater than the bandwidth of the circuit.

$$\frac{1}{2 \times \pi \times (C_{cm} + C_{diff}) \times (R_1 ||R_2||R_3)} > \frac{GBP}{NG}$$

$$\frac{1}{2 \times \pi \times 3 \ pF \times 3 \ pF \times 1.7 \ k\Omega} > \frac{1.2 \ MHz}{11.75 \ \overline{V}}$$

(13)

$15.6\,MHz>102\,kHz$

- C<sub>cm</sub> and C<sub>diff</sub> are the common-mode and differential input capacitances.

- Since the zero frequency is greater than the bandwidth of the circuit, this requirement is met.

(14)

# **Design Simulations**

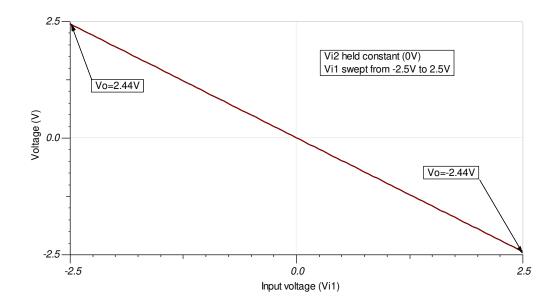

# **DC Simulation Results**

This simulation sweeps  $V_{i1}$  from –2.5V to 2.5V while  $V_{i2}$  is held constant at 0V. The output is inverted and ranges from –2.44V to 2.44V.

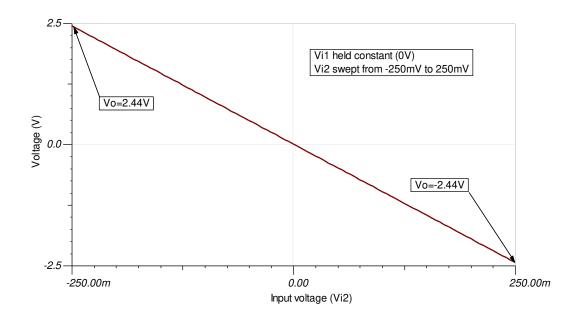

This simulation sweeps  $V_{i2}$  from –250mV to 250mV while  $V_{i1}$  is held constant at 0V. The output is inverted and ranges from –2.44V to 2.44V.

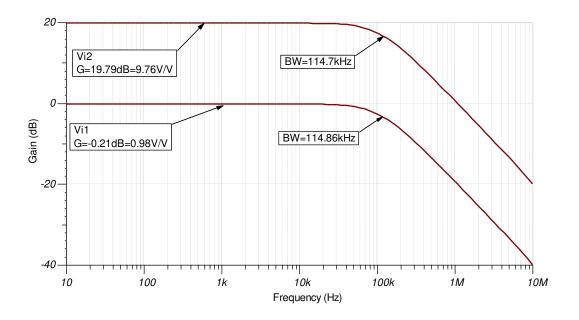

#### **AC Simulation Results**

This simulation shows the bandwidth of the circuit. Note that the bandwidth is the same for either input. This is because the bandwidth depends on the noise gain of the circuit, not the signal gain of each input. These results correlate well with the calculations.

#### **Transient Simulation Results**

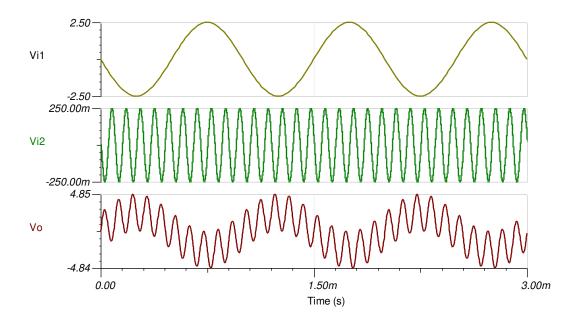

This simulation shows the inversion and summing of the two input signals.  $V_{i1}$  is a 1-kHz, 5- $V_{pp}$  sine wave and  $V_{i2}$  is a 10-kHz, 500-m $V_{pp}$  sine wave. Since both inputs are properly amplified or attenuated, the output is within specification.

# **Design References**

See Analog Engineer's Circuit Cookbooks for TI's comprehensive circuit library.

See circuit SPICE simulation file SBOC494.

For more information on many op amp topics including common-mode range, output swing, bandwidth, and how to drive an ADC please visit TI Precision Labs.

# **Design Featured Op Amp**

| OPA170                    |                        |  |  |  |

|---------------------------|------------------------|--|--|--|

| V <sub>ss</sub>           | 2.7V to 36V            |  |  |  |

| V <sub>inCM</sub>         | (Vee-0.1V) to (Vcc-2V) |  |  |  |

| V <sub>out</sub>          | Rail-to-rail           |  |  |  |

| V <sub>os</sub>           | 0.25mV                 |  |  |  |

| lq                        | 110µA                  |  |  |  |

| ۱ <sub>b</sub>            | 8pA                    |  |  |  |

| UGBW                      | 1.2MHz                 |  |  |  |

| SR                        | 0.4V/µs                |  |  |  |

| #Channels                 | 1, 2, 4                |  |  |  |

| www.ti.com/product/opa170 |                        |  |  |  |

#### **Design Alternate Op Amp**

| LMC7101                    |               |  |  |  |

|----------------------------|---------------|--|--|--|

| V <sub>ss</sub>            | 2.7V to 15.5V |  |  |  |

| V <sub>inCM</sub>          | Rail-to-rail  |  |  |  |

| V <sub>out</sub>           | Rail-to-rail  |  |  |  |

| V <sub>os</sub>            | 110µV         |  |  |  |

| Ιq                         | 0.8mA         |  |  |  |

| l <sub>b</sub>             | 1pA           |  |  |  |

| UGBW                       | 1.1MHz        |  |  |  |

| SR                         | 1.1V/µs       |  |  |  |

| #Channels                  | 1             |  |  |  |

| www.ti.com/product/Imc7101 |               |  |  |  |

#### **Revision History**

| Revision       | Date          | Change                                                                                                         |

|----------------|---------------|----------------------------------------------------------------------------------------------------------------|

| С              | January 2021  | Updated Formula format                                                                                         |

| В              | December 2020 | Updated Design Goals Table                                                                                     |

| A January 2019 |               | Down-style title.<br>Updated title role to <i>Amplifiers</i> .<br>Added link to circuit cookbook landing page. |

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated