## OPTIMIZING PERFORMANCE OF THE DCP01B, DVC01 AND DCP02 SERIES OF UNREGULATED DC/DC CONVERTERS.

By Dave McIlroy

The DCP01B, DCV01, and DCP02 are three families of miniature DC/DC converters providing an isolated unregulated voltage output. All are fabricated using a CMOS/DMOS process with the DCP01B replacing the familiar DCP01 family that was fabricated from a bipolar process. The DCP02 is essentially an extension of the DCP01B family providing a higher power output with a significantly improved load regulation, and the DCV01 is tested to a higher isolation voltage.

#### **TECHNOLOGICAL IMPROVEMENTS**

#### Transformer drive circuit

The new CMOS/DMOS process represents an improvement over the bipolar process as the internal circuits can switch much faster. Additionally, the transformer drive transistors have a characteristically low value of transistor 'on' resistance, ( $R_{DS}$ ), thus more power is transferred to the transformer. With the Bipolar process, the transformer drive circuit was limited by the base current available to switch on the power transistors driving the transformer, and their characteristic current gain (beta) resulting in a slower turnon time. Consequently, more power was dissipated within the transistor. This resulted in a lower overall efficiency, particularly at higher output load currents.

#### Self synchronization

The input synchronizations facility,  $(SYNC_{IN})$  has been improved over the bipolar devices. If two to eight devices (maximum) have their respective  $SYNC_{IN}$  pins connected together, then all devices will be synchronized.

Each device has its own onboard oscillator. This is generated by charging a capacitor from a constant current and producing a ramp. When this ramp passes a threshold, an internal switch is activated that discharges the capacitor to a second threshold before the cycle is repeated.

When several devices are connected together, all the internal capacitors are charged simultaneously.

The improvements within the new process are such that when one device passes its threshold during the charge cycle, it starts the discharge cycle. All the other devices sense this falling voltage and likewise initiate a discharge cycle so that all devices discharge together. A subsequent charge cycle is only restarted when the last device has finished its discharge cycle.

#### **OPTIMIZING PERFORMANCE**

The optimum performance can only be achieved if the device is correctly supported. By the very nature of a switching converter, it requires power to be instantly available when it 'switches' on. If the converter has DMOS switching transistors, the fast edges will create a high current demand on the input supply. This transient load placed on the input is supplied by the external input decoupling capacitor, thus maintaining the input voltage. Therefore, the input supply does not see this transient (this is an analogy to high-speed digital circuits). The positioning of the capacitor is critical and must be placed as close as possible to the input pins and tracked via a low impedance path.

The optimum performance is primarily dependent on two factors:

- 1) Tracking of the input and output circuits for minimal loss.

- 2) The ability of the decoupling capacitors to maintain the input and output voltages at a constant level.

#### **PCB Tracking**

The losses due to resistance and inductance caused by tracking can be minimized by the use of a ground and power plane where possible. If that is not possible, use wide tracks to reduce the losses. If several devices are being powered from a common power source, a 'star' connected system for the tracking must be deployed; devices must not be tracked in 'series', as this will cascade the losses. The position of the decoupling capacitors is important. They must be as close to the devices as possible in order to reduce losses.

#### **Decoupling capacitors**

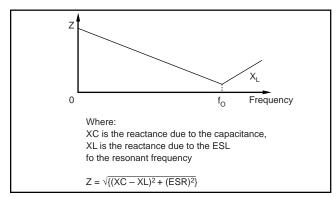

All capacitors have losses due to their internal Equivalent Series Resistance, (ESR) and to a lesser degree their Equivalent Series Inductance (ESL). Values for the latter are not always easy to obtain, however, some manufacturers provide graphs of Frequency versus Capacitor Impedance. These will show the capacitors impedance falling as frequency is increased. As the frequency is increased the impedance will stop decreasing and begin to rise. The point of minimum impedance indicates the capacitors resonant frequency. This frequency is where the components of capacitance and inductance reactance are of equal magnitude. Beyond this point the capacitor is not effective as a capacitor.

FIGURE 1. Capacitor Impedance versus Frequency.

At  $f_o$ ,  $X_C = X_{L}$ , however, there is a 180° phase difference resulting in cancellation of the imaginary component. The resulting effect is the impedance at the resonant point is the real part of the complex impedance namely the value of the ESR. The resonant frequency must be well above the 800kHz switching frequency of the DCP and DCVs.

The effect of the ESR is to cause a voltage drop within the capacitor. The value of this voltage drop is simply the product of the ESR and the transient load current:

$$\mathbf{V}_{\mathrm{IN}} = \mathbf{V}_{\mathrm{PK}} - (\mathrm{ESR} \bullet \mathbf{I}_{\mathrm{TR}})$$

Where  $V_{IN}$  is the voltage at the device input,  $V_{PK}$  is the maximum value of the voltage on the capacitor during charge, and  $I_{TR}$  is the transient load current.

The other factor that effects the performance is the value of the capacitance. However, for the input and the full wave outputs (single output voltage devices) the ESR is the dominant factor.

#### Input Capacitor and the effects of ESR

If the input decoupling capacitor does not have a low value of ESR, then at the instant the power transistors switch on, the voltage at the input pins will fall momentarily. Should the voltage fall below approximately 4V, the DCP will detect an under voltage condition and switch the DCP drive circuits to the off state. This is carried out as a precaution against a genuine low input voltage condition that could slow down or even stop the internal circuits from operating correctly. This would result in the drive transistors being turned on too long, causing saturation of the transformer and destruction of the device. Following detection of a low input voltage condition, the device switches off the internal drive circuits until the input voltage returns to a safe value. Then the device tries to restart. If the input capacitor is still unable to maintain the input voltage, shutdown reoccurs. This process is repeated until the capacitor is charged sufficiently to start the device correctly. Otherwise, the device will be caught up in a loop.

Normal start up should occur in approximately 1ms from power being applied to the device. If a considerably longer start up duration time is encountered, it is likely that either (or both) the input supply or the capacitors are not performing adequately.

For 5V input devices a  $2.2\mu$ F ceramic capacitor will ensure a good start up performance, and for the remaining input voltage ranges,  $0.47\mu$ F ceramic capacitors are good. If tantalum capacitors are being considered, close attention must be paid to the ESR value specified, as most tantalum capacitors do not have low ESR values.

#### **Output Ripple Calculation Example**

DCP020505: Output voltage 5V, Output current 0.4A. At full output power, the load resistor is 12.5 $\Omega$ . Output capacitor of 1 $\mu$ F, ESR of 0.1 $\Omega$ . Capacitor discharge time 1% of 800kHz (ripple frequency):

$$t_{DIS} = 0.0125\mu s$$

$$\tau = C \cdot R_{LOAD}$$

$$\tau = 1 \cdot 10^{-6} \cdot 12.5 = 12.5\mu s$$

$$V_{DIS} = V_0(1 - EXP(-t_{DIS}/\tau))$$

$$V_{DIS} = 5mV$$

By contrast the voltage dropped due to the ESR:

$$\begin{split} V_{\text{ESR}} &= I_{\text{LOAD}} \bullet \text{ESR} \\ V_{\text{ESR}} &= 40 \text{mV}. \\ \text{Ripple voltage} &= 45 \text{mV}. \end{split}$$

Clearly, increasing the capacitance will have a much smaller effect on the output ripple voltage than reducing the value of the ESR for the filter capacitor.

#### DUAL OUTPUT VOLTAGE DCP AND DCV'S

The voltage output for the dual DCPs is half wave rectified, therefore, the discharge time is  $1.25\mu s$ . Repeating the above calculations using the 100% load resistance of  $25\Omega$  (0.2A per output), the results are shown below:

$$\tau = 25\mu s$$

$$T_{DIS} = 1.25\mu s.$$

$$V_{DIS} = 244mV$$

$$V_{ESR} = 20mV.$$

Ripple Voltage = 266mV.

This time it is the capacitor discharging that is contributing to the largest component of ripple. Changing the output filter to  $10\mu$ F, and repeating the calculations:

Ripple Voltage =

$$45 \text{mV}$$

.

This value is composed of almost equal components.

The above calculations are given only as a guide, capacitor parameters usually have large tolerances and can be susceptible to environmental conditions.

# OTHER DOCUMENTS RELATING TO THE DCP01B, DCV01 AND DCP02

AB-153: External Synchronization of the DCP01, 02 Series of DC/DC Converters (SBAA035).

### PCB LAYOUT NOTES

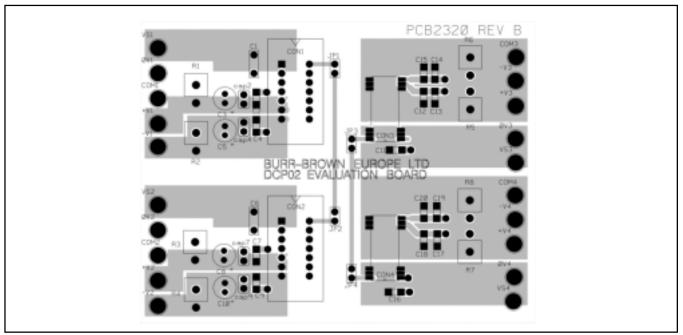

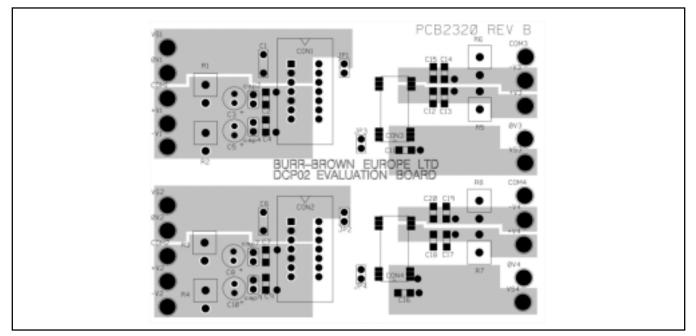

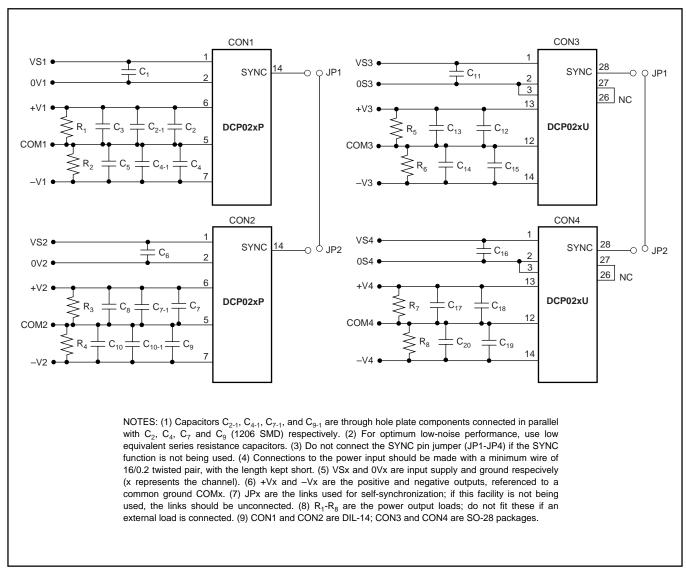

Figures 2 and 3 illustrate a printed circuit board layout tracked for the two conventional (DCP01/02, DCV01), and two SO-28 surface mount packages (DCP02U).

Input power and ground planes have been utilized providing a low impedance path for the input power. For the output the common or 0V has been tracked via a ground plane while the tracking for the positive and negative voltage outputs are conducted via wide tracks in order to minimize losses. The location of the decoupling capacitors in close proximity to their respective pins ensures low losses due to the effects of tracking inductance thus improving the ripple performance. This is of particular importance to the input decoupling capacitor as this supplies the transient current associated with the fast switching waveforms of the power drive circuits.

The Sync pin when not being used is best left as a floating pad. A ground ring or annulus connected around the pin will prevent noise being conducted onto the pin. If the Sync pin is being connected to one or more Sync pins then the linking track should be narrow and must be kept short in length, also no other track should be in close proximity to this track as this will increase the stray capacitance on this pin, that will effect the performance of the oscillator.

FIGURE 2. Example of PCB Layout, View on Component Side.

FIGURE 3. Example of PCB Layout, Non Component Side.

FIGURE 4. Example of PCB Layout, Schematic Diagram.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2001, Texas Instruments Incorporated