#### **Texas Instruments GTLP Frequently Asked Questions**

Steve Blozis

Standard Linear & Logic

#### ABSTRACT

Using a question-and-answer format, advantages of TI's GTLP devices, particularly for backplane applications, are presented, as well as differences between GTLP and GTL/LVDS devices. Applicable topics include data throughput rates, synchronous clocks, price and alternative sources, bus transceivers, live insertion, power consumption, backplane termination, voltage translation, IBIS and HSPICE models, and sample availability.

#### **Table of Contents**

|     | Introduction                                                                                   | 4  |

|-----|------------------------------------------------------------------------------------------------|----|

| 1.  | What is a backplane?                                                                           | 4  |

| 2.  | What is a backplane protocol?                                                                  |    |

| 3.  | Should I use a parallel or serial architecture?                                                | 4  |

| 4.  | If I use a parallel single-ended backplane, why do I need to use backplane-optimized           |    |

|     | transceivers and not just typical LVT or FCT devices?                                          | 5  |

| 5.  | What is VME?                                                                                   | 5  |

| 6.  | What is GTL?                                                                                   | 6  |

| 7.  | What is the difference between GTLP and GTL?                                                   | 9  |

| 8.  | What is distributed capacitance?                                                               | 12 |

| 9.  | What are you going to do with GTL now that you have GTLP?                                      | 15 |

| 10. | How should I terminate GTL devices in short-distance applications?                             | 16 |

|     | What is the advantage of using GTLP in my backplane?                                           |    |

| 12. | What is the difference between GTLP and LVDS?                                                  | 18 |

| 13. | How does GTLP compare to other single-ended and differential bus solutions?                    | 19 |

|     | What is the maximum data throughput using GTLP?                                                |    |

| 15. | What is the difference between synchronous clock and source-synchronous clock?                 | 23 |

|     | What GTLP devices are available and how much will they cost?                                   |    |

| 17. | These function numbers are different. How do they compare to normal logic functions?           | 25 |

| 18. | I know what a bus transceiver is, but what is a UBT™?                                          | 26 |

| 19. | I need an alternate source. Are there any?                                                     | 28 |

| 20. | Are the alternate-source devices identical?                                                    | 29 |

| 21. | What is important about live insertion?                                                        | 30 |

| 22. | What is the total power consumption of an 18-bit GTLP driver?                                  | 31 |

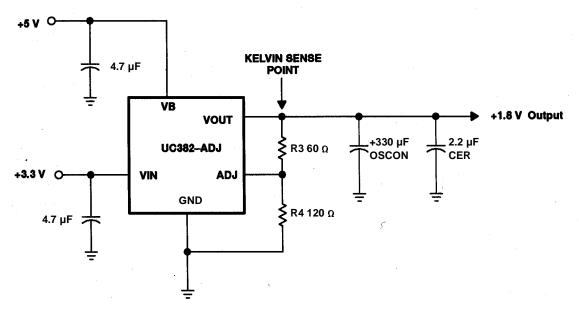

| 23. | How should I generate the termination voltage?                                                 | 34 |

| 24. | Why not use Thevenin voltage dividers for termination?                                         | 35 |

|     | Tell me more about bus hold                                                                    |    |

|     | Tell me more about power-up 3-State (PU3S).                                                    |    |

| 27. | Should I tie GTLPH16612 control inputs to 3.3 V or to 5 V?                                     | 36 |

| 28. | What do I do with unused or undriven GTLP A- or B-port I/Os?                                   | 37 |

| 29. | Can I connect the SN74GTLPH16612GR unused I/O pins of the                                      |    |

|     | A ports and B ports directly to GND?                                                           |    |

|     | How does an extender card affect signal integrity?                                             |    |

|     | What is the transistor count for GTLP devices?                                                 |    |

|     | Can I use GTLP as a low-voltage translator?                                                    |    |

|     | What is the voltage input range I can apply to the B port if V <sub>ref</sub> is set at 0.8 V? |    |

|     | Can I use GTLP as a replacement for FB+ devices?                                               | 42 |

| 35. | I'm trying to determine which 3.3-V logic family will best fit my needs, and                   |    |

|     | I'm still not quite clear on what choice I should make                                         |    |

|     | How do I get a GTLP data sheet?                                                                |    |

| 37. | When will GTLP models and devices be available?                                                | 45 |

| 38. How do I get IBIS Models?                                                           | 45 |

|-----------------------------------------------------------------------------------------|----|

| 39. How do I get HSPICE Models?                                                         |    |

| 40. Why does the unencrypted Level-37 HSPICE model require a confidentiality agreement? | 46 |

| 41. How should I request a confidentiality agreement?                                   | 46 |

| 42. What does the encrypted HSPICE model zipped file contain?                           | 46 |

| 43. If the file is encrypted, why do we need the one-time patch from Avant ?            | 47 |

| 44. How do I request preproduction samples?                                             | 47 |

| 45. How do I request production samples?                                                | 47 |

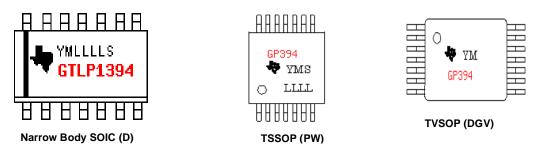

| 46. I requested the SN74GTLP1394, but the topside marking is GP394                      | 47 |

| 47. How can I request additional technical support?                                     | 49 |

#### Introduction

This information on GTLP and backplane design is presented in the frequently asked-question (FAQ) format. The GTLP FAQs allow the novice backplane user to learn more about parallel backplanes and allows the experienced backplane user to better design-in and use the higher performance of GTLP devices. Any questions not adequately addressed or applications you want highlighted can be sent to GTLP@list.ti.com for action and possible future insertion into the FAQs.

#### 1 What is a backplane?

A backplane is a physical and electrical system bus that interconnects several printed circuit boards though a series of connectors. These buses can vary by the number of layers and traces and by electrical architecture. Generally, backplanes are passive, particularly in the telecom market, in which reliability concerns force designers to minimize the number of backplane components. Backplane transceivers/buffers drive data onto and receive data directed to PC boards located along the backplane.

#### 2 What is a backplane protocol?

The protocol decides the electrical, logical, and mechanical characteristics of a backplane. In addition to the standard protocols, many backplane designers prefer to employ proprietary protocols and architectures. Some of the more popular standard protocols are BLT, MBLT, 2eVME, and 2eSST on VME64x backplanes, PCI, cPCI, PMC, ISA, Multibus, PC/104, and PC/104+. Of these, VME, PCI and cPCI, collectively, dominate the market. cPCI combines the robust, rugged VME backplane physical configurations with the electrical performance of the PCI backplanes.

#### 3 Should I use a parallel or serial architecture?

Part of choosing a protocol is deciding which type of backplane architecture is suited best to your application. You must choose between parallel and serial architectures, or a combination of both, and select point-to-point, multidrop, or multipoint data-distribution methods. Parallel systems require less protocol overhead, which is useful when sending status or control bits over short distances. Serial implementations offer board saving through the reduction in the number of board traces (if SERDES devices are used) and supply higher data throughput over greater distances.

# 4 If I use a parallel single-ended backplane, why do I need to use backplane-optimized transceivers and not just typical LVT or FCT devices?

The physics involved with a distributed-capacitance load limits the maximum frequency, unless the device is optimized with slower edge rates that ring less in these environments. FCT or LVT can offer only up to about 25 MHz, and, even then, signal integrity might be poor. The new VME and GTLP families are optimized with slower edge rates and provide much better signal integrity in a backplane environment. VME devices can operate up to about 40 MHz and are compatible with existing TTL/LVTTL backplane logic. GTLP is a derivative of GTL, and can operate at up to 175 MHz.

#### 5 What is VME?

VME is short for VERSA bus architecture and owes its heritage to the Motorola 6800 microprocessor. It is a standardized 21-slot, 64-bit backplane architecture, coordinated and controlled by the VMEbus International Trade Association (VITA). TI is working with VITA on the SN74VMEH22501, a new backplane-optimized device that supports the 2eVME and 2eSST protocols. More information on VITA can be obtained at http://www.vita.com. More information on the new VME device can be obtained at http://www.ti.com/sc/etl.

#### 6 What is GTL?

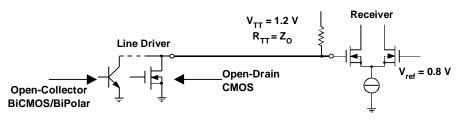

GTL is a reduced-voltage-swing (<1 V), open-drain/collector, differential-input JEDEC standard that allows higher frequency operation than TTL devices in point-to-point and lightly loaded memory-interface-bus applications. The reduced voltage swing reduces EMI and allows higher frequencies. For best signal integrity, the open-drain/collector arrangement facilitates matching the termination resistor (R<sub>TT</sub>) to the trace impedance (Z<sub>O</sub>). As shown in Figure 1, the open-drain/collector pulls the signal low when the device is turned on, but when the device is turned off, the pullup termination resistor is required to pull the signal high to the termination voltage (V<sub>TT</sub>). The GTL standard is V<sub>TT</sub>/V<sub>OH</sub>= 1.2 V, V<sub>OL</sub> = 0.4 V, and V<sub>IH</sub> and V<sub>IL</sub> set ±50 mV around the GTL differential-input reference voltage (V<sub>ref</sub>) of 0.8 V.

Figure 1. GTL Open-Drain/Collector Differential-Input Device

Open-drain and open-collector devices operate in exactly the same way to sink energy to ground. Open drain refers to CMOS transistors, while open collector refers to bipolar transistors. GTL devices can be manufactured using either process.

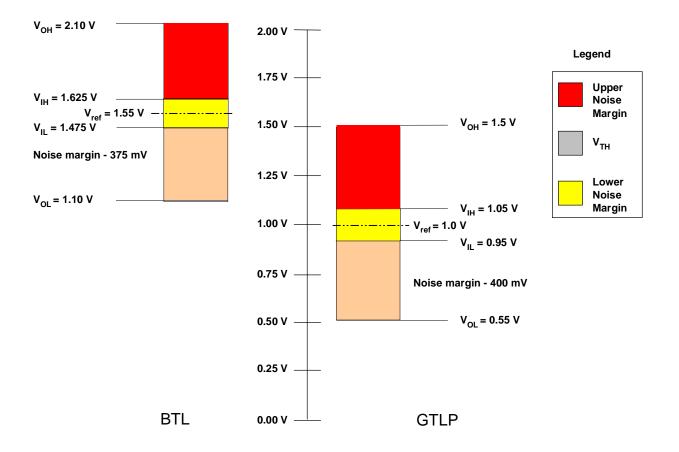

GTL+ is a variation on GTL that moves  $V_{ref}$  from 0.8 V to 1.0 V so that it is farther from the ground-bounce region. GTL+ voltage swing improves the upper and lower noise margins. Voltage swing is from  $V_{OL} = 0.55$  V to the termination voltage of  $V_{TT}/V_{OH} = 1.5$  V.

Any device that operates at GTL signal levels also can operate at GTL+ signal levels, and vice versa, with GTL+ being the preferred signal level due to its higher noise margins. In unusually noisy situations,  $V_{ref}$  can be adjusted to other than 0.8 V or 1.0 V in either standard to equalize, and, therefore, maximize both the upper and lower noise margins.

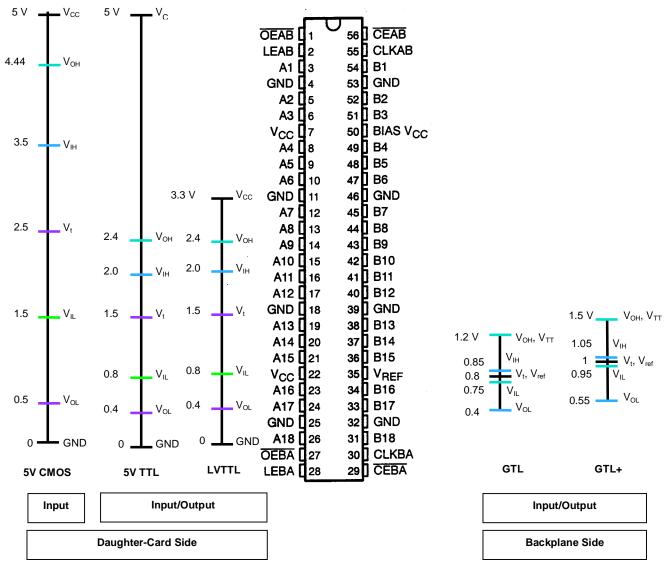

GTL devices are bidirectional translators (see Figure 2). A-Port (daughter-card side) input can be 5-V CMOS, TTL, or LVTTL logic levels; output is LVTTL, which is compatible with TTL logic levels. B-Port (backplane side) input and output is GTL or GTL+ signal levels.

Figure 2. GTL Bidirectional Translator

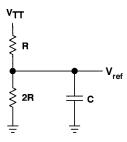

As shown in Figure 3, V<sub>ref</sub> is set by an R/2R resistor network between V<sub>TT</sub> and GND. The resistor network maintains balanced upper and lower noise margins for any termination-voltage fluctuations. A 0.1- to 0.01- $\mu$ F bypass capacitor buffers voltage fluctuations and should be as close to the V<sub>ref</sub> pin as possible.

Figure 3. GTL R/2R Resistor Network

$V_{ref}$  is generated locally on each card, using size 805 1-k $\Omega$  and 2-k $\Omega$  ±1% resistors. Each device  $V_{ref}$  input takes, at most, 10  $\mu A$ , so one resistor network per card is acceptable. The card resistor network takes  $V_{TT}$  from the backplane through a connector power pin. Do not distribute the  $V_{ref}$  power across all cards from one resistor network.

#### 7 What is the difference between GTLP and GTL?

TI introduced the GTL family of devices in 1993. GTL devices were designed with faster edge rates to drive a lumped load. Originally, these devices were designed for small buses on a board, e.g., memory applications, and did not support hot insertion. The devices rang excessively when used in larger multipoint distributed-capacitance backplane applications because of the faster edge rate. Maximum backplane frequency was limited to about 30 MHz.

GTLP devices were introduced in 1997 to serve distributed-capacitance backplane applications. GTLP is a subset of GTL devices, with one major difference. GTLP incorporates improved output edge-control (OEC) circuitry that slows the edge rate and reduces ringing, which allows maximum possible frequencies above 80 MHz in backplane applications. GTLP devices can operate at GTL signal levels, but are optimized for, and normally only specified at, GTL+ signal levels ( $V_{OL} = 0.55$  V to  $V_{OH} = 1.5$  V, with  $V_{ref} = 1.0$  V). GTLP backplane-optimized devices normally refer to GTLP instead of GTL+ as the 1.5-V  $V_{OH}/1.0$ -V  $V_{ref}$  standard, while GTL lumped-load optimized devices refer to GTL+ at this voltage level.

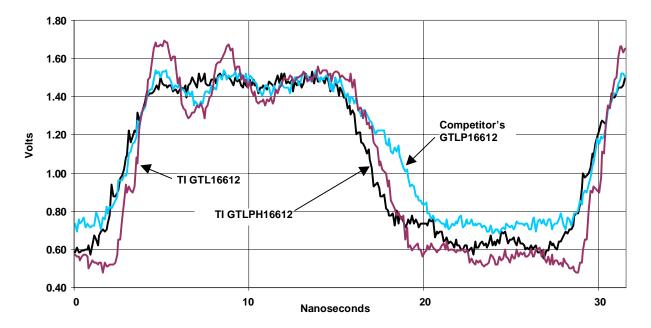

The waveforms in Figure 4 demonstrate the difference between the TI SN74GTL16612 and the newer SN74GTLPH16612, and how the backplane-optimized edge rates improve signal integrity in a distributed load.

Test results for the competitor's GTLP16612, a pin-for-pin functional equivalent of the SN74GTLPH16612, is shown in Figure 4 for comparison. These receiver waveforms were obtained using a fully loaded 16-slot demonstration backplane, with  $Z_0 = 50 \Omega$ ,  $R_{TT} = 24 \Omega$ , slot spacing = 0.9 inch, and data frequency of 37.5 MHz. The driver card was in slot number 8 and the receiver card was in slot number 1.

Figure 4. Demonstration of Output Edge Control

All three devices shown in Figure 4 have bus hold on the LVTTL A port. But, only the newer TI GTLP family uses H in the part number to denote bus hold, because there are several devices in the GTLP family without bus hold. All TI GTL devices have bus hold, while the competitor's GTL or GTLP family has some of both; the only way to determine the configuration is by referring to the data sheet.

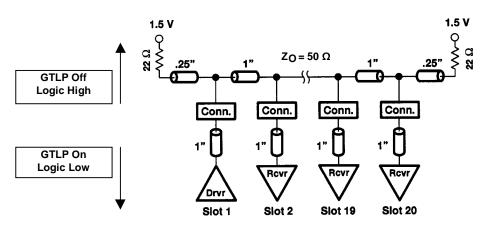

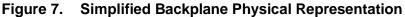

A typical single-bit distributed-capacitance open-drain/open-collector backplane physical representation is shown in Figure 5. Normally, backplanes are 4, 16, 32, 64, 128, or more bits wide, with each bit identical to the representation in Figure 5. Both GTL and GTLP devices need a pullup resistor to pull the bus high. In this representation, the device in slot 1 is on, pulling the trace below 0.55 V, and providing a valid low. Receivers in slots 2 through 20 detect that the signal is low and, if not in the high-impedance state, transmit a low logic level to the A-port daughter-card side. Although not shown, each driver/receiver on the daughter card is a transceiver that can be configured to transmit or receive signals from the backplane. When the device in slot 1 is turned off, the bit is pulled high to 1.5-V by the  $22-\Omega$  termination resistors. The receivers in slots 2 through 20 detect that the signal is now high and transmit a high logic level to the daughter card. This process is repeated multiple times, with any card being able to transmit low signals onto the backplane. This can be done, even with multiple devices at the same time (wired-OR), without bus contention. This example assumes true logic.

Figure 5. GTLP Open-Drain Backplane Physical Representation

GTLP devices are offered in two drive levels to match the termination-resistance value. For best signal integrity and incident-wave switching, the termination resistor should match or be smaller than the effective trace impedance. The effective trace impedance and, hence, the optimum termination-resistance value, varies, based on stub length, device  $C_{io}$ , slot pitch, and type of connector. Medium-drive (50 mA) devices are good replacements for existing TTL/LVTTL devices where higher frequencies are needed, but lower power consumption is a concern. These devices should be used with termination-resistor values  $\geq$ 38- $\Omega$ . High-drive (100 mA) devices are best for replacing ABTE/FB+ devices where lower termination resistor values (22  $\Omega$  to 38  $\Omega$ ) are required. Either medium- or high-drive devices can be used with higher resistance (e.g., 60  $\Omega$ ) termination resistors, with the only outcome being the device pulls V<sub>OL</sub> to a lower level, closer to GND, and probably poorer signal integrity, unless the effective trace impedance also is 60  $\Omega$ .

Incident-wave switching ensures that the first received signal during a transition (low to high or high to low) is valid, and reduces wait time. Reflected-wave switching requires additional wait time as shown in Figure 6.

|            | SWITCHING WITH THE<br>INCIDENT WAVE                                              | SWITCHING WITH THE<br>REFLECTED WAVE                                                                      |

|------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| A⇒B        | t <sub>pd Driver</sub> + t <sub>pd Receiver</sub><br>= 5 ns + 5 ns = 10 ns       | $t_{pd Driver} + t_{pd Line} + t_{pd Line} + t_{pd Receiver}$<br>= 5 ns + 10 ns + 10 ns + 5 ns = 30 ns    |

| A⇒C        | $t_{pd Driver} + t_{pd Line} + t_{pd Receiver}$<br>= 5 ns + 10 ns + 5 ns = 20 ns | t <sub>pd Driver</sub> + t <sub>pd Line</sub> + t <sub>pd Receiver</sub><br>= 5 ns + 10 ns + 5 ns = 20 ns |

| Worst case | 20 ns                                                                            | 30 ns                                                                                                     |

Additional information on incident-wave switching is in the *Fast GTLP Backplanes With the GTLPH1655* application report, literature number SCBA015A.

In summary, GTLP is a bidirectional translator (5-V CMOS, TTL or LVTTL to GTLP, and GTLP to LVTTL or TTL) that facilitates significantly higher frequencies (>80 MHz) and higher data throughput in multipoint, heavily loaded, distributed-capacitance backplane applications because the B-port GTLP output transistors produce these features:

- Reduced voltage swing (<1 V), which reduces EMI over TTL solutions.

- Optimized OEC with low slew rates (0.35 to 0.5 V/ns), which minimizes overshoot in distributed loads.

- Open-drain configuration with matched termination resistors ( $\geq$ 22  $\Omega$  high drive or  $\geq$ 38  $\Omega$  medium drive), which ensures incident-wave switching and optimum signal integrity.

- I<sub>OFF</sub>, PU3S, and BIAS V<sub>CC</sub> precharge circuitry prevent data disturbance during card insertion or removal, permitting full live-insertion capability.

#### 8 What is distributed capacitance?

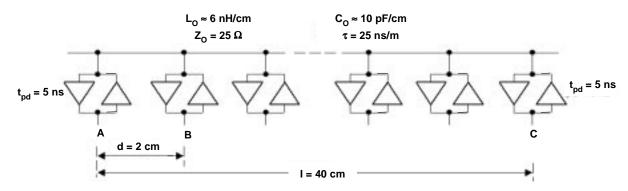

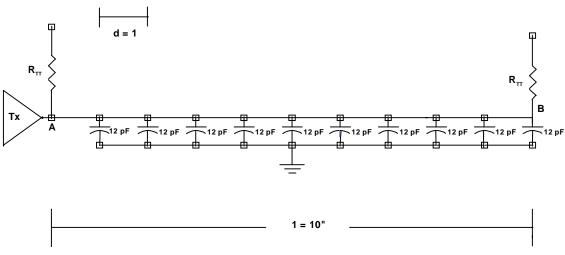

Figure 7 is a simplified backplane physical representation, where an equivalent capacitive load of 12 pF replaces the receivers. The transmitter also has an equivalent capacitive load of 12 pF.

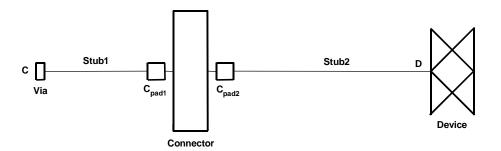

The total capacitance  $(C_t)$  of each card is calculated by summing all the capacitive components associated with the transceiver and the connection to the backplane. Figure 8 shows a typical connection scheme between the backplane stripline and the transceiver device on the daughter card. Point C is the connection to the backplane stripline, and point D is the connection to a transceiver integrated circuit. The total capacitance at point C is the sum of each of the elements in the connection chain.

The capacitance in the chain illustrated in Figure 8 is summed as follows:

$C_{stub1}$  = capacitance of Stub1 = 0.0625 inch  $\times$  2.6 pF/inch = 0.16 pF

$C_{cpad1}$  = capacitance of  $C_{pad1}$  = 0.5 pF

$C_{con}$  = capacitance of connector = 0.74 pF

$$C_{cpad2}$$

= capacitance of  $C_{pad2}$  = 0.5 pF

$C_{stub2}$  = capacitance of Stub2 = 1 inch × 2.6 pF/inch = 2.6 pF

C<sub>io</sub> = typical input/output capacitance of device = 7 pF

$$C_{t} = C_{via} + C_{stub1} + C_{cpad1} + C_{con} + C_{cpad2} + C_{stub2} + C_{io}$$

$$C_t = 0.5 + 0.16 + 0.5 + 0.74 + 0.5 + 2.6 + 7$$

$$C_{t} = 12 \, pF$$

This total capacitance ( $C_t$ ) of 12 pF is placed at point C on the backplane for every transceiver. With all the slots filled, the 10-inch transmission line has ten 12-pF capacitors and one transmitter (12 pF) distributed at 1-inch intervals.

Total capacitance then can be distributed uniformly across the transmission line at an equivalent rate of capacitance per inch ( $C_d$ ). The total capacitance per distance is the distributed capacitance. The higher the total card capacitance and the closer the card spacing (slot pitch) the heavier the backplane loading.

The distributed capacitance equals the total capacitance divided by the separation, or  $C_d = C_t/d$ . In our example,  $C_d = 12 \text{ pF}$  per 1 inch or 472 pF per meter. The new effective trace impedance  $Z_{O(eff)}$  and effective propagation delay ( $t_{pd(eff)}$ ) can be calculated using the following equations.  $C_o$  is the characteristic capacitance, which is dependent on  $Z_O$  and is fixed.

$$Z_{O}(eff) = Z_{O} / \sqrt{1 + (C_{d}/C_{O})}$$

$$t_{pd}(eff) = t_{pd} \times \sqrt{1 + (C_{d}/C_{O})}$$

The distributed capacitance ( $C_d$ ) affects both the propagation delay and the characteristic impedance of the transmission line. A larger  $C_d$  (higher  $C_t$  and/or smaller d) results in lower effective trace impedance ( $Z_{O(eff)}$ ) and a higher effective propagation delay ( $t_{pd(eff)}$ ).

This illustrates why the termination-resistor values should be lower than the typical  $50-\Omega$  natural transmission-line impedance in multipoint applications. Matching the termination resistor with the effective trace impedance ensures incident-wave switching and better signal integrity. Higher-drive (100 mA) devices are offered because termination values lower than 38  $\Omega$  often are required.

For example, in a 20-slot, slot pitch = 0.94 inch backplane, the characteristics in Table 1 are observed.

|                       | Unloaded (Natural) Embedded<br>Microstrip Trace |      |                                                    |     |                            |                            | Card $C_t^{\dagger}$ |  |

|-----------------------|-------------------------------------------------|------|----------------------------------------------------|-----|----------------------------|----------------------------|----------------------|--|

| Ζ <sub>Ο</sub><br>(Ω) | •                                               |      | Z <sub>O(eff)</sub> <sup>t</sup> pd<br>(Ω) (ns/in) |     | Z <sub>O(eff)</sub><br>(Ω) | <sup>t</sup> pd<br>(ns/in) | (pF)                 |  |

| 48                    | 142                                             | 2.99 | 37                                                 | 183 | 18                         | 382                        | 15                   |  |

| 90                    | 165                                             | 1.84 | 62                                                 | 239 | 26                         | 570                        | 16.2                 |  |

| Table 1. | Backplane Characteristics, 20 Slots at 0.94-Inch Slot Pitch |

|----------|-------------------------------------------------------------|

|----------|-------------------------------------------------------------|

<sup>†</sup> Different stub lengths provide a unique C<sub>t</sub> for each bit on the same daughter card.

Table 1 clearly shows that, in a heavily loaded backplane with the 48- $\Omega$  natural Z<sub>O</sub>, the termination resistance should go as low as 18  $\Omega$ , but is limited to 22  $\Omega$  by the GTLP high-drive maximum recommended I<sub>OI</sub>. Increasing the natural Z<sub>O</sub> to 90  $\Omega$  can change the termination

resistor to 26  $\Omega$ , a value that is within the capacity of the high-drive devices and better approximates what the medium-drive devices can handle. The disadvantage is that the backplane time of flight is about 50% higher. Typical card capacitance will be between 12 pF and 18 pF, depending on device C<sub>io</sub> and stub length, with stub length being most critical. Stub length always should be less than one inch for best backplane performance. Lower C<sub>t</sub> always is better.

For best signal integrity, termination resistor  $R_{TT}$  should equal the loaded-trace impedance  $(Z_{O(eff)})$ . A lower value for  $R_{TT}$  could be used to compensate for possible variations of the device typical  $C_{io}$ , up to the maximum  $C_{io}$  value.

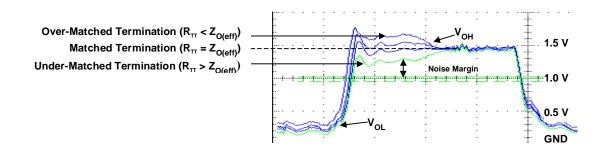

The waveforms in Figure 9 show the effect on signal integrity in over-matched and undermatched termination conditions.  $R_{TT}$  should be less than or equal to  $Z_{O(eff)}$  for optimum signal integrity and upper noise margin.

#### Figure 9. GTLP Waveform Under Different R<sub>TT</sub> Conditions

The result of using an under-matched termination is that V<sub>OL</sub> will be closer to ground and the upper noise margin will be less, as is clearly shown in Figure 9.

The result of a matched termination is optimal upper and lower noise margins.

The result of using an over-matched termination is that V<sub>OL</sub> on the card farthest from the driver is higher and the lower noise margin is reduced.

More information on calculating distributed capacitance is in the *Basic Design\_Considerations for Backplanes* application report, literature number SZZA016A, at www.ti.com/sc/docs/apps/logic/appnotes.html under backplane logic.

#### 9 What are you going to do with GTL now that you have GTLP?

TI will continue to support and expand the GTL family because these devices are well suited for voltage-level translations, point-to-point applications, and lightly loaded bus onboard-memory applications, e.g., Intel<sup>™</sup> Pentium<sup>™</sup> microprocessors operate at GTL+ signal levels. Customers can switch between GTL and GTLP families, but must be aware of the differences in the edge rates. GTLP devices can be used in memory applications, but, due to the slower edge rates, the device propagation delay is longer. GTL devices should not be used in high-frequency heavily loaded backplanes.

Intel and Pentium are trademarks of Intel Corporation.

#### 10 How should I terminate GTL devices in short-distance applications?

GTL products are open drain, so they must be connected to  $V_{TT}$  via proper  $R_{TT}$  termination resistors. One question is that if GTL or GTLP is used to transmit signals on a daughter card, the distance is very short, about 4 cm to 6 cm. Do we need to position a  $R_{TT}$  termination resistor at both the driver and receiver? If so, can you provide the  $R_{TT}$  based on your experience? In such a condition, how can better results be obtained?

You need only to put the  $R_{TT}$  termination resistor at the receiver end of the transmission line. On the backplanes we recommend putting the termination resistors on both ends of the backplane because you do not know when slot 1 or 20 will be the transmitter or receiver, so you have to cover both cases. The  $R_{TT}$  value should equal the loaded-trace impedance whether or not you use one or two  $R_{TT}$  termination resistors. If two are used, the effective

resistance is reduced by a factor of two (i.e., 50  $\Omega$  at either end, the driver will see 25- $\Omega$  effective resistance) which means simply that the driver has to be able to sink more current. For this short trace and lower loading you could probably use a single termination resistor at the receiver that is about 10  $\Omega$  less than the natural trace impedance (i.e., If Z<sub>0</sub> is 50  $\Omega$ , use

40  $\Omega$ .). Using the GTLP EVM, we have removed the driver termination and the signal integrity was satisfactory, however, when the receiver termination was removed and only the driver side was terminated, signal integrity was poor. As you would expect, it did not work when both terminations were removed.

#### 11 What is the advantage of using GTLP in my backplane?

Increasing bandwidth and data throughput speeds are major issues today for many systems, as our world becomes increasingly interconnected. TI has taken what it has learned about the use of GTL over the last four years and applied this expertise and knowledge to future backplane-based applications using GTLP devices.

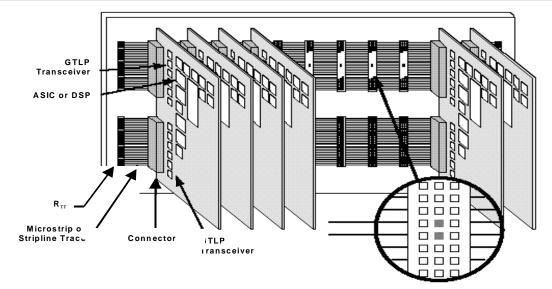

TI's GTLP family has been designed specifically for optimum signal integrity in multipoint, heavily loaded, distributed-capacitance backplanes like those shown in Figure 10. These improvements allow higher data throughput in the same bit-width backplanes that are currently being used and provide an easy migration from current TTL/LVTTL and BTL/FB+ backplane drivers to GTLP devices.

#### Figure 10. Heavily Loaded, Distributed-Capacitance Backplane Installation

GTLP devices allow higher frequencies on the backplane because of the improved signal-integrity/incident-wave switching the results from the reduced swing (<1 V), lower slew rate (0.35 V/ns to 0.5 V/ns), and matched termination resistors.

Additionally, GTLP fully supports live insertion, a capability that is imperative in high-availability communications and networking applications.  $I_{off}$  and PU3S provide hot-insertion capability, while the BIAS  $V_{CC}$  precharge circuitry precharges the B-port input/outputs to the threshold voltage. This protects active data on the backplane from voltage spikes or glitching, and provides true live-insertion capability.

GTLP devices are designed and manufactured in an advanced CMOS process that reduces static-power consumption.

GTLP devices are 5-V tolerant because, although most applications are migrating to 3.3 V, or lower, some existing circuits/devices on the board remain at 5 V.

GTLP is offered in a wide variety of packaging options and pinouts that are similar to previous-generation devices. This helps simplify the designer's task of migrating to a GTLP-based backplane. High-drive devices are identical to the comparable medium-drive devices, except for the addition of five ground, two V<sub>CC</sub>, and one edge-rate control (ERC) pins. The additional ground and V<sub>CC</sub> pins reduce ground and V<sub>CC</sub> supply noise, thus providing additional noise margin. The ERC pin allows the selection of either a slow or fast edge rate by holding the control pin at V<sub>CC</sub> or ground. The faster edge rate reduces the propagation delay and allows higher frequency operation in an optimally terminated backplane.

Lumped loads normally are associated with point-to-point applications. However, GTLP devices have been designed into actual backplane netlists and a resistance/inductance/ capacitance (RLC) network that closely matches the results in a backplane. TI's GTLP devices are tested into a lumped load, as are all other devices offered by TI and other semiconductor manufacturers. Engineers are using GTLP devices in high-performance distributed-capacitance loads and the actual switching characteristics are radically different from the lumped loads that are specified in the data sheet. TI SPICE-modeled values using the RLC network are included in the data sheet to better help engineers understand backplane effects. In summary, the data-sheet switching-characteristics into the lumped-load parameter values are going to look ugly but the actual performance of the device in a distributed load is going to be beautiful.

#### 12 What is the difference between GTLP and LVDS?

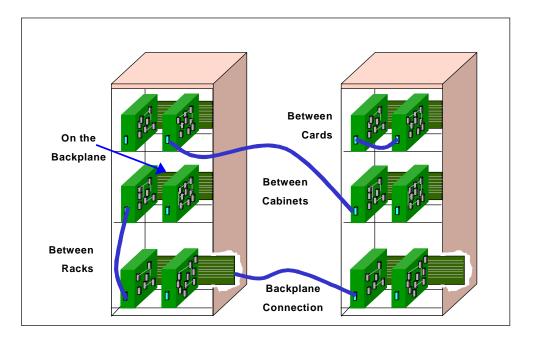

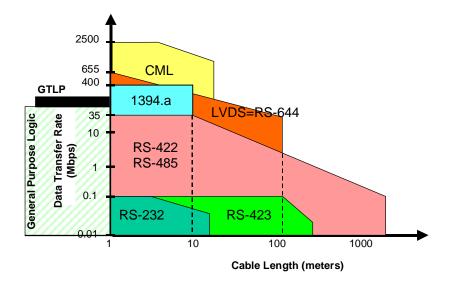

GTLP is a single-ended low-voltage-swing (<1 V) standard, whereas LVDS is a differential low-voltage-swing (350 mV, typical) standard. Single-ended devices require only one trace per bit of data, while differential devices require two traces for each bit of data. Differential devices, e.g., LVDS, LVDM (backplane optimized LVDS), SERDES, Wizard, etc., work well for high-speed data transmission over long cables, such as between cabinets, cards, or racks, as shown in Figure 11, but they do not fit all applications where simplicity and lower cost of implementation indicate that single-ended devices are better for use in multislot backplane applications.

Figure 11. Various Equipment Connections

# 13 How does GTLP compare to other single-ended and differential bus solutions?

Reduced voltage swing, lower slew rate, and open-drain construction allow GTLP devices to operate at higher frequencies than TTL devices in parallel-backplane architecture. GTLP offers an alternative to high-data-throughput differential devices where parallel backplanes are the best solution and higher data throughput is now required (see Table 2).

| Device (typically 16245<br>function) | Bidirectional (B) or<br>Unidirectional (U) | V <sub>cc</sub> (V) | Tolerant to | Hot Insertion | Live Insertion | Number of Pins in the<br>Package | Number of Bits | Cost (\$ in DGG qty 999<br>Internet Price) | Card Interface Drive<br>(mA) | BP Interface Drive (mA) | I <sub>cc</sub> (mA - Output Low) | C <sub>io</sub> (pF - max) | Freq. Max BP (MHz) | Data Throughput Per<br>Package (Mbps -<br>Transparent Mode) | Data Throughput per<br>Bit-\$ (Mbps/bit\$) | Data Throughput per<br>Bit (Mbps/bit) |

|--------------------------------------|--------------------------------------------|---------------------|-------------|---------------|----------------|----------------------------------|----------------|--------------------------------------------|------------------------------|-------------------------|-----------------------------------|----------------------------|--------------------|-------------------------------------------------------------|--------------------------------------------|---------------------------------------|

|                                      |                                            |                     |             |               |                |                                  | S              | ingle-Ende                                 | d Bus Inter                  | face Solutio            | n                                 |                            |                    |                                                             |                                            |                                       |

| ABT                                  | В                                          | 5                   | 5           | Y             | N              | 48                               | 16             | \$1.92                                     | -32/+64                      | -32/+64                 | 32                                | 6 -typ                     | 33                 | 1,056                                                       | 34                                         | 66                                    |

| LVT                                  | В                                          | 3.3                 | 5           | Y             | N              | 48                               | 16             | \$2.17                                     | -32/+64                      | -32/+64                 | 5                                 | 10 - typ                   | 33                 | 1,056                                                       | 30                                         | 66                                    |

| ALVT                                 | В                                          | 3.3                 | 5           | Y             | Ν              | 48                               | 16             | \$3.09                                     | -32/+64                      | -32/+64                 | 5                                 | 6 - typ                    | 40                 | 1,280                                                       | 26                                         | 80                                    |

| GTLP Medium Drive                    | В                                          | 3.3                 | 5           | Y             | Y              | 48                               | 16             | \$5.00                                     | -24/+24                      | 50                      | 35*                               | 9                          | 80                 | 2,560                                                       | 32                                         | 160                                   |

| ABTE                                 | В                                          | 5                   | 5           | Y             | Y              | 48                               | 16             | \$5.01                                     | -12/+12                      | -60/+90                 | 48                                | 8                          | 45                 | 1,440                                                       | 18                                         | 90                                    |

| BTL/FB+                              | В                                          | 5                   | 5           | Y             | Y              | 52                               | 8              | \$10.47                                    | -3/+24                       | 100                     | 70                                | 5                          | 50                 | 800                                                         | 10                                         | 100                                   |

| GTLP High Drive                      | В                                          | 3.3                 | 5           | Y             | Y              | 56                               | 16             | \$5.85                                     | -24/+24                      | 100                     | 35*                               | 10                         | 100                | 3,200                                                       | 34                                         | 200                                   |

|                                      |                                            |                     |             |               |                |                                  |                | Differential                               | Bus Interfa                  | ace Solution            |                                   |                            |                    |                                                             |                                            |                                       |

| ECL/PECL                             | U                                          | 5                   | 5           | Ν             | Ν              | 24                               | 8              | \$10.20                                    | -3/+24                       | -25                     | 69                                |                            | 80                 | 640                                                         | 8                                          | 80                                    |

| TLK2500                              | В                                          | 2.5                 | 3.3         | Y             | N              | 64                               | 16             | \$36.70                                    | -1/+1                        | 1 Serial                | 135                               | Serial                     |                    | 2,500                                                       | 4                                          | 156                                   |

| LVDS386/387                          | U                                          | 3.3                 | 5           | Y             | Y              | 64                               | 16             | \$9.58                                     | -8/+8                        | 16 - Serial             | 70                                | Serial                     |                    | 10,080                                                      | 66                                         | 630                                   |

| LVDS93/94 SERDES                     | U                                          | 3.3                 | 5           | Y             | Y              | 64                               | 28             | \$3.50                                     | -4/+4                        | 5 - Serial              | 84                                | Serial                     |                    | 1,820                                                       | 19                                         | 65                                    |

Table 2.

Comparison of Single-Ended vs Differential Bus-Interface Solutions

The maximum backplane frequency is based on good backplane construction and termination techniques. The TLK, LVDS, and SERDES data throughputs are theoretical maximum values; actual data throughput rates are less.

Comparison of cost of GTLP versus other single-ended technologies shows that GTLP data throughput per bit-dollar is about the same as the most popular parallel technologies, such as ABT. Although GTLP costs about three times more than ABT, the GTLP data throughput is more than three times greater than ABT in heavily loaded backplanes. GTLP also is an excellent replacement for ABT or LVT in low-frequency applications where signal integrity is an important consideration.

Strong interest in point-to-point differential-backplane connections in high-end networking and 3G wireless base-station applications has been seen, although that requires dozens to hundreds of connections along a 19-inch backplane. Typically, telecom engineers dislike single-ended solutions because of past EMI, maximum system frequency, and power-consumption difficulties with older TTL solutions. The tradeoff is the ease of design of the single-end solution versus the low EMI, higher frequency, and lower power consumption of differential designs. GTLP provides massive throughput at lower EMI and power-consumption levels than TTL, which is what they're thinking of when they think single-ended. Throughput on the backplane using GTLP devices at lower cost and without serious EMI or crosstalk effects compares very favorably with point-to-point serial schemes.

Figure 12 allows you to pick the bus solution technology offered by TI that would be most appropriate, based on throughput and transmission distance.

More information on TI's vast array of parallel and serial technologies can be found in the *Comparing Bus Solutions* application report, literature number SLLA067.

More information on LVDS, LVDM, SERDES, Gigabit CMOS, and 1394 can be found on TI's semiconductor internet home page at www.ti.com/sc.

More information on GTLP can be found on TI's GTLP internet home page at www.ti.com/sc/gtlp.

#### 14 What is the maximum data throughput using GTLP?

Data throughput is a function of clock frequency times the bit width of the backplane. Increasing the maximum frequency or backplane bit width increases data throughput. GTLP devices can operate at speeds up to 175 MHz into a distributed load with good signal integrity.

A 32-bit backplane operating at 110-MHz clock frequency has a data transfer rate of 1.76 Gbit/s in single-edge latched-mode (data is transferred at one-half the clock frequency) applications to 7 Gbit/s in dual-edge transparent-mode applications.

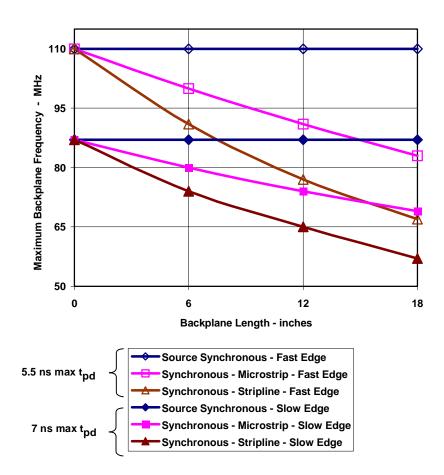

Data throughput in GTLP backplanes is now limited by timing requirements, not signal integrity, as in past backplane devices. Maximum frequency is a function of device maximum propagation delay ( $t_{pd}$ ), pin-to-pin skew, backplane construction or length, and how the clock is distributed (see Figure 13).

Figure 13. Maximum Backplane Frequency

Propagation delay is a function of the edge rate. Only high-drive GTLP devices are able to operate at both slow and fast edge rates, with a maximum  $t_{pd}$  of about 7 ns and 5.5 ns, respectively. Medium-drive devices operate only at the slow edge rate, with a maximum  $t_{pd}$  of about 7 ns. These are design goals, and actual values may be different.

Setup and hold times and skew are inherent in the device.

Backplane flight time depends on backplane length and construction (microstrip or stripline). Microstrip places the trace on top of the printed circuit board and does not reduce the flight time as much as stripline, but it is more susceptible to EMI. Stripline places the trace between printed circuit board dielectric layers and is less susceptible to EMI, but the signals are slower and, consequently, flight time is longer. Most high-quality backplanes use stripline construction to minimize EMI. Proper backplane layout and stub lengths of less than 1 inch help minimize backplane capacitance.

Most backplanes use a system clock that provides an absolute clock signal to all cards at the same time. Maximum system frequency is reduced based on backplane length, as shown in Figure 13, to accommodate the difference between the time-of-arrival of the driver card and receiver card clock signal (flight time), respectively. Source-synchronous operation is a technique in which the clock is sent with the system data as a relative clock signal. This means that there is no delay due to backplane flight time because the clock is sent along with the data. Flight time always is zero; therefore, maximum frequency is independent of backplane length.

Studies performed using the 19-inch 20-slot GTLP EVM with the SN74GTLPH1655 DGGR device show that the maximum frequency is 46 MHz in system-clock mode and 120 MHz in source-synchronous clock mode, and, for short time periods, 160 MHz in asynchronous mode.

In summary, maximum frequency (MHz) is the inverse of the maximum delay time (ns), i.e., 10 ns = 100 MHz. Maximum delay time depends on the sum of these factors:

- Maximum propagation delay

- Fast edge (5.5 ns)

- Slow edge (7 ns)

- Setup time (2.5 ns)

- Skew time (1 ns)

- Backplane flight time

- Source synchronous flight time is zero and is independent of backplane length because the clock is sent with the data

- Microstrip (1 ns/6 inches)

- Stripline (~2 ns/6 inches)

To improve backplane performance, review the *High-Performance Backplane Design With GTL+* application report, literature number SCEA011A, and *Basic Design Considerations for Backplanes* application report, literature number SZZA016A.

Additional information on calculating backplane impedance can be found at www.ultracad.com. There is detailed information on microstrip and stripline calculations and an impedance calculator that can be downloaded.

## 15 What is the difference between synchronous clock and source-synchronous clock?

Synchronous clock is an **absolute** clock in which each card receives the same clock signal at exactly the same time. A clock generator with clock lines running to each card provides this absolute clock. For the clock signal to arrive at each card at exactly the same time, the line length must be exactly the same. For cards closer to the clock board, the lines are mitered (run up and down, parallel to each other) to add distance to the line.

Source-synchronous clock is a **relative** clock. The driver card uses the incoming absolute clock signal for timing, but all receiver cards use the clock sent from the driver card. Since the driver card data and slightly delayed clock signal are sent at the same time, backplane length or flight time is not a factor in timing calculations, unlike the absolute clock, which has to account for the backplane length or flight time between the driver and receiver.

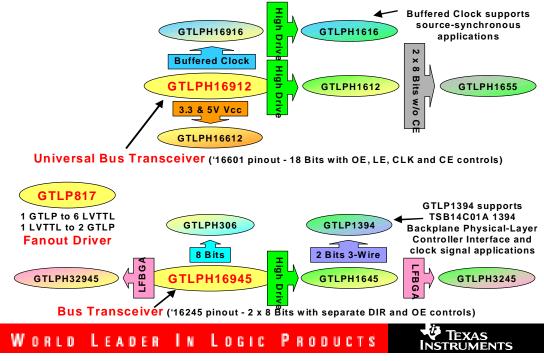

Additional information on source-synchronous operation was presented by Lee Sledjeski at DesignCon 2000, in which he discussed private source-synchronous clocks for every 16 bits of data to minimize delays due to device skew. The paper can be viewed at http://www.fairchildsemi.com/products/backplane/designcon/lsdcon2k.pdf. These private clocks can be implemented easily with the GTLPH16916 or the high-drive GTLPH1616; each has one delayed buffered clock bit for every 17 bits of data. This paper also discusses reducing the clock signal transmitted across the backplane by a factor of one-half as a way to transfer data at the full system clock rate, i.e., data rate equals clock rate, which is 110 MHz.

#### 16 What GTLP devices are available and how much will they cost?

The first wave of TI's GTLP devices comprises seven medium-drive and six high-drive devices. They are offered in ultra compact (LFBGA/VFBGA), small (TVSOP), medium (TSSOP), or large (SOIC or SSOP) packages. Pricing is two to three times higher than standard LVTTL/TTL backplane drivers, but GTLP devices allow two to four times higher maximum backplane frequencies, providing higher data throughput without migrating to more complex serial devices. Because signal integrity is superior in distributed loads, it also makes sense to use GTLP in low-frequency applications where the noise margin using HC, ABT, or LVT is not acceptable because of the weaker drive and poorer signal integrity. GTLP pricing is the same or less than TI's current GTL pricing (see Table 3).

Obtain the data sheet at www.ti.com/sc/gtlp. Go to www.ti.com/sc/package for package drawings, symbolization, layout, and thermal-performance information.

| SN74GTLP | Function                  | Bits      | Pin Count | SOIC | SSOP | TSSOP | TVSOP | BGA | Suggested<br>Resale Price<br>(1000 Quantity) |

|----------|---------------------------|-----------|-----------|------|------|-------|-------|-----|----------------------------------------------|

|          | Med                       | dium Driv | /e (50 n  | ıA)  |      |       |       |     |                                              |

| H306     | Bus Transceiver           | 8         | 24        | DW   |      | PW    | DGV   |     | \$4.65                                       |

| 817      | 1:6 Fanout Driver         | NA        | 24        | DW   |      | PW    | DGV   |     | \$5.40                                       |

| H16612   | Universal Bus Transceiver | 18        | 56        |      | DL   | DGG   |       |     | \$7.35                                       |

| H16912   | Universal Bus Transceiver | 18        | 56        |      |      | DGG   | DGV   |     | \$7.90                                       |

| H16916   | UBT with Buffered Clock   | 17        | 56        |      |      | DGG   | DGV   |     | \$7.90                                       |

| H16945   | Bus Transceiver           | 2 x 8     | 48        |      |      | DGG   | DGV   | GQL | \$5.00                                       |

| H32945   | Bus Transceiver           | 4 x 8     | 96        |      |      |       |       | GKE | \$10.50                                      |

|          | Hi                        | gh Drive  | (100 m    | A)   |      |       |       |     |                                              |

| 1394     | Transceiver               | 2         | 16        | D    |      | PW    | DGV   |     | \$3.75                                       |

| H1612    | Universal Bus Transceiver | 18        | 64        |      |      | DGG   |       |     | \$9.15                                       |

| H1616    | UBT with Buffered Clock   | 17        | 64        |      |      | DGG   |       |     | \$9.15                                       |

| H1645    | Bus Transceiver           | 2 x 8     | 56        |      |      | DGG   | DGV   | GQL | \$5.85                                       |

| H1655    | Universal Bus Transceiver | 2 x 8     | 64        |      |      | DGG   |       |     | \$9.15                                       |

| H3245    | Bus Transceiver           | 4 x 8     | 114       |      |      |       |       | GKF | \$12.25                                      |

Table 3. GTLP Family Offerings

Relevant package application information is contained in the following reports:

Thin Very Small-Outline Package (TVSOP) application report, literature number SCBA009C.

32-Bit Logic Families in LFBGA Packages 96 and 114 Ball Low-Profile Fine-Pitch BGA Packages application report, literature number SCEA014.

*Comparison of Electrical and Thermal Parameters of Widebus SMD and LFBGA Packages* application report, literature number SCYA007.

## 17 These function numbers are different. How do they compare to normal logic functions?

When the GTL family was introduced, it was decided to differentiate GTL function numbers from other similar logic functions because of the V<sub>ref</sub> pin and the reduced B-port GTL signal levels. The first GTL device (SN74GTL16612) has exactly the same pinout as the 3.3-V V<sub>CC</sub> '16601 universal bus transceiver, except that the two V<sub>CC</sub> pins on the B-port side serve different purposes. Pin 34 is used for the GTL differential V<sub>ref</sub> input and pin 50 is used for the 5-V V<sub>CC</sub> that powers the GTL circuitry. The first GTLP device is the SN74GTLPH16612, which is identical to the SN74GTL16612, except for the improved B-port circuitry that allows better performance in distributed loads. Based on the SN74GTLPH16612, other existing GTL devices, and TI's device-naming convention, the names of the additional GTLP devices were selected as shown in the migration summary below.

Figure 14. GTLP Migration Summary

GTLP device naming considerations are:

- The 16XXX and 32XXX function numbers signify Widebus<sup>™</sup> (16 to 18 bits) and Widebus+<sup>™</sup> (32 to 36 bits) bit widths. Typically, octals are XXX only.

- Function numbers of XX9XX signify single-V<sub>CC</sub> operation and the incorporation of BIAS V<sub>CC</sub>.

- Medium-drive devices are either three or five digits. High-drive devices have the "9" removed and are four digits long to conform to the prior BTL/FB+ high-drive device-naming convention.

- The 2-bit high-drive 1394 is designed uniquely to support the 1394 backplane physicallayer controller and, therefore, was named GTLP1394. Application information is included in the data sheet. The GTLP1394 is also very useful in providing 2-bit GTLP clock signals in backplane applications.

- "H" is added after the GTLP family name if bus hold is featured on the A-port I/O pins. Typical 1394 and 817 applications do not require bus hold, so bus hold was not included in these devices. Bus hold is not required on B port I/O pins because the termination resistors keep the bit high if it is not actively pulled low by the device.

#### 18 I know what a bus transceiver is, but what is a UBT™?

A UBT<sup>™</sup> device performs numerous functions that are done by other logic functions by proper selection of their OE, LE, and CLK control pins ('16500 or '16501 functions) or their OE, LE, CLK, and CE control pins ('16600 or '16601 functions). The '16601 logic function is shown in Table 4.

|      |      |        | FUN      | CHON   | TABLET           |                           |  |

|------|------|--------|----------|--------|------------------|---------------------------|--|

|      |      | INPUTS |          | OUTPUT | NODE             |                           |  |

| CEAB | OEAB | LEAB   | CLKAB    | Α      | В                | MODE                      |  |

| Х    | Н    | Х      | Х        | Х      | Z                | Isolation                 |  |

| L    | L    | L      | н        | Х      | B0‡              |                           |  |

| L    | L    | L      | L        | х      | в₀‡<br>В₀§       | Latched storage of A data |  |

| Х    | L    | Н      | х        | L      | L                | Trenerart                 |  |

| Х    | L    | н      | х        | н      | н                | Transparent               |  |

| L    | L    | L      | <b>↑</b> | L      | L                | Cleaked storage of A data |  |

| L    | L    | L      | Ŷ        | н      | н                | Clocked storage of A data |  |

| Н    | L    | L      | х        | Х      | в <sub>0</sub> § | Clock inhibit             |  |

### Table 4. '16601 Logic Functions

$^\dagger$  A-to-B data flow is shown. B-to-A data flow is similar but uses  $\overline{\text{OEBA}},$  LEBA, CLKBA, and  $\overline{\text{CEBA}}.$

<sup>‡</sup> Output level before the indicated steady-state input conditions were established, provided that CLKAB was high before LEAB went low

§ Output level before the indicated steady-state input conditions were established

UBT, Widebus, and Widebus+ are trademarks of Texas Instruments.

UBT devices can be used for many different logic functions, reducing the number of different devices you have to buy. This reduces the number of other types of devices that must be maintained in inventory. Ordering larger quantities of UBT devices can reduce the price. However, simpler functions normally are less expensive. Backplane applications usually require only bus-transceiver functionality. Other applications might need more complex functions. The functions available from a UBT device or UBT device with clock enable are listed in Table 5.

The GTLPH306 is a functional equivalent of the '245, the GTLPH16945 is a pin-for-pin functional equivalent of the '16245, and the GTLPH16912 is a pin-for-pin functional equivalent of the '16601.

| Function                                                            | 8 Bit                     | 9 Bit | 10 Bit | 16 Bit                  | 18 Bit        |

|---------------------------------------------------------------------|---------------------------|-------|--------|-------------------------|---------------|

| Transceiver                                                         | ` <b>245</b> , `623, `645 | `863  | `861   | ` <b>16245</b> , `16623 | `16863        |

| Buffer/driver                                                       | `214, `244, `541          |       | `827   | `16241, `16244, `16541  | `16825        |

| Latched transceiver                                                 | `543                      |       |        | `16543                  | `16472        |

| Latch                                                               | `373, `573                | `843  | `841   | `16373                  | `16843        |

| Registered transceiver                                              | `646, `652                |       |        | `16646, `16652          | `16474        |

| Flip-flop                                                           | `374, `574                |       | `821   | `16374                  |               |

| Universal bus driver                                                |                           |       |        |                         | `16835        |

| Standard UBT                                                        |                           |       |        |                         | `16500, `1650 |

|                                                                     |                           |       |        |                         |               |

| GTLPH1655 replaces above functi<br>CLKAB, CLKBA), but is at GTLP le |                           |       |        |                         | EAB, LEBA,    |

|                                                                     |                           |       |        |                         | EAB, LEBA,    |

| CLKAB, CLKBA), but is at GTLP le                                    | evels on the B port a     |       |        | o 8-bit sections.       | EAB, LEBA,    |

| Table 5. | <b>UBT Equivalent-Functions Table</b> |

|----------|---------------------------------------|

|----------|---------------------------------------|

#### 19 I need an alternate source. Are there any?

Several companies manufacture GTL and GTLP devices. Fairchild (FSC) entered the market in 1997. Pericom and Philips also recently entered the market.

Pericom's two released offerings closely match the FSC GTLP data-sheet specifications, and it is assumed that their other planned offerings will also.

Philips markets their GTL devices toward the bus on the card/microprocessor interface market much like TI's existing GTL family. The GTL family has faster edge rates and is not optimized for backplane applications.

TI offers a wide range of medium-drive GTLP devices, a wider range of high-drive GTLP devices, and the widest range of packaging offerings. These devices support the needs of the emerging high-data-throughput parallel-backplane market. Additionally, TI has included a BIAS  $V_{CC}$  feature in the medium- and high-drive GTLP devices in place of one of the  $V_{CC}$  pins, to support true live insertion. The BIAS  $V_{CC}$  circuitry is disabled when  $V_{CC}$  is applied; therefore, except for the precharge feature, the TI device is fully functional in competitors' sockets.

All devices occupying the comparable bit width/drive box in Table 6 are pin-for-pin functional equivalents.

All 816/817 devices have the same pinout. They are one GTLP input to six TTL/LVTTL outputs and one TTL/LVTTL input to two GTLP outputs, but are various drives and  $V_{CC}$ . Refer to the data sheet, then test each device to pick the best one for your application.

|                | TI - SN74           | IGTLP                      | Fairchild                                              | - GTLP                        | Pericom - GTLP      |            |  |  |

|----------------|---------------------|----------------------------|--------------------------------------------------------|-------------------------------|---------------------|------------|--|--|

| Bit Width      | Medium Drive        | High Drive                 | Medium Drive                                           | High Drive                    | Medium Drive        | High Drive |  |  |

| 32             | H32945              | H3245                      |                                                        |                               |                     |            |  |  |

| 18             | H16912              | H1612                      | 18T612                                                 |                               | 18T612              |            |  |  |

|                | ₩ <u>H16612</u>     |                            | <u>16612</u>                                           |                               | 16612A              |            |  |  |

| 17             | H16916              | H1616                      | 2 17T616                                               |                               |                     |            |  |  |

|                |                     |                            | 16616<br>16617                                         |                               | <u>16616</u>        |            |  |  |

|                |                     |                            | 💥 <u>16617</u>                                         |                               | <u>16617</u>        |            |  |  |

| 16             |                     | ₩H1655                     |                                                        | 16T1655                       |                     | 16T1655    |  |  |

|                | H16945              | H1645                      |                                                        |                               |                     |            |  |  |

| 8              | H306                |                            | 💥 8Т306                                                |                               | 8T306               |            |  |  |

| 6              | 817                 |                            | 🔆 <u>6C817</u>                                         |                               |                     |            |  |  |

|                |                     |                            | 6C817           6C816A           6C816           6C816 |                               |                     |            |  |  |

|                |                     |                            | 🔆 <u>6C816</u>                                         |                               | 2014 <u>6C816</u>   |            |  |  |

| 2              |                     | 1394                       |                                                        |                               |                     |            |  |  |

| .egend         |                     |                            |                                                        | •                             |                     |            |  |  |

| 16612 (underli | ne) = 3.            | .3- and 5-V or 5           | -V V <sub>CC</sub> operation                           |                               |                     |            |  |  |

|                | = R                 | eleased to Marl            | ket                                                    |                               |                     |            |  |  |

| 116912 (black) | = 3.                | .3-V V <sub>CC</sub> while | 18T612 (blue italics                                   | ) is 3.3-V V <sub>CC</sub> bi | ut not 5-V tolerant |            |  |  |

| ledium Drive = | 50 mA, High Drive : | = 100 mA                   |                                                        |                               |                     |            |  |  |

Table 6.

GTLP Device Cross-Reference

#### 20 Are the alternate-source devices identical?

While all GTLP devices operate in the same manner and have the same pinout and functionality, they are not all designed equally. The most important characteristic in GTLP devices is the B-port OEC circuitry and the corresponding edge rate. Faster edges perform poorly in backplane. In our demonstration backplane under the same conditions, the SN74GTLPH16612 had better signal integrity than the FSC GTLP16612, and the SN74GTLPH1655 had better signal integrity than the FSC GTLP16T1655. We believe that TI's GTLP devices exhibit excellent signal integrity due to the improved OEC and TI-OPC<sup>™</sup> circuitry. If the design is optimized for the worst-case performance of all devices that are used, FSC or Pericom GTLP can be used as an alternate source.

Additional differences in other manufacturers' devices are shown in Table 7.

|                                                               |                  | Number of Devices | 6       |

|---------------------------------------------------------------|------------------|-------------------|---------|

| Features                                                      | ті               | Fairchild         | Pericom |

| Total number of GTLP devices                                  | 13               | 10                | 7       |

| 3.3-V V <sub>CC</sub> operation                               | 12               | 5                 | 3       |

| Inputs/outputs 5-V tolerant                                   | All              | 6                 | 5       |

| I <sub>off</sub> – Partial power down <i>(protect device)</i> | All              | All               | All     |

| PU3S - Hot insertion (protect equipment)                      | 12               | 4                 | 1       |

| LFBGA package option                                          | 3                | None              | None    |

| Backplane (GTLP                                               | /B-Port) Options | •                 |         |

| BIAS V <sub>CC</sub> - Live insertion (protect data)          | 10               | 1                 | 1       |

| Output edge control                                           | All              | All               | All     |

| TI-OPC circuitry                                              | 11               | None              | None    |

| Edge-rate control                                             | 7                | 1                 | 1       |

| Medium drive (34/50 mA)                                       | 7                | 9                 | 6       |

| High drive (100 mA)                                           | 6                | 1                 | 1       |

| Functio                                                       | onality          |                   | •       |

| Transparent mode                                              | 12               | 7                 | 6       |

| Clocked mode                                                  | 5                | 6                 | 5       |

| Latched mode                                                  | 5                | 6                 | 5       |

| Clock enabled mode                                            | 4                | 5                 | 4       |

| Buffered clock option                                         | 2                | 3                 | 2       |

| 1-to-6 TTL/LVTTL fanout driver                                | 1                | 3                 | 1       |

#### Table 7. Comparison of GTLP Features

TI-OPC is a trademark of Texas Instruments.

#### 21 What is important about live insertion?

Many backplane systems in communications applications must remain operational 24 hours a day, 7 days a week. These systems cannot be shut down when a board is inserted or removed from the system, as frequently happens during regular maintenance or system upgrades, nor can active backplane data be disturbed.

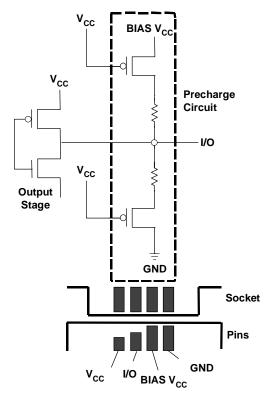

GTLP devices fully support live insertion with  $I_{off}$ , PU3S, and BIAS  $V_{CC}$  circuitry.

BIAS  $V_{CC}$  circuitry allows easy internal precharging of the daughter-card backplane connections to mid-threshold levels to prevent glitching active data during card insertion or removal.

In the typical connection sequence shown in Figure 15, the GND and BIAS V<sub>CC</sub> connections are made first to establish the GND plane and precharge the GTLP I/Os through the BIAS V<sub>CC</sub> circuitry to the 1.0-V ±50-mV threshold voltage. Next, the GTLP I/O pins are connected. Because the outputs are precharged to 1.0-V before connecting with the backplane, they do not glitch any active backplane data as they are mated. Finally, V<sub>CC</sub> is connected. As V<sub>CC</sub> ramps up, the BIAS V<sub>CC</sub> precharge circuitry is disabled and the device starts operating, presenting valid signals on the backplane.

Figure 15. Typical BIAS V<sub>CC</sub> Connection Sequence

#### 22 What is the total power consumption of an 18-bit GTLP driver?

When you look at backplane performance, you must take into consideration static drive and dynamic drive. The static output drive is the current needed to maintain a steady-state dc voltage level on an output. Dynamic output drive is the current available when an output switches output states. This drive is necessary to overcome reactive loading effects and can determine the switching speeds in your applications.

Total power consumption is defined as the sum of the static (measured by the device  $I_{CC}$ ), dynamic (measured by the device internal transistor switching), and output (measured by the external capacitive load) power of the device.

#### **Static Power**

$P_{\text{STAT}} = \sum \{V_{\text{CC}} [\text{share}_{L}(k) \times I_{\text{CCL}} + \text{share}_{H}(k) \times I_{\text{CCH}} + \text{share}_{Z}(k) \times I_{\text{CCZ}}]\} / n$

Where:

$\Sigma =$  Sum of k = 1 to n

$V_{CC}$  = Supply voltage

share (k) = Average percentage share of the k<sup>th</sup> output in a low state

share<sub>H</sub>(k) = Average percentage share of the  $k^{th}$  output in a high state

share<sub>7</sub>(K) = Average percentage share of the  $k^{th}$  output in a high-impedance state

I<sub>CCL</sub> = Device current consumption for static low at output

$I_{CCH}$  = Device current consumption for static high at output

$I_{CCH}$  = Device current consumption for high-impedance state at output

n = Total number of outputs in the device

Example 1:

A 50% duty cycle output waveform on all outputs force share<sub>L</sub>(k) and share<sub>H</sub>(k) to be 0.5 each. Share<sub>Z</sub>(k) is zero. Therefore, for an 18-bit device, sum k = 1 to 18, static power is:

$\mathsf{P}_{\mathsf{STAT}} = \sum \left[ \mathsf{V}_{\mathsf{CC}} \left( 0.5 \times \mathsf{I}_{\mathsf{CCL}} + 0.5 \times \mathsf{I}_{\mathsf{CCH}} + 0 \times \mathsf{I}_{\mathsf{CCZ}} \right) \right] / 18 = 0.5 \ \mathsf{V}_{\mathsf{CC}} \left( \mathsf{I}_{\mathsf{CCL}} + \mathsf{I}_{\mathsf{CCH}} \right)$

Example 2:

A 50% duty cycle output waveform on nine outputs and nine outputs at a fixed static low. share<sub>Z</sub>(k) is zero. Therefore, for an 18-bit device, sum k = 1 to 9, the static power is:

$P_{\text{STAT}} = \sum \left[ V_{\text{CC}} \left( 0.5 \times I_{\text{CCL}} + 0.5 \times I_{\text{CCH}} + 0 \times I_{\text{CCZ}} \right) \right] / 18 + \sum \left[ V_{\text{CC}} \left( 1 \times I_{\text{CCL}} + 0 \times I_{\text{CCH}} + 0 \times I_{\text{CCH}} + 0 \times I_{\text{CCH}} \right) \right] / 18$

$\mathsf{P}_{\mathsf{STAT}}$  = 0.5  $\times$  0.5  $\times$  V\_{CC} (I\_{CCL} + I\_{CCH}) + 0.5  $\times$  V\_{CC} (I\_{CCL}) = V\_{CC} (0.75  $\times$  I\_{CCL} + 0.25  $\times$  I\_{CCH})

$I_{CCL}$ ,  $I_{CCH}$ , and  $I_{CCZ}$  are identical for CMOS devices, but different for BiCMOS/bipolar devices. Normally, these are combined in CMOS-device data sheets, but, because both the GTL and GTLP families include both CMOS and BiCMOS devices, all values are included to preclude questions about whether all values are the same or only the maximum value was included.

#### **Dynamic Power**

While switching the outputs, most of the dynamic power is generated in the output structure of devices that have totem-pole configurations. Because GTL and GTLP devices have open-drain/collector outputs and no active pullup transistors, dynamic power caused by current spikes due to internal charging and discharging processes within the GTLP circuit can be approximated as a very small value that, in comparison to the static and output power, is negligible.

The Thin Very Small-Outline Package (TVSOP) application report, literature number SCBA009C, March 1997, at www.ti.com/sc/docs/psheets/abstracts/app/scba009.htm, provides more information on how to calculate dynamic power consumption for devices with totem-pole outputs.

#### **Output Power**

Output power per bit is:

$P_{OUT} = I_{OL} \times V_{OL} \times (1 - output duty cycle)$

Where

$I_{OL} = (V_{TT} - V_{OL}) / (R_{TT} / 2)$

Example:

For an output duty cycle of 60% (output stays high 60% of the cycle),

assuming V<sub>TT</sub> = 1.5 V, V<sub>OL</sub> = 0.55 V, and R<sub>TT</sub> = 38  $\Omega$ , then:

$$I_{OL} = (V_{TT} - V_{OL}) / (R_{TT} / 2) = (1.5 \text{ V} - 0.55 \text{ V}) / (38 \Omega / 2) = 50 \text{ mA}$$

$P_{OUT} = I_{OL} \times V_{OL} \times (1 - output duty cycle) = 50 \text{ mA} \times 0.55 \text{ V} \times (1 - 0.6) = 11 \text{ mW per bit}$

For an 18-bit device running all 18 bits at 60% output duty cycle,

$P_{OUT} = 18 \times 11 \text{ mW} = 198 \text{ mW}$

#### **Total Power Consumption**

Total power consumption for an 18-bit device operating at 3.3-V  $V_{CC}$  is calculated using the following equations. Nine outputs are switching at a 50% duty cycle with the other nine outputs at a fixed static low:

$I_{CC}$  = 50 mA,  $V_{TT}$  = 1.5 V,  $V_{OL}$  = 0.55 V, and  $R_{TT}$  = 38  $\Omega$

$P_{STAT} = V_{CC} (0.75 \times I_{CCL} + 0.25 \times I_{CCH}) = 3.3 V (0.75 \times 50 \text{ mA} + 0.25 \times 50 \text{ mA}) = 165 \text{ mW}$

$I_{OL} = (V_{TT} - V_{OL}) / (R_{TT} / 2) = (1.5 \text{ V} - 0.55 \text{ V}) / (38 \Omega / 2) = 50 \text{ mA}$

$P_{OUT}$  switching =  $I_{OL} \times V_{OL} \times (1 - output duty cycle)$  = 50 mA  $\times$  0.55 V  $\times$  (1 - 0.5) = 13.75 mW/bit

$P_{OUT}$  static low =  $I_{OL} \times V_{OL} \times (1 - output duty cycle) = 50 \text{ mA} \times 0.55 \text{ V} \times (1 - 0) = 27.5 \text{ mW/bit}$

There are nine switching outputs and nine static low outputs, therefore:

$P_{OUT} = 13.75 \text{ mW} \times 9 \text{ bits} + 27.5 \text{ mW} \times 9 \text{ bits} = 123.75 \text{ mW} + 247.5 \text{ mW} = 371.25 \text{ mW}$

The total power consumption is:

$P_{TOT} = P_{STAT} + P_{DYN} + P_{OUT} = 165 \text{ mW} + 0 \text{ mW} + 371.25 \text{ mW} = 536.25 \text{ mW}$

The junction temperature of the device never must exceed 150°C. To determine if the total power consumption exceeds the maximum junction temperature for a certain package, calculate junction temperature using the following equation:

$T_{J} = R_{\Theta JA} \times P_{TOT} + T_{A}$

In the previous example, assuming a 56-pin TSSOP (DGG) package with high-K board and no airflow, the junction temperature is: