# Operating ADS1605 and ADS1606 in 2X Mode: 10 MSPS

Wern Ming Koe, Yong-In Park, and Zhongnong Jiang

## ABSTRACT

This application report discusses the built-in 2X mode of the ADS1605 and ADS1606 analog-to-digital converters (ADCs). In 2X mode, the data rate doubles to 10 MSPS. This report presents a brief overview, pin configuration, timing requirements, summary of key performances, and typical characteristics. In addition, this report also shows the settling time, impulse response, and frequency response of the digital decimation filter.

#### Contents

| 1 | Overview                    | 3 |

|---|-----------------------------|---|

| 2 | Pin Configuration           | 3 |

| 3 | Timing Requirements         | 4 |

| 4 | Summary of Key Performances | 4 |

| 5 | Typical Characteristics     | 5 |

| 6 | Digital Decimation Filter   | 9 |

#### List of Figures

| 1                    | Pin Configuration for Doubling Output Data Rate                                                                                 | 3 |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------|---|

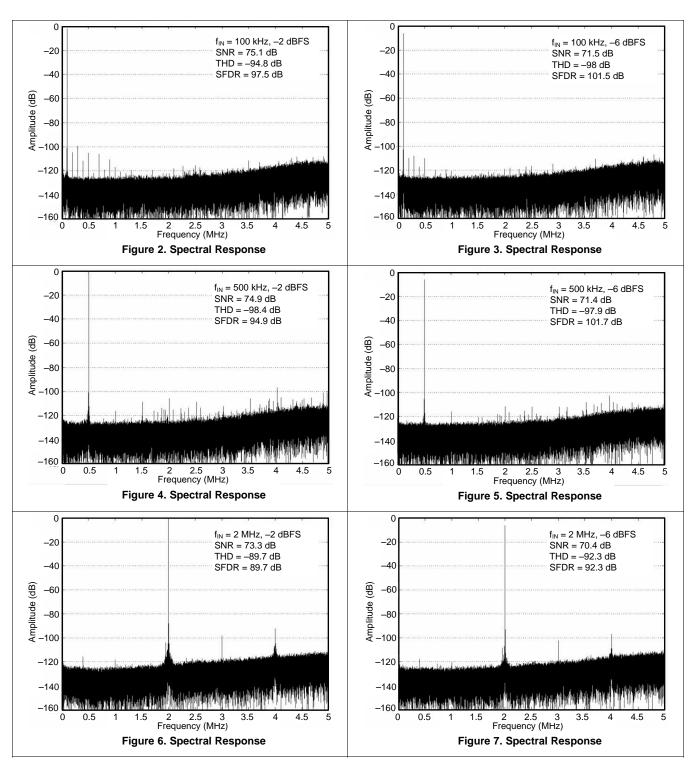

| 2                    | Spectral Response                                                                                                               | 5 |

| 3                    | Spectral Response                                                                                                               | 5 |

| 4                    | Spectral Response                                                                                                               | 5 |

| 5                    | Spectral Response                                                                                                               | 5 |

| 6                    | Spectral Response                                                                                                               | 5 |

| 7                    | Spectral Response                                                                                                               | 5 |

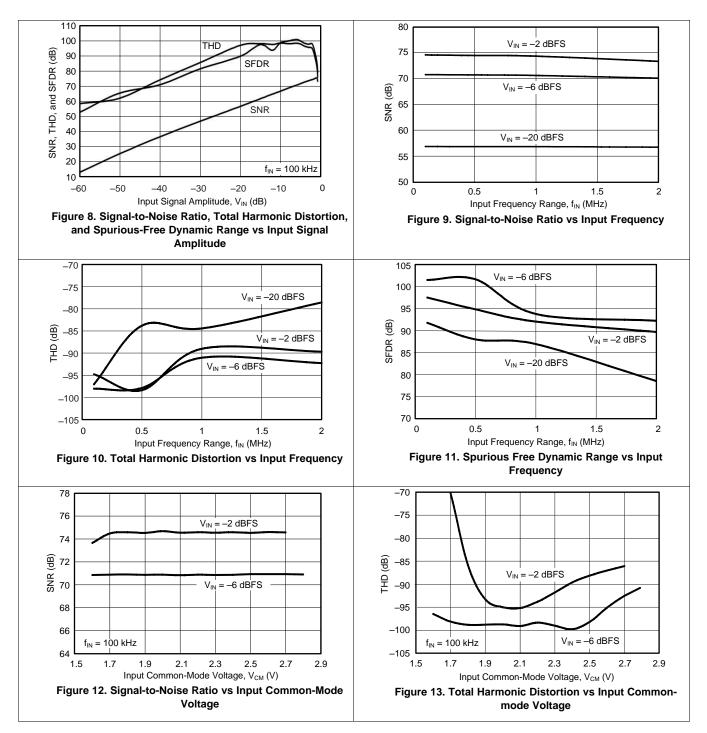

| 8                    | Signal-to-Noise Ratio, Total Harmonic Distortion, and Spurious-Free Dynamic Range vs Input Signal Amplitude                     | 6 |

| 9                    | Signal-to-Noise Ratio vs Input Frequency                                                                                        | 6 |

| 10                   | Total Harmonic Distortion vs Input Frequency                                                                                    | 6 |

| 11                   | Spurious Free Dynamic Range vs Input Frequency                                                                                  | 6 |

| 12                   | Signal-to-Noise Ratio vs Input Common-Mode Voltage                                                                              | 6 |

| 13                   | Total Harmonic Distortion vs Input Common-mode Voltage                                                                          | 6 |

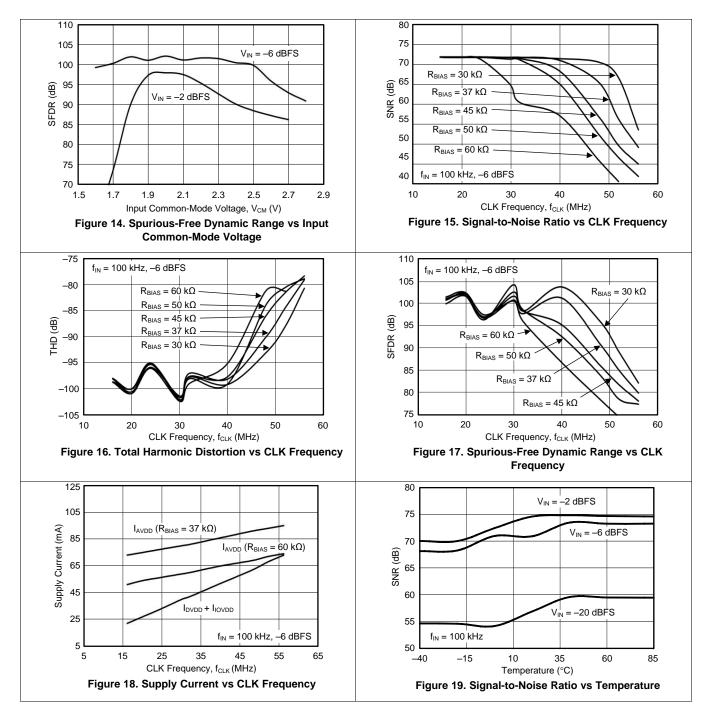

| 14                   | Spurious-Free Dynamic Range vs Input Common-Mode Voltage                                                                        | 7 |

| 15                   | Signal-to-Noise Ratio vs CLK Frequency                                                                                          | 7 |

| 16                   | Total Harmonic Distortion vs CLK Frequency                                                                                      | 7 |

| 17                   | Spurious-Free Dynamic Range vs CLK Frequency                                                                                    | 7 |

| 18                   | Supply Current vs CLK Frequency                                                                                                 | 7 |

| 19                   | Signal-to-Noise Ratio vs Temperature                                                                                            | 7 |

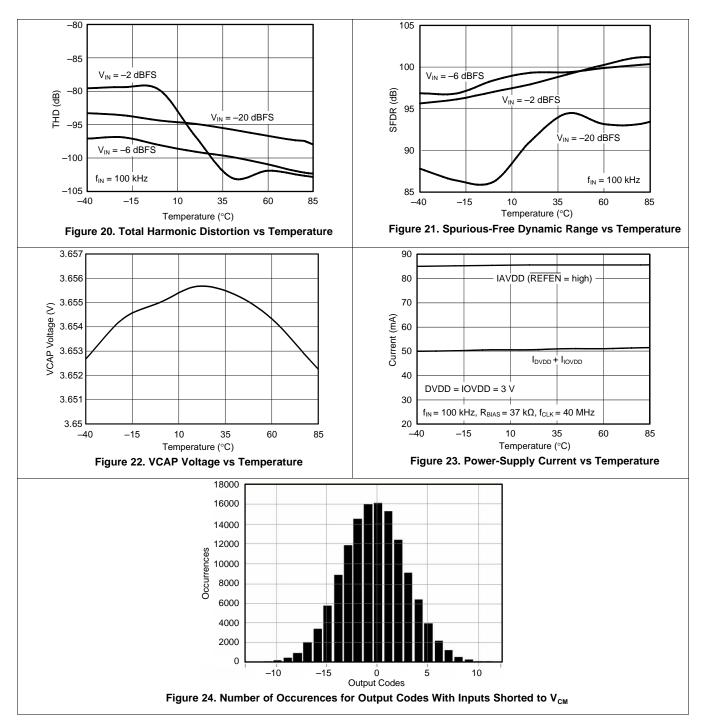

| 20                   | Total Harmonic Distortion vs Temperature                                                                                        | 8 |

| 21                   | Spurious-Free Dynamic Range vs Temperature                                                                                      | 8 |

| 22                   | VCAP Voltage vs Temperature                                                                                                     | 8 |

| 23                   | Power-Supply Current vs Temperature                                                                                             | 8 |

| 24<br>All trademarks | Number of Occurences for Output Codes With Inputs Shorted to $V_{\mbox{\tiny CM}}$ are the property of their respective owners. | 8 |

| 25 | Settling Time                     | 9  |

|----|-----------------------------------|----|

| 26 | Impulse Response                  | 9  |

| 27 | Frequency Response                | 10 |

|    | Pass-Band Ripple                  |    |

| 29 | Pass-Band Transition              | 10 |

| 30 | Frequency Response Out to 120 MHz | 10 |

|    |                                   |    |

## List of Tables

| 1 | Timing Requirements for Double Data Rate Mode | 4 |

|---|-----------------------------------------------|---|

| 2 | Typical Dynamic Performance                   | 4 |

| 3 | Digital Filter Characteristics                | 4 |

## 1 Overview

To complement the data sheet, this application report describes the performance when the 2XMODE input pin is taken high, placing the device in 2X mode. The oversampling ratio is reduced to four, which doubles the data rate, and also reduces group delay and settling time, and decreases SNR performance. In 2X mode, the ADS160x operates at a 10-MSPS data rate with 14-bit SNR performance.

## 2 Pin Configuration

The 2XMODE digital input sets the decimation rate of the digital filter.

When 2XMODE = low, the decimation rate = 8.

When 2XMODE = high, the decimation rate = 4.

For the 10-MSPS performance, 2XMODE must be set high. Decreasing the decimation rate from 8 to 4 doubles the data rate. For  $f_{CLK}$  = 40 MHz, the data rate then becomes 10 MSPS with this lower decimation value.

In addition, the group delay decreases to 0.9  $\mu s$  and the settling time becomes 1.3  $\mu s$  or 13 DRDY cycles. With the reduced decimation rate, the noise increases. Typical SNR performance degrades by 14 dB when the decimation rate is 4 versus 8. THD remains approximately the same. There is an internal pulldown resistor of 170 k $\Omega$  on the 2XMODE; however, TI recommends this pin be forced either high or low externally. See the respective pin assignments and locations diagram and the terminal functions table in the ADS160x data sheet. Figure 1 shows the pin configuration for doubling the output data rate.

Figure 1. Pin Configuration for Doubling Output Data Rate

Overview

## 3 Timing Requirements

The timing requirements indicated in the ADS160x data sheet that are affected when operating at double data rate are shown in Table 1. See the ADS160x data sheet for timing diagram and timing label definition.

| SYMBOL          | DESCRIPTION                                               | TYP | UNIT        |

|-----------------|-----------------------------------------------------------|-----|-------------|

| t <sub>4</sub>  | DRDY pulse with high or low         8 t <sub>1</sub> 1    |     | ns          |

| t <sub>12</sub> | Delay from DOUT active to valid DOUT (settling to 0.001%) | 13  | DRDY Cycles |

## 4 Summary of Key Performances

All specifications at T<sub>A</sub> = 25°C, AVDD = 5 V, DVDD = IOVDD = 3 V, f<sub>CLK</sub> = 40 MHz, External V<sub>REF</sub> = 3 V, 2XMODE = high, V<sub>CM</sub> = 2 V, and R<sub>BIAS</sub> = 37 k $\Omega$  (unless otherwise noted).

| TEST CONDITION                                      | SNR (dB) | SINAD (dB) | THD (dB) | SFDR (dB) |

|-----------------------------------------------------|----------|------------|----------|-----------|

| $f_{IN} = 100 \text{ kHz}, V_{IN} = -2 \text{ dB}$  | 75       | 75         | -95      | 98        |

| $f_{IN} = 100 \text{ kHz}, V_{IN} = -6 \text{ dB}$  | 72       | 71         | -98      | 102       |

| $f_{IN} = 100 \text{ kHz}, V_{IN} = -20 \text{ dB}$ | 58       | 57         | -97      | 91        |

| $f_{IN} = 500 \text{ kHz}, V_{IN} = -2 \text{ dB}$  | 75       | 74         | -98      | 95        |

| $f_{IN} = 500 \text{ kHz}, V_{IN} = -6 \text{ dB}$  | 71       | 71         | -98      | 102       |

| $f_{IN} = 500 \text{ kHz}, V_{IN} = -20 \text{ dB}$ | 58       | 57         | -84      | 88        |

| $f_{IN} = 2 \text{ MHz}, V_{IN} = -2 \text{ dB}$    | 73       | 73         | -90      | 90        |

| $f_{IN} = 2 \text{ MHz}, V_{IN} = -6 \text{ dB}$    | 70       | 70         | -92      | 92        |

| $f_{IN} = 2 \text{ MHz}, V_{IN} = -20 \text{ dB}$   | 58       | 70         | -79      | 79        |

<sup>(1)</sup> See the ADS160x data sheet for definition of measurement parameters.

## **Table 3. Digital Filter Characteristics**

| PARAMETER            | TEST CONDITONS      | MIN                                                 | ТҮР                                                        | MAX                                                         | UNIT |

|----------------------|---------------------|-----------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------|------|

| Pass band            | ±0.0003-dB ripple   | 0                                                   |                                                            | $2.2 \Biggl( \frac{f_{\text{CLK}}}{40 \text{ MHz}} \Biggr)$ | MHz  |

| Pass-band transition | -0.1-dB attenuation |                                                     | $3 \left( \frac{f_{\text{CLK}}}{40 \text{ MHz}} \right)$   |                                                             | MHz  |

|                      | -3-dB attenuation   |                                                     | $4.5 \left( \frac{f_{CLK}}{40 \text{ MHz}} \right)$        |                                                             |      |

| Stop band            | -40-dB attenuation  | $6.9 \left( \frac{f_{CLK}}{40 \text{ MHz}} \right)$ |                                                            | $33 \left( rac{f_{CLK}}{40 \text{ MHz}}  ight)$            | MHz  |

| Group delay          |                     |                                                     | $0.9 \left( \frac{40 \text{ MHz}}{f_{\text{CLK}}} \right)$ |                                                             | μs   |

| Settling time        | ±0.001%             |                                                     | $1.3 \left( \frac{40 \text{ MHz}}{f_{\text{CLK}}} \right)$ |                                                             | μs   |

## 5 Typical Characteristics

All specifications at  $T_A = 25^{\circ}$ C, AVDD = 5 V, DVDD = IOVDD = 3 V,  $f_{CLK} = 40$  MHz, External  $V_{REF} = 3$  V, 2XMODE = high,  $V_{CM} = 2$  V, and  $R_{BIAS} = 37$  k $\Omega$  (unless otherwise noted)

## **Typical Characteristics (continued)**

All specifications at T<sub>A</sub> = 25°C, AVDD = 5 V, DVDD = IOVDD = 3 V, f<sub>CLK</sub> = 40 MHz, External V<sub>REF</sub> = 3 V, 2XMODE = high, V<sub>CM</sub> = 2 V, and R<sub>BIAS</sub> = 37 k $\Omega$  (unless otherwise noted)

## **Typical Characteristics (continued)**

All specifications at  $T_A = 25^{\circ}$ C, AVDD = 5 V, DVDD = IOVDD = 3 V,  $f_{CLK} = 40$  MHz, External  $V_{REF} = 3$  V, 2XMODE = high,  $V_{CM} = 2$  V, and  $R_{BIAS} = 37$  k $\Omega$  (unless otherwise noted)

## **Typical Characteristics (continued)**

All specifications at T<sub>A</sub> = 25°C, AVDD = 5 V, DVDD = IOVDD = 3 V, f<sub>CLK</sub> = 40 MHz, External V<sub>REF</sub> = 3 V, 2XMODE = high, V<sub>CM</sub> = 2 V, and R<sub>BIAS</sub> = 37 k $\Omega$  (unless otherwise noted)

## 6 Digital Decimation Filter

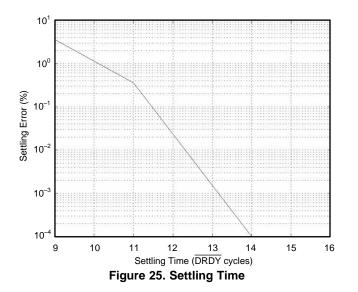

## 6.1 Settling Time

The settling time is an important consideration when measuring signals with large steps or when using a multiplexer in front of the analog inputs. The ADS160x digital filter requires time for an instantaneous change in signal level to propagate to the output. Make sure to allow the filter time to settle after applying a large step in the input signal, switching the channel on a multiplexer placed in front of the inputs, resetting the ADS160x, or when exiting the power-down mode. Figure 25 shows the settling error as a function of time for a full-scale signal step applied at t = 0 with 2XMODE = high. Figure 25 uses DRDY cycles for the time scale (X-axis). After 13 DRDY cycles, the settling error drops below 0.001%. For  $f_{CLK} = 40$  MHz, this corresponds to a settling time of 1.3  $\mu$ s.

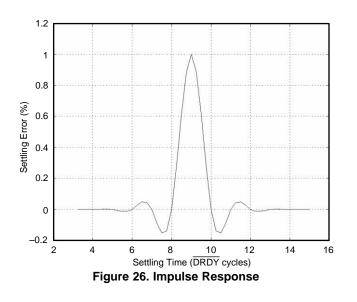

## 6.2 Impulse Response

Figure 26 plots the normalized response for an input applied at t = 0 with 2XMODE = high. The X-axis units of time are DRDY cycles. As shown in Figure 26, the peak of the impulse takes nine DRDY cycles to propagate to the output. For  $f_{CLK}$  = 40 MHz, a DRDY cycle is 0.1 µs in duration, and the propagation time (or group delay) is 9 × 0.1 µs = 0.9 µs.

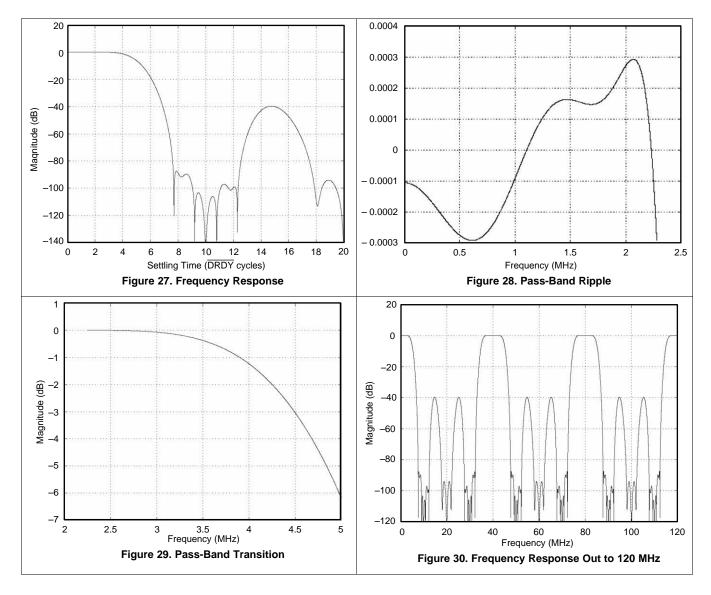

## 6.3 Frequency Response

The linear phase FIR digital filter sets the overall frequency response. The decimation rate is set to 4 (2XMODE = high) for all the figures shown in this section. Figure 27 shows the frequency response from dc to 20 MHz for  $f_{CLK}$  = 40 MHz. The frequency response of the ADS160x filter scales directly with CLK frequency. For example, if the CLK frequency is decreased by half (to 20 MHz), the values on the X-axis in Figure 27 must to be scaled by half, with the span becoming dc to 10 MHz. Figure 28 shows the passband ripple from dc to 2.2 MHz ( $f_{CLK}$  = 40 MHz). Figure 29 shows a closer view of the pass-band transition by plotting the response from 2 MHz to 5 MHz ( $f_{CLK}$  = 40 MHz). The overall frequency response repeats at multiples of the CLK frequency. To help illustrate this, Figure 30 shows the response out to 120 MHz ( $f_{CLK}$  = 40 MHz). Notice how the pass-band response repeats at 40 MHz, 80 MHz, and 120 MHz; important to consider, when there is high-frequency noise present with the signal. The modulator bandwidth extends to 100 MHz. High-frequency noises around 40 MHz and 80 MHz are not attenuated by either the modulator or the digital filter. This noise aliases back in-band, and reduces the overall SNR performance unless the noise is filtered out prior to the ADS1605. To prevent this, place an antialias filter in front of the ADS160x.

Within the 2.2-MHz pass band for  $f_{CLK} = 40$  MHz, the pass-band ripple decreased to ±0.0003 (when 2XMODE = high) compared to ±0.0025 (when 2XMODE = low). The -0.1-dB pass-band transition increases up to 3 MHz, while the -3-dB pass-band transition increases up to 4.5 MHz for  $f_{CLK} = 40$  MHz when 2XMODE = high.

## **Revision History**

## NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Ch | Changes from Original (December 2003) to A Revision             |   |  |

|----|-----------------------------------------------------------------|---|--|

| •  | Changed document to meet Texas Instruments formatting standards | 3 |  |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated