# LVDS Serdes 48 EVM Kit Setup and Usage

Boyd Barrie and Dung Nguyen

Mixed Signal DSP Solutions

### **Abstract**

This document describes the Texas Instruments (TI<sup>TM</sup>) LVDS Serdes 48 evaluation module (EVM) kit. The LVDS Serdes 48 EVM kit is used to evaluate and design high data throughput prototypes using the TI LVDS95 transmitter and LVDS96 receiver boards. The boards allow the designer to connect 21 bits of data and clock to the transmitter board where LVDS technology is available to serialize and transmit the data along four differential pairs (three data and one clock). The receiver board then deserializes the data, providing 21 bits of 3.3 V TTL data and clock.

The transmitter and receiver boards can be used to evaluate device parameters while acting as a guide for high-speed board layout. The high-speed LVDS interface uses a 50  $\Omega$  controlled-impedance parallel cable available in various lengths. The low-speed interface uses a standard 50 pin parallel ribbon cable. Overall, the designer can use the EVM kit as a tool for successful evaluation and design of an end product.

### **Contents**

| ntroduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| VDS Serdes 48 EVM Kit Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3 |

| VDS Serdes 48 EVM Boards Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| Typical Test and Setup Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

| Fest Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

| PCB Transmission Line Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

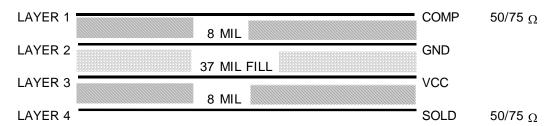

| ayer Construction for Transmitter/Receiver Boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |

| Appendix A. Schematics, Board Layouts, and MDR Cable Assembly Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

| appointment of the matter, bear a Layeste, and men out of the month of the matter of t |   |

### **Figures**

| Figure 1. LVDS Serdes 48 EVM Test Configuration                                            | 5  |

|--------------------------------------------------------------------------------------------|----|

| Figure 2. Eye Diagram Taken RX(B) Across 2 m of Cable at 65 MHz                            |    |

| Figure 3. Eye Diagram Taken RX(B) Across 5 m of Cable at 65 MHz                            |    |

| Figure 4. Eye Diagram Taken RX(B) Across 10 m of Cable at 65 MHz                           |    |

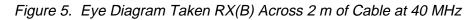

| Figure 5. Eye Diagram Taken RX(B) Across 2 m of Cable at 40 MHz                            |    |

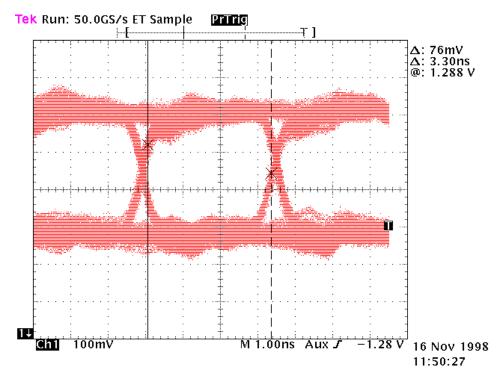

| Figure 6. Eye Diagram Taken RX(B) Across 5 m of Cable at 40 MHz                            |    |

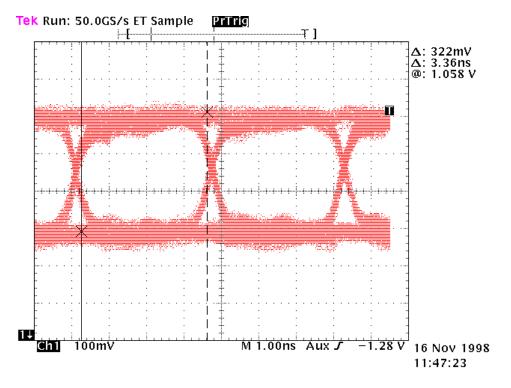

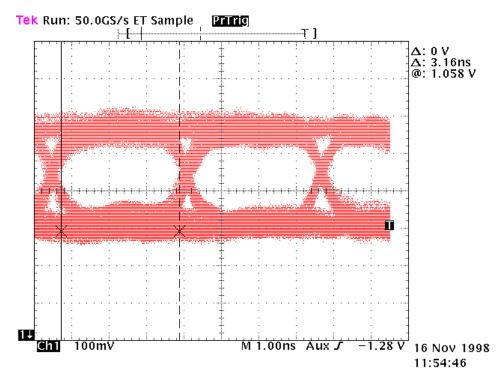

| Figure 7. Eye Diagram Taken RX(B) Across 10 m of Cable at 40 MHz                           | 9  |

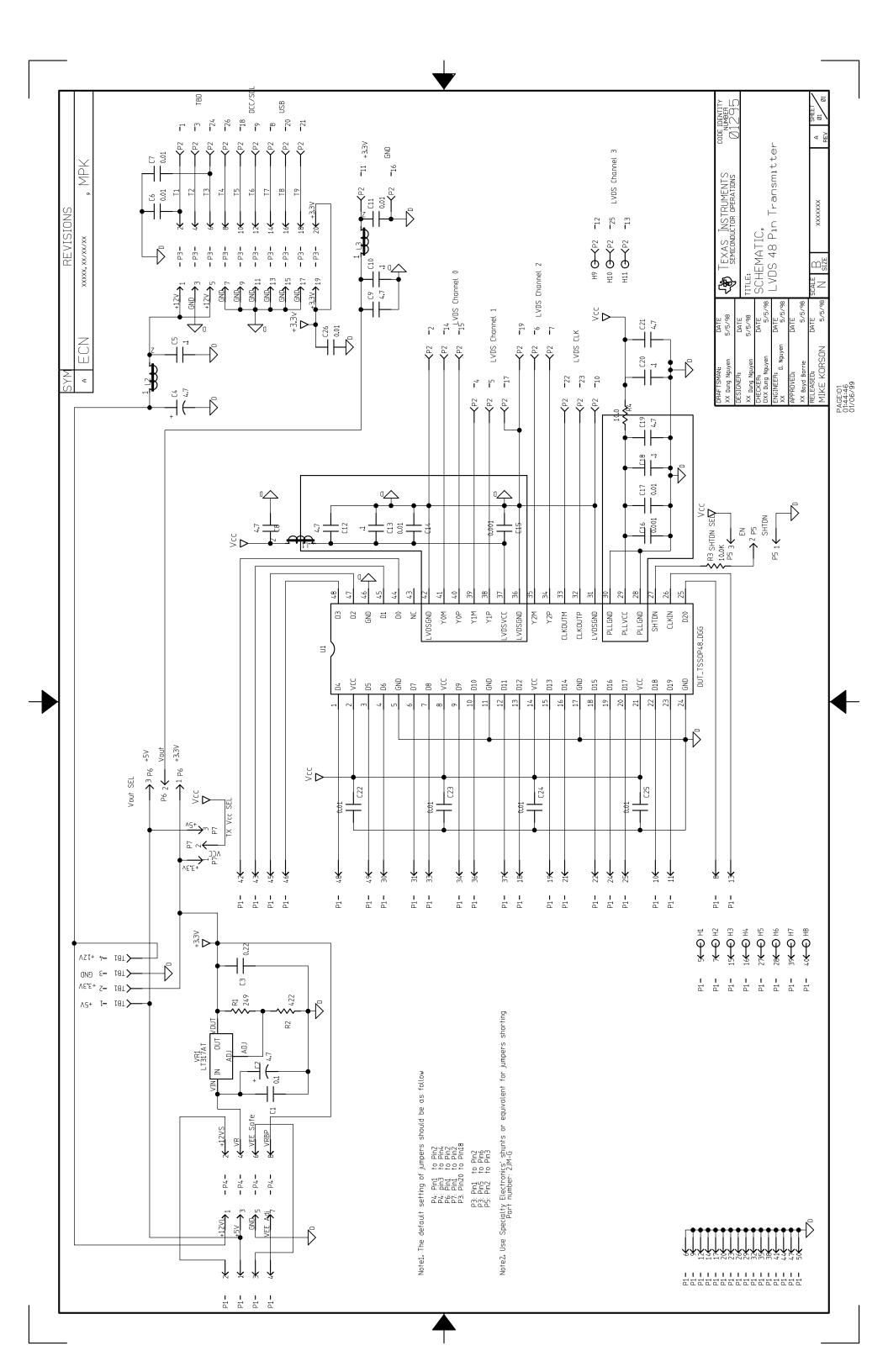

| Figure 8. LVDS Serdes 48 Pin Transmitter Schematic                                         |    |

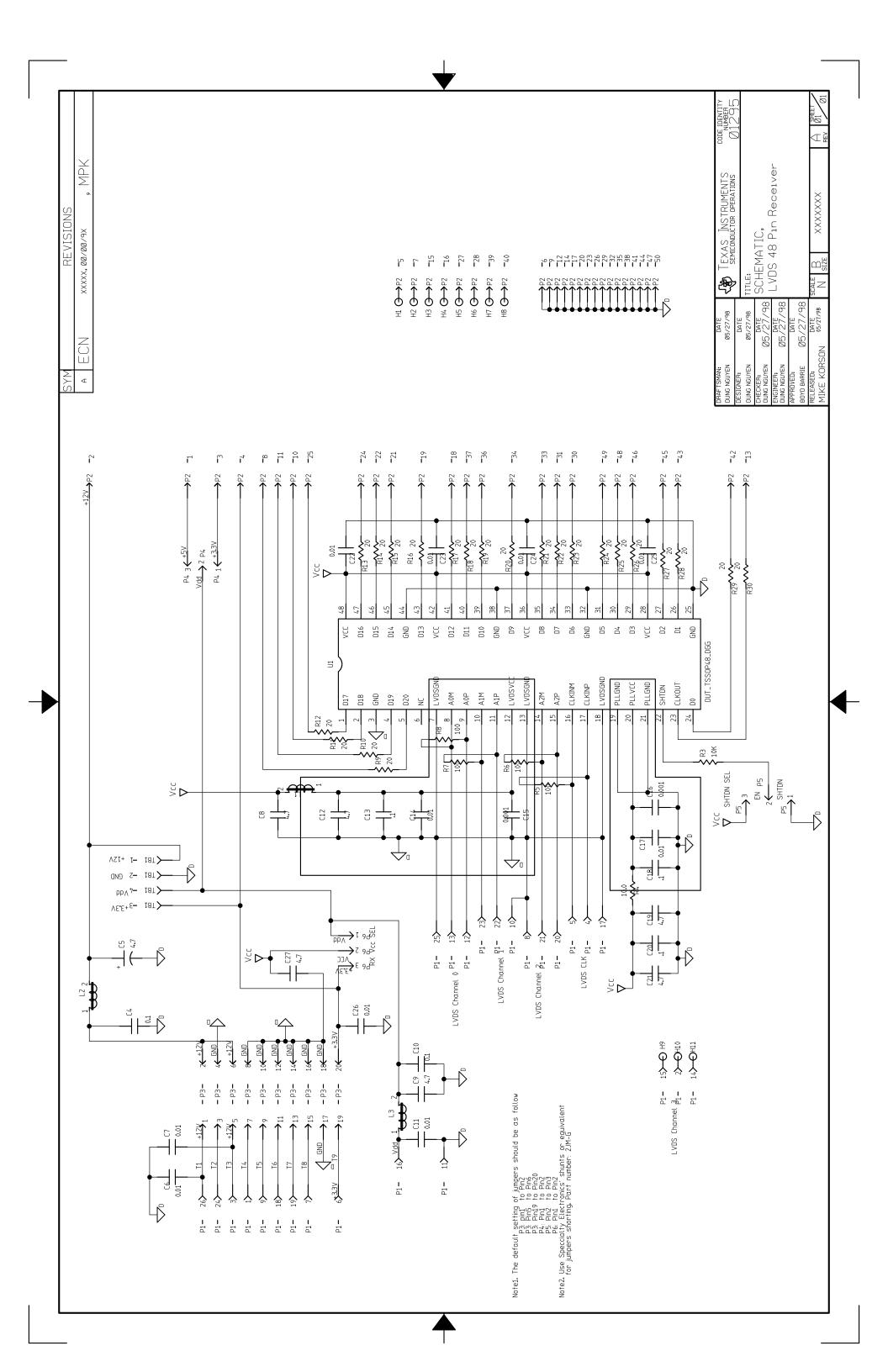

| Figure 9. LVDS Serdes 48 Pin Receiver Schematic                                            |    |

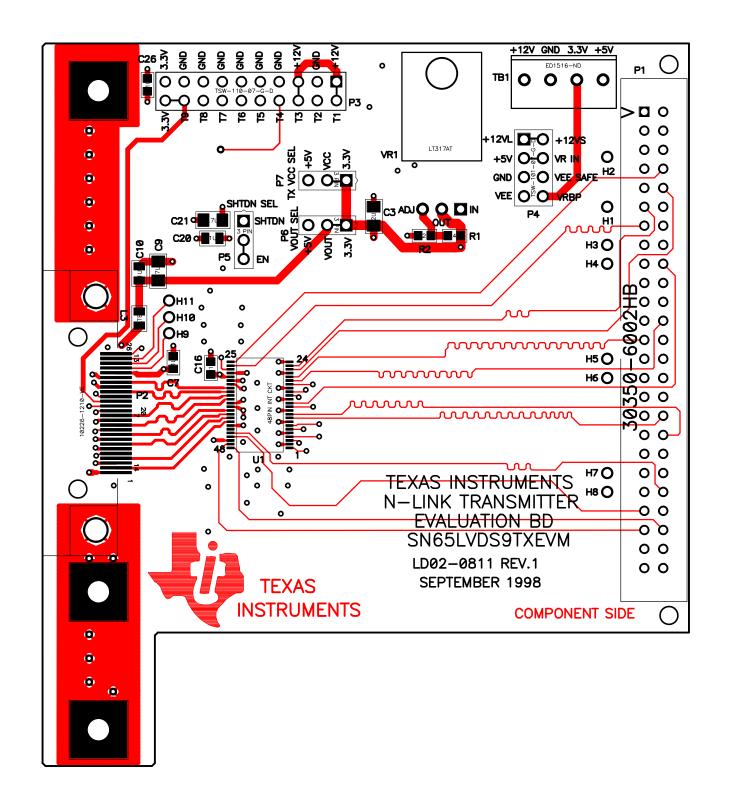

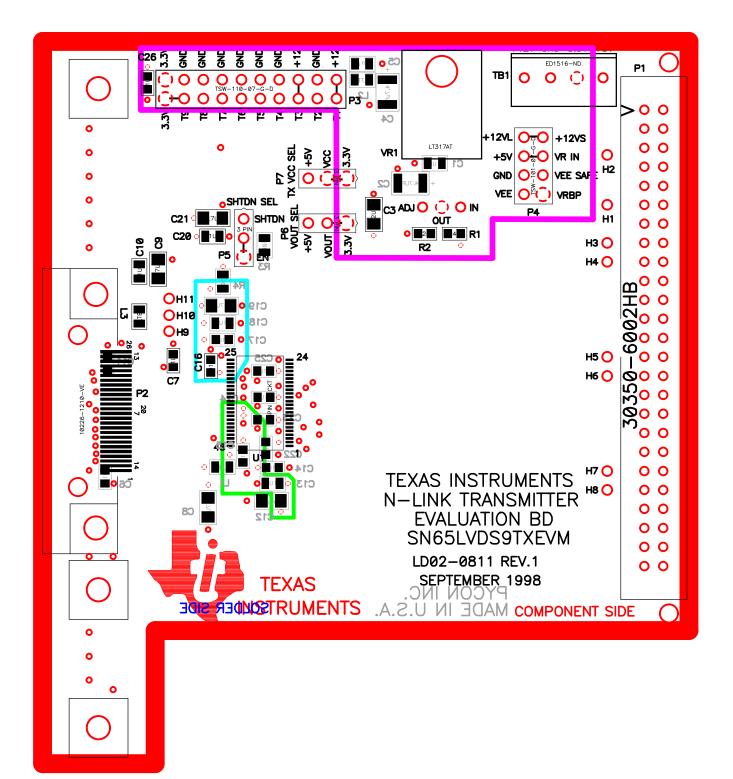

| Figure 10. TX Top Layer                                                                    | 16 |

| Figure 11. TX Vcc Layer                                                                    | 17 |

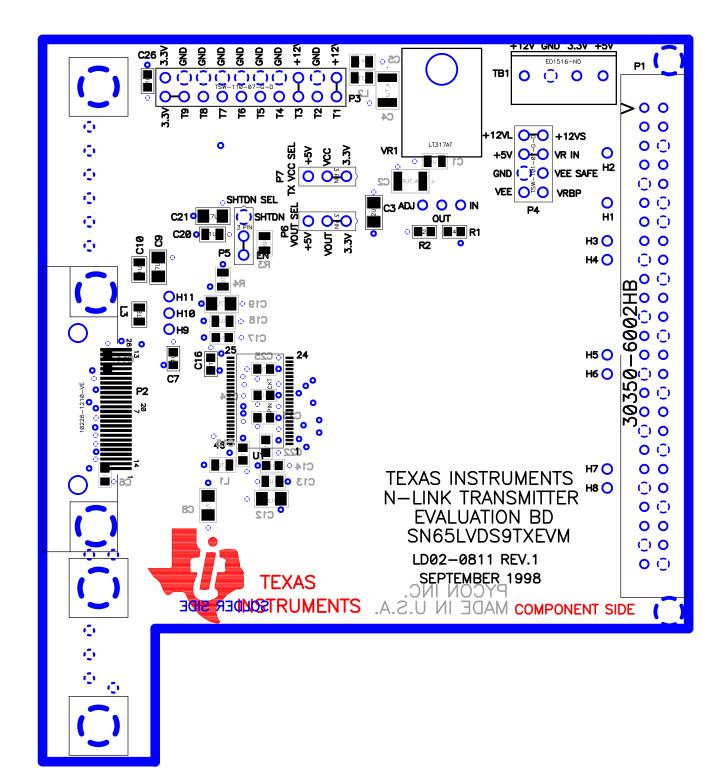

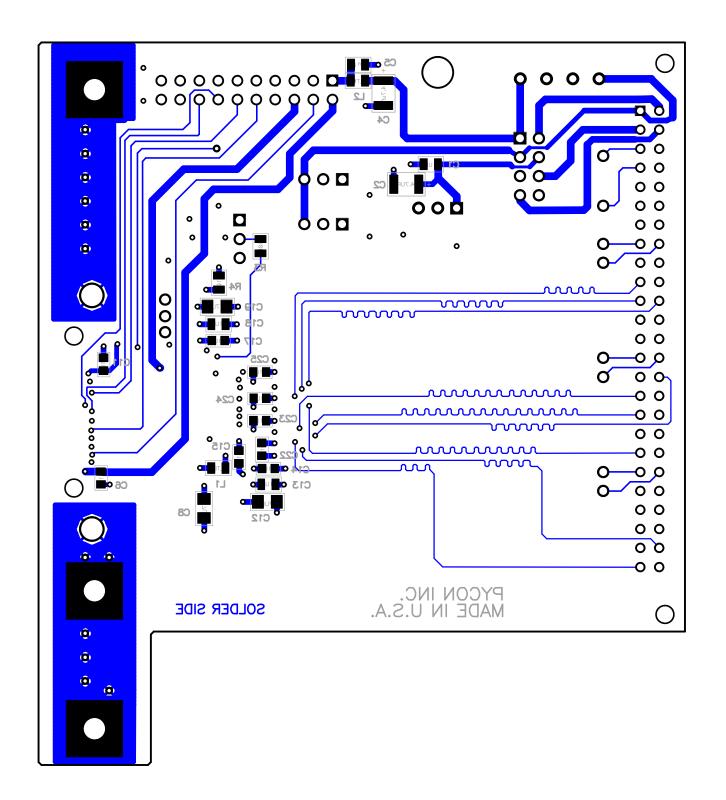

| Figure 12. TX GND Layer                                                                    | 18 |

| Figure 13. TX Bottom Layer                                                                 | 19 |

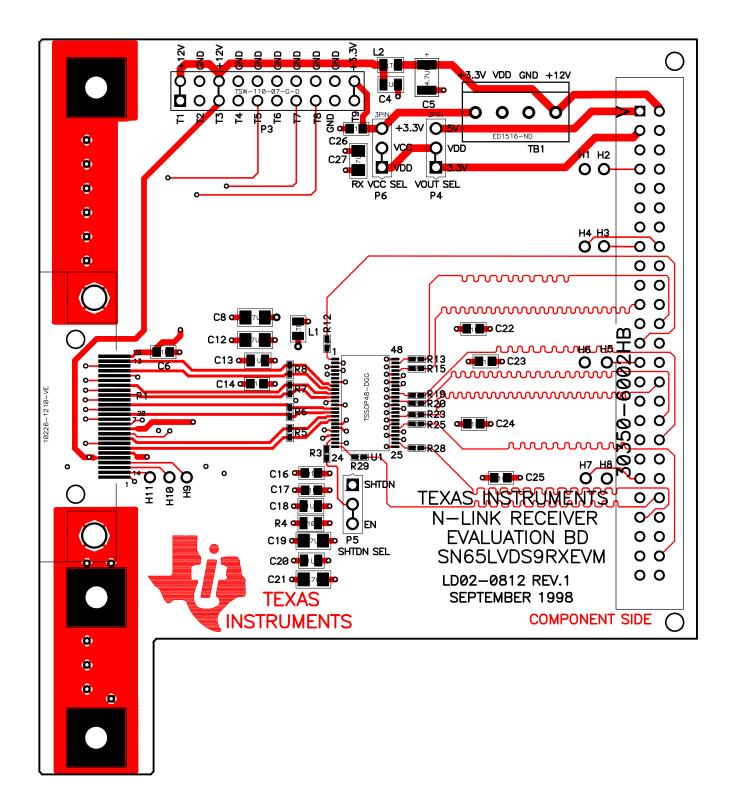

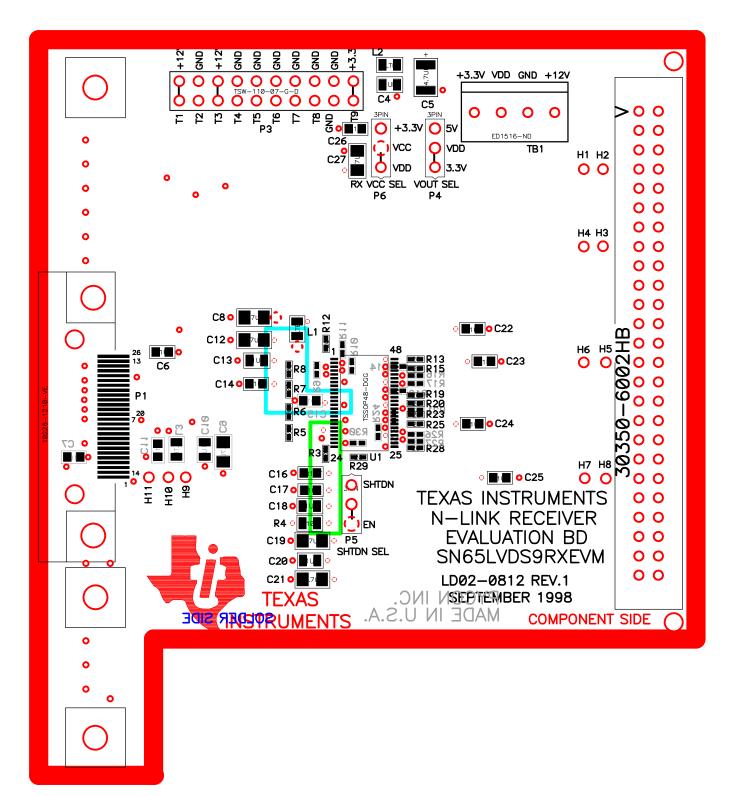

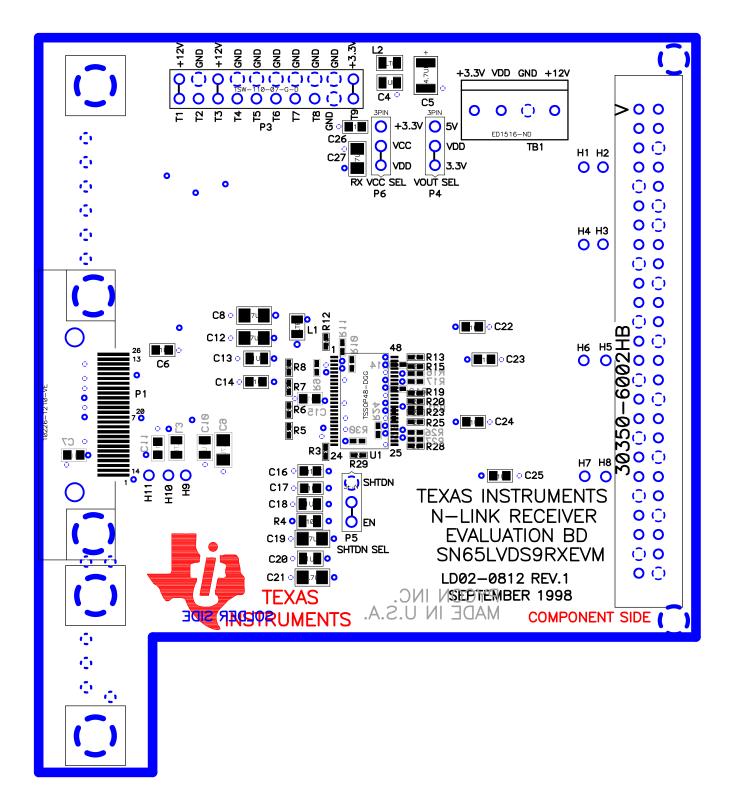

| Figure 14. RX Top Layer                                                                    | 20 |

| Figure 15. RX Vcc Layer                                                                    |    |

| Figure 16. RX GND Layer                                                                    |    |

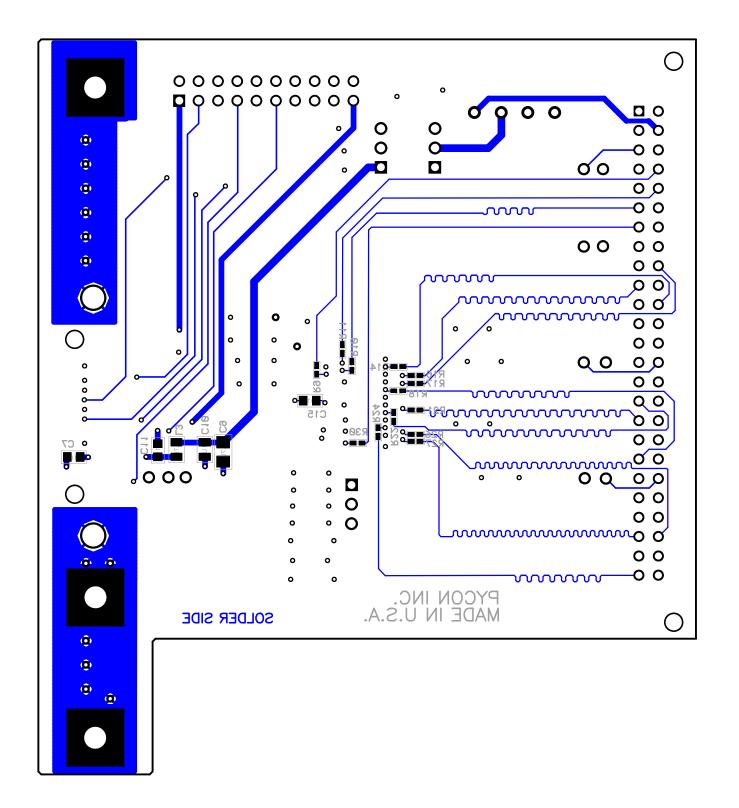

| Figure 17. RX Bottom Layer                                                                 |    |

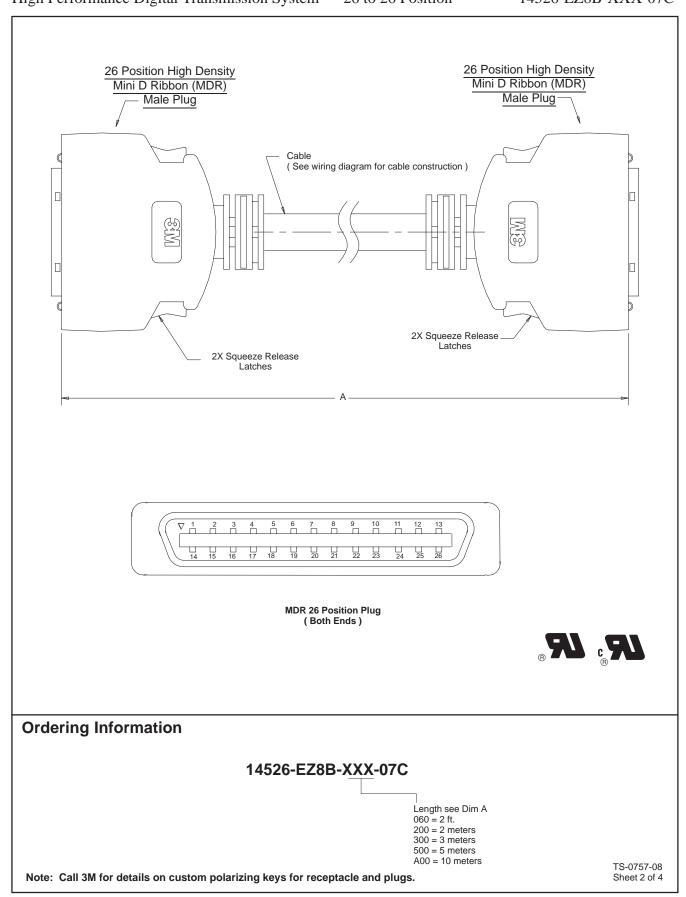

| Figure 18. 0.05-Inch MDR Cable Assembly (Physical/Electrical/Environmental Specifications) |    |

| Figure 19. 0.05-Inch MDR Cable Assembly (26-Position Plug)                                 |    |

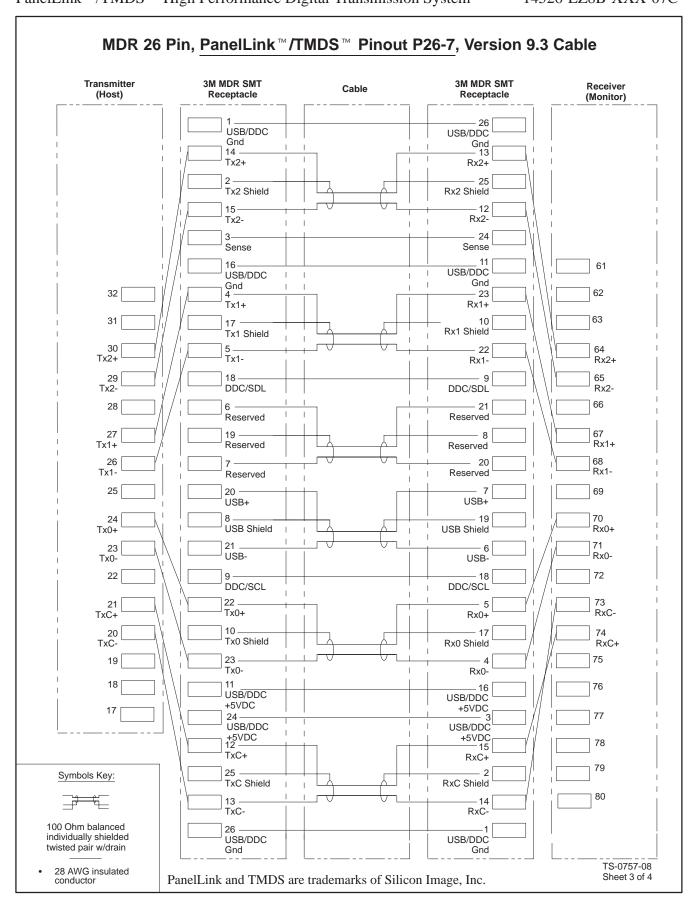

| Figure 20. 0.05-Inch MDR Cable Assembly (PanelLink/TMDS Pinout)                            |    |

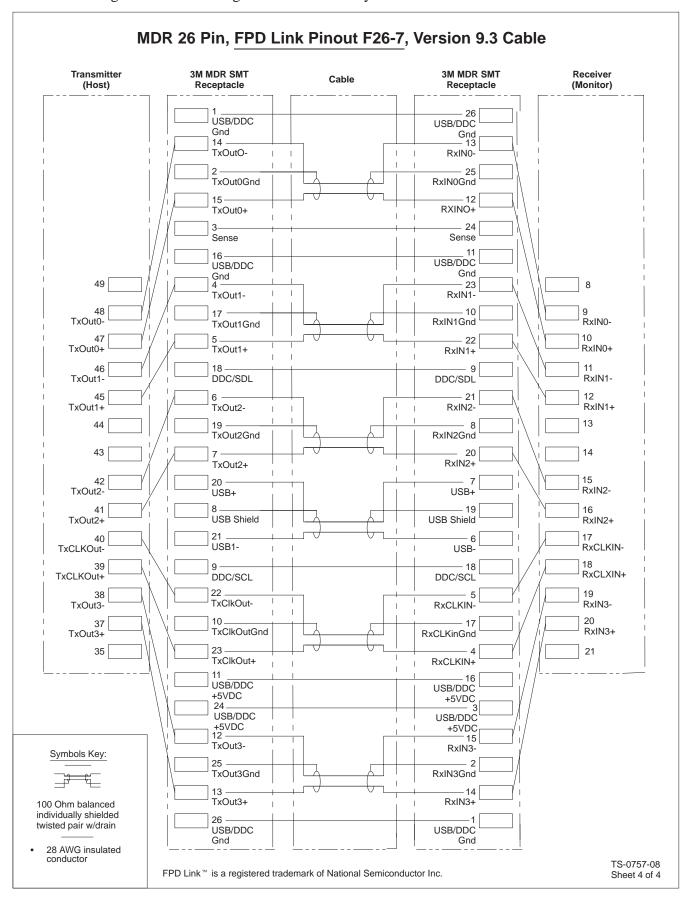

| Figure 21. 0.05-Inch MDR Cable Assembly (FPD Link Pinout)                                  | 27 |

|                                                                                            |    |

| Tables                                                                                     |    |

|                                                                                            | 4  |

| Table 1. Default Transmitter Board Configuration as Shipped                                |    |

| Table 2. Default Receiver Board Configuration as Shipped                                   |    |

| Table 3. LVDS Serdes 48 Transmitter PCB Transmission Line Characteristics                  |    |

| Table 4. LVDS Serdes 48 Receiver PCB Transmission Line Characteristics                     |    |

| Table 5. LVDS Serdes 48 Pin Transmitter Bill of Materials                                  | _  |

| Table 6. LVDS Serdes 48 Pin Receiver Bill of Materials                                     | 15 |

### Introduction

The TI LVDS Serdes 48 EVM kit is used to evaluate and design high data throughput prototypes using the TI LVDS95 transmitter (TX) and LVDS96 receiver (RX) boards. The boards allow the designer to connect 21 bits of TTL-compatible data and clock to the transmitter board where LVDS technology is used to serialize and transmit the data along four differential pairs. The receiver board then deserializes the data, providing 21 bits of TTL data and clock.

The transmitter and receiver boards can be used to evaluate device parameters while acting as a guide for high-speed board layout. The LVDS Serdes EVM boards can be used as daughter boards that are plugged into new or existing designs.

As the frequency of operation increases, the board designer must take special care to ensure that the highest signal integrity is maintained. To achieve this, the board's impedance is controlled to 50  $\Omega$  for the high-speed LVDS serial connections and 75  $\Omega$  for the slower parallel data. In addition, the 50  $\Omega$  impedance mismatches are reduced by designing the component pad size to be as close as possible to the width of the connecting transmission line. Vias are minimized and, when necessary, placed as close as possible to the device drivers. Since this is a combined serial and parallel interface, care was taken to control both impedance and trace length mismatch (board skew).

Overall, the board layout is designed and optimized to support high-speed operation. Thus, understanding impedance control and transmission line effects are crucial when designing high-speed boards.

Some of the advanced features offered by this board include:

| PCB (printed circuit board) and LVDS cable are designed for high-speed signal integrity.             |

|------------------------------------------------------------------------------------------------------|

| Flexibility–The PCB can be configured for additional signals and power supply options.               |

| Provision for chassis-mount connector provides for a low EMI interface.                              |

| All input/output signals are accessible for rapid prototyping.                                       |

| Power can be supplied through either the 50 pin IDC ribbon cable or a screw-on wire crimp connector. |

| Series termination resistors provide parallel RX outputs.                                            |

### **LVDS Serdes 48 EVM Kit Contents**

- □ LVDS Serdes 48 transmitter board (SN65LVDS9TXEVM)

- □ LVDS Serdes 48 receiver board (SN65LVDS9RXEVM)

- □ LVDS Serdes 48 EVM kit documentation

## LVDS Serdes 48 EVM Boards Configuration

The LVDS Serdes 48 EVM boards give the developer various options for operation, many of which are selectable by jumpers. Other options can be either soldered into the EVM or connected through input connectors.

The 50 pin IDC connector provides a connection for both power and data signals. Header "P3" provides access to the signals not used in the 3M Mini D Ribbon (MDR) cable. The "P4" header on the transmitter board is used to select power sources for the voltage regulator and optional input power. The power plane is split for both the transmitter and receiver. Therefore, jumpers labeled "Vcc Sel" are used to connect the chip power plane to the desired voltage source. Additional jumpers are provided for chip enable and output power. For details, see Figure 8, "LVDS Serdes 48 Pin Transmitter Schematic," and Figure 9, "LVDS Serdes 48 Pin Receiver Schematic" in Appendix A.

The board is normally delivered in a default configuration that requires external clock and data inputs. Power can be supplied either through the 50 pin IDC connector or through a 4 pin connector (TB1). The LVDS Serdes 48 EVM is shipped with jumpers for default operation. Table 1 and Table 2 show the default configurations.

Table 1. Default Transmitter Board Configuration as Shipped

| Designator | Function                         | Condition                                                                |

|------------|----------------------------------|--------------------------------------------------------------------------|

| TB1        | Alternate power                  | Another means of providing power to or from the TX board                 |

| P4         | +12 VS - +12 VL                  | Jumper installed between Pins 1 and 2                                    |

|            | Peripheral power source          | <optional evm="" for="" function="" necessary="" not="" –=""></optional> |

| P4         | +5 V – VR IN                     | Jumper installed between Pins 3 and 4                                    |

|            | Normal TX power                  | <normal board="" for="" input="" or="" power="" vr=""></normal>          |

| P6         | Vout SEL                         | Jumper installed between Pins 1 and 2 (Vout: +3.3 V)                     |

| P7         | TX Vcc SEL                       | Jumper installed between Pins 1 and 2 (Vcc: +3.3 V)                      |

| P3         | 3.3 V Aux Out                    | Jumper installed between Pins 20 and 18 (T9: +3.3 V)                     |

| P3         | 12 V Power Output<br>Select      | Jumper installed between Pins 1 and 2 (T1 : +12 V)                       |

| P3         | 12 V Power Output<br>Select      | Jumper installed between Pins 5 and 6 (T3:+12 V)                         |

| P7         | TX Vcc SEL                       | Jumper installed between Pins 1 and 2 (Vcc: +3.3 V)                      |

|            | Selects power source for RX chip |                                                                          |

| P5         | SHTDN SEL                        | Jumper installed between Pins 2 and 3                                    |

Note: For details, see Figure 8, "LVDS Serdes 48 Pin Transmitter Schematic," in Appendix A.

Table 2. Default Receiver Board Configuration as Shipped

| Designator | Function                         | Condition                                                                                                      |

|------------|----------------------------------|----------------------------------------------------------------------------------------------------------------|

| TB1        | Alternate Power                  | Another means of providing power to or from the RX board                                                       |

| P3         | 12 V Power Input<br>Select       | Jumper installed between Pins 1 and 2 <optional evm="" for="" function="" necessary="" not="" –=""></optional> |

|            | Peripheral power source          |                                                                                                                |

| P3         | 12 V Power Input                 | Jumper installed between Pins 5 and 6                                                                          |

|            | Select                           | <optional evm="" for="" function="" necessary="" not="" –=""></optional>                                       |

|            | Peripheral power<br>source       |                                                                                                                |

| P3         | 3.3 V                            | Jumper installed between Pins 19 and 20                                                                        |

|            | Alternate input source           | <optional evm="" for="" function="" necessary="" not="" –=""></optional>                                       |

| P4         | Vout Sel                         | Jumper installed between Pins 1 and 2                                                                          |

|            | Alternate output source          | <optional: +3.3="" output="" power="" rx="" v=""></optional:>                                                  |

| P5         | SHTDN SEL                        | Jumper installed between Pins 2 and 3                                                                          |

|            | Enables/Disables RX              | < Enables RX chip U1>                                                                                          |

| P6         | RX Vcc SEL                       | Jumper installed between Pins 1 and 2 (Vcc : +3.3 V)                                                           |

|            | Selects power source for RX chip |                                                                                                                |

Note: For details, see Figure 9, "LVDS Serdes 48 Pin Receiver Schematic," in Appendix A.

### Typical Test and Setup Configuration

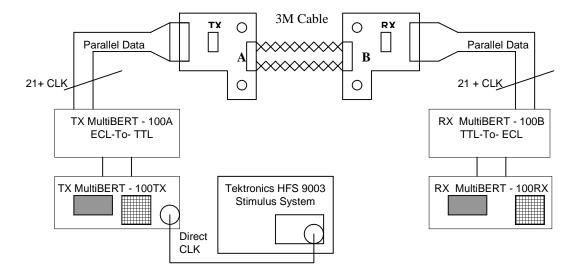

The following typical configuration is used to test the LVDS Serdes transmitter and receiver pair. A parallel bit error rate tester (BERT) generates a predefined parallel bit pattern. The pattern is connected to the transmitter board through a 50 pin IDC connector to the TX chip. The TX chip serializes the data and transmits the data using LVDS technology through the MDR cable (see Appendix A). The RX chip then converts the serial data back to parallel TTL compatible data. The data is then received by the BERT and compared against a predefined pattern.

If any bit errors are received, a bit rate is displayed over the time interval of the test. Therefore, the BERT test is a good indication of failure rate. However, the test does not give the designer an indication of timing margin to bit failure.

The BERT test configuration can also be used to measure the system's characteristic eye diagram on the high-speed LVDS side at test point "B". The eye opening is a direct indication of how much margin exists before the system starts to develop bit errors. During the eye characterization, a pattern of Pseudo Random Binary Sequence (PRBS) is sent through the system.

Figure 1. LVDS Serdes 48 EVM Test Configuration

### **Test Results**

The EVM boards were tested to verify system performance. These tests are useful in showing the capabilities of the system and both TX and RX LVDS Serdes 48 devices.

The first test performed was the BERT test, which was run using PRBS pattern. Figure 1 shows the setup configuration. This test shows the bit errors relative to the time the system is running. The longer the test is run the greater the probability of a bit error. The BERT test was operated for 30 minutes at 65 MHz, nominal 3.3 volts Vcc and across 5 meters of LVDS cable. The test showed no bit errors over the 30 minutes of operation.

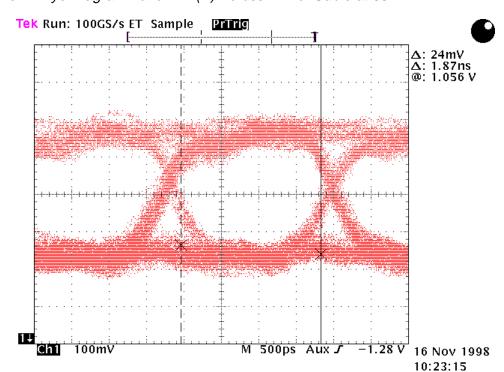

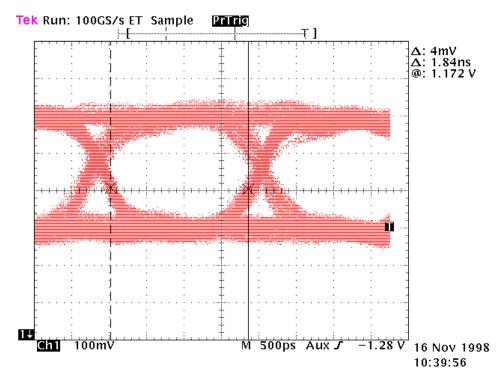

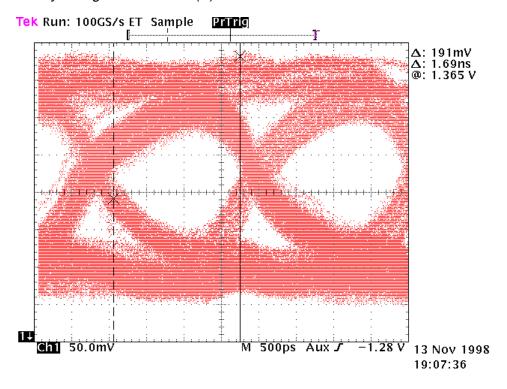

The second test shows eye timing characteristics of the high-speed LVDS portion of the system. An eye diagram is used to evaluate design and timing margins of the system. Eye closure is a result of intersymbol interference and additive noise that is directly proportional to cable quality and length. Therefore, it is important to the designer to keep the eye as open as possible to prevent bit errors form occurring.

In Figure 2 through Figure 7, the eye closes as the cable length increases. This is especially true of the 10-meter cable at 65 MHz. As clearly shown in Figure 2 and Figure 4, the 10-meter cable exhibits a much smaller eye than the 2 meter cable. In addition to cable length, the frequency of operation can directly affect the eye's opening. As the period increases, the margin increases for deterministic jitter and noise in the system. Thus, a system designer can use a longer cable at a lower frequency. This can be seen in Figure 4 and Figure 7, where the eye at 65 MHz is much smaller than the eye at 40 MHz.

Figure 2. Eye Diagram Taken RX(B) Across 2 m of Cable at 65 MHz

Figure 3. Eye Diagram Taken RX(B) Across 5 m of Cable at 65 MHz

Figure 4. Eye Diagram Taken RX(B) Across 10 m of Cable at 65 MHz

Figure 6. Eye Diagram Taken RX(B) Across 5 m of Cable at 40 MHz

Figure 7. Eye Diagram Taken RX(B) Across 10 m of Cable at 40 MHz

### **PCB Transmission Line Characteristics**

The PCB characteristics are calculated and based on the layer construction and trace width of the board. This should be useful in determining the proper interface to the EVM and establishing system timing.

|  |  | Line Characteristics |

|--|--|----------------------|

| Device<br>Pin No. | Connector<br>Pin No. | Trace Width (inches) | Length (inches) | Capacitance (pF) | Inductance<br>(nH) | Impedance (Ω) | Line Delay (ps) |

|-------------------|----------------------|----------------------|-----------------|------------------|--------------------|---------------|-----------------|

| 1                 | 48                   | 0.0065               | 2.6065          | 4.7              | 25.7               | 74.3          | 345.4           |

| 3                 | 49                   | 0.0065               | 2.6267          | 4.7              | 25.7               | 74.3          | 345.4           |

| 4                 | 30                   | 0.0065               | 2.6329          | 4.7              | 25.7               | 74.3          | 345.4           |

| 6                 | 31                   | 0.0065               | 2.6387          | 4.7              | 25.7               | 74.3          | 345.4           |

| 7                 | 33                   | 0.0065               | 2.661           | 4.8              | 26.6               | 74.3          | 358.7           |

| 9                 | 34                   | 0.0065               | 2.6294          | 4.7              | 25.7               | 74.3          | 345.4           |

| 10                | 36                   | 0.0065               | 2.624           | 4.7              | 25.7               | 74.3          | 345.4           |

| 12                | 37                   | 0.0065               | 2.638           | 4.7              | 25.7               | 74.3          | 345.4           |

| 13                | 18                   | 0.0065               | 2.7273          | 4.8              | 26.6               | 74.3          | 358.7           |

| 15                | 19                   | 0.0065               | 2.6708          | 4.8              | 26.6               | 74.3          | 358.7           |

| 16                | 21                   | 0.0065               | 2.614           | 4.7              | 25.7               | 74.3          | 345.4           |

| 18                | 22                   | 0.0065               | 2.704           | 4.8              | 26.6               | 74.3          | 358.7           |

| 19                | 24                   | 0.0065               | 2.6464          | 4.8              | 26.6               | 74.3          | 358.7           |

| Device<br>Pin No. | Connector<br>Pin No. | Trace Width (inches) | Length (inches) | Capacitance (pF) | Inductance<br>(nH) | Impedance $(\Omega)$ | Line Delay (ps) |

|-------------------|----------------------|----------------------|-----------------|------------------|--------------------|----------------------|-----------------|

| 20                | 25                   | 0.0065               | 2.653           | 4.8              | 26.6               | 74.3                 | 358.7           |

| 22                | 10                   | 0.0065               | 2.76            | 5.0              | 27.6               | 74.3                 | 372.0           |

| 23                | 11                   | 0.0065               | 2.6717          | 4.8              | 26.6               | 74.3                 | 358.7           |

| 25                | 8                    | 0.0065               | 2.6975          | 4.8              | 26.6               | 74.3                 | 358.7           |

| 26                | 13                   | 0.0065               | 2.6953          | 4.8              | 26.6               | 74.3                 | 358.7           |

| 44                | 42                   | 0.0065               | 2.6616          | 4.8              | 26.6               | 74.3                 | 358.7           |

| 45                | 43                   | 0.0065               | 2.6482          | 4.8              | 26.6               | 74.3                 | 358.7           |

| 47                | 45                   | 0.0065               | 2.6845          | 4.8              | 26.6               | 74.3                 | 358.7           |

| 48                | 46                   | 0.0065               | 2.6441          | 4.7              | 25.7               | 74.3                 | 345.4           |

| 32                | 23                   | 0.015                | 0.6804          | 1.9              | 4.8                | 50.8                 | 94.2            |

| 33                | 22                   | 0.015                | 0.6828          | 1.9              | 4.8                | 50.8                 | 94.5            |

| 34                | 7                    | 0.015                | 0.6804          | 1.9              | 4.8                | 50.8                 | 94.2            |

| 35                | 6                    | 0.015                | 0.6991          | 1.9              | 4.9                | 50.8                 | 96.8            |

| 38                | 5                    | 0.015                | 0.6894          | 1.9              | 4.8                | 50.8                 | 95.4            |

| 39                | 4                    | 0.015                | 0.6833          | 1.9              | 4.8                | 50.8                 | 94.6            |

| 40                | 15                   | 0.015                | 0.6899          | 1.9              | 4.9                | 50.8                 | 95.5            |

| 41                | 14                   | 0.015                | 0.7026          | 1.9              | 4.9                | 50.8                 | 97.3            |

Note: All values presented in this table are theoretical calculated values and may not reflect actual measured parameters.

Table 4. LVDS Serdes 48 Receiver PCB Transmission Line Characteristics

| Device<br>Pin No. | Connector<br>Pin No. | Trace Width (inches) | Length (inches) | Capacitance<br>(pF) | Inductance<br>(nH) | Impedance $(\Omega)$ | Line Delay<br>(ps) |

|-------------------|----------------------|----------------------|-----------------|---------------------|--------------------|----------------------|--------------------|

| 1                 | 25                   | 0.0065               | 2.76            | 5.0                 | 27.6               | 74.3                 | 372.0              |

| 2                 | 10                   | 0.0065               | 2.47            | 4.4                 | 24.4               | 74.3                 | 328.2              |

| 4                 | 11                   | 0.0065               | 3.04            | 5.4                 | 30.0               | 74.3                 | 403.9              |

| 5                 | 8                    | 0.0065               | 2.63            | 4.7                 | 26.0               | 74.3                 | 349.4              |

| 23                | 13                   | 0.0065               | 2.63            | 4.7                 | 26.0               | 74.3                 | 349.4              |

| 24                | 42                   | 0.0065               | 2.66            | 4.8                 | 26.3               | 74.3                 | 353.4              |

| 26                | 43                   | 0.0065               | 2.62            | 4.7                 | 25.9               | 74.3                 | 348.1              |

| 27                | 45                   | 0.0065               | 2.71            | 4.8                 | 26.7               | 74.3                 | 360.0              |

| 29                | 46                   | 0.0065               | 2.64            | 4.7                 | 26.1               | 74.3                 | 350.7              |

| 30                | 48                   | 0.0065               | 2.56            | 4.6                 | 25.3               | 74.3                 | 340.1              |

| 31                | 49                   | 0.0065               | 2.69            | 4.8                 | 26.5               | 74.3                 | 357.4              |

| 33                | 30                   | 0.0065               | 2.56            | 4.6                 | 25.3               | 74.3                 | 340.1              |

| 34                | 31                   | 0.0065               | 2.71            | 4.8                 | 26.7               | 74.3                 | 360.0              |

| 35                | 33                   | 0.0065               | 2.51            | 4.7                 | 24.8               | 74.3                 | 333.5              |

| 37                | 34                   | 0.0065               | 2.54            | 4.5                 | 25.1               | 74.3                 | 337.5              |

| 39                | 36                   | 0.0065               | 2.5             | 4.5                 | 24.7               | 74.3                 | 332.1              |

| 40                | 37                   | 0.0065               | 2.58            | 4.6                 | 25.4               | 74.3                 | 341.4              |

| 41                | 18                   | 0.0065               | 2.63            | 4.7                 | 26.0               | 74.3                 | 349.4              |

| 43                | 19                   | 0.0065               | 2.57            | 4.6                 | 25.4               | 74.3                 | 341.4              |

| 45                | 21                   | 0.0065               | 2.53            | 4.5                 | 25.0               | 74.3                 | 336.1              |

| 46                | 22                   | 0.0065               | 2.47            | 4.4                 | 24.4               | 74.3                 | 328.2              |

| Device<br>Pin No. | Connector<br>Pin No. | Trace Width (inches) | Length (inches) | Capacitance (pF) | Inductance<br>(nH) | Impedance $(\Omega)$ | Line Delay<br>(ps) |

|-------------------|----------------------|----------------------|-----------------|------------------|--------------------|----------------------|--------------------|

| 47                | 24                   | 0.0065               | 2.52            | 4.5              | 24.9               | 74.3                 | 334.8              |

| 8                 | 13                   | 0.015                | 1.2138          | 3.3              | 8.5                | 50.8                 | 168.0              |

| 9                 | 12                   | 0.015                | 1.1885          | 3.2              | 8.4                | 50.8                 | 164.5              |

| 10                | 23                   | 0.015                | 1.1877          | 3.2              | 8.4                | 50.8                 | 164.4              |

| 11                | 22                   | 0.015                | 1.159           | 3.2              | 8.1                | 50.8                 | 160.0              |

| 14                | 21                   | 0.015                | 1.1718          | 3.2              | 8.2                | 50.8                 | 162.2              |

| 15                | 20                   | 0.015                | 1.162           | 3.2              | 8.2                | 50.8                 | 160.8              |

| 16                | 5                    | 0.015                | 1.1889          | 3.2              | 8.4                | 50.8                 | 164.6              |

| 17                | 4                    | 0.015                | 1.2015          | 3.3              | 8.4                | 50.8                 | 166.3              |

Note: All values presented in this table are theoretical calculated values and may not reflect actual measured parameters.

# Layer Construction for Transmitter/Receiver Boards

Notes: 1) All cores consist of 1 oz Cu.

- 2) Trace width

- A) 15 mils (for 50  $\Omega$ )

- B) 6.5 mils (for 75  $\Omega$ )

- C) 9.0 mils (for others)

- 3) Overall board thickness is 62 mils  $\pm 10\%.$

- 4) Impedance is 50  $\Omega$  and 75  $\Omega$  ±5%.

- 5) Material is G-Tek. Dielectric constant = 3.5.

# Appendix A. Schematics, Board Layouts, and MDR Cable Assembly Specifications

This appendix contains schematics and corresponding bill of materials for the LVDS Serdes 48 pin EVM transmitter and receiver boards along with board layouts. Specifications for the MDR cable assembly are also included.

Table 5. LVDS Serdes 48 Pin Transmitter Bill of Materials

| Item | Qty    | Mfg               | Mfg Part No.    | Ref Des                                 | Description          | Value or Function               |

|------|--------|-------------------|-----------------|-----------------------------------------|----------------------|---------------------------------|

| 762  | 11     |                   | .040PTH         | H1-H11                                  |                      | .040DIA Plated hole             |

| 763  | 1      | ROHM              | MCH212C104KP    | C1                                      | CAPACITOR,SMT0805    | 25 V, 10%,<br>0.1 μF, 0805      |

| 764  | 2      | PANASONIC         | ECS-T1DX475R    | C2,C4                                   | CAPACITOR,SMT,TANT   | 20%, 20 V,<br>4.7 μF            |

| 765  | 5<br>* | RUTILCON          | LMK316BJ475ML-B | C8,C9,C12,C19<br>C21                    | CAPACITOR,SMT1206    | 10 V, 20%,<br>4.7 μF            |

| 766  | 5<br>* | AVX               | 08051C104JATMA  | C5,C10,C13,C1<br>8C20                   | CAPACITOR,SMT0805    | 100 V, 5%,<br>0.1 μF            |

| 767  | 1      | AVX               | 12063C224JATMA  | C3                                      | CAPACITOR,SMT1206    | 25 V, 5%,<br>0.22 μF            |

| 768  | 2      | AVX               | 06033G102JATMA  | C15,C16                                 | CAPACITOR,SMT0603    | 25 V, 5%,<br>0.001 μF           |

| 769  | 10     | AVX               | 06033G103JATMA  | C6,C7,C11,C14<br>C17,C22,C23<br>C24-C26 | CAPACITOR,SMT0603    | 25 V, 5%,<br>0.01 μF            |

| 770  | 1      | 3M                | 10226-1210 VE   | P2                                      | CONNECTOR,SMT,26PIN  | MINI D<br>RIBBON<br>BOARD RA RE |

| 771  | 1      | 3M                | 30350-6002HB    | P1                                      | CONNECTOR,.1X.1      | LOW PROFILE<br>HEADER           |

| 772  | 3      | STEWARD           | HZ_0805_E_601_R | L1-L3                                   | FILTER,SMT,0805      | FERRITE,0805                    |

| 773  | 1      | SAMTEC            | TSW-104-07-G-D  | P4                                      | HEADER,2X4,.1CTR     | HEADER, 2X4,<br>.1CTR           |

| 774  | 1      | SAMTEC            | TSW-110-07-G-D  | P3                                      | HEADER,2X10,.1CTRS   | HEADER 2X 10<br>.1CTR           |

| 775  | 3      | ANY               | HEADER,MALE,3PI | P5-P7                                   | HEADER               | MALE,3PIN,.10<br>0CC            |

| 776  | 1      | LINEAR            | LT317AT         | VR1                                     | IC,3P,TO220          | 3 TERMINAL<br>POSITIVE<br>REGU  |

| 777  | 1      |                   | DUT_TSSOP48_DGG | U1                                      | IC,TSSOP,48P         | DUT TSSOP<br>48PIN DGG<br>PKG   |

| 778  | 1      | DALE              | CRCW080510R0F   | R4                                      | RESISTOR,SM,1/10w,1% | 10.0 OHM                        |

| 779  | 1      | DALE              | CRCW08051002F   | R3                                      | RESISTOR,SM,1/10w,1% | 10.0K OHM                       |

| 780  | 1      | DALE              | CRCW0603249F    | R1                                      | RESISTOR,SMT,0603    | 249 OHM                         |

| 781  | 1      | DALE              | CRCW0603422F    | R2                                      | RESISTOR,SMT,0603    | 422 OHM                         |

| 782  | 1      | ON-SHORE<br>TECHN | ED1516-ND       | TB1                                     | TERMINAL BLOCK       | TERMINAL<br>BLOCK 4<br>POSITION |

Total Part Count: 54 Total Parts Cost: 0

Table 6. LVDS Serdes 48 Pin Receiver Bill of Materials

| Item | Qty    | Mfg               | Mfg Part No.    | Ref Des                                 | Description          | Value or Function               |

|------|--------|-------------------|-----------------|-----------------------------------------|----------------------|---------------------------------|

| 84   | 11     |                   | .040PTH         | H1-H11                                  |                      | .040DIA Plated hole             |

| 85   | 1      | PANASONIC         | ECS-T1DX475R    | C5                                      | CAPACITOR,SMT,TANT   | 20%, 20 V,<br>4.7 μF            |

| 86   | 6      | RUTILCON          | LMK316BJ475ML-B | C8,C9,C12,C19<br>C21,C27                | CAPACITOR,SMT1206    | 10 V, 20%,<br>4.7 μF            |

| 87   | 5<br>* | AVX               | 08051C104JATMA  | C4,C10,C13,C18<br>C20                   | CAPACITOR,SMT0805    | 100 V, 5%, .1 μF                |

| 88   | 2      | AVX               | 06033G102JATMA  | C15,C16                                 | CAPACITOR,SMT0603    | 25 V,5%,<br>0.001 μF            |

| 89   | 10     | AVX               | 06033G103JATMA  | C6,C7,C11,C14<br>C17,C22,C23<br>C24-C26 | CAPACITOR,SMT0603    | 25 V,5%,<br>0.01 μF             |

| 90   | 1      | 3M                | 10226-1210 VE   | P1                                      | CONNECTOR,SMT,26PIN  | MINI D RIBBON<br>BOARD RA RE    |

| 91   | 1      | 3M                | 30350-6002HB    | P2                                      | CONNECTOR,.1X.1      | LOW PROFILE<br>HEADER           |

| 92   | 3      | STEWARD           | HZ_0805_E_601_R | L1-L3                                   | FILTER,SMT,0805      | FERRITE,0805                    |

| 93   | 1      | SAMTEC            | TSW-110-07-G-D  | P3                                      | HEADER,2X10,.1CTRS   | HEADER 2X 10<br>.1CTR           |

| 94   | 3      | ANY               | HEADER,MALE,3PI | P4-P6                                   | HEADER               | MALE,3PIN,.100<br>CC            |

| 95   | 1      |                   | DUT_TSSOP48_DGG | U1                                      | IC,TSSOP,48P         | DUT TSSOP<br>48PIN DGG<br>PKG   |

| 96   | 1      | DALE              | CRCW080510R0F   | R4                                      | RESISTOR,SM,1/10w,1% | 10.0 OHM                        |

| 97   | 4      | PANASONIC         | ERJ-2GEJ101     | R5-R8                                   | RESISTOR,SMT0402     | +/-1%,100                       |

| 98   | 1      | PANASONIC         | ERJ-2GEJ103     | R3                                      | RESISTOR,SMT0402     | +/-5%,10K                       |

| 99   | 22     | PANASONIC         | ERJ-2GEJ200     | R9-R30                                  | RESISTOR,SMT0402     | +/-5%,20                        |

| 100  | 1      | ON-SHORE<br>TECHN | ED1516-ND       | TB1                                     | TERMINAL BLOCK       | TERMINAL<br>BLOCK 4<br>POSITION |

Total Part Count: 74 Total Parts Cost: 0

# .050" Mini D Ribbon (MDR) Cable Assembly

High Performance Digital Transmission System — 26 to 26 Position

14526-EZ8B-XXX-07C

#### IMPORTANT NOTICE TO PURCHASER

ALL STATEMENTS, TECHNICAL INFORMATION AND RECOMMENDATIONS CONTAINED HEREIN ARE BASED ON TESTS WE BELIEVE TO BE RELIABLE, BUT THE ACCURACY OR COMPLETENESS THEREOF IS NOT GUARANTEED, AND THE FOLLOWING IS MADE IN LIEU OF ALL WARRANTIES, EXPRESSED OR IMPLIED:

SELLER'S AND MANUFACTURER'S ONLY OBLIGATION SHALL BE TO REPLACE SUCH QUANTITY OF THE PRODUCT PROVED TO BE DEFECTIVE. NEITHER SELLER NOR MANUFACTURER SHALL BE LIABLE FOR ANY INJURY, LOSS OR DAMAGE, DIRECT OR CONSEQUENTIAL, ARISING OUT OF THE USE OF OR THE INABILITY TO USE THE PRODUCT. BEFORE USING, USER SHALL DETERMINE THE SUITABILITY OF THE PRODUCT FOR HIS INTENDED USE, AND USER ASSUMES ALL RISK AND LIABILITY WHATSOEVER IN CONNECTION THEREWITH. NO STATEMENT OR RECOMMENDATION NOT CONTAINED HEREIN SHALL HAVE ANY FORCE OR EFFECT UNLESS IN AN AGREEMENT SIGNED BY OFFICERS OR SELLER AND MANUFACTURER.

TS-0757-08 Sheet 1 of 4

Date Issued: June 3, 1998

# **Physical**

**Connector Contact Plating**

Wiping Area:  $30 \mu''$  [  $0.76 \mu m$  ] Min. Gold

Shell

Color: Parchment/Beige

Material: Acrylonitrile Butadiene Styrene (ABS)

Cable

Color: Parchment/Beige

Jacket Material: Polyvinyl Chloride (PVC)

### **Electrical**

**Voltage Rating:** 30 V **Current Rating:** 1 A

**Insulation Resistance:**  $> 5 \times 10^8 \Omega$  at 500 Vdc **Withstanding Voltage:** 500 Vrms for 1 minute

**Individually Shielded Twisted Pairs**

Characteristic Impedance:  $100 \pm 10\Omega$

**Conductor Size:** 28 AWG Stranded **Propogation Velocity:** 1.25 ns/ft [4.1 ns/m]

### **Environmental**

**Temperature Rating:** -20°C to +75°C **Flammability Rating:** N.E.C. 725, CL2

UL File No.: E86982

### **TI Contact Numbers**

### **INTERNET**

TI Semiconductor Home Page

www.ti.com/sc

TI Distributors

www.ti.com/sc/docs/distmenu.htm

### PRODUCT INFORMATION CENTERS

Americas

Phone +1(972) 644-5580 Fax +1(972) 480-7800 Email sc-infomaster@ti.com

Europe, Middle East, and Africa

Phone

Deutsch +49-(0) 8161 80 3311 +44-(0) 1604 66 3399 English Español +34-(0) 90 23 54 0 28 +33-(0) 1-30 70 11 64 Français +33-(0) 1-30 70 11 67 Italiano Fax +44-(0) 1604 66 33 34

Email epic@ti.com

Japan Phone

> International +81-3-3457-0972 Domestic 0120-81-0026

Fax

International +81-3-3457-1259 Domestic 0120-81-0036 Email pic-japan@ti.com

Asia

Phone

International +886-2-23786800

Domestic

Australia 1-800-881-011 TI Number -800-800-1450

10810 China

TI Number -800-800-1450 Hong Kong 800-96-1111 TI Number -800-800-1450

India 000-117

TI Number -800-800-1450 Indonesia 001-801-10 TI Number -800-800-1450 Korea 080-551-2804 Malaysia 1-800-800-011 TI Number -800-800-1450 New Zealand 000-911 TI Number -800-800-1450 Philippines 105-11

TI Number -800-800-1450 Singapore 800-0111-111 TI Number -800-800-1450 Taiwan 080-006800 Thailand 0019-991-1111 TI Number -800-800-1450

Fax 886-2-2378-6808 **Email** tiasia@ti.com

TI is a trademark of Texas Instruments Incorporated.

Other brands and names are the property of their respective owners.

#### IMPORTANT NOTICE

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty, or endorsement thereof.

Copyright © 1999 Texas Instruments Incorporated