# TPS2306 Dual Sequencing Hot Swap Power Manager Evaluation Module and Interface Card

Power Distribution and Processing Solutions

#### **Contents**

| 1 | Introduction                                                       | 3  |

|---|--------------------------------------------------------------------|----|

|   | 1.1 Features                                                       |    |

|   | 1.2 Description                                                    |    |

| 2 | The TPS2306 EVM Kit                                                | 4  |

|   | 2.1 The TPS2306 Hot Swap EVM Board                                 |    |

|   | 2.1.1 Module Description                                           |    |

|   | 2.1.2 EVM Schematic Diagram and Bill of Materials (BOM)            |    |

|   | 2.2 The TPS2300 Hot Swap Interface Card                            |    |

|   | 2.2.1 Description                                                  |    |

|   | 2.2.2 Interface Card Schematic Diagram and Bill of Materials (BOM) |    |

|   | 2.3 TPS2306 EVM Kit Operating Specifications                       |    |

| 3 | Getting Started                                                    | 11 |

| • | 3.1 Equipment Requirements                                         |    |

|   | 3.2 Verifying the EVM Operation                                    |    |

|   | 3.2.1 Equipment Setup                                              |    |

|   | 3.2.2 Functional Test                                              |    |

|   | 3.3 Using the EVM Kit to Evaluate the TPS2306 HSPM                 |    |

| 4 | Reconfiguring the EVM                                              | 13 |

| • | 4.1 Pre-configured Fault Timer Settings                            |    |

|   | 4.2 Modifying Load Characteristics                                 |    |

|   | 4.3 Changing the Output Sequencing                                 |    |

|   | 4.4 Setting the Constant-Current Mode Output Level                 |    |

|   | 4.5 Optional Soft-Start With the TPS2306                           |    |

|   | 4.6 Configuring the EVM for High Voltage Applications              |    |

|   | 4.7 Automatic Power-Up                                             |    |

## **Figures**

| 1 | Evaluation Module Top Assembly                                      | 4  |

|---|---------------------------------------------------------------------|----|

| 2 | EVM Schematic Diagram                                               | 6  |

| 3 | Interface Card Top Assembly                                         | 8  |

| 4 | Hot Swap Interface Card Schematic                                   | 9  |

| 5 | Equipment Setup                                                     | 10 |

| 6 | Output Start-Up Waveforms                                           | 11 |

| 7 | Fault Time-Out Waveforms                                            | 12 |

|   | Tables                                                              |    |

| 1 | TPS2306 EVM Test Points                                             | 5  |

| 2 | TPS2306 Hot Swap Evaluation Module Bill of Materials (SLUP056A-001) | 7  |

| 3 | Hot Swap Interface Card Bill of Materials (SLVP155A-003)            | 9  |

| 4 | Evaluation Module Design Parameters                                 | 10 |

| 5 | EVM Absolute Maximum Ratings                                        | 10 |

| 6 | EVM Switch S1 Initial Positions                                     | 11 |

| 7 | Example Load Capacitance/Fault Timer Setting Combinations           | 13 |

| 8 | TPS2306 EVM Output Sequence Programming                             | 14 |

| 9 | Ramp-Up and Ramp-Down Comparator Specifications                     | 15 |

#### 1 Introduction

This User's Guide describes the use and operating features of the TPS2306 evaluation module (EVM). The Texas Instruments (TI) TPS2306 is a dual channel hot-swap power manager with programmable output sequencing control. It integrates inrush current control, electronic circuit breaker, power-up and power-down sequencing and fault indication functions to provide plug-in module designers with a configurable hot swap solution. The TPS2306 EVM is a PCB-based tool used to evaluate the performance of the device in simulated live insertion and removal actions.

#### 1.1 Features

The following list highlights some of the features of the TPS2306.

- Wide Input Operating Range: 2.75 V to 13.6 V

- Controls Ramp-Up Sequence and Slope

- Controls Ramp-Down Sequence

- Controls Inrush Current

- Precise Linear Current Amplifier

- Programmable Overcurrent Threshold

- Programmable Soft-Start Capability and Fault Timer

- Internal Charge Pump to Drive Low-Cost External N-Channel MOSFETs

- Cascadable for Three or More Supplies

- Fault Indicator Output

- Remote Shutdown/Enable Control

### 1.2 Description

The TPS2306 provides hot swap control, fault handling and sequencing of two positive voltage supplies. The input supply operating range of 2.75 V to 13.6 V makes the TPS2306 applicable in numerous digital and signaling applications.

The TPS2306 operates in conjunction with two external N-channel MOSFETs to limit inrush current, and control output sequencing and slope during live insertion events, while creating a low impedance interface between supply and load after insertion transients have passed. An on-chip linear current amplifier (LCA) provides closed-loop control of the current sourced to the load circuitry during hot swap. An internal charge pump boosts the Channel 1 input supply to fully enhance the MOSFETs under subsequent steady-state loading conditions.

A second level of power bus protection is provided by fast over-current comparators monitoring the load current levels of each channel. In a short-circuit event, the overcurrent comparators will rapidly latch off both N-channel MOSFETs.

A high degree of user programmability allows configuration of the TPS2306 over a wide range of load characteristics. Control inputs allow the module designer to set the maximum current level and inrush current profile (slew rate) during module start-up. Under fault conditions, an on-chip timer controls how long the HSPM is allowed to operate in current-control mode prior to turning off the pass elements. Timer duration is easily programmed with a single external capacitor.

Supply sequencing control is implemented via four comparator inputs to independently control the ramp-up and ramp-down of each supply output. A TTL- and CMOS-compatible enable input allows system-level control of the output status and selection of the low-power sleep mode. The open-drain FAULT output provides single line fault reporting to the system host or controller.

#### 2 The TPS2306 EVM Kit

The TPS2306 EVM kit is a two-board platform that enables designers to rapidly learn about the TPS2306 operation, and evaluate its performance during hot swap actions. The hot swap board (TI part number SLUP056) simulates the plug-in or module side of the power interface in a target hot-swappable system. It contains the TPS2306 device, MOSFET switches, programming circuitry, and some load electronics. This board is used in conjunction with the TPS2300 hot swap interface board (TI part number SLVP155). The interface card simulates the backplane side of the system.

#### 2.1 The TPS2306 Hot Swap EVM Board

#### 2.1.1 Module Description

As supplied from the factory, the hot swap board is configured for a 5.0-V and 3.3-V system. By way of the P1 fingers connector and the interface card, 5.0-V power is applied to the HSPM Channel 1 controller, and 3.3-V power is applied to Channel 2. The default configuration is set up for Channel 1 ramping up first, with Channel 2 ramp-up controlled by the Channel 1 output status. Turnoff sequencing is set up for Channel 2 turning off first, with Channel 1 turnoff controlled by the Channel 2 output status. User modifications of the sequencing programming is easily achieved via the installation and removal of the appropriate 0805 jumpers and resistors, as described in Section 4.3 (Changing the Output Sequencing).

The Channel 1 constant-current mode level (IMAX1) has been set to 2.0 A; Channel 2 IMAX is preset to 4.0 A. These thresholds are user-configurable; see Section 4.4 (Setting the Constant-Current Mode Output Level) for details.

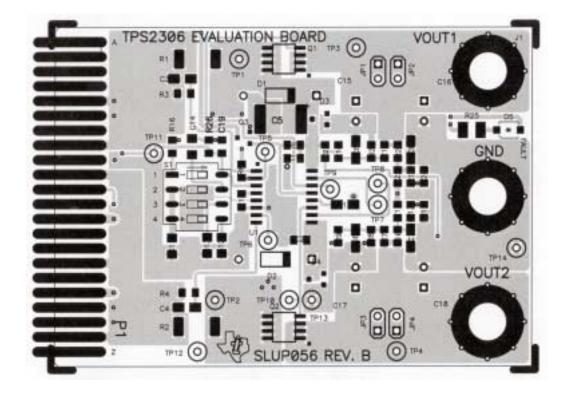

The hot swap EVM top layer assembly is shown in Figure 1.

Figure 1. Evaluation Module Top Assembly

The board has been designed with two thru-hole patterns and two jumpers on each of the two supply outputs. These can be used for the installation of large-value electrolytic capacitors to simulate the load capacitance of the target application. The TPS2306 EVM ships from the factory with 220- $\mu$ F caps (C15 and C17) and 330- $\mu$ F caps (C16 and C18) installed for functional demonstration. In addition, banana jacks J1 through J3 are available for easy hook-up of the user's resistive or electronic loads for simulation of the application's load current levels, if desired.

Test points are provided throughout the EVM circuit for waveform monitoring. The test point connections are listed in Table 1.

Table 1. TPS2306 EVM Test Points

| REFERENCE<br>DESIGNATOR | SIGNAL NAME | DESCRIPTION                                             |  |  |

|-------------------------|-------------|---------------------------------------------------------|--|--|

| TP1                     | VCC         | VCC supply to TPS2306, and Channel 1 current sense node |  |  |

| TP2                     | CS2         | Channel 2 current sense                                 |  |  |

| TP3                     | VOUT1       | Channel 1 output voltage                                |  |  |

| TP4                     | VOUT2       | Channel 2 output voltage                                |  |  |

| TP5 UP1                 |             | Channel 1 rampup comparator input                       |  |  |

| TP6                     | UP2         | Channel 2 rampup comparator input                       |  |  |

| TP7                     | DOWN1       | Channel 1 rampdown comparator input                     |  |  |

| TP8                     | DOWN2       | Channel 2 rampdown comparator input                     |  |  |

| TP9                     | GATE1       | Channel 1 (switch Q1) gate                              |  |  |

| TP10                    | GATE2       | Channel 2 (switch Q2) gate                              |  |  |

| TP11                    | ENABLE      | ENABLE input to the TPS2306                             |  |  |

| TP12                    | GND         | Circuit common (ground) node                            |  |  |

| TP13                    | GND         | Circuit common (ground) node                            |  |  |

| TP14                    | GND         | Circuit common (ground) node                            |  |  |

Switch S1 is used for easy selection from among the preset fault timer values available in the default configuration. The timing capacitors installed correlate to different combinations of the load capacitors, as detailed in Table 7. In addition, a fourth timing capacitor slot is open at C14 for installation of a user-selected timing cap for even larger loads.

## 2.1.2 EVM Schematic Diagram and Bill of Materials (BOM)

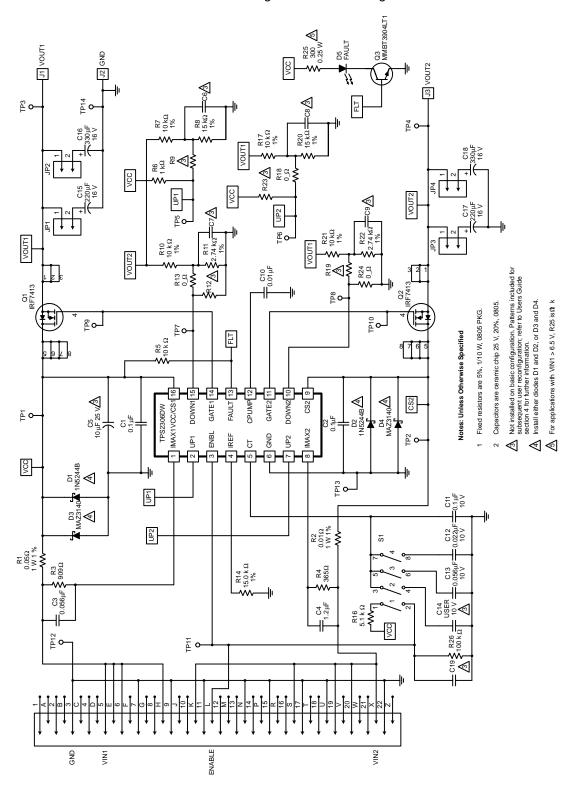

The TPS2306 evaluation module schematic diagram is shown in Figure 2.

Figure 2. EVM Schematic Diagram

The TPS2306 evaluation module bill of materials is shown below in Table 2.

Table 2. TPS2306 Hot Swap Evaluation Module Bill of Materials (SLUP056A-001)

|            | REFERENCE<br>DESIGNATOR  | QTY | DESCRIPTION                                                        | MANUFACTURER            | PART NUMBER       |

|------------|--------------------------|-----|--------------------------------------------------------------------|-------------------------|-------------------|

|            | C12                      | 1   | Ceramic, 0.022 µF, 10 V, 10%, X7R, 1206                            | Kemet                   | C1206C223K8RAC    |

|            | C3, C13                  | 2   | Ceramic, 0.056 μF, 10 V, 10%, X7R, 1206                            | Kemet                   | C1206C563K8RAC    |

|            | C11                      | 1   | Ceramic, 0.1 μF, 10 V, 10%, X7R, 1206                              | Kemet                   | C1206C104K8RAC    |

|            | C4                       | 1   | Ceramic, 1.2 μF, 10 V, 10%, X7R, 1206                              | Kemet                   | C1206C125K8RAC    |

|            | C19                      | -   | Not installed                                                      |                         |                   |

| Capacitor  | C1, C2                   | 2   | Ceramic, 0.1 μF, 25 V, 20%, Z5U, 0805                              | Venkel                  | C0805Z5U250-104MN |

|            | C10                      | 1   | Ceramic, 0.01 µF, 50 V, 20%, Z5U, 0805                             | Venkel                  | C0805Z5U500-103MN |

|            | C5                       | _   | Not installed                                                      |                         |                   |

|            | C15, C17                 | 2   | Aluminum electrolytic, 220 μF, 16 V, 20%                           | Panasonic               | EEU-FC1C221       |

|            | C16, C18                 | 2   | Aluminum electrolytic, 330 μF, 16 V, 20%                           | Panasonic               | EEU-FC1C331       |

|            | D5                       | 1   | LED, ultra bright red, GW                                          | Panasonic               | LN1261CAL         |

| Diode      | D3, D4                   | 2   | Zener, 14 V, 0.2 W, 2.5%, SC-59                                    | Panasonic               | MAZ3140-M         |

|            | D1, D2                   | -   | Not installed                                                      |                         |                   |

| Jack       | J1 – J3                  | 3   | Banana, non-ins, PC mount                                          | Pomona                  | 3267              |

| Jumpers    | JP1 – JP4                | 4   | IEADER, single row, 0.100 centers, 0.025 quare, 0.230 head Sullins |                         | PTC36SAAN         |

|            | Q3                       | 1   | NPN, small signal, type 3904, SOT-23                               | Zetex                   | FMMT3904          |

| Transistor | Q1, Q2                   | 2   | MOSFET, N-channel, V(BR)>30 V, SOIC-8                              | International Rectifier | IRF7413           |

|            | R13, R18, R24            | 3   | $0~\Omega$ jumper, $0805$                                          | Venkel                  | CR0805-10W000J    |

|            | R9, R12, R19, R23        | -   | Not installed                                                      |                         |                   |

|            | R6                       | 1   | 1.0 kΩ, 0.1 W, 5%, 0805                                            | Venkel                  | CR0805-10W102J    |

|            | R16                      | 1   | 5.1 kΩ, 0.1 W, 5%, 0805                                            | Venkel                  | CR0805-10W512J    |

|            | R26                      | 1   | 100 kΩ, 0.1 W, 5%, 0805                                            | Venkel                  | CR0805-10W104J    |

|            | R4                       | 1   | 365 Ω, 0.1 W, 1%, 0805                                             | Venkel                  | CR0805-10W3650F   |

| Resistor   | R3                       | 1   | 909 Ω, 0.1 W, 1%, 0805                                             | Venkel                  | CR0805-10W9090F   |

| Kesisioi   | R11, R22                 | 2   | 2.74 kΩ, 0.1 W, 1%, 0805                                           | Venkel                  | CR0805-10W2741F   |

|            | R5, R7, R10, R17,<br>R21 | 5   | 10.0 kΩ, 0.1 W, 1%, 0805                                           | Venkel                  | CR0805-10W1002F   |

|            | R8, R14, R20             | 3   | 15.0 kΩ, 0.1 W, 1%, 0805                                           | Venkel                  | CR0805-10W1502F   |

|            | R25                      | 1   | 300 Ω, 0.25 W, 5%, 1210                                            | Panasonic               | ERJ-14(Y)J301     |

|            | R2                       | 1   | 0.01 Ω, 1 W, 1%, 2512                                              | Panasonic               | ERJ-M1WSFR01U     |

|            | R1                       | 1   | 0.05 Ω, 1 W, 1%, 2512                                              | Panasonic               | ERJ-L1WKFR05U     |

| Switch     | S1                       | 1   | Dip, 4 position, SPST, SMD                                         | C & K                   | SD04H1SK(D)       |

| _          | TP1 – TP11               | 11  | Red, 1mm                                                           | Keystone                | 5000              |

| Test point | TP12 – TP14              | 3   | Black, 1mm                                                         | Keystone                | 5001              |

| IC         | U1                       | 1   | Dual sequencing hot swap power manager, SOIC-16                    | TI                      | TPS2306DW         |

#### 2.2 The TPS2300 Hot Swap Interface Card

#### 2.2.1 Description

The interface card is used to simulate the backplane side of the application system. A 44-pin card edge connector mates to the P1 connector on the hot swap EVM. The connector and EVM card are keyed to maintain proper orientation of the two boards for insertion.

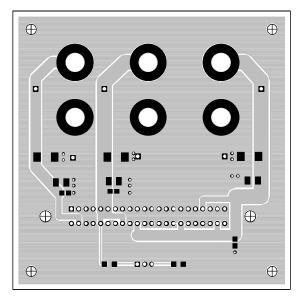

A pictorial of the interface card top layer is shown in Figure 3.

Top Layer

Top Assembly

Figure 3. Interface Card Top Assembly

Banana jacks are supplied for connection of the two input supplies to be hot swapped. In addition, land patterns have been included for the installation of backplane capacitance as required. Switch S1 can be used to toggle the TPS2306 ENABLE signal for device testing.

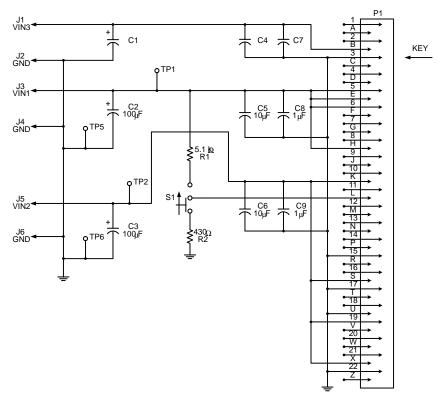

## 2.2.2 Interface Card Schematic Diagram and Bill of Materials (BOM)

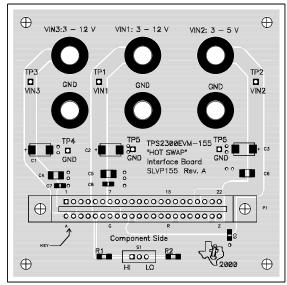

The hot swap interface card schematic diagram is shown in Figure 4.

UDG-01064

Figure 4. Hot Swap Interface Card Schematic

The bill of materials for the hot swap interface card is shown below in Table 3.

Table 3. Hot Swap Interface Card Bill of Materials (SLVP155A-003)

|            | REFERENCE<br>DESIGNATOR | QTY | DESCRIPTION                                           | MANUFACTURER | PART NUMBER       |

|------------|-------------------------|-----|-------------------------------------------------------|--------------|-------------------|

|            | C1                      | _   | Not installed                                         |              |                   |

|            | C2, C3                  | 2   | Tantalum, 100 μF, 16 V, 20%, EIA D                    | AVX          | TPSD-107M016R0150 |

| 0 "        | C4                      | _   | Not installed                                         |              |                   |

| Capacitor  | C5, C6                  | 2   | Ceramic, 10 μF, 16 V, 80/–20%, Y5V, 1210              | TDK          | GRM235Y5V106Z016  |

|            | C7                      | _   | Not installed                                         |              |                   |

|            | C8, C9                  | 2   | Ceramic, 1.0 μF, 16 V, 80/–20%, Y5V, 0805             | Panasonic    | ECJ-2VF1C105Z     |

|            | J1, J2                  | _   | Not installed                                         |              |                   |

| Jack       | J3 – J6                 | 4   | Banana, non-ins, PC mount                             | Pomona       | 3267              |

| Connector  | P1                      | 1   | 44-pin edge, 0.062 PCB, vertical mount, 0.100 centers | Cinch        | 50-22SN-11        |

| 5          | R1                      | 1   | 5.1 kΩ, 0.125 W, 5%, 1206                             | Panasonic    | ERJ-8GEYJ512      |

| Resistor   | R2                      | 1   | 430 Ω, 0.125 W, 5%, 1206                              | Panasonic    | ERJ-8GEYJ431      |

| Switch     | S1                      | 1   | Slide, SPDT, vertical actuator, 200 mA                | E-Switch     | EG1218            |

|            | TP1, TP2                | 2   | Red, 1 mm                                             | Farnell      | 240–345           |

| Test point | TP3, TP4                | _   | Not installed                                         |              |                   |

|            | TP5, TP6                | 2   | Black, 1 mm                                           | Farnell      | 240-333           |

### 2.3 TPS2306 EVM Kit Operating Specifications

Component selection for the TPS2306 EVM was done to configure the circuit for the input and load conditions shown in Table 4. Therefore, these parameters describe the intended operating conditions of the module. Current limit and fault timeout options were determined using the nominal load currents shown. In addition, the load electronics were assumed to have the minimum Under Voltage Lockout (UVLO) thresholds shown. Instead of UVLO protection, another applicable implementation would be one in which the load electronics are held in reset for at least the period of the supply voltage ramps.

**Table 4. Evaluation Module Design Parameters**

| PARAMETER                      | MIN | NOM  | MAX | UNITS |

|--------------------------------|-----|------|-----|-------|

| Operating temperature range    | -40 |      | 85  | °C    |

| Supply voltage 1 (VIN1)        |     | 5.0  |     | VDC   |

| Tolerance on VIN1              |     | ± 10 |     | %     |

| Supply voltage 2 (VIN2)        |     | 3.3  |     | VDC   |

| Tolerance on VIN2              |     | ± 5  |     | %     |

| UVLO threshold, channel 1 load | 4.0 |      |     | VDC   |

| UVLO threshold, channel 2 load | 3.0 |      |     | VDC   |

| Channel 1 load current         |     | -0.5 | ·   | Α     |

| Channel 2 load current         |     | -2.0 |     | Α     |

NOTES:

- 1. All voltages are with respect to the PCB GND node.

- 2. Currents are positive into and negative out of the specified terminal.

- 3. Channel 1 load current is limited by installed value and rating of resistor R1.

The TPS2306 EVM was designed with a high degree of user-programmability, as described in Section 4 (Reconfiguring the EVM). This includes modifications for different input voltage and load current conditions. However, under no circumstances should the EVM be operated beyond the input supply or load current levels specified in Table 5.

**Table 5. EVM Absolute Maximum Ratings**

| PARAMETER                       | NODE  | MIN | MAX  | UNITS |

|---------------------------------|-------|-----|------|-------|

| Supply voltage 1                | VIN1  | 4   | 13.6 | V     |

| Supply voltage 2                | VIN2  | 3   | 13.6 | V     |

| Channel 1 output (load) current | VOUT1 |     | -4.2 | Α     |

| Channel 2 output (load) current | VOUT2 |     | -7.0 | Α     |

NOTES:

- 1. All voltages are with respect to the PCB GND node.

- 2. Currents are positive into and negative out of the specified terminal.

- 3. Channel 1 load current is limited by installed value and rating of resistor R1.

## 3 Getting Started

### 3.1 Equipment Requirements

The following test equipment is required to use the TPS2306 hot swap EVM.

- Power supply, 5 V<sub>DC</sub> at 3 amps minimum

- Power supply, 3.3 V<sub>DC</sub> at 5 amps minimum

- Oscilloscope

- Digital voltmeter

#### 3.2 Verifying the EVM Operation

#### 3.2.1 Equipment Setup

Turn on the power supplies. Set one of the supply outputs to 5 V<sub>DC</sub>, and the other to 3.3 V<sub>DC</sub>.

On the interface card, place switch S1 in the LO position. On the hot swap EVM, place the individual DIP switches of S1 in the positions shown in Table 6.

Table 6. EVM Switch S1 Initial Positions

| SWITCH | POSITION |

|--------|----------|

| S1-1   | OFF      |

| S1–2   | X        |

| S1–3   | ON       |

| S1–4   | ON       |

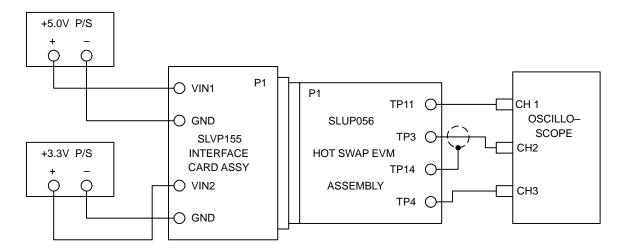

Install jumpers across terminals JP1, JP2, JP3, and JP4. Insert the hot swap EVM board into the P1 edge connector on the interface card, observing the insertion keying. Connect the power supplies, EVM boards, and oscilloscope as shown in Figure 5.

Figure 5. Equipment Setup

#### 3.2.2 Functional Test

Verify the two power supplies are ON. On the hot swap EVM, verify that the red *FAULT* LED is ON. Using the DVM, verify that both outputs at TP3 and TP4 are OFF (0 volts present).

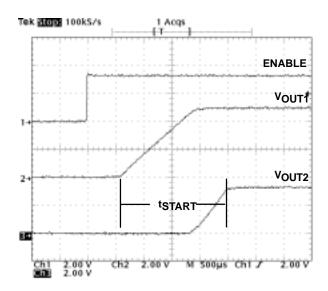

Set the oscilloscope to trigger on the rising edge of the ENABLE signal on scope Channel 1. Set the trigger mode to NORMAL. On the interface card, place switch S1 in the HI position. Verify a scope sweep is obtained which is similar to the one shown in Figure 6. The total ramp time of the two output voltages, from the start of  $V_{OUT1}$  to  $V_{OUT2}$  attaining the input dc level, should be approximately 2.1 ms.

Figure 6. Output Start-Up Waveforms

Verify the red LED is off. At test points TP3 (V<sub>OUT1</sub>) and TP4 (V<sub>OUT2</sub>) verify that the input supply potential is present.

On the interface card, set switch S1 to the LO position. Verify that the two output node voltages decay to 0 volts.

**NOTE:** Due to the amount of capacitance present at the EVM board outputs, the output decay will be very slow.

**NOTE:** In the following procedure step, if the EVM LED turns OFF, the interface card S1 switch should be returned to the LO position without unnecessary delay. This will prevent excessive temperature rise in the interface card and EVM UUT, and possible subsequent damage to the boards.

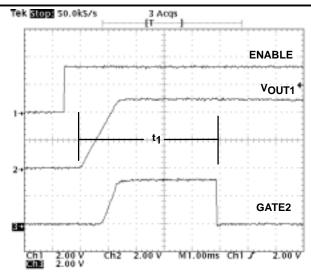

Move the scope channel 3 probe to test point TP10 on the hot swap EVM. Connect a shorting jumper between banana jacks J2 and J3 on the EVM. On the interface card, place switch S1 in the HI position. Verify that the EVM red *FAULT* LED remains ON.

Verify a scope sweep was obtained similar to the one shown in Figure 7. The time t<sub>1</sub> in the figure should be approximately 4.84 ms. Verify the EVM outputs are OFF (0 volts present at J1 (TP3) and J3 (TP4)).

Figure 7. Fault Time-Out Waveforms

### 3.3 Using the EVM Kit to Evaluate the TPS2306 HSPM

Procedures similar to the steps of Section 3.2.2 (Functional Test) for functional test of the EVM board can be used to continue evaluation of the TPS2306 device. Alternatively, to have the TPS2306 turn on the outputs automatically after insertion, see Section 4.7, Automatic Power-Up, for setup instructions. Also, input supply and output load characteristics can be modified to better approximate the user's system parameters. See Section 4 for details on modifying the EVM configuration.

## 4 Reconfiguring the EVM

## 4.1 Pre-Configured Fault Timer Settings

The TPS2306 EVM is easily modified to simulate different load characteristics. Onboard capacitors C15 – C18 are available for easy hookup to their respective EVM outputs. Switch S1 selects the appropriate timeout period for the supplied load caps. Table 7 summarizes some of the preset timer settings that should be used for different load combinations.

Table 7. Example Load Capacitance/Fault Timer Setting Combinations

| JUMPERS       | JUMPERS       | LOAD CAP (F) | CAP ( F) S1-3 S1- |      | FAULT T | IME(ms) |

|---------------|---------------|--------------|-------------------|------|---------|---------|

| JP1/JP3       | JP2/JP4       | (EA. CHAN)   | 31-3              | S1–4 | NOM     | MIN     |

| Installed     | Not installed | 220          | OFF               | OFF  | 3.00    | 2.08    |

| Not installed | Installed     | 330          | OFF               | ON   | 3.66    | 2.53    |

| Installed     | Installed     | 550          | ON                | OFF  | 4.68    | 3.24    |

### 4.2 Modifying Load Characteristics

Values of load capacitance other than those supplied can be simulated by removing capacitors C15 and C16 (EVM Channel 1) and C17 and C18 (EVM Channel 2) and replacing them with the appropriate values to represent the user's application. Alternatively, the user's test loads can be connected via banana jacks J1 through J3.

**NOTE:** If connecting loads to the EVM outputs, use appropriately rated loads for the anticipated power dissipation when the EVM outputs are ON.

When the load characteristics are modified, the fault timer setting may need to be adjusted accordingly. Please refer to the TPS2306 device data sheet for complete details on determining a value for the timing capacitance according to the load type and value. Once the applicable capacitor value is known, it may be possible to approximate it on the EVM using poles 3 and 4 of S1 to switch capacitors C11 – C13 in and out of the circuit. If not, these component PCB patterns, and also the C14 slot, are available for installation of user–selected capacitors. The component lands are sized for EIA 1206-packaged devices.

#### 4.3 Changing the Output Sequencing

As supplied from the factory, the TPS2306 EVM board is configured to ramp Channel 1 up first and down last, with respect to the Channel 2 output. For the TPS2306 device, sequencing can be easily programmed with the use of resistive dividers on the two channel outputs, or to other control inputs. Additional circuitry has been laid out on the EVM module for the installation of SMD jumpers and resistors as required to program alternate output sequences. See Table 8 below for EVM setup details to obtain various sequencing options.

| RAMP-UP<br>SEQUENCE | RAMP-DOWN<br>SEQUENCE | R6 | R9 | R18 | R23 | R12 | R13 | R19 | R24 |

|---------------------|-----------------------|----|----|-----|-----|-----|-----|-----|-----|

| (2) 1,2             | 2,1                   | 1k | NI | 0   | NI  | NI  | 0   | Х   | 0   |

| 1,2                 | 1,2                   | 1k | NI | 0   | NI  | 0   | Χ   | 0   | NI  |

| 2,1                 | 1,2                   | NI | 0  | NI  | 1k  | 0   | Х   | 0   | NI  |

| 2,1                 | 2,1                   | NI | 0  | NI  | 1k  | NI  | 0   | Х   | 0   |

| Track               | Х                     | 1k | NI | NI  | 1k  | 0   | Х   | Х   | 0   |

Table 8. TPS2306 EVM Output Sequence Programming

NOTES: 1. Key to table entries:

NI = not installed

X = don't care

2. Default (factory) configuration

In addition to the sequencing order, the relative ramp-up and ramp-down timing between the two channels can be modified from the default settings. Resistors R8 (for Channel 1) and R20 (for Channel 2) can be changed to adjust the threshold at which the controlled channel begins to ramp up when its turnon condition is a function of the other channel's output status. The value of R8 or R20 ( $R_{ONB}$  in the equation below) is given by equation 1.

$$R_{ONB} = \frac{V_{UP}}{\left(V_{RAMP} - V_{UP}\right)} \times R_{ONA}$$

(1)

Where:

- V<sub>UP</sub> = the UPx comparator reference voltage, nominally 1.5 V

- V<sub>RAMP</sub> = desired output voltage of the primary channel at which the secondary channel should be ramped up

- R<sub>ONA</sub> = the top leg of the resistor divider, R7 or R17

If resistors R7 and R17 are left at the original values of 10 k $\Omega$ , equation 1 becomes:

$$R_{ONB} = \frac{V_{UP}}{\left(V_{RAMP} - V_{UP}\right)} \times 10 \text{ k}\Omega$$

(2)

For ramp-down sequencing, resistors R11 (for Channel 1) and R22 (for Channel 2) can be changed to adjust the threshold at which the controlled channel turns off when its turnoff condition is a function of the other channel's output status. The value of R11 or R22 (R<sub>OFFB</sub> in the equation below) is given by equation 3.

$$R_{OFFB} = \frac{V_{DN}}{(V_{OFF} - V_{DN})} \times R_{OFFA}$$

(3)

Where:

- V<sub>DN</sub> = the DNx comparator reference voltage, nominally 0.5 V

- V<sub>OFF</sub> = the desired voltage of the turnoff control channel at which the controlled channel gate drive should be turned off

- R<sub>OFFA</sub> = the top leg of the resistor divider, R10 or R21

If resistors R10 and R21 are left at the original value of 10 k $\Omega$ , equation 3 becomes:

$$R_{OFFB} = \frac{V_{DN}}{\left(V_{OFF} - V_{DN}\right)} \times 10 \text{ k}\Omega$$

(4)

The TPS2306 data sheet specifies the minimum and maximum ramp comparator thresholds, shown in Table 9 for quick reference. Once the desired ramp dividers are determined from equations 1 and 3, the minimum and maximum ON and OFF thresholds should be checked against the supply tolerances to ensure proper sequencing operation over the input supply voltage range.

Table 9. Ramp-Up and Ramp-Down Comparator Specifications

| PARAMETER                                       | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------------|------|------|------|-------|

| V <sub>UP</sub> , rampup trip level threshold   | 1.35 | 1.50 | 1.65 | V     |

| V <sub>DN</sub> , rampdown trip level threshold | 0.35 | 0.50 | 0.65 | V     |

### 4.4 Setting the Constant-Current Mode Output Level

During an output start-up sequence, the TPS2306 linearly controls the magnitude of the output current sourced to the loads. This maximum linear mode current, referred to as IMAX, can be set by the user with external programming resistors. This allows flexibility in controlling the rate at which the load capacitance is charged to steady-state levels. The current limits of the two channels can be set independently of each other. For the TPS2306 EVM, the current limit programming resistors are R14 (to set the reference current), R3 (for Channel 1) and R4 (for Channel 2).

To modify the IMAX levels of the EVM, appropriate resistor values are determined using equation 5. For a desired IMAXx value, the value of R3 or R4 (R<sub>IMAXx</sub> in the equation) is given by:

$$R_{\text{IMAXx}} = \frac{\text{IMAXx} \times R_{\text{SNSx}}}{(1.1) \times (1.5 \text{ V})/R14}$$

(5)

Where:

- IMAXx = the desired current level for Channel x, and

- R<sub>SNSx</sub> = the value of that Channel's current sense resistor

As an example, the Channel 1 IMAX current of the TPS2306 EVM, as supplied from the factory, is a nominal 2 A. Using equation 5, the value of R3 is found as follows:

$$R3 = \frac{IMAX1 \times R1}{\underbrace{(1.1) \times (1.5 \text{ V})}_{R14}} = \frac{(2.0) \times (0.05 \Omega)}{\underbrace{(1.1) \times (1.5 \text{ V})}_{(15 \text{ k}\Omega)}} = 909 \Omega$$

(6)

For additional details on setting the IMAX levels, refer to the TPS2306 device data sheet.

#### 4.5 Optional Soft-Start With the TPS2306

The TPS2306 can be used with or without inrush soft-start. Without soft-start, when the output turn-on conditions are met, the load currents virtually step to the programmed IMAX level, where they are limited during the start-up transient. Once the loads' input bulk capacitance is charged to the input dc levels, the sourcing current tapers to the steady-state load level. In this configuration, the TPS2306 provides constant-current charging of the loads' capacitance. To test this mode of operation, the user should remove capacitors C3 (for Channel 1) and C4 (for Channel 2).

Even with the current-limiting function provided by the internal LCA control, some power distribution systems may still be sensitive to the di/dt event that occurs when the pass FETs are first turned on. For these applications, inrush slew-rate control (soft-start) is easily implemented with the TPS2306, by installing capacitors in parallel with the IMAX programming resistors. The TPS2306 EVM is designed to demonstrate the soft-start capability of the device. Capacitors C3 and C4 are installed to program the slew rates to two very different curves. Adding a capacitor in parallel with the IMAX resistor applies an RC time-constant to the reference voltage generation at the IMAXx pins of the device. Due to the closed-loop control provided by the internal amplifiers during output ramp-up, the load current supplied also ramps with a corresponding RC characteristic. For the TPS2306 EVM, Channel 1 sourcing current has a time constant of only  $(0.056~\mu F)$  \*  $(909~\Omega)$  = 51  $\mu$ s, while the Channel 2 constant is on the order of  $(1.2~\mu F)$  \*  $(365~\Omega)$   $\cong$  440  $\mu$ s.

For additional information on establishing the inrush current profile, and a discussion about its effect on load start-up times, refer to the device data sheet.

#### 4.6 Configuring the EVM for High Voltage Applications

The TPS2306 EVM can be easily configured for high voltage applications, up to 13.6 V maximum supply input. For these applications, two steps must be taken.

- 1. Set the fault timing, sequencing, and IMAX component values for the targeted supplies and load characteristics, as described in Sections 4.1 4.4.

- 2. For applications where the Channel 1 supply is greater than 6.5 V (e.g., 10-V or 12-V systems), remove resistor R25 and replace it with a 1-k $\Omega$ , SMD 1210-size resistor.

#### 4.7 Automatic Power-Up

The TPS2306 EVM and interface card can be set up to bring up the supply outputs automatically after board insertion. The following two steps will select an autonomous power-up mode of operation.

- 1. On the hot swap EVM, set switch S1-1 in the ON position.

- 2. Remove resistor R1 from the interface card. R1 is located near switch S1 (refer to Figure 3). Place switch S1 in the HI position.

The EVM now brings up the outputs automatically when it is inserted into the interface card's P1 connector. To create a short start-up delay from insertion, install an appropriate value, 0805-size capacitor at C19 on the EVM card.

For proper operation of the supply turnoff sequencing, the TPS2306 device itself must remain powered up during the shutdown event. To observe operation of this function, return switch S1-1 to the OFF position prior to PCB removal from the interface card.

#### **EVM WARNINGS AND RESTRICTIONS**

It is important to operate this EVM within the specified input and output ranges described in the EVM User's Guide.

Exceeding the specified input range, (see Table 5), may cause unexpected operation and/or irreversible damage to the EVM. If there are questions concerning the input range, please contact a TI field representative prior to connecting the input power.

Applying loads outside of the specified output range, (see Table 5), may result in unintended operation and/or possible permanent damage to the EVM. Please consult the EVM User's Guide prior to connecting any load to the EVM output. If there is uncertainty as to the load specification, please contact a TI field representative.

During normal operation, some circuit components may have case temperatures greater than 60°C. The EVM is designed to operate properly with certain components above 60°C as long as the input and output ranges are maintained. These components include but are not limited to pass transistors, Q1 and Q2, current sense resistors, R1 and R2, and limiting resistor R25. These types of devices can be identified using the EVM schematic located in the EVM User's Guide. When placing measurement probes near these devices during operation, please be aware that these devices may be very warm to the touch.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2001, Texas Instruments Incorporated

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, license, warranty or endorsement thereof.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Resale of TI's products or services with <u>statements different from or beyond the parameters</u> stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Also see: Standard Terms and Conditions of Sale for Semiconductor Products, www.ti.com/sc/docs/stdterms.htm

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265