Application Report SLVA273-April 2007

## DaVinci<sup>™</sup> Sequencing Using The TPS65023

Todd Vanyo

Low Power DC/DC Systems

## ABSTRACT

The Texas Instruments DaVinci<sup>™</sup> family of application processors has specific sequencing and reset requirements. The TPS65023, designed to supply the DaVinci<sup>™</sup> family's power needs, has some built-in, but not immediately obvious, functions that can also easily and cheaply support the sequencing and reset requirements, eliminating the need for external comparators or supervisors. This document starts with a quick overview of the DaVinci<sup>™</sup> family sequencing requirements. The TPS65023 features – two general-purpose comparators and a Power Good output – are then described individually. After the setup, the simple connections combining them to fulfill the power sequencing and reset requirements are detailed.

The DaVinci<sup>™</sup> family of processors is forgiving in power sequencing. The only hard requirement, listed in Section 5.3.1 of the data sheets for TMS320DM6441 (<u>SPRS359</u>), TMS320DM6443 (<u>SPRS282</u>), and TMS320DM6446 (<u>SPRS283</u>), is the need for the ARM microcontroller core (1.2-V domain) to come up prior to the Memory (1.8-V domain) and I/O (3.3-V domain). The Memory and I/O voltages may come up in any order after the ARM core is powered. The DaVinci<sup>™</sup> reset signal, RESET, must also be held low until all three voltage domains are fully up.

These straightforward requirements are easy to implement using features built into the TPS65023. The next part of this document describes the features in more detail before presenting the application solution to DaVinci<sup>™</sup> sequencing.

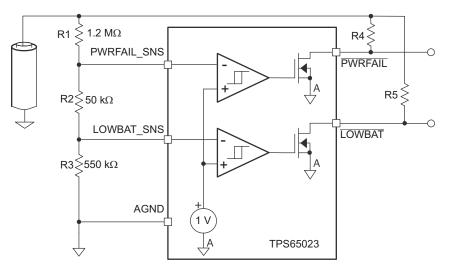

Two pairs of input/output pins, LOWBAT\_SNS with  $\overline{LOWBAT}$  and PWRFAIL\_SNS with  $\overline{PWRFAIL}$ , are often overlooked in the TPS65023. These are the input/output pairs for two independent and stand-alone comparators, with a 1-V  $\pm$ 1% reference supplied internally by the TPS65023. The intended use of the pins was signaling to the processor when the battery supplying power reached a low threshold (LOWBAT) and when the system needed to be shut down (PWRFAIL) – this lead to the pin names. Using an external resistor divider network, the designer can set the voltage when each output pin activates, flagging the processor. The outputs are the open-drain inversion of the comparator output. Figure 1 shows a block diagram of the comparators and how they could be used as originally intended, with the LOWBAT signal going low at 3.27 V and the PWRFAIL signal going low at 3 V.

DaVinci is a trademark of Texas Instruments.

1

Figure 1. TPS65023 Comparators (Original Intended Use)

The comparators reference voltage and hysteresis specifications are given in document <u>SLVS670</u> under the heading of Voltage Comparator Detectors.

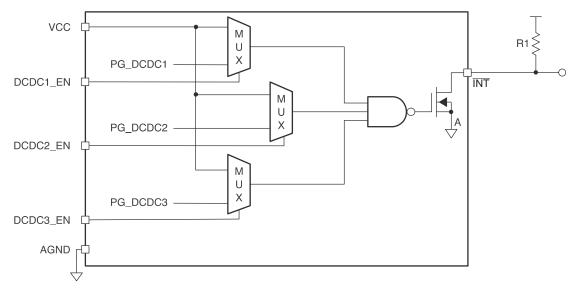

The TPS65023 consists of three step-down converters and two linear regulators that default to the voltages needed by the DaVinci<sup>™</sup> processor family. Each converter has a Power Good comparator that enables when the converter enables and toggles when the output voltage is 95% of the target voltage. The inverted output of each comparator is available as a flag in the memory map, accessible via I2C at register address 0x01 (PGOODZ register). In addition to the Power Good flags available in software, the INT pin is an open-drain output that is the logical AND of the Power Good comparator outputs for each enabled converter. When a converter is enabled and its output voltage is below 10% of the target voltage, the INT pin is pulled to ground. Figure 2 shows a logical representation of the INT function.

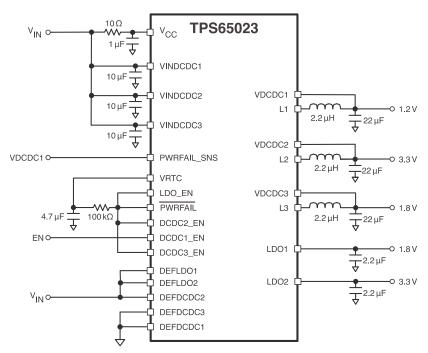

To fulfill the DaVinci<sup>™</sup> sequencing requirements, the 1.2-V output from the TPS65023 must be up prior to the 1.8-V and 3.3-V outputs. One way to achieve this is to connect the DCDC1 output directly to the DCDC2\_EN, DCDC3\_EN, and LDO\_EN inputs. However, the digital V<sub>IH</sub> of these input pins is 1.2 V minimum. This does not provide sufficient headroom in the event of transients on the DCDC1 output. But

one of the comparators previously described can be used to compare the 1.2-V output to the 1-V reference voltage. With the corresponding comparator output pulled up to VRTC, a voltage available whenever the  $V_{CC}$  voltage is present, and tied to the enables for the other converters and linear regulators, the sequencing requirements would be met. Figure 3 gives a schematic view of the connections to obtain the necessary sequencing .

NOTE: Not all TPS65023 pins are shown, only those needed for sequencing the converters.

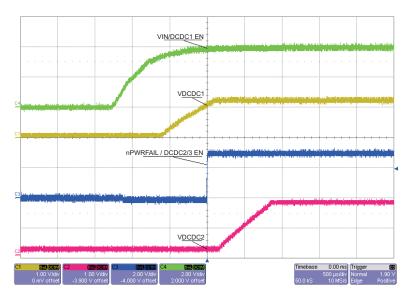

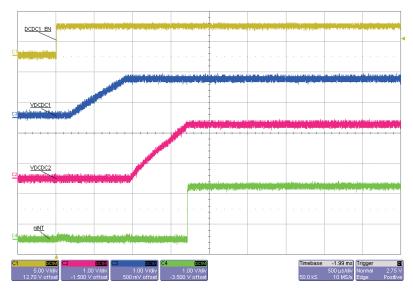

Figure 4 shows the scope trace of the power up of DCDC1 and DCDC2, using the connections shown in Figure 3.

Figure 3. Sequencing Schematic

Figure 4. Sequencing Trace

Note in Figure 4 that DCDC2 is enabled before DCDC1 has reached the full 1.2 V (triggers at approximately 1 V). DCDC1 reaches 1.2 V prior to DCDC2 and DCDC3 ramping because of the delay time used to precharge to minimize inrush current, and this satisfies the DaVinci<sup>™</sup> sequencing requirements.

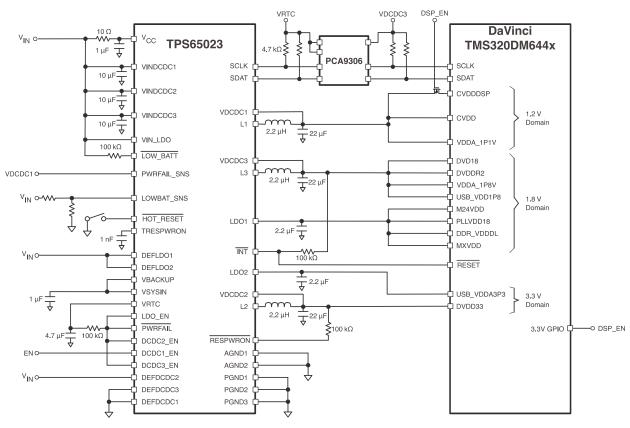

The DaVinci<sup>™</sup> reset requirement, that the RESET input be held low until all the voltages are available, can be met by using the Power Good logic that drives the INT pin on the TPS65023. Because INT stays low when an enabled converter is out of regulation, the INT pin can be pulled up to the 1.8-V converter (RESET on the DaVinci<sup>™</sup> family is a 1.8-V input) and tied directly to RESET. This works because the INT pin is low while DCDC1 ramps up. When DCDC1 hits approximately 1 V (still below valid regulation), DCDC2 and DCDC3 are enabled – thus holding INT low until all converters are within regulation. Figure 5 shows a full schematic for the TPS65023 connection to the DaVinci<sup>™</sup> processors, and Figure 6 shows the scope trace with the INT signal (labeled nINT). The schematic in Figure 5 also shows a level shifter needed to enable the I2C from the DaVinci<sup>™</sup> processor (1.8-V I/O) to the TPS65023 (3.3-V I/O).

Figure 5. Full Schematic for Sequencing and Reset

Figure 6. Scope Trace of INT Signal for DaVinci™ Reset

To summarize, the TPS65023 has two uncommitted comparators and a Power Good output that can be combined to fulfill the sequencing and reset requirements of the DaVinci<sup>™</sup> family of processors. Using one comparator to monitor the output of the core voltage converter (DCDC1) and enable the other converters provides the necessary sequencing. Using the Power Good output, pin INT, provides a simple way of holding the processor in reset until all the voltage rails are up and within regulation. This is a minimal design, eliminating the need for external voltage supervision and saving board space and component cost.

## **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products           |                        | Applications       |                           |

|--------------------|------------------------|--------------------|---------------------------|

| Amplifiers         | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters    | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface          | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic              | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt         | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers   | microcontroller.ti.com | Security           | www.ti.com/security       |

| Low Power Wireless | www.ti.com/lpw         | Telephony          | www.ti.com/telephony      |

|                    |                        | Video & Imaging    | www.ti.com/video          |

|                    |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2007, Texas Instruments Incorporated