# Powering the Freescale<sup>™</sup> i.MX25 Using the TPS65051

Sanjay Pithadia and Christian Hoefling

Power Management Products

### ABSTRACT

This application report details the power requirements of the Freescale<sup>™</sup> i.MX25 processor and how to power it using the <u>TPS65051</u>, a highly-integrated power management unit (PMU) device from Texas Instruments. With its 3.3-V to 6.0-V input voltage range, output current up to 600 mA, and excellent efficiency (up to 95%), the TPS65051 PMU is an excellent choice to meet the requirements of the i.MX25.

#### Contents

| 1 | Introduction                                                  | 2  |

|---|---------------------------------------------------------------|----|

| 2 | i.MX25 Requirements                                           | 2  |

| 3 | Powering Freescale i.MX25 with the TPS65051: Reference Design | 4  |

| 4 | Detailed Design Information                                   | 8  |

| 5 | Measurement Results                                           | 9  |

| 6 | References                                                    | 10 |

### **List of Figures**

| 1 | Recommended Power-Up Sequence               | 3  |

|---|---------------------------------------------|----|

| 2 | TPS65051 PMU Block Diagram                  | 4  |

| 3 | Reference Design Schematic                  | 6  |

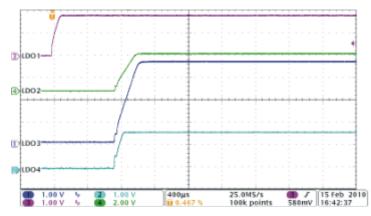

| 4 | Power-Up Sequence: DCDC1, DCDC2, LDO1, LDO2 | 9  |

| 5 | Power-Up Sequence: LDO1, LDO2, LDO3, LDO4   | 9  |

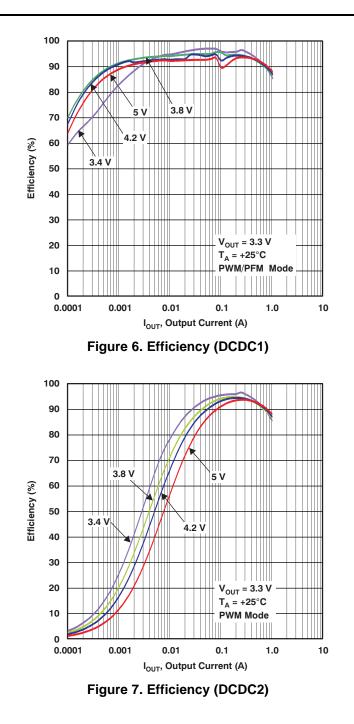

| 6 | Efficiency (DCDC1)                          | 10 |

| 7 | Efficiency (DCDC2)                          | 10 |

|   |                                             |    |

### List of Tables

| 1 | i.MX25 Voltage Requirements                   | 2 |

|---|-----------------------------------------------|---|

| 2 | TPS65051 Assignment of Converter Output Rails | 5 |

| 3 | List of Materials                             | 7 |

Freescale is a trademark of Freescale Semiconductor, Inc. All other trademarks are the property of their respective owners.

# 1 Introduction

The reference design discussed in this report applies to the entire Freescale<sup>™</sup> i.MX25 processor family. It provides all required analog and logic supply rails and the sequencing necessary to power up an i.MX25 processor.

# 2 i.MX25 Requirements

Table 1 lists the voltage requirements of the i.MX25 processor.

| Parameter                                                                  | Symbol                  | Min  | Тур                 | Max                 | Units |

|----------------------------------------------------------------------------|-------------------------|------|---------------------|---------------------|-------|

| Core supply voltage (at 266 MHz)                                           | QV <sub>DD</sub>        | 1.15 | 1.34                | 1.52                | V     |

| Core supply voltage (at 400 MHz)                                           | QV <sub>DD</sub>        | 1.38 | 1.45                | 1.52                | V     |

| Coin battery                                                               | V <sub>DD_BAT</sub>     | 1.15 | _                   | 1.55                | V     |

| I/O supply voltage GPIO1 (NFC, CSI, SDIO)                                  | NV <sub>DD_GPIO1</sub>  | 1.75 | —                   | 3.6                 | V     |

| I/O supply voltage GPIO2 (CRM, LCDC, JTAG, MISC)                           | NV <sub>DD_GPIO2</sub>  | 3.0  | 3.3                 | 3.6                 | V     |

| I/O supply voltage DDR (Mobile DDR mode) (EMI1, EMI2)                      | NV <sub>DD_MDDR</sub>   | 1.75 | —                   | 1.95                | V     |

| I/O supply voltage DDR (DDR2 mode) (EMI1, EMI2)                            | NV <sub>DD_DDR2</sub>   | 1.75 | —                   | 1.9                 | V     |

| I/O supply voltage DDR (SDRAM mode) (EMI1, EMI2)                           | NV <sub>DD_SDRAM</sub>  | 1.75 | _                   | 3.6                 | V     |

| USBPHY1 supply (HS) (USBPHY1_VDDA_BIAS,<br>USBPHY1_UPLL_VDD. USBPHY1_VDDA) | V <sub>DD_USBPHY1</sub> | 3.17 | 3.3                 | 3.43                | V     |

| USBPHY2 supply (FS) (USBPHY2_VDD)                                          | V <sub>DD_USBPHY2</sub> | 3.0  | 3.3                 | 3.6                 | V     |

| OSC24M supply (OSC24M_VDD)                                                 | V <sub>DD_OSC24M</sub>  | 3.0  | 3.3                 | 3.6                 | V     |

| PLL supply (MPLL_VDD, UPLL_VDD)                                            | V <sub>DD_PLL</sub>     | 1.4  | —                   | 1.65                | V     |

| Supply of touch screen ADC (NVCC_ADC)                                      | V <sub>DD_TSC</sub>     | 3.0  | 3.3                 | 3.6                 | V     |

| External reference of touch screen ADC                                     | V <sub>REF</sub>        | 2.5  | V <sub>DD_tsc</sub> | V <sub>DD_tsc</sub> | V     |

| Fusebox program supply voltage (FUSE_VDD)                                  | FUSEV <sub>DD</sub>     | _    | 3.6                 | —                   | V     |

<sup>(1)</sup> See Reference 1 for complete information.

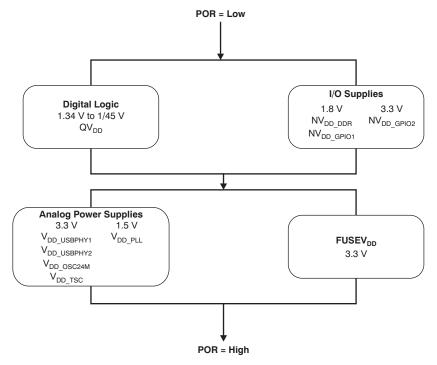

# 2.1 Power-Up/-Down Sequencing

The i.MX25 processor consists of four major sections for the power-supply voltage: digital logic domains  $(V_{DDn})$ ; I/O power supplies  $(NV_{DDx})$ ; analog power supplies; and the fuse voltage supply (FUSEV<sub>DD</sub>). These voltage groups can be integrated in several ways, depending on the operating mode and the requirements of the i.MX processor, as well as the specific application.

# 2.1.1 Power-Up Sequencing

The recommended power-up sequence for the processor follows this order:

- Step 1. Assert Power-On-Reset (POR) (POR = low)

- Step 2. Turn on the core supply voltages and I/O power supplies (NV<sub>CCx</sub>)

- Step 3. Turn on all analog power supplies (V\_{DDx}) and FUSEV\_{DD}

- Step 4. Release POR (POR = high)

Figure 1 illustrates the recommended power-up sequence.

Figure 1. Recommended Power-Up Sequence

# 2.1.2 Power-Down Sequencing

The power-down sequence has no special requirements.

# 3 Powering Freescale i.MX25 with the TPS65051: Reference Design

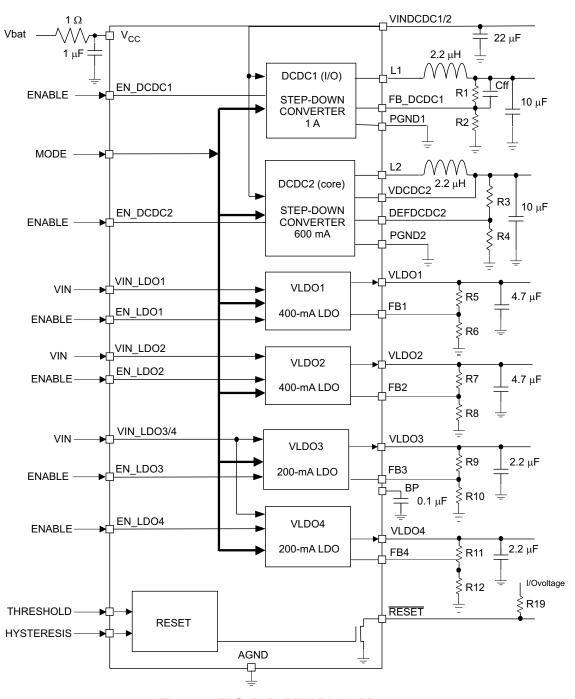

The TPS65051 is an integrated power management device, suitable for applications that require multiple power rails. The TPS65051 provides two highly efficient, 2.25-MHz step-down converters as well as four low dropout (LDO) regulators. The block diagram of the TPS65051 is shown in Figure 2.

**TPS65051**

Figure 2. TPS65051 PMU Block Diagram

Following the pattern shown in Figure 1, a power-up sequence that consists of two groups was configured and applied in the power reference design conceived for this report.

The first group in the power-up sequence consists of all rails supplied by DCDC1, DCDC2, and the LDO LDO1. The second group contains LDO2, LDO3, and LDO4. Table 2 describes the converter output rail assignents for the TPS65051.

| Supply Rail                                                              |      | Voltage (V) | TPS65051<br>Output | Sequencing<br>Order |

|--------------------------------------------------------------------------|------|-------------|--------------------|---------------------|

| QV <sub>DD</sub>                                                         | Core | 1.45        | DCDC1              | 1                   |

| $NV_{DD\_GPIO1}, NV_{DD\_GPIO2}, NV_{DD\_SDRAM}$                         |      | 3.3         | DCDC2              | 1                   |

| $NV_{DD_{MDDR}}, NV_{DD_{DDR2}}$                                         |      | 1.8         | LDO1               | 1                   |

| $V_{DD\_USBPHY1}, V_{DD\_USBPHY2}, V_{DD\_OSC24M}, V_{DD\_TSC}, V_{REF}$ |      | 3.3         | LDO2               | 2                   |

| FUSEV <sub>DD</sub>                                                      |      | 3.6         | LDO3               | 2                   |

| V <sub>DD_PLL</sub>                                                      |      | 1.6         | LDO4               | 2                   |

### Table 2. TPS65051 Assignment of Converter Output Rails

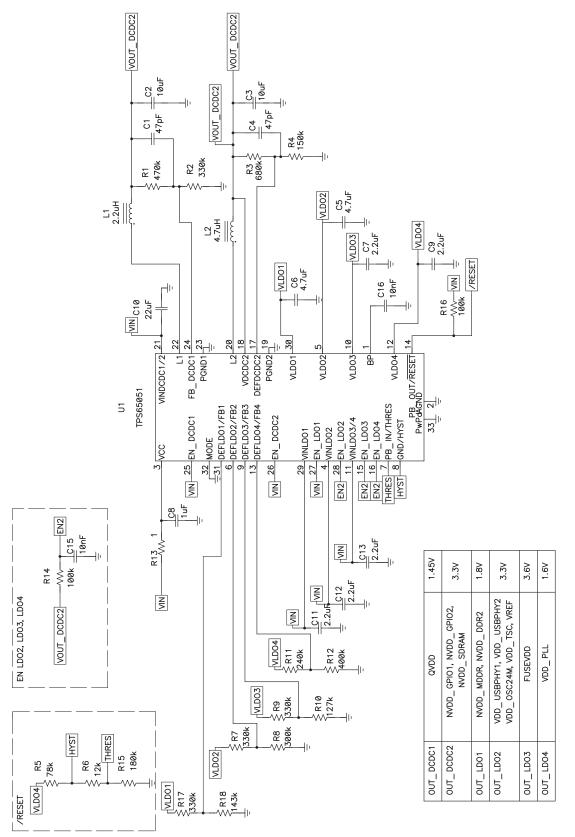

Figure 3 illustrates the reference design schematic.

# Figure 3. Reference Design Schematic

Table 3 provides the parts list for the reference design.

| Count | Ref Des                  | Value    | Description                                                                  | Size                  | Part No            | Mfr       |

|-------|--------------------------|----------|------------------------------------------------------------------------------|-----------------------|--------------------|-----------|

| 2     | C1, C4                   | 47 pF    | Capacitor, ceramic, 50V,<br>COG, 5%                                          | 0603                  | C1608C0G1H470J     | TDK       |

| 1     | C10                      | 22 µF    | Capacitor, ceramic, 6.3 V, X5R, 20%                                          | 0805                  | GRM21BR60J226ME39L | Std       |

| 2     | C15, C16                 | 10 nF    | Std                                                                          | 0805                  | Std                | muRata    |

| 2     | C2, C3                   | 10 µF    | Capacitor, ceramic, 10 V, X5R, 20%                                           | 0805                  | GRM188R60J106ME47D | muRata    |

| 2     | C5, C6                   | 4.7 µF   | Capacitor, ceramic, 10 V, X5R, 10%                                           | 0805                  | GRM21BR61A106KE19L | muRata    |

| 5     | C7, C9, C11,<br>C12, C13 | 2.2 µF   | Capacitor, ceramic, 6.3 V, X5R, 10%                                          | 0805                  | GRM188R60J225KE01D | muRata    |

| 1     | C8                       | 1 µF     | Capacitor, ceramic, 25 V, X5R, 10%                                           | 0805                  | GRM188R61E105KA12D | muRata    |

| 1     | L1                       | 2.2 µH   | Inductor, SMT, 1.3 A, 130 mΩ                                                 | 0.118 x<br>0.118 inch | LPS3015-332ML      | Coilcraft |

| 1     | L2                       | 4.7 µH   | Inductor, SMT, 1.3 A, 130 mΩ                                                 | 0.118 x<br>0.118 inch | LPS3015-332ML      | Coilcraft |

| 1     | R1                       | 470 kΩ   | Resistor, chip, 1/16W, 1%                                                    | 0603                  | Std                | Std       |

| 1     | R10                      | 127 kΩ   | Resistor, chip, 1/16W, 1%                                                    | 0603                  | Std                | Std       |

| 1     | R11                      | 240 kΩ   | Resistor, chip, 1/16W, 1%                                                    | 0603                  | Std                | Std       |

| 1     | R12                      | 400 kΩ   | Resistor, chip, 1/16W, 1%                                                    | 0603                  | Std                | Std       |

| 1     | R13                      | 1 Ω      | Resistor, chip, 1/16W, 1%                                                    | 0603                  | Std                | Std       |

| 2     | R14, R16                 | 100 kΩ   | Resistor, chip, 1/16W, 1%                                                    | 0603                  | Std                | Std       |

| 1     | R15                      | 180 kΩ   | Resistor, chip, 1/16W, 1%                                                    | 0603                  | Std                | Std       |

| 1     | R18                      | 143 kΩ   | Resistor, chip, 1/16W, 1%                                                    | 0603                  | Std                | Std       |

| 4     | R2, R7, R9,<br>R17       | 330 kΩ   | Resistor, chip, 1/16W, 1%                                                    | 0603                  | Std                | Std       |

| 1     | R3                       | 680 kΩ   | Resistor, chip, 1/16W, 1%                                                    | 0603                  | Std                | Std       |

| 1     | R4                       | 150 kΩ   | Resistor, chip, 1/16W, 1%                                                    | 0603                  | Std                | Std       |

| 1     | R5                       | 78 kΩ    | Resistor, chip, 1/16W, 1%                                                    | 0603                  | Std                | Std       |

| 1     | R6                       | 12 kΩ    | Resistor, chip, 1/16W, 1%                                                    | 0603                  | Std                | Std       |

| 1     | R8                       | 300 kΩ   | Resistor, chip, 1/16W, 1%                                                    | 0603                  | Std                | Std       |

| 1     | U1                       | TPS65051 | IC, 2.25-MHz Dual Step-Down<br>Converter with Four Low-Input<br>Voltage LDOs | QFN-32                | TPS65050/51        | TI        |

# Table 3. List of Materials

# 4 Detailed Design Information

# QV<sub>DD</sub> (1.45 V)

This rail is supplied by DCDC1.

The output voltage of DCDC1 is adjustable using an external voltage divider. Using Equation 4 from the <u>TPS65051 data sheet</u>, for an output voltage of 1.45 V, the external voltage divider values can be calculated as shown:

R1 = 470 k $\Omega$ , R2 = 330 k $\Omega$ , C<sub>FF</sub> = 47 pF

QVDD is part of the first sequencing group. Therefore, the EN DCDC1 pin can be directly connected to VIN.

# $NV_{DD_{GPIO1}}, NV_{DD_{GPIO2}}, NV_{DD_{SDRAM}}$ (3.3 V)

This rail is supplied by DCDC2.

The output voltage of DCDC2 is also adjustable using an external voltage divider. Using Equation 5 from the <u>TPS65051 data sheet</u>, for an output voltage of 3.3 V, the external voltage divider values can be calculated in the following way:

$R3 = 680 \text{ k}\Omega, R4 = 150 \text{ k}\Omega, C_{FF} = 47 \text{ pF}$

The rails NVDD\_GPIO1, NVDD\_GPIO2, and NVDD\_SDRAM are part of the first sequencing group. EN DCDC2 can thus be directly connected to VIN.

# $NV_{DD_{MDDR}}, NV_{DD_{DDR2}}$ (1.8 V)

These rails are supplied by LDO1.

The output voltage of LDO1 is adjustable using an external voltage divider. Using Equation 9 from the <u>TPS65051 product data sheet</u>, for an output voltage of 1.8 V, the external voltage divider values can be calculated in this way:

R5 = 240 kΩ, R6 = 300 kΩ

The rails NVDD\_MDDR and NVDD\_DDR2 are part of the first sequencing group. EN LDO1 can be directly connected to VIN.

# $V_{\text{DD}\_\text{USBPHY1}}, V_{\text{DD}\_\text{USBPHY2}}, V_{\text{DD}\_\text{OSC24M}}, V_{\text{DD}\_\text{TSC}}, V_{\text{REF}} \text{ (3.3 V)}$

These rails are supplied by LDO2.

The output voltage of LDO2 is adjustable using an external voltage divider. Using Equation 9 from the <u>TPS65051 product data sheet</u>, for an output voltage of 3.3 V, the external voltage divider values can be calculated as shown:

R17 = 330 kΩ, R18 = 143 kΩ

The rails  $V_{DD_USBPHY1}$ ,  $V_{DD_USBPHY2}$ ,  $V_{DD_OSC24M}$ ,  $V_{DD_TSC}$ , and  $V_{REF}$  are part of the second sequencing group. EN LDO2 is connected to the output of DCDC2. In addition there is an RC filter connected on EN LDO2 to make sure the second sequencing groups starts after DCDC2.

# Generation of FUSEV<sub>DD</sub> (3.6 V)

These rails are supplied by LDO3.

The output voltage of LDO3 is adjustable using an external voltage divider. Using Equation 9 from the <u>TPS65051 data sheet</u>, for an output voltage of 3.6 V, the external voltage divider values can be calculated as following

R9 = 470 kΩ, R10 = 180 kΩ

The rail  $FUSEV_{DD}$  is part of the second sequencing group. EN LDO3 is connected to the output of DCDC2. In addition, there is an RC filter connected on EN LDO3 to ensure that the second sequencing groups starts after DCDC2.

# Generation of $V_{DD_PLL}$ (1.6 V at 200 mA)

These rails are supplied by LDO4.

The output voltage of LDO4 is adjustable using an external voltage divider. Using Equation 9 from the <u>TPS65051 product data sheet</u>, for an output voltage of 1.6 V, the external voltage divider values can be calculated as shown:

$R11 = 220 \text{ k}\Omega, R12 = 360 \text{ k}\Omega$

The rail  $FUSEV_{DD}$  is part of the second sequencing group. EN LDO4 is connected to the output of DCDC2. In addition, there is an RC filter connected on EN LDO4 to make sure the second sequencing groups starts after DCDC2.

### POR

The reset signal for the processor is generated using the integrated SVS onboard the TPS65051 PMU. The SVS monitors the last rail coming up in the power sequence. The last rail is OUT\_LDO4 (that is, VDD\_PLL). In the design, this rail is monitored; once it reaches 0.3 V, the RESET signal is generated.

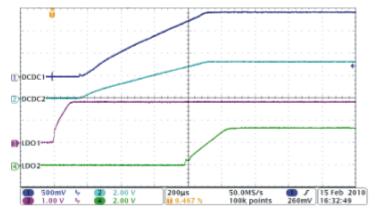

Measurement Results

### 5 Measurement Results

This section presents some of the measured performance results for this configuration.

Figure 4. Power-Up Sequence: DCDC1, DCDC2, LDO1, LDO2

Figure 5. Power-Up Sequence: LDO1, LDO2, LDO3, LDO4

# 6 References

- 1. i.MX25 Power Management Using the MC34704. (2009). Application note AN3820. Freescale Semiconductor, Inc.

- 2. <u>TPS65051</u> product data sheet. Texas Instruments (<u>SLVS710A</u>). Revised August, 2007.

# **Revision History**

| Cł | Changes from Original (February, 2010) to A Revision Page                           |   |  |  |  |

|----|-------------------------------------------------------------------------------------|---|--|--|--|

| •  | Updated Figure 3                                                                    | 6 |  |  |  |

| •  | Replaced Bill of Materials                                                          | 7 |  |  |  |

| •  | Corrected resistor names indicated is calculation of external voltage divider value | 8 |  |  |  |

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications                  |                                   |

|-----------------------------|------------------------|-------------------------------|-----------------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio                         | www.ti.com/audio                  |

| Data Converters             | dataconverter.ti.com   | Automotive                    | www.ti.com/automotive             |

| DLP® Products               | www.dlp.com            | Communications and<br>Telecom | www.ti.com/communications         |

| DSP                         | dsp.ti.com             | Computers and<br>Peripherals  | www.ti.com/computers              |

| Clocks and Timers           | www.ti.com/clocks      | Consumer Electronics          | www.ti.com/consumer-apps          |

| Interface                   | interface.ti.com       | Energy                        | www.ti.com/energy                 |

| Logic                       | logic.ti.com           | Industrial                    | www.ti.com/industrial             |

| Power Mgmt                  | power.ti.com           | Medical                       | www.ti.com/medical                |

| Microcontrollers            | microcontroller.ti.com | Security                      | www.ti.com/security               |

| RFID                        | www.ti-rfid.com        | Space, Avionics & Defense     | www.ti.com/space-avionics-defense |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Video and Imaging             | www.ti.com/video                  |

|                             |                        | Wireless                      | www.ti.com/wireless-apps          |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2010, Texas Instruments Incorporated