# User's Guide TPS62745 Buck Converter Evaluation Module User's Guide

# **TEXAS INSTRUMENTS**

#### ABSTRACT

This user's guide describes the characteristics, operation, and use of the Texas Instruments TPS62745 evaluation module (EVM). This EVM is designed to help the user easily evaluate and test the operation and functionality of the TPS62745. The EVM converts a 2.2-V to 5.5-V input voltage to a regulated output voltage that is set between 1.8 V and 3.3 V at up to 300 mA. The TPS62745 also includes a load switch and power good output, while having an ultra-low quiescent current of 400 nA. This user's guide includes setup instructions for the hardware, a printed-circuit board (PCB) layout for the EVM, a schematic diagram, a bill of materials (BOM), and test results for the EVM.

### **Table of Contents**

| 1.1 Background.       2         2 Setup.       3         2.1 Input/Output Connector Descriptions.       3         2.2 Operation.       3         3 Common Efficiency Measurement Errors with Ultra-Low Iq Devices.       3         3.1 Efficiency Measurement Setup.       3         3.2 Pullup and Pulldown Resistors.       4         4 Board Layout.       5         5 Schematic and Bill of Materials.       8         5.1 Schematic.       9         5.2 Bill of Materials.       10         6 Revision History.       10 | 1 Introduction                                                   | 2  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----|

| 2 Setup.       3         2.1 Input/Output Connector Descriptions.       3         2.2 Operation.       3         3 Common Efficiency Measurement Errors with Ultra-Low Iq Devices.       3         3.1 Efficiency Measurement Setup.       3         3.2 Pullup and Pulldown Resistors.       4         4 Board Layout.       5         5 Schematic and Bill of Materials.       8         5.1 Schematic.       9         5.2 Bill of Materials.       10                                                                      | 1.1 Background                                                   | 2  |

| 2.1 Input/Output Connector Descriptions.       3         2.2 Operation.       3         3 Common Efficiency Measurement Errors with Ultra-Low Iq Devices.       3         3.1 Efficiency Measurement Setup.       4         3.2 Pullup and Pulldown Resistors.       4         4 Board Layout.       5         5 Schematic and Bill of Materials.       8         5.1 Schematic.       9         5.2 Bill of Materials.       10                                                                                               |                                                                  |    |

| 2.2 Operation       3         3 Common Efficiency Measurement Errors with Ultra-Low Iq Devices       3         3.1 Efficiency Measurement Setup       4         3.2 Pullup and Pulldown Resistors       4         4 Board Layout       5         5 Schematic and Bill of Materials       8         5.1 Schematic       9         5.2 Bill of Materials       10                                                                                                                                                                |                                                                  |    |

| 3.1 Efficiency Measurement Setup.       .4         3.2 Pullup and Pulldown Resistors.       .4         4 Board Layout.       .5         5 Schematic and Bill of Materials.       .8         5.1 Schematic.       .9         5.2 Bill of Materials.       .10                                                                                                                                                                                                                                                                   |                                                                  |    |

| 3.2 Pullup and Pulldown Resistors       4         4 Board Layout       5         5 Schematic and Bill of Materials       8         5.1 Schematic.       9         5.2 Bill of Materials       10                                                                                                                                                                                                                                                                                                                               | 3 Common Efficiency Measurement Errors with Ultra-Low Ig Devices | 3  |

| 4 Board Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.1 Efficiency Measurement Setup                                 | 4  |

| 4 Board Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.2 Pullup and Pulldown Resistors                                | 4  |

| 5.1 Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4 Board Layout                                                   | 5  |

| 5.2 Bill of Materials10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                  |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.1 Schematic                                                    | 9  |

| 6 Revision History 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.2 Bill of Materials                                            | 10 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6 Revision History                                               | 10 |

## **List of Figures**

| Figure 4-1. Assembly Layer            | 5 |

|---------------------------------------|---|

| Figure 4-2. Top Layer                 | 6 |

| Figure 4-3. Bottom Layer              | 7 |

|                                       |   |

| Figure 5-1. TPS62745EVM-622 Schematic | 9 |

# List of Tables

| Table 2-1. | Output Voltage Settings            | 3 |

|------------|------------------------------------|---|

| Table 5-1. | TPS62745EVM-622 Bill of Materials1 | 0 |

#### Trademarks

All trademarks are the property of their respective owners.

# **1** Introduction

The TPS62745 is a 300-mA, synchronous, step-down converter in a 2 x 3-mm, 10-pin SON package. The output voltage is fixed inside the device by the connection of the four VSELx pins.

#### 1.1 Background

The TPS62745EVM-622 uses the TPS62745 device. The EVM operates with full-rated performance with an input voltage between 3.3 V and 10 V.

# 2 Setup

This section describes how to properly use the TPS62745EVM-622.

#### 2.1 Input/Output Connector Descriptions

| J1 – VIN                | Positive input connection from the input supply for the EVM (3.3 V to 10 V)                                                                                                                                                     |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J2 – S+/S-              | Input voltage sense connections. Measure the input voltage at this point.                                                                                                                                                       |

| J3 – GND                | Return connection from the input supply for the EVM.                                                                                                                                                                            |

| J4 – VOUT               | Output voltage connection.                                                                                                                                                                                                      |

| J5 – S+/S-              | Output voltage sense connections. Measure the output voltage at this point.                                                                                                                                                     |

| J6 – GND                | Output return connection.                                                                                                                                                                                                       |

| J7 – PG/GND             | The PG output appears on pin 1 of this header with a convenient ground on pin 2.                                                                                                                                                |

| J8 – VIN_SW             | VIN switch output connection.                                                                                                                                                                                                   |

| J9 – SW/GND             | Switch Node sense connection.                                                                                                                                                                                                   |

| JP1 – EN                | EN pin input jumper. Place the supplied jumper across ON and EN to turn on the IC. Place the jumper across OFF and EN to turn off the IC.                                                                                       |

| JP2 – EN_VIN_SW         | Enable VIN switch jumper. Place the supplied jumper across VIN_SW_ON and EN_VIN_SW to activate (close) the internal VIN switch. Place the jumper across VIN_SW_OFF and EN_VIN_SW to de-activate (open) the internal VIN switch. |

| JP3 through JP6 – VSELx | These four inputs set the output voltage. By connecting each pin high or low, the output voltage is programmed per Table 2-1. Do not leave any jumper open for proper operation.                                                |

Table 2-1 provides the output voltage settings for the TPS62745EVM-622. A 0 refers to logic low, while 1 refers to logic high.

| VOUT | VSEL 4 | VSEL 3 | VSEL 2 | VSEL 1 |  |

|------|--------|--------|--------|--------|--|

| 1.8  | 0      | 0      | 0      | 0      |  |

| 1.9  | 0      | 0      | 0      | 1      |  |

| 2.0  | 0      | 0      | 1      | 0      |  |

| 2.1  | 0      | 0      | 1      | 1      |  |

| 2.2  | 0      | 1      | 0      | 0      |  |

| 2.3  | 0      | 1      | 0      | 1      |  |

| 2.4  | 0      | 1      | 1      | 0      |  |

| 2.5  | 0      | 1      | 1      | 1      |  |

| 2.6  | 1      | 0      | 0      | 0      |  |

| 2.7  | 1      | 0      | 0      | 1      |  |

| 2.8  | 1      | 0      | 1      | 0      |  |

| 2.9  | 1      | 0      | 1      | 1      |  |

| 3.0  | 1      | 1      | 0      | 0      |  |

| 3.1  | 1      | 1      | 0      | 1      |  |

| 3.2  | 1      | 1      | 1      | 0      |  |

| 3.3  | 1      | 1      | 1      | 1      |  |

#### Table 2-1. Output Voltage Settings

## 2.2 Operation

To operate the EVM, set jumpers JP1 through JP6 to the desired positions per Section 2.1. Connect the input supply to J1 and J3 and connect the load to J4 and J6.

## **3 Common Efficiency Measurement Errors with Ultra-Low Iq Devices**

Efficiency is a common measurement for a power supply. With an ultra-low quiescent current device, such as the TPS62745, measurement errors can have a large impact on the measured efficiency, especially at very low load currents (< 100  $\mu$ A).

### 3.1 Efficiency Measurement Setup

To accurately measure the efficiency of the TPS62745EVM-622, use the setup described in SLVA236 Figure 6. The 'Additional Input Capacitor' referred to in that application note is not needed as C5 is already included on the TPS62745EVM-622. Any additional input capacitance is not recommended as it incurs increased leakage on the input which lowers the measured efficiency.

When measuring efficiency through the setup in SLVA236, special care must be taken to remove the current consumed by the measurement instruments from the efficiency calculations. Such measurement instruments typically include the input voltage and output voltage multimeters as well as the input power supply's remote sense lines (if it has this capability). The current into these points affects the measured efficiency at very light loads. Two possible methods to overcome this are: measuring the current into these points (measure the current into the multimeters and/or remote sense lines) and then subtracting this current from the efficiency calculation or simply removing these instruments from the test setup. At very light load currents, it is typically best to remove the remote sense lines of the input power supply and then measure the current into the input and output voltage multimeters to get the most accurate efficiency measurement.

#### 3.2 Pullup and Pulldown Resistors

In addition to the input capacitor and remote sense lines noted in Section 3.1, any pullup or pulldown resistors can draw significant current and affect the measured efficiency. For example, if the VSEL2 pin were pulled up to the input voltage with a 1-M $\Omega$  resistor and the pin were tied low through JP4, this would draw an extra 3.6  $\mu$ A from the input source at a 3.6-V input voltage. This would greatly affect the efficiency at very light loads. For this reason, no pullup or pulldown resistors have been used on the TPS62745EVM-622. The final application circuit should ensure that all digital inputs to the TPS62745 are terminated either high or low and not left floating, per the device data sheet.

# 4 Board Layout

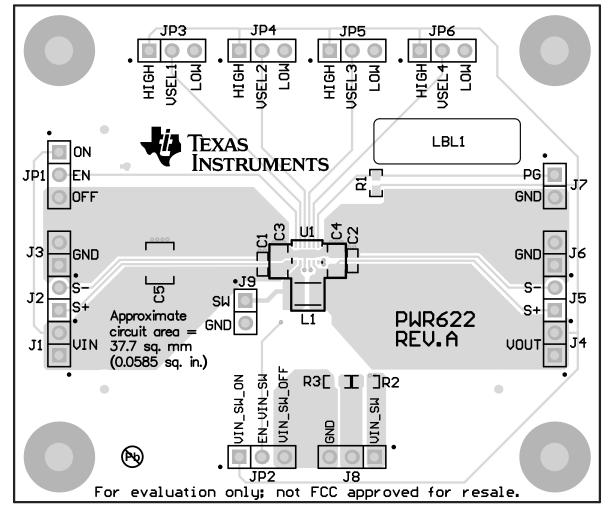

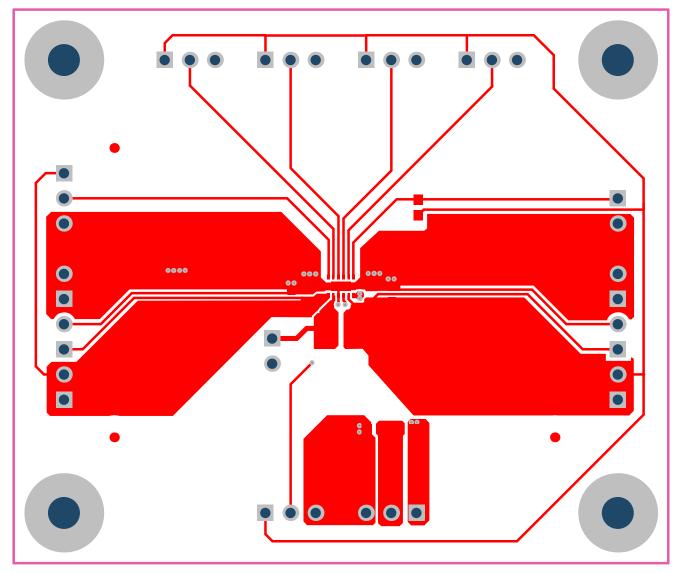

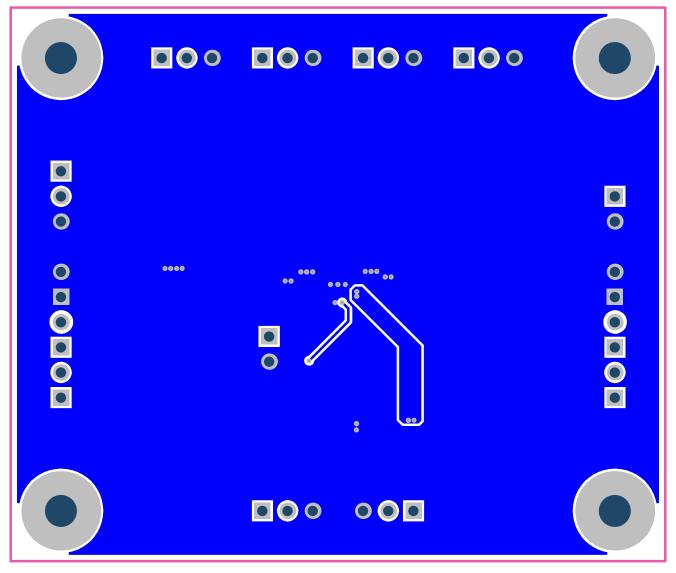

This section provides the TPS62745EVM-622 board layout and illustrations. The gerbers are available on the EVM product page: TPS62745EVM-622.

Figure 4-1. Assembly Layer

Figure 4-2. Top Layer

Figure 4-3. Bottom Layer

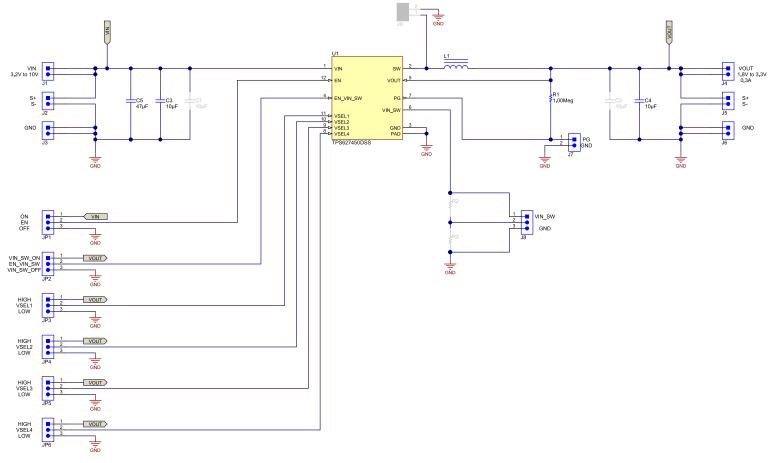

## **5** Schematic and Bill of Materials

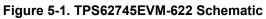

This section provides the TPS62745EVM-622 schematic and bill of materials.

## 5.1 Schematic

Figure 5-1 illustrates the TPS62745EVM-622 schematic.

### 5.2 Bill of Materials

Table 5-1 lists the TPS62745EVM-622 bill of materials.

| Table 5-1. TPS62745EVM-622 Bill of Materials |  |

|----------------------------------------------|--|

|----------------------------------------------|--|

| Count | RefDes | Value         | Description                                      | Size                | Part Number        | MFR         |

|-------|--------|---------------|--------------------------------------------------|---------------------|--------------------|-------------|

| 3     | C1, C2 | not Populated | Capacitor, Ceramic                               | 0603                |                    |             |

| 2     | C3, C4 | 10uF          | Capacitor, Ceramic, X5R, 10V, 10%                | 0805                | LMK212BJ106KG-T    | Taiyo Yuden |

| 1     | C5     | 47uF          | Capacitor, Ceramic, X5R, 16V, 20%                | 1210                | GRM32ER61C476ME15L | Murata      |

| 1     | L1     | 4.7uH         | Inductor, Multilayer, 1.7A, 165- $m\Omega$       | 1008                | DFE252012P-4R7M    | Toko        |

| 1     | R1     | 1.00M         | Resistor, Chip, 1/16W, 1%                        | 0603                | RC0603FR-071ML     | Yageo       |

| 1     | U1     | TPS62745      | IC, 400 nA I <sub>Q</sub> Step Down<br>Converter | 2 mm x 3 mm<br>WSON | TPS62745DSS        | ТІ          |

#### **6 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Revision \* (June 2015) to Revision A (May 2021)

Page

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated