# **High-Performance Analog Products**

# Analog Applications Journal

Second Quarter, 2007

### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Managemen  | t power.ti.com         | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

| Mailing Address: | Texas Instruments      |                    |                           |

| Ü                | Post Office Box 655303 |                    |                           |

|                  | Dallas, Texas 75265    |                    |                           |

|                  | ,                      |                    |                           |

# **Contents**

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 4 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Data Acquisition  Conversion latency in delta-sigma converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 5 |

| Power Management Enhanced-safety, linear Li-ion battery charger with thermal regulation and input overvoltage protection.  Using unregulated power sources can easily drive linear Li-ion battery chargers beyond safe thermal operating limits. The bq2406x chargers offer thermal regulation and input overvoltage protection that alleviate thermal concerns while maximizing the charge rate and minimizing the charging time.                                                                                                      | . 8 |

| Current balancing in four-pair, high-power PoE applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11  |

| Interface (Data Transmission) Enabling high-speed USB OTG functionality on TI DSPs  USB On-The-Go (OTG) enables connectivity to various USB devices without a PC host. This article provides insight to getting the TUSB60xx OTG-capable devices to gluelessly provide a USB interface to TI processors that supports the VLYNQ interface—such as the DaVinci™ family, the DM320, and the OMAP™ family.                                                                                                                                 | 18  |

| Amplifiers: Op Amps New zero-drift amplifier has an $I_0$ of 17 $\mu$ A                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 22  |

| General Interest Spreadsheet modeling tool helps analyze power- and ground-plane voltage drops to keep core voltages within tolerance  PCB power- and ground-plane voltage drops can become a real problem when working with very low core voltages. This article shows how to use your spreadsheet software to model a PCB layout to predict voltage drops for various copper thicknesses and temperatures. Using the spreadsheet surface-charting function, a 3D map of the voltage drops can be generated for quick visual analysis. | 29  |

| Index of Articles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 41  |

| TI Worldwide Technical Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 45  |

To view past issues of the Analog Applications Journal, visit the Web site www.ti.com/aaj

# Introduction

Analog Applications Journal is a collection of analog application articles designed to give readers a basic understanding of TI products and to provide simple but practical examples for typical applications. Written not only for design engineers but also for engineering managers, technicians, system designers and marketing and sales personnel, the book emphasizes general application concepts over lengthy mathematical analyses.

These applications are not intended as "how-to" instructions for specific circuits but as examples of how devices could be used to solve specific design requirements. Readers will find tutorial information as well as practical engineering solutions on components from the following categories:

- Data Acquisition

- Power Management

- Interface (Data Transmission)

- Amplifiers: Op Amps

- General Interest

Where applicable, readers will also find software routines and program structures. Finally, *Analog Applications Journal* includes helpful hints and rules of thumb to guide readers in preparing for their design.

**High-Performance Analog Products**

# **Conversion latency in delta-sigma converters**

# By Bonnie C. Baker (Email: bonnie@ti.com)

Senior Applications Engineer

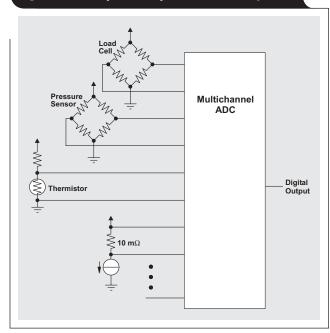

Small-signal sensors often generate slow-moving dc signals. For these types of sensors, the delta-sigma ( $\Delta\Sigma$ ) analog-todigital converter (ADC) eliminates most of the analog input circuitry by providing a complete high-resolution, low-noise solution. Some systems have multiple sensors generating low-frequency signals. This situation may require a highresolution, low-noise ADC with a multiplexer at its input. An example of a multiplexed sensor system is an automotive diagnostic application where numerous small-signal sensors monitor temperature, tire pressure, air-bag readiness, etc. (see Figure 1). Examples of other sensor-input multiplexed systems are found in industrial-control, medical, avionics, and process-control applications. Even though the sensors at the input of the multiplexer in these systems present low-frequency (nearly dc) signals, switching from channel to channel creates the need for an ADC that is capable of a high-speed response.

There are two common units of measure that describe the latency of an ADC: cycles and seconds. Cycle latency is the number of complete data cycles between the conversion initiation and the availability of the corresponding output data. Latency time, measured in seconds, tells the user how fast fully settled conversions can be performed.

In the system in Figure 1, the multiple-channel ADC

must have high resolution, low noise, zero-cycle latency, and low latency time. (Zero latency or 0-cycle latency is sometimes called no latency.)

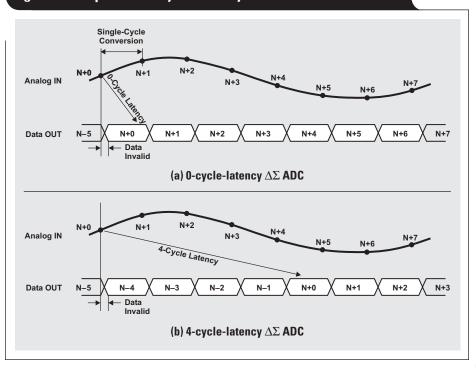

# **ADC** cycle latency

For ADCs, cycle latency is the number of complete data cycles between the initiation of the inputsignal conversion and the availability of the corresponding output data (see Figure 2). The unit of measure for this definition of latency is N-cycle latency, where N is a whole number. Figure 2 shows the timing diagrams for a 0-cycle-latency (or zero-latency) ADC and a 4-cyclelatency ADC. In Figure 2(a), with 0-cycle latency, the sampling period of N+0 is initiated. The output data of N+0 is acquired before the sampling period of N+1 is initiated. In Figure 2(b), with 4-cycle latency, the sampling period of N+0 is

Figure 1. Example multiplexed sensor system

Figure 2. Comparison of cycle-latency behavior of two  $\Delta\Sigma$  ADCs

initiated. The output data of N+0 is presented after the completion of four conversion cycles.

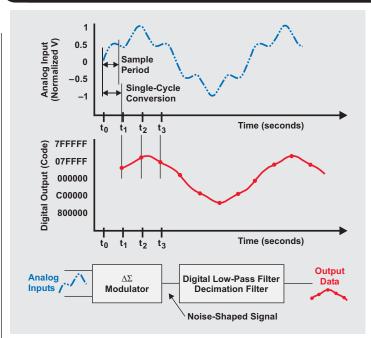

Figure 3 shows zero-latency ADC behavior graphically. In Figure 3, the input signal is first acquired at  $t_0$ . The  $\Delta\Sigma$  converter continues to acquire input samples through the sampling period and continually modulates the signal into a noise-shaped representation. The digital low-pass/decimation filter accumulates the noise-shaped signal and generates the output code at the end of the  $t_0$  period. A  $\Delta\Sigma$  converter has zero latency if data is available before a new sampling period is initiated. The output code represents the oversampled, filtered-input signal. At  $t_1$  the converter initiates the next sampling period.

The successive approximation register (SAR) ADCs are capable of zero latency as are many  $\Delta\Sigma$  converters. The better choice for the application shown in Figure 1 is a high-resolution, zero-latency  $\Delta\Sigma$  ADC. Some data sheets for  $\Delta\Sigma$  ADCs claim single-cycle conversions. This is another way of saying that a converter has zero latency.

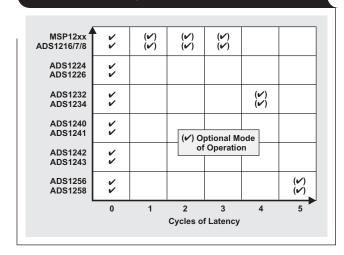

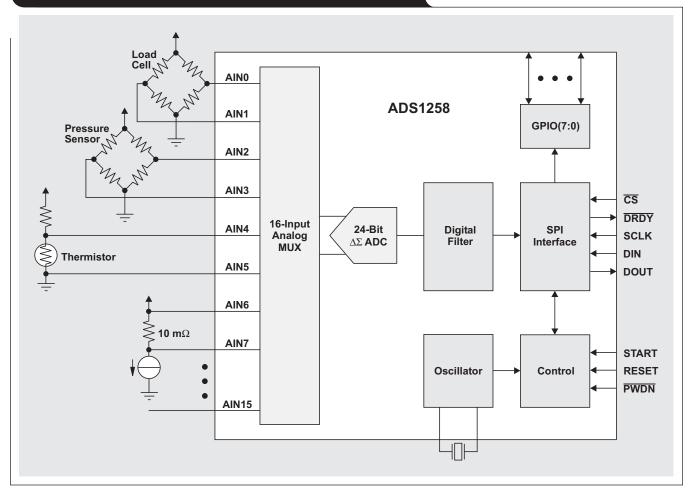

Texas Instruments (TI) offers numerous multiplexed, zero-latency  $\Delta\Sigma$  ADCs that provide low-noise, high-resolution solutions (see Figure 4). These  $\Delta\Sigma$  converters are capable of masking the filter action and providing a fully settled signal before the end of one cycle. As an example, TI's 16-channel, 24-bit ADS1258 has an internal, fifth-order, sinc digital filter followed by a programmable, first-order averaging filter. When the converter is configured in its auto-scan mode, the cycle latency is zero. In the auto-scan mode, the ADS1258 scans through the selected channels automatically, with break-before-make switching.

# **ADC** latency time

Latency time is typically viewed as the time required for an ideal step input to converge, within an error margin, to a final digital output value. This error band can be expressed as a predefined percentage of the total output-voltage step. The latency time of a conversion is the time between the beginning of the signal acquisition and the time when data is available to download from the converter. In contrast to the cycle-latency specification, the latency time (or settling time) is never equal to zero.

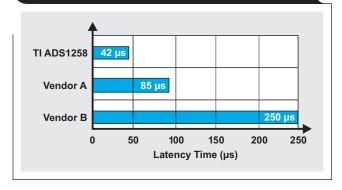

Figure 5 compares the latency-time performance of various multiplexed  $\Delta\Sigma$  ADCs. The latency time of a zero-latency  $\Delta\Sigma$  ADC varies from device to device, depending on the system clock and the order of the converter's digital filter. A requirement for larger applications is that the multiplexed ADC must quickly cycle through the channels. The latency time for these types of applications can be critical.

Figure 3. Typical input and output of zero-latency  $\Delta\Sigma$  ADC

Figure 4. Tl's multiplexed zero-latency  $\Delta\Sigma$  ADCs

Figure 5. Latency-time comparison of  $\Delta\Sigma$  ADCs

When the ADS1258 (Figure 6) is configured in its autoscan mode (zero latency), the output data is fully settled at the end of each conversion. The minimum latency time in the ADS1258's auto-scan mode is  $42~\mu s$ .

It is possible to reduce the throughput time of a zero-latency  $\Delta\Sigma$  ADC if the intermediate or masked digital filter results are available. In this mode, the digital output results are not necessarily fully settled. For these devices the throughput time is always less than the latency time. Reduction of throughput time best suits sensors that produce small voltage changes at a slow rate (such as temperature sensors, pressure sensors, or load cells). With these types of sensors it might be advantageous to acquire several conversions and perform post-processing on the data.

When the ADS1258 is configured in its fixed-channel mode, the intermediate results from the fifth-order digital filter are available to the user. In the ADS1258 fixed-channel mode, the converter is no longer automatically cycling from channel to channel, and the output data may

or may not be fully settled. The minimum throughput time of the ADS1258 in fixed-channel mode is 8  $\mu$ s (½ of the fully settled latency time).

### **Conclusion**

The economy and efficiency of using multiplexed  $\Delta\Sigma$  ADCs for applications with multiple sensors must be weighed against possible problems caused by ADC conversion latency and any latency introduced by external processing. The TI ADS1258 offers 16-channel, 24-bit conversions with low noise and zero latency. The device's single-cycle, low-latency-time capability provides fully settled data at the end of each conversion cycle. In auto-scan mode, the ADS1258 can complete a conversion for all 16 channels in under 700  $\mu s$ . Cycle latency and the total conversion time must be evaluated for each ADC considered to be sure the device will perform as intended.

# **Related Web sites**

dataconverter.ti.com www.ti.com/sc/device/ADS1258

Figure 6. The ADS1258, a 16-channel, zero-latency, 24-bit  $\Delta\Sigma$  ADC

# Enhanced-safety, linear Li-ion battery charger with thermal regulation and input overvoltage protection

# By Jinrong Qian

# Applications Manager, Battery Management Applications

The lithium-ion (Li-ion) battery is widely adopted in portable devices because of its high energy density on both a gravimetric and volumetric basis. Due to their simplicity, low cost, and small size, highly integrated linear battery chargers are widely used to charge single-cell Li-ion batteries. However, when unregulated adapters are used to power portable systems, it can be a challenge to remove or minimize the heat generated from the linear chargers and to maintain their operation within a safe thermal range. This article describes a newly developed battery charger with thermal regulation. This charger has input overvoltage protection (OVP), which alleviates thermal concerns while maximizing the charge rate and minimizing the charging time, allowing use of an unregulated adapter.

# **Battery-charging requirements**

The charge profile widely used for charging Li-ion batteries consists of three charging phases: precharge; fast-charge constant current (CC); and constant voltage (CV). In the precharge phase, the battery is charged at a low rate when the cell voltage is below 3.0 V. Typically, when the cell voltage reaches 3.0 V, the charger enters the CC phase. The faster-charge CC is usually limited to stay below the cell's 1C rating. The cell cycle life decreases with charge rates above 1C because metallic lithium deposited on the

node easily reacts with the electrolyte and is permanently lost. Finally, the charger enters the CV phase, where it maintains the peak cell voltage and then terminates charging when the charge current drops to a predefined level.

The cell capacity is a function of the cell voltage—the higher the voltage, the higher the capacity. However, higher cell voltage results in shorter cycle life. For example, charging a cell at 4.3 V can provide 10% more capacity, but cell cycle life may be 50% shorter. On the other hand, if the cell is undercharged at just 40 mV under the optimum voltage, it can have about 8% lower capacity. Therefore, a very accurate battery charge voltage is extremely important.

# Thermal-regulated battery charger with input OVP

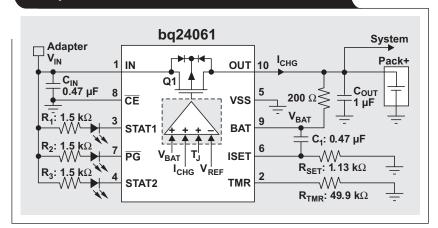

Figure 1 shows a low-cost, stand-alone linear battery charger circuit with thermal regulation and input OVP. The charger simply drops the adapter's DC voltage down to the battery voltage. The power dissipation in the linear charger is given by

$$P_{CHGR} = (V_{IN} - V_{BAT}) \times I_{CHG}.$$

There is a large difference between the input and battery voltages when the charger transitions from precharge to fast-charge mode, where the power dissipation reaches the maximum. For example, if a 5-V adapter is used to

Figure 1. Application circuit with thermal regulation and input OVP

charge a 1200-mAh Li-ion battery, it has a maximum power dissipation of 1.8 W with a 1-A charge current and a 3.2-V battery voltage. This power dissipation results in an 85°C temperature rise for a  $3\times3$ -mm QFN package with 47°C/W thermal impedance. The junction temperature exceeds the maximum allowed operating temperature of 125°C at 45°C ambient temperature. It is hard to maintain the junction temperature within a safe thermal range at the beginning of the charging. As the battery voltage rises during the charging, the power dissipation drops. After charging enters the CV mode, the power dissipation drops further as the charge current starts to taper down.

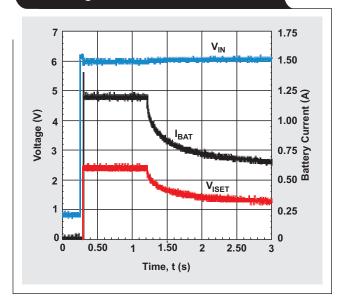

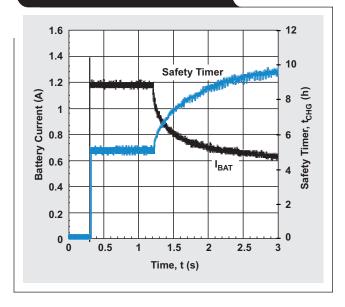

How do we improve the design to keep the charger operating in a safe thermal range? The more advanced battery chargers such as bq2406x and bq2403x have introduced a thermal regulation loop to prevent overheating of the charger. When the internal chip temperature reaches a predefined temperature threshold—for example, 110°C—any further increase of the IC temperature results in reduction of the charge current. This limits the power dissipation and provides thermal protection to the charger. The maximum power dissipation causing the IC junction temperature to reach thermal regulation depends upon the PCB layout, the number of thermal vias, and the ambient temperature. Figure 2 shows that after 1.2 seconds the thermal loop reduces the effective charging current from 1.2 A to 600 mA within 2 seconds.

Thermal regulation usually happens at the early stage of the fast charge, but if it is active during the CV mode, the charging current could prematurely reach the charge termination threshold. To prevent this false charge termination, the battery charge-termination function is disabled whenever the thermal regulation loop is active. In addition, the effective charge current is reduced, which increases the battery charging time and which, if the charge safety timer had a fixed setting, could terminate charging early. The bq2406x employs a dynamic safety-timer control circuit that effectively extends the safety time during thermal regulation and minimizes the chance of a safety-timer fault. Figure 3 shows that the safety-timer response is inversely proportional to the effective charge current in thermal-regulation mode.

When the battery-charging function is enabled, the internal circuit generates a current proportional to the real charging current set by the ISET pin. The voltage generated across resistor RSET reflects the charge current. This voltage can be monitored by the host for charge-current information.

There are several types of adapters used to charge Li-ion batteries. Less expensive adapters may not have well regulated output and have higher output voltages under no load than at the normal load. In addition, during the battery hot plug-in, the input voltage to the charger could reach as high as two times that of the adapter voltage due to resonance between the cable inductance and the input

Figure 2. Charge-current waveform under thermal regulation

Figure 3. Dynamic safety timer in thermal regulation

capacitor of the battery charger. To increase safety when the input voltage is above the predefined threshold, the input OVP implemented in bq2406x chargers does not allow charging.

The LDO mode (with the TMR pin open) disables the charge-termination circuit and the battery-detection routine and holds the safety-timer clock in reset. This mode is often used for operation without a battery or in production testing.

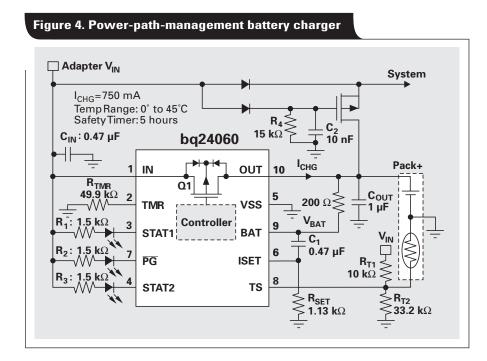

Many applications require powering the system while charging the battery simultaneously. When the system is directly connected to the battery-charge output as shown in Figure 1, interaction between the system and charger may result in a false charge termination caused by the safety timer. Figure 4 shows a typical application circuit that eliminates such issues. There are two independent power paths, one to charge the battery and one to power the system. When the AC adapter is not available, the battery discharge MOSFET is turned on after a time delay set by R4 and C2 so that the battery will provide power to the system.

# **Summary**

The linear battery charger with thermal regulation can significantly improve the thermal design and safety. With input OVP, it allows only authorized adapters to charge the battery, improving system safety.

# **Related Web sites**

power.ti.com www.ti.com/sc/device/bq24060 www.ti.com/sc/device/bq24061

# **Current balancing in four-pair, high-power** PoE applications

# By Steven R. Tom

Systems Engineer, Power Interface Products

### Introduction

Power-over-Ethernet (PoE) parameters are specified by IEEE 802.3-2005 clause 33, which defines both the allowable architectures and the maximum deliverable power for a PoE system. The present standard mandates a two-pair architecture allowing a maximum of 12.95 W at the end of the cable. As end equipment becomes more complex, it requires more power and architectures more flexible than the IEEE standard allows. This article describes a unique current-balancing technique that uses a four-pair architecture to deliver up to 50-W to the end equipment.

# Review of PoE two-pair/four-pair architectures

An end-to-end PoE solution typically comprises a power source, referred to as "power sourcing equipment" (PSE), and end equipment, referred to as the "powered device" (PD). The PSE may be standalone or embedded in a router or switch. Most Ethernet cable used today is Category 5E (CAT5E) cable composed of four unshielded twisted pairs of copper.

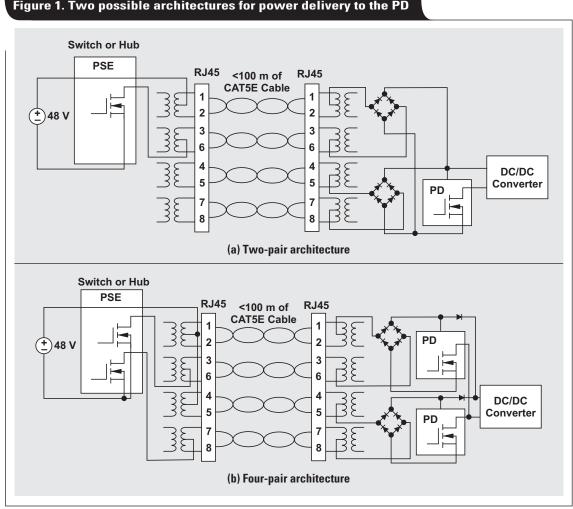

Figure 1 shows the possible architectures that can be used to deliver power over CAT5E cable. The architecture in Figure 1a delivers power to the PD from the PSE in a single loop over two pairs of the CAT5E cable. The IEEE

Figure 1. Two possible architectures for power delivery to the PD

standard specifies that power may be delivered in a single loop over either of the two pairs but not over all four pairs simultaneously. Using two current loops over all four pairs, the architecture in Figure 1b increases the available power delivered to the input of the PD. The main advantage of the four-pair architecture is the increased number of conductors which decreases power loss and increases total power to the end equipment. The main disadvantages are the added cost and the increased complexity needed to ensure that the current is balanced between the two current loops.

In the four-pair architecture, both current loops feed a single DC/DC converter. If the impedances of each loop were identical, current balancing would be unnecessary and each loop would provide half of the needed input current to the DC/DC converter. However, mismatches in the wires, connectors, and components will naturally cause one loop to carry more current than the other. To ensure

reliability, the series components in each current loop must be designed to handle the worst-case imbalance while maintaining data transmission. A larger imbalance implies an oversized (and thus more costly) design. Maximum power delivery can be obtained by balancing the current between the line pairs so that each path operates just below its current limit. The following design example and analysis show how the worst-case imbalance can be determined and minimized.

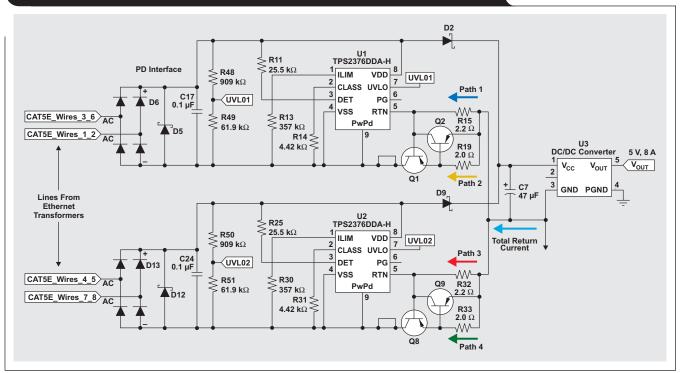

# Design example with current-booster circuit

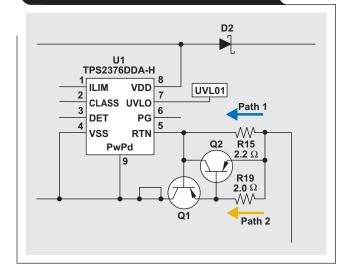

In a four-pair architecture, the detection and classification functions of the PD must be performed on each two-pair current loop, which necessitates the need for two PD controllers. In the design example that follows, two TPS2376-H controllers are used as the PD input source to the DC/DC power supply<sup>2</sup> (see Figure 2). The DC/DC power supply uses a UCC3809-2 in a single-switch flyback

Figure 2. Design example of four-pair architecture with current-booster circuit

topology to provide an isolated 5 V at 8 A to the load.

Table 1 shows the predetermined design specifications used for this design example. It is assumed that an available PSE will supply a regulated voltage between 51 and 57 V that is capable of sourcing up to 800 mA for each current loop consisting of two pairs of the CAT5E cable. A reasonable assumption for the loop impedance of each two-pair loop (maximum length of 100 m) is 12.5  $\Omega$ . The CAT5E cable will connect to the PD interface and input to the DC/DC converter that will provide an isolated 5 V at 8 A to the load. For simplicity and emphasis on the PD interface, the DC/DC power supply is shown in Figure 2 as a simple black box.

Assuming that the DC/DC converter is  $\sim 85\%$  efficient, approximately 47 W of input power is needed. Depending on the CAT5E cable length and the PSE voltage, an input current between 0.825 and 1.2 A is required to meet the input-power specification.

The current limit of the TPS2376-H is listed in Table 1 because it is imperative that the current in either of the two current loops not exceed this value during operation to avoid unwanted shutdown. Because the minimum current limit of the TPS2376-H is 625 mA, the current-booster circuitry in Figure 3 was introduced to gain the full potential of the allowable 800 mA of input current per two-pair loop. In reality, the current is not boosted—it is merely shunted around the TPS2376-H. Figure 3 shows how the current-booster circuit works for one of the current loops. As the return current into pin 5 (RTN) on the TPS2376-H increases, the voltage drop across R15 increases, lowering the voltage between base and emitter sufficiently to turn on transistor Q1. Current through R15 will turn on Q1 when  $V_{R15} > 0.7$  V. This allows Q1 to conduct and shunt a portion of the return current around the TPS2376-H. Q2 provides protection for Q1 during short-circuit and transient conditions by clamping the base of Q1 to its collector and forcing it off. Q2 will turn on when  $V_{R19} > 0.7$  V, shunting some of the Q1 base current and eventually turning it off if the current continues to increase. For a more detailed explanation of this circuit, please see Reference 3.

**Table 1. Design specifications**

|                                      | MIN   | TYP   | MAX   |

|--------------------------------------|-------|-------|-------|

| PSE Voltage (V)                      | 51    | _     | 57    |

| Impedance per Two Pairs ( $\Omega$ ) | _     | 12.5  | _     |

| Input Current per Two Pairs (A)      | _     | _     | 0.800 |

| V <sub>OUT</sub> (V)                 | 4.95  | 5     | 5.05  |

| I <sub>OUT</sub> (A)                 | _     | _     | 8.0   |

| DC/DC Output Power to Load (W)       | _     | _     | 40    |

| DC/DC Input Power (W)                | _     | _     | 47    |

| DC/DC Efficiency (%)                 | _     | 85    | _     |

| DC/DC Input Current (A)              | 0.825 | _     | 1.200 |

| Current Limit (A) (TPS2376-H)        | 0.625 | 0.765 | 0.900 |

Figure 3. Current-booster circuit for one current loop

# Modeling the four-pair architecture within PSPICE

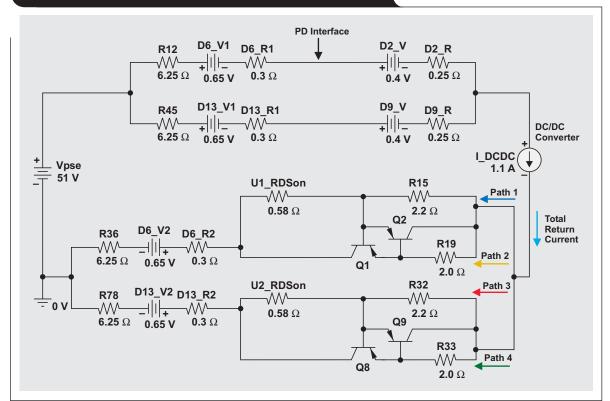

To ensure that the design will current share appropriately, it is necessary to model the four-pair architecture within a simulation tool such as PSPICE. The key elements that need to be modeled are the sources of impedance in series with each current loop; i.e., the diode bridge, the CAT5E cable resistance, and the series resistances of the TPS2376-H pass FETs and booster circuitry. Table 2 correlates the actual schematic in Figure 2 with the PSPICE simulation schematic in Figure 4.

The simulation models the PSE as an ideal DC voltage source, the DC/DC power supply as an ideal DC current source, and the CAT5E cable and PD interface as the four current paths. The color-coded paths in Figure 4 correspond to those shown in Figure 2. Modeling the PSE as an ideal voltage source and the DC/DC power supply as an ideal DC current source are reasonable assumptions that simplify the simulation significantly and allow the analysis to focus on the current balancing of the CAT5E and PD circuitry.

As stated earlier, in an ideal circuit the current would be equal in each current path because each path contains the same components. However, imbalances do arise because of variations in diode forward voltage drops, cable resistance, and pass FET on resistances. PSPICE allows for examination of the ideal case where matched components are used and the current in each current loop is balanced. The simulation is made by sweeping the current in the DC current source, I\_DCDC, and recording the current in

Table 2. Modeling of four-pair architecture

| ACTUAL SCHEMATIC                   | PSPICE SIMULATION                  |  |  |

|------------------------------------|------------------------------------|--|--|

| (Figure 2)                         | SCHEMATIC (Figure 4)               |  |  |

| U1                                 | U1_RDSon                           |  |  |

|                                    | (pass FET on resistance)           |  |  |

| U2                                 | U2_RDSon                           |  |  |

|                                    | (pass FET on resistance)           |  |  |

| D6                                 | D6_V1, D6_V2, D6_R1, D6_R2         |  |  |

| D13                                | D13_V1, D13_V2, D13_R1, D13_R2     |  |  |

| D2                                 | D2_V, D2_R                         |  |  |

| D9                                 | D9_V, D9_R                         |  |  |

| CAT5E cable resistance             | R12, R45, R36, R78                 |  |  |

| PSE input voltage                  | Vpse                               |  |  |

| DC/DC power supply                 | I_DCDC                             |  |  |

| Q1, Q2, Q8, Q9, R15, R19, R32, R33 | Q1, Q2, Q8, Q9, R15, R19, R32, R33 |  |  |

each of the two current loops and the power delivered to the DC current source. The power delivered to the DC current source represents the input power to the DC/DC converter. (If the efficiency of the DC/DC power supply is known, it can be multiplied by the input power to calculate the actual power to the load.) Within each current loop, it is important to make sure that the current through the pass FET of each TPS2376-H device is less than the 625-mA current-limit threshold and that the total current in either current loop does not exceed 800 mA.

A second variable that must be considered is the length of the CAT5E cable. The IEEE standard allows for a

Figure 4. Balanced PSPICE circuit for load-share simulation

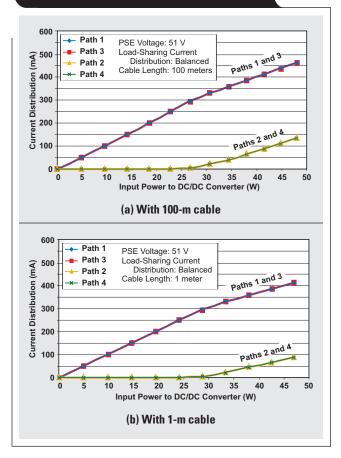

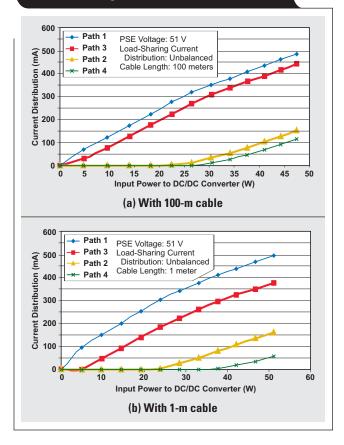

maximum of 100 m of Ethernet cable between the PD and PSE. Figure 5 shows the simulation results for the corner areas of 100 m and 1 m of cable length when the model cable resistances (R12, R45, R36, R78) are modified. All simulations are done at the minimum PSE voltage of 51 V because input current is highest at this condition.

The simulation results confirm that when matched, the current loops will load share identically as Path 1 overlaps Path 3 and Path 2 overlaps Path 4. As input power increases above 25 W, the current-booster circuitry begins turning on and a portion of the current in each current loop is shunted around the TPS2376-H. The largest current handled by either TPS2376-H device is ~465 mA when the input power to the DC/DC power supply is 48 W and 100 m of cable connects the PD to the PSE. The largest current in either of the two-pair current loops is 599 mA (465 mA + 134 mA). This simulation result is acceptable because the maximum TPS2376-H current is less than the 625-mA current limit and the maximum current in either of the two-pair current loops is less than 800 mA.

# Understanding sources of loop-impedance mismatch

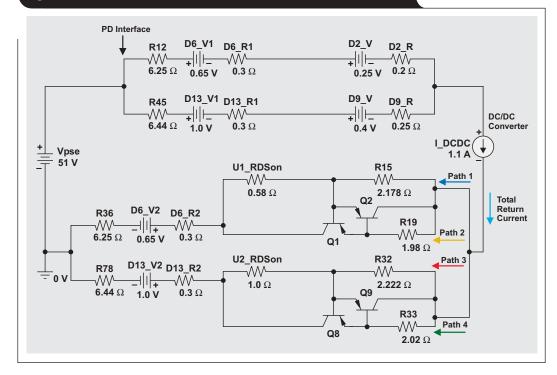

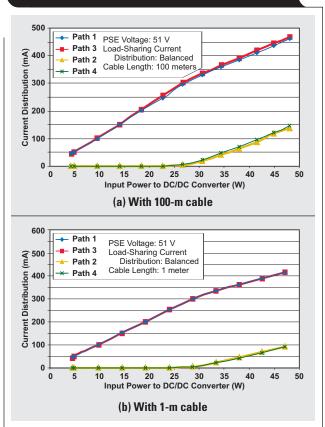

To ensure reliable performance, it is important to understand the sources of loop-impedance mismatch so that worst-case imbalances can be entered into the simulation and analyzed. The simulation circuit in Figure 6 takes into account maximum variations in diode forward voltage, 1% resistor tolerances, and maximum pass FET on-resistance tolerances. Also, the maximum cable length resistance tolerance of 3% was used in accordance with the IEEE standard.

Figure 5. PSPICE simulation of balanced current sharing

Figure 6. Unbalanced PSPICE circuit for load-share simulation

The values were adjusted so that all impedance mismatches were in one current loop, allowing for the largest imbalance. The four-pair architecture simulation previously discussed was run a second time to determine the extent of current imbalance in each current pair.

Figure 7 shows that the largest current through either of the TPS2376-H devices is 488 mA with a 100-m cable and 498 mA with a 1-m cable. The largest current available (in this example, Path 1 plus Path 2) is 640 mA with a 100-m cable and 660 mA with a 1-m cable. Because the worst-case current imbalance exceeds neither 625 mA through the TPS2376-H nor 800 mA in one current loop, the design remains within the original design specification.

Figure 7. PSPICE simulation of unbalanced current sharing

### **Board-level results**

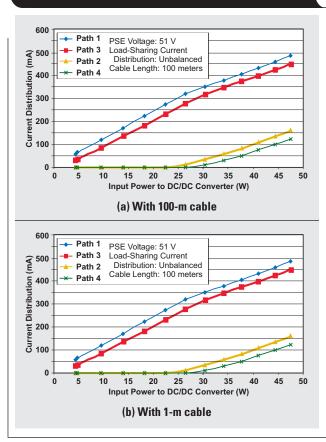

To verify that the simulations are accurate, an evaluation board was built and tested. Figure 8 shows the current in each of the current loops when measured in an ideal lab setting at  $25^{\circ}$ C ambient temperature. These board-level results demonstrate a current imbalance through each TPS2376-H of only 10 mA (2.1%) with a 100-m cable and 1 mA (0.2%) with a 1-m cable.

To emulate worst-case conditions, the evaluation board was retested with a diode and resistor in series with the return path of the R78 current loop (Paths 3 and 4). The forward voltage drop of the diode (0.7 V) and an additional 0.5- $\Omega$  resistance were added to compensate for worst-case

Figure 8. Board-level test results of balanced current sharing

diode forward voltage variations and system resistance tolerances. This permitted a reasonable board-level test to be conducted to measure actual current-loop imbalances.

Figure 9 shows that the largest current through either of the TPS2376-H devices is 488 mA with a 100-m cable and 484 mA with a 1-m cable. The largest current available (in this example, Path 1 plus Path 2) is 648 mA with a 100-m cable and 640 mA with a 1-m cable. Because the worst-case current imbalance exceeds neither 625 mA through the TPS2376-H nor 800 mA in one current loop, the design remains within the original design specification.

# **Conclusion**

Overall, both simulation and board-level results confirm that the current-booster circuit will meet the initial design requirements for current balancing by keeping the return current through each TPS2376-H under its minimum current limit and under the maximum current allowable in the CAT5E Ethernet cable. The addition of the current-booster circuit improves the current balancing between the two current loops so that the wire, connector, and component tolerances do not cause the design to fall out of the design specifications.

# References

For more information related to this article, you can download an Acrobat Reader file at www-s.ti.com/sc/techlit/litnumber and replace "litnumber" with the **TI Lit. #** for the materials listed below.

# Document Title TI Lit. #

- 1. IEEE 802.3 standard, http://standards.ieee.org/getieee802/802.3.html —

- 2. "IEEE 802.3af PoE High Power PD Controller,"

TPS2376-H Datasheet ......slvs646

- 3. Martin Patoka, "High-Power PoE PD Using TPS2375/77-1," Application Report ......slva225

# **Related Web sites**

power.ti.com www.ti.com/sc/device/TPS2376-H www.ti.com/sc/device/UCC3809-2

Figure 9. Board-level test results of unbalanced current sharing

# Enabling high-speed USB OTG functionality on TI DSPs

# By Dan Harmon

Product Line Marketing Manager, Digital Interface Products

High-speed USB On-The-Go (OTG) enables connectivity between portable consumer electronic devices over the industry's most popular peripheral interface, USB. Currently, USB devices require a PC host—laptop or desktop—to transfer data. High-speed USB OTG removes the need to find a bulky PC host to transfer pictures, music, and data to/from a cell phone, digital camera, MP3 player, memory stick, etc. Power is not much of an issue with today's PC host-centric USB, but is of increasing concern as portable devices take on more functionality and the demand for longer battery life increases. The problem of USB direct connection and power-management complexities is solved with the new USB 2.0 high-speed OTG controllers and power-management devices from Texas Instruments (TI). These devices allow developers to add full high-speed OTG capability to their platforms in small-form-factor, lowpower designs. TI's OTG devices are available with a muxed NOR-flash or VLYNQ host interface for easy connectivity to TI's OMAP processors and many other DSPs.

# What is USB OTG?

The terms USB 1.1, USB 2.0, USB OTG, WUSB, and OTG are all in common use today. In many cases they have created confusion among engineers and end users. The original USB 1.0 specification was released in January 1996. It defined two speeds for devices, low speed (LS) at 1.5 Mbps and full speed (FS) at 12 Mbps. The specification was revised in July 1998 and released as USB 1.1 with major clarifications/updates. In April 2000, the specification underwent a major revision and was released as USB 2.0, the current version that fully superseded USB 1.1. The beauty of USB 2.0 is that it maintains full backwards compatibility with USB 1.1 devices. However, it adds a much needed third speed node, high speed at 480 Mbps, while keeping support for both low speed and full speed. In July 2003, the USB OTG addendum was released, defining a new class of devices for portable, battery-powered products with limited host capabilities. Finally, in May 2005, the Wireless USB (WUSB) specification was released.

USB OTG is an addendum to the USB 2.0 specification that defines a new class of devices that extends the functionality of a peripheral product to include limited host capabilities. As the name implies, the original target of the specification was consumer portable devices with which end users may have wanted to share data when a computer was not available. Usage examples included sharing contact information between two PDAs or cell phones, sharing pictures from one digital still camera or camera phone with another, or printing directly from a digital still camera or

PDA. Like standard USB, OTG is a point-to-point, host-centric bus and is not intended as a peer-to-peer networking connection. An OTG product must act as a standard peripheral when connected to a standard USB host such as a PC. The OTG addendum mainly addresses how a device must act when it is in host mode.

Just like a standard USB host port, an OTG host must supply power; but the required supply current is limited to 8 mA. Unlike a standard USB host in a PC, an OTG device may not have a simple way to add drivers for "unrecognized" devices. Therefore, an OTG device must supply what is called a Targeted Peripheral List (TPL), which allows device manufacturers to specify exactly what peripherals they will support. The specification also mandates messaging that will communicate to the end user that an unsupported device has been plugged in and will not work. This messaging can be as simple as an LED or as complex as a text display.

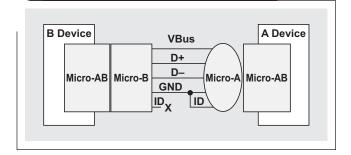

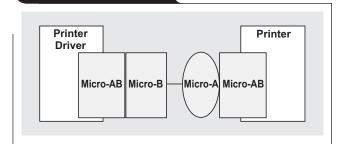

Since the target end products were primarily small portable consumer electronics, a standard USB connector was too large. Therefore the USB Implementers Forum introduced new mini and micro connectors. The mini-B connector has been in common use as a small-form-factor receptacle on many USB peripherals. The micro-AB receptacle is what a dual-role OTG device must use. This connector accepts either a micro-A plug or a micro-B plug. The orientation of the cable determines which device in an OTG connection acts as the host (A side) and which acts as the peripheral (B side), as shown in Figure 1. The new connector has an additional pin (ID) that is left open on the micro-B plug and is grounded in the micro-A plug to determine initial roles.

Although cable orientation determines which role, host or peripheral, each OTG device will initially assume at connection, the roles can be reversed via a dynamic switching method called Host Negotiation Protocol (HNP).

Figure 1. Cable orientation determines initial state

Why switch roles? The need for this can be understood if we look at Figure 2 and consider that every OTG device must include a TPL. The device on the left has the printer on its TPL, but it is *not* on the printer's TPL. If the user plugs in the cable backwards as shown in Figure 2, then communication between the two devices will not be possible without reversing the roles. HNP allows the roles to be reversed silently and automatically, thus enabling the communication and enhancing the end-user experience by eliminating the need to disconnect the cable and reverse it.

Session Request Protocol (SRP) is a method for turning bus power off/on at the discretion of the host device to save power when communication is not needed. Many of the target devices for OTG are battery-powered. Extending battery life is of utmost importance to both the manufacturer and the end user. With this in mind, the A device (as indicated by cable orientation) in an OTG connection can

Figure 2. HNP example

power off the bus and go into a sleep mode, extending battery life. This also allows the B device to go to sleep if it so desires. However, if the end user desires the communication to start up again and initiates this request on the B device, SRP allows the B device to request the A device to turn on VBus power and start a session. An OTG session is defined as the time during which the A device is furnishing VBus power. To wake up the A device, the B device pulses first the D+ wire and then the VBus wire. The A Device, which can respond to either pulsing, detects the pulse, causing it to switch on VBus and start a session.

SRP is more complex than this simple illustration. The B device, for example, must first measure VBus to ensure that a session is not in progress. It must also be able to differentiate between a classic PC or an OTG device at the other end of the cable. It does this by delivering measured amounts of current to the VBus wire and noting the resulting voltage.

# TUSB60xx: The family of high-speed, OTG-interface-solution devices

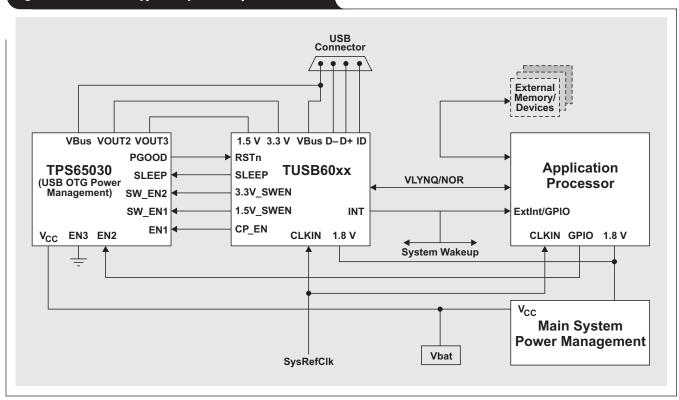

This family of devices enables application processors (DSPs, OMAP $^{\text{TM}}$ , and MCUs) that do *not* have integrated USB cores to function as either a USB 2.0 high-speed peripheral, an embedded USB 2.0 high-speed host controller, or a full USB 2.0 high-speed OTG device. The TUSB60xx devices serve as bridges between a USB 2.0 high-speed bus and a local processor host interface. Figure 3 shows a typical system implementation. The TUSB60xx family is

Figure 3. TUSB60xx typical system implementation

fully compliant with high-speed USB OTG. These devices come in a space-saving  $5\times5\text{-mm}$  MicroStar Junior  $^{\text{TM}}$  BGA package and support an ultralow-power idle mode that consumes less than  $100~\mu\text{A}$ . Both of these features are critical to small portable consumer devices that feature USB OTG. An application processor is required to support software needs. These include the operating system for host mode, the drivers for the TPL devices when they are in OTG host mode, and the application functionality when the TPL devices are in peripheral mode. A summary of the TUSB60xx family's features and benefits is given in Table 1.

The TPS65030 is a companion power-management device to the TUSB60xx devices. In addition to providing all of the power requirements of the TUSB60xx, it can provide 5 V at 100 mA on the VBus line when a TUSB60xx device is in OTG host mode.

The first two members of the TUSB60xx family are the TUSB6010B and the TUSB6020. The only difference between the two devices is the external processor interface.

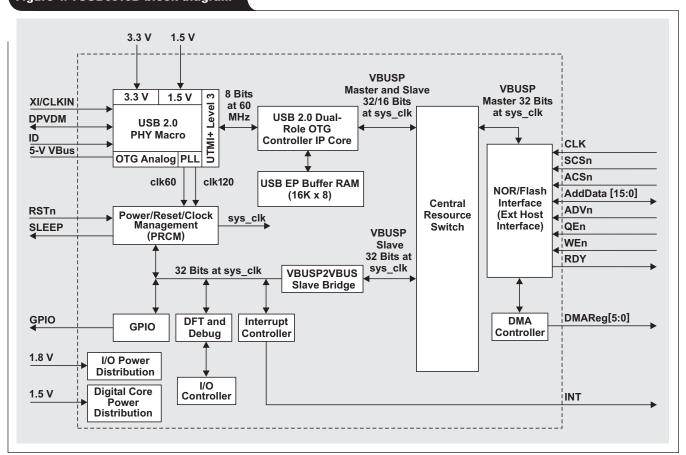

The TUSB6010B (Figure 4) features a 16-bit muxed NOR-flash interface that supports both synchronous and asynchronous transfers. The TUSB6010B supports single and burst read/write access with a programmable burst size of up to 16 half words. It can also support 6 external direct-memory-access (DMA) requests. The TUSB6010B will gluelessly interface to the OMAP1710 and the OMAP2420 processors. When the device is used with the OMAP2420 with the GPMC running at 55 MHz, the throughput measures a sustained 250-Mbps bulk input and bulk output with DMA. When the TUSB6010B is connected to the OMAP1710 with the external memory interface running at 55 MHz, the throughput measures a sustained 250-Mbps

Table 1. TUSB60xx family

| Features                                                                                 | Benefits                                                                                                  |

|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| USB 2.0 high-speed, OTG-compliant device                                                 | Certified compliance and interoperability                                                                 |

| Multiple external processor interface options                                            | Flexible architectures to interface to multiple processors                                                |

| • Ultralow-power (<100-μA) idle mode; small form factor = 5 x 5-mm MicroStar Junior™ BGA | <ul> <li>Designed to meet the critical demands of portable,<br/>battery-powered target devices</li> </ul> |

Figure 4. TUSB6010B block diagram

bulk output with synchronous DMA and a sustained 100-Mbps bulk input with asynchronous DMA.

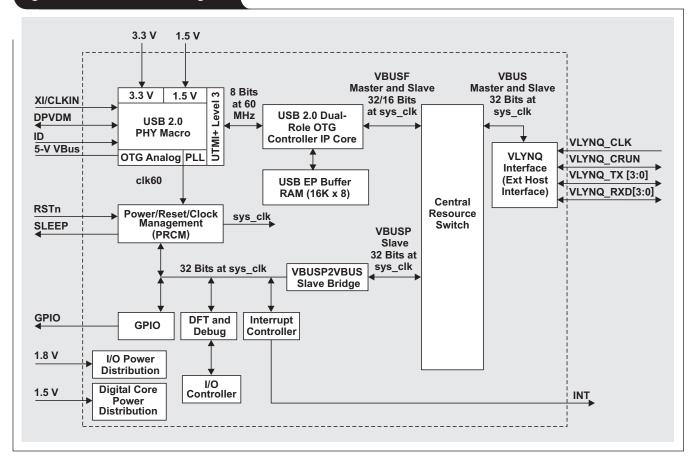

The TUSB6020 (Figure 5) features a VLYNQ interface, which is a high-speed, low-pin-count, point-to-point serial specification developed by TI. The TUSB6020 features a 10-pin interface supporting 4 receive lines and 4 transmit lines that run at 150 MHz. It works as a memory-mapped master/slave interface with a multichannel DMA controller. The integrated list processor is capable of parsing CPPI 3.0-compliant buffer descriptors. The TUSB6020 will gluelessly interface to any TI processor that supports a VLYNQ interface. These processors include (but are not limited to)

the DaVinci<sup>™</sup> family, the DM320, and the OMAP5912. Utilizing an 8-pin VLYNQ interface running at 125 MHz, the TUSB6020 will enable a sustained 267-Mbps bulk input and bulk output.

# **Related Web sites**

interface.ti.com www.ti.com/davinci www.ti.com/sc/device/partnumber Replace partnumber with OMAP5912, TUSB6020, or TPS65030

Figure 5. TUSB6020 block diagram

# New zero-drift amplifier has an $I_0$ of 17 $\mu$ A

# By Thomas Kugelstadt

Senior Systems Engineer, Industrial Systems

Micropower applications require not only a very small offset and offset drift but also very low noise. Such applications include instrumentation front ends in biomedical electronics, conditioning stages in CO2 detectors, and electronic sensor interfaces in precision metrology equipment. A front-end, low-noise amplifier combined with signal-conditioning circuits and a sensor forms a microsystem that often has to either be portable or stand alone and is therefore battery-powered. Hence, the power consumption has to be small. It is therefore crucial to eliminate the 1/f (flicker) noise and to reduce the overall noise down to the fundamental thermal noise, which is mainly determined by the allowable current consumption of the input stage.

While an auto-zero amplifier (AZA) removes its offset and 1/f noise at the cost of a raised white-noise level in the baseband, a chopper-stabilized amplifier reduces its baseband noise to the initial white-noise level but generates large output ripple instead. Because the input-stage noise is inversely proportional to its quiescent current,  $e_{\rm n}^2 \approx 1/I_{\rm Q}$ , an AZA often requires a significant increase in  $I_{\rm Q}$  to achieve the desired noise levels after noise folding. Since this increase counteracts the requirements of a micropower amplifier, it is desirable to use a chopper-stabilized amplifier in micropower applications and to find some way to filter the output ripple.

This article describes a new, micropower, low-noise, chopper-stabilized operational amplifier, the OPA333, which operates from a 1.8-V supply, requiring a quiescent current of only 17  $\mu A$ .

### **Overview**

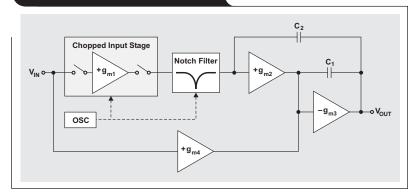

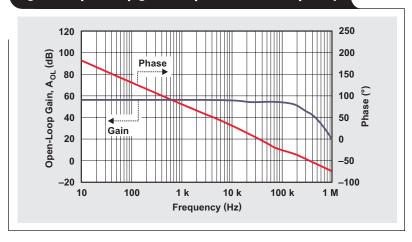

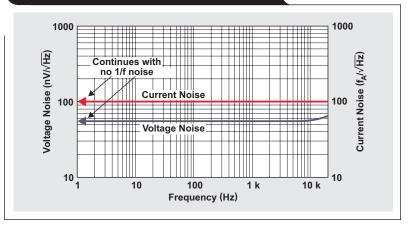

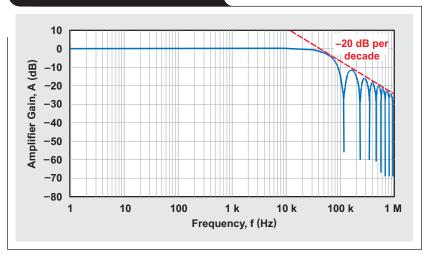

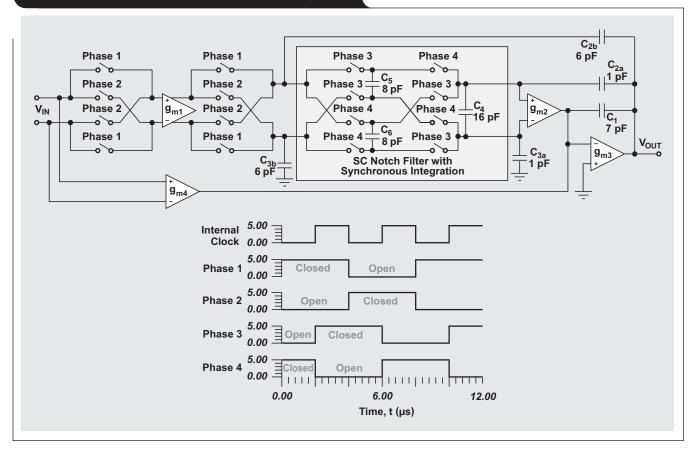

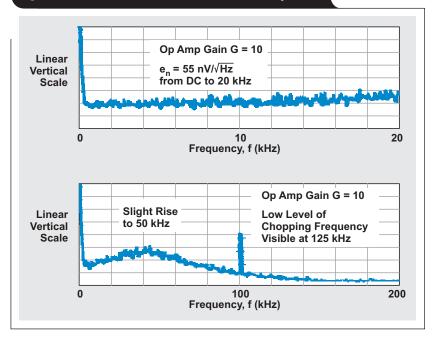

The OPA333 consists of a high-precision path  $(g_{m1}, g_{m2},$  and  $g_{m3})$  in parallel with a wideband path  $(g_{m4}$  and  $g_{m3})$  (see Figure 1). The precision path ensures a high open-loop gain,  $A_{OL}$ , of 130 dB, while the wideband path provides a 350-kHz gain bandwidth at a phase margin of 60° (Figure 2). An internal, patent-pending notch filter removes chopper noise by a factor of more than 500, yielding a voltage-noise spectral density of 55 nV/ $\sqrt{\rm Hz}$  across a 20-kHz bandwidth (Figure 3).

Figure 1. Internal block diagram

Figure 2. Open-loop gain and phase versus frequency

Figure 3. Noise densities versus frequency

With typical values for offset and drift of  $V_{OS}=2~\mu V$  and  $dV_{OS}/dT=20~nV/^{\circ}C$ , respectively, the OPA333 also generates only 1.1  $\mu V_{pp}$  of instantaneous noise in the 0.01- to 10-Hz band. The device offers rail-to-rail input and output and is available in SC70 and SOT23 packaging. Operation is specified from  $-40^{\circ}C$  to  $125^{\circ}C$ .

# **OPA333** design rationale

The remainder of this article explains the underlying principles of the OPA333 design, describing the functional blocks and their individual contributions to the overall performance of this remarkable amplifier.

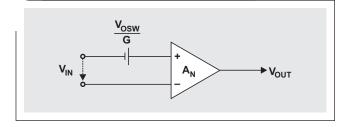

# Offset cancellation of a wideband amplifier in general

Reducing the input offset voltage of a wideband amplifier,  $A_{\rm W}$ , typically requires the support of an additional stabilizing or nulling amplifier,  $A_{\rm N}$ , which is connected in parallel to the main amplifier (Figure 4). The stabilizing amplifier must be able to cancel its own offset, thus resembling an ideal amplifier. In addition, its open-loop gain has to be significantly larger than  $A_{\rm N} >> A_{\rm W}$ . This is usually achieved by using a multistage amplifier whose input gain is identical to  $A_{\rm W}$  and whose output gain is G, with G >> 1. Note that the nulling amplifier can use chopping or auto-zeroing to null its own offset.

The output voltage of the circuit in Figure 4 is given by

$$\label{eq:Vout} V_{\text{OUT}} = V_{\text{W}} + V_{\text{N}} = A_{\text{W}} \times (\text{G}+1) \times \frac{V_{\text{IN}} + V_{\text{OSW}}}{\text{G}+1}.$$

Assuming G>>1 and substituting  $A_WG$  with  $A_N$  yields the effective open-loop gain and input offset for the amplifier model in Figure 5:

$$V_{OUT} = A_N \times \frac{V_{IN} + V_{OSW}}{G}$$

.

Figure 4. Offset cancellation principle

Figure 5. Effective amplifier model

Thus, the DC gain has increased by factor G, from  $A_W$  to  $A_N$ , while the input offset of the wideband amplifier is reduced by G (typically 60 dB).

# Multistage stabilizing amplifier

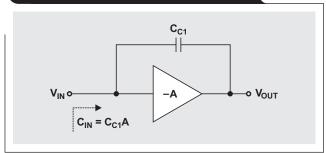

Large capacitance values are required to achieve low dominant pole frequencies. We recall that Miller compensation is used in op amp design to reduce these large values down to a size feasible for on-chip integration. Miller compensation relies on the effect that the input capacitance of an amplifier,  $C_{\rm IN}$ , appears to be A times larger than the actual capacitance in the feedback loop,  $C_{\rm C1}$ , with A being the amplifier gain (see Figure 6).

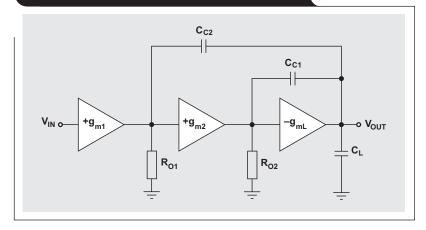

Because the precision path requires significantly higher gain than the wideband path, a three-stage cascade structure is used to provide that gain while allowing operation from very low supply voltages. If we neglect the chopper mechanism and the notch filter in Figure 1, the stabilizing

Figure 6. Miller effect:  $\rm C_{IN} = \rm C_{C1}(A+1).$  For A >> 1:  $\rm C_{IN} \approx \rm C_{C1}A.$

amplifier that remains is a three-stage, nested Miller-compensated (NMC) cascade amplifier as shown in Figure 7.

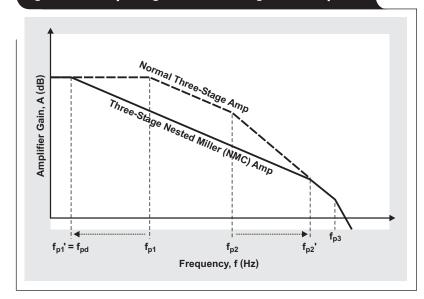

Miller compensation provides the additional valuable feature of frequency-response shaping through a process known as *pole-splitting*. Figure 8 shows the frequency response of an uncompensated three-stage amplifier with its pole frequencies  $f_{\rm p1}$ ,  $f_{\rm p2}$ , and  $f_{\rm p3}$ . Through careful design of the  $g_{\rm m}$  stages and appropriate selection of the Miller compensation capacitances, it is possible to shift  $f_{\rm p1}$  down to a very low frequency,  $f_{\rm p1}{}'$ , making it the dominant pole of the precision path. At the same time,  $f_{\rm p2}$  is pushed to higher frequencies,  $f_{\rm p2}{}'$ , expanding the 20-dB/dec slope and thus the range of stable operation.

In the case of a stand-alone amplifier,  $\rm f_{p2}$  is usually located beyond the unity-gain frequency, allowing a three-stage NMC structure to achieve high bandwidth beyond 10 MHz while maintaining phase margins of up to 70°.

In the OPA333 design, however, the NMC amplifier operates in parallel with the wideband stages,  $g_{\rm m4}$  and  $g_{\rm m3}.$  Because this wideband forward path is responsible for providing the necessary bandwidth and phase margin of the overall amplifier, the stability requirements of the NMC amplifier are relaxed, allowing its second pole,  $f_{\rm p2},$  to occur before the unity-gain crossover.

# Where do we apply the actual offset cancellation?

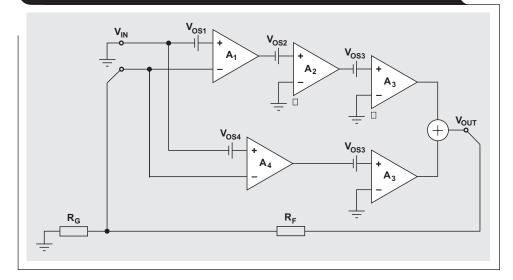

To answer this question we can, for convenience, replace the  $g_{\rm m}$  stages with actual op amps, where the precision path comprising  $A_1$

to  $A_3$  is in parallel with the wideband path comprising  $A_4$  and  $A_3$  (Figure 9). For further simplification, the switching network and the notch filter have been left out, and the amplifier circuit is shown in a feedback configuration.

Figure 7. Three-stage NMC cascade amplifier

Figure 8. Pole splitting of the three-stage NMC amplifier

Figure 9. Deriving  $\mathsf{V}_\mathsf{OUT}$  as a function of individual offset voltages,  $\mathsf{V}_\mathsf{OSi}$

Providing each amplifier with its individual input offset voltage and setting  $V_{\rm IN}$  to zero yields an output of

$$\begin{split} \mathbf{V}_{\mathrm{OUT}} &= \mathbf{A}_{3} \left\{ \mathbf{V}_{\mathrm{OS3}} + \mathbf{A}_{2} \left[ \mathbf{V}_{\mathrm{OS2}} + \mathbf{A}_{1} \left( \mathbf{V}_{\mathrm{OS1}} - \mathbf{V}_{\mathrm{OUT}} \, \boldsymbol{\beta} \right) \right] \right\} \\ &+ \mathbf{A}_{3} \left[ \mathbf{V}_{\mathrm{OS3}} + \mathbf{A}_{4} \left( \mathbf{V}_{\mathrm{OS4}} - \mathbf{V}_{\mathrm{OUT}} \, \boldsymbol{\beta} \right) \right], \end{split}$$

where

$$\beta = \frac{R_F}{R_F + R_G}.$$

Separating the  $V_{\text{OUT}}$  terms and solving for  $V_{\text{OUT}}$  gives

$$V_{OUT} = \frac{1}{\beta} \Bigg( \frac{2V_{OS3} + V_{OS2}A_2 + V_{OS4}A_4 + V_{OS1}A_1A_2}{A_1A_2 + A_4} \Bigg).$$

Assuming that the DC gains of  $A_4$  and  $A_1$  are matched,

$$V_{OUT} = \frac{1}{\beta} \left( \frac{2V_{OS3}}{A_1 A_2} + \frac{V_{OS2}}{A_1} + \frac{V_{OS4}}{A_2} + V_{OS1} \right).$$

We see that, except for  $V_{\rm OS1}$ , all offsets are strongly suppressed by the open-loop gains of at least one, if not two, preceding amplifiers. The nonattenuated  $V_{\rm OS1}$ , however, requires active cancellation through either chopping or auto-zeroing.

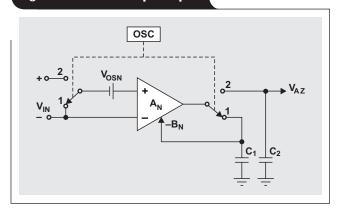

# **Auto-zeroing versus chopping**

Figures 10 and 11 show the simplified principles of both offset cancellation methods. Auto-zeroing consists of two phases, a nulling phase with switches in position 1 and an amplification phase with switches in position 2. In the nulling phase, the amplifier measures its own offset and stores it on capacitor  $\mathrm{C}_1$ . In the amplification phase, the amplifier measures the input voltage plus the offset and subtracts the previously stored offset from the contaminated input. The resulting, offset-free output signal is stored on  $\mathrm{C}_2$  and operates as correcting voltage for the main amplifier.

The function of sampling and holding the offset voltage makes the AZA a data-sampling system prone to aliasing and folding effects. For DC and low frequencies, the noise properties in the time domain change slowly, and the subtraction of two consecutive noise samples results in a true cancellation. At higher frequencies this correlation diminishes, and subtraction errors translate into wideband foldover components in the baseband, where they make up the lion's share of baseband noise.

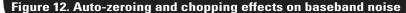

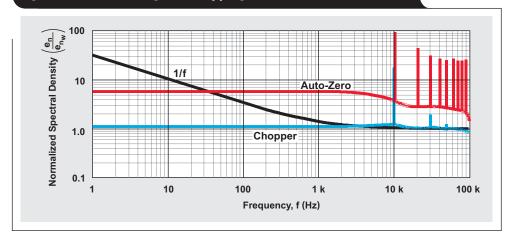

Figure 12 shows that the AZA removes offset and 1/f noise, but at the cost of a significantly raised noise floor in the baseband.

Because the noise power density of an amplifier's input stage is inversely proportional to its transconductance

Figure 10. Auto-zero principle

Figure 11. Chopper principle

Figure 13. Filter transfer function

$(e_n^2=2/3\times 4KT/g_m),$  and  $g_m$  is proportional to the stage quiescent current  $(g_m\approx I_Q),$  the power density is inversely proportional to the quiescent current  $(e_n^2\approx 1/I_Q).$  Therefore, to reduce the baseband noise of an AZA to the desired level, the initial input noise must be lowered through a significant increase in quiescent current, which counteracts the intrinsic requirements of a micropower amplifier.

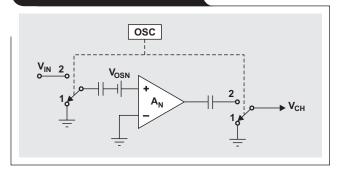

In strong contrast to the AZA, the chopper amplifier does not introduce aliasing fold-over components. As shown in Figure 11, a chopper simply modulates its offset and low-frequency noise to higher frequencies. Here the noise is neither sampled nor held, just periodically inverted without changing the general properties of the noise in the time domain. Although the power density of the chopper output noise results from a summation in the chopper modulation, as is the case for the sample-and-hold process in the AZA, the replicas (odd harmonics only) vary rapidly via a  $1/n^2$  function, making their contribution to the baseband negligible.

As shown in Figure 12, for chopper frequencies larger than the noise-corner frequencies, the baseband white noise in the output is only slightly larger than the initial white-noise floor, which eliminates increases in quiescent current and makes the chopper amplifier suitable for micropower applications.

# **Output noise filter**

While the chopper does not introduce wideband folding components into the baseband, the process of chopping does modulate the offset, or DC noise, into the higher frequency range where no noise existed before, thus creating large output ripples. The OPA333 therefore possesses a switched-capacitor (SC), low-pass notch filter in the offset cancellation path with filter notches at the chopper frequency and its harmonics. The filter's transfer function, shown in Figure 13, reduces the output ripple by a factor of more than 500. Figure 14 shows the difference in output ripple with and without the notch filter.

Figure 14. Output ripple with and without filter = 75 mV without Notch Filter 40 Output Voltage, V (mV) 30 20 10 0 -10 -20 260 290 300 250 270 280 Time, t (µs)

# The final amplifier system

Figure 15 shows the actual implementation of the chopper-stabilized amplifier, revealing a differential signal-path structure for  $g_{\rm m1}$  and the SC notch filter. Note that, for signal symmetry, the implementation of a third capacitor,  $C_3$ , is required.

During phases 1 and 2, the input signal is modulated. During phases 3 and 4, the capacitors  $C_5$  and  $C_6$  work in tandem. While  $C_5$  is charged with  $g_{\rm ml}$ 's output current, the charge of  $C_6$  is transferred to the integrator,  $g_{\rm m2}$ , and vice versa.

Note that the input signal is modulated twice, once by the input switches of  $g_{m1}$  and a second time by the output switches. Relative to  $V_{\rm IN}$ , the polarity or direction of  $g_{m1}$ 's output current remains the same during phases 1 and 2. However, the offset voltage, or offset current, is modulated only once by the output switches. Its polarity changes from phase 1 to phase 2.

During the first half of phase 3 (that is,  $t_{CK}/2$  of the clock period), the phase 1 switches are active and  $C_5$  is charged with  $g_{m1}$ 's output current,  $I_{SIG} + I_{OS}$ . During the

second half of phase 3, the phase 2 switches are active, the direction of the offset current changes, and  $C_5$  is charged with  $I_{\rm SIG}-I_{\rm OS}$ .

charged with  $I_{\rm SIG}-I_{\rm OS}.$  The capacitor charge is given by  $Q=I_{\rm C}\times t,$  with  $t=t_{\rm CK}/2,$   $I_{\rm C1}=I_{\rm SIG}+I_{\rm OS},$  and  $I_{\rm C2}=I_{\rm SIG}-I_{\rm OS}.$  Thus, after phase 3 is completed,  $C_5$  has the charge of  $Q_{\rm C5}=(I_{\rm SIG}+I_{\rm OS})\times t_{\rm CK}/2+(I_{\rm SIG}-I_{\rm OS})\times t_{\rm CK}/2=I_{\rm SIG}\times t_{\rm CK}.$  The offset-free charge is then transferred to the next stage during phase 4, where the same procedure is applied to  $C_6.$

While the large attenuation of the notch filter removes the output ripple, it may also filter the signal to some degree. A signal delay is created by the integrate-and-transfer action, which affects the circuit differently depending on how the compensation capacitors are connected.

Notice that  $\mathrm{C}_2$  and  $\mathrm{C}_3$  have been split into "a" and "b" portions (Figure 15). The "b" portion returns most of the compensation to the filter input,  $\mathrm{C}_{2\mathrm{b}}=6$  pF, maintaining good continuous-time characteristics for the signal path. The smaller "a" portion,  $\mathrm{C}_{2\mathrm{a}}=1$  pF, connects to the filter output, providing sufficient local-loop stability. The complex compensation scheme is responsible for a slight rise in the

Figure 15. Internal block diagram and timing sequence

noise floor beyond  $20~\mathrm{kHz}$ , which is visible in Figure 16.

# **Summary**

This article elaborates on the technical implementations of the OPA333, the industry's superior, zero-drift micropower amplifier. Chopper stabilization ensures low baseband noise at very low supply currents. An integrated, patent-pending notch filter removes the output ripple created by the chopper modulation of the input offset.

Because an amplifier's noise power density is inversely proportional to its quiescent current, the product  $(e_n^2\times I_Q)$  represents a figure of merit, revealing how much additional tail current was necessary to reduce the remaining baseband noise to the desired level after the process of offset cancellation. A more familiar figure is the ratio of gain bandwidth to quiescent current, GBW/I\_Q, disclosing how much bandwidth per microampere was achieved. In both figures of merit, the OPA333 demonstrates far superior performance versus even its closest competitor (see Table 1).

# Related Web sites amplifier.ti.com www.ti.com/sc/device/OPA333

Figure 16. DC to 20-kHz and 200-kHz noise spectra

Table 1. Comparison of the OPA333 versus previous zero-drift amplifiers

|                                                 | TI     | COMPETITOR    |                |                |               |               |  |

|-------------------------------------------------|--------|---------------|----------------|----------------|---------------|---------------|--|

| DEVICE                                          | OPA333 | (1)<br>AD8628 | (2)<br>ICL7650 | (3)<br>LTC2054 | (4)<br>OPA335 | (5)<br>AD8551 |  |

| Year                                            | 2006   | 2005          | 2005           | 2004           | 2002          | 2002          |  |

| f <sub>CH</sub> (kHz)                           | 125    | 15            | _              | _              | _             | _             |  |

| f <sub>AZ</sub> (kHz)                           | _      | 15            | 0.25           | 1              | 10            | 4             |  |

| V <sub>0S</sub> (μV)                            | 2      | 1             | 1              | 3              | 1             | 1             |  |

| I <sub>B</sub> (pA)                             | 70     | 30            | 5              | 1              | 70            | 10            |  |

| GBW (kHz)                                       | 350    | 2500          | 2000           | 500            | 2000          | 1500          |  |

| $e_n (nV/\sqrt{Hz})$                            | 55     | 22            | 25             | 85             | 55            | 42            |  |

| Ι <sub>Q</sub> (μΑ)                             | 15     | 1100          | 2000           | 150            | 285           | 975           |  |

| $e_n^2 \times I_0$ (nV <sup>2</sup> × $\mu$ A)* | 45     | 532           | 1250           | 1084           | 862           | 1720          |  |

| GBW/I <sub>Q</sub> (kHz/μA)*                    | 23     | 2             | 1              | 3              | 7             | 2             |  |

<sup>\*</sup>Figure of merit

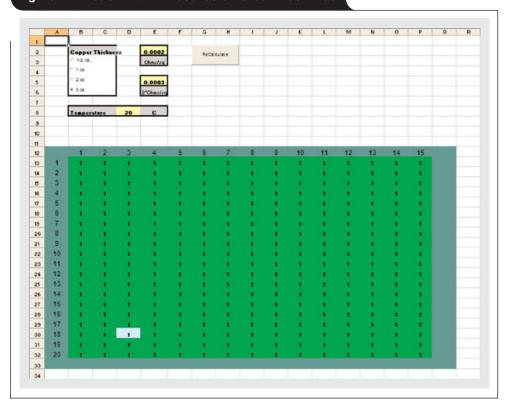

# Spreadsheet modeling tool helps analyze power- and ground-plane voltage drops to keep core voltages within tolerance

# By Steve Widener

Analog Field Applications Engineer

# Introduction

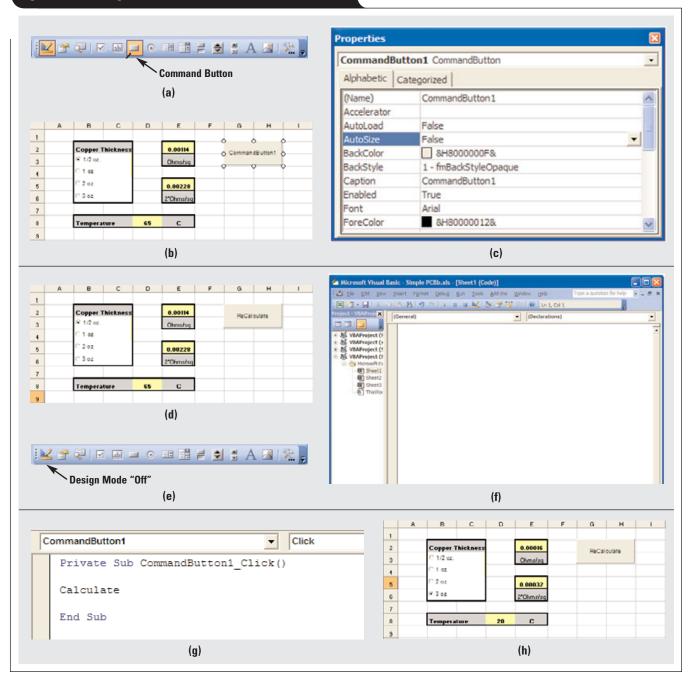

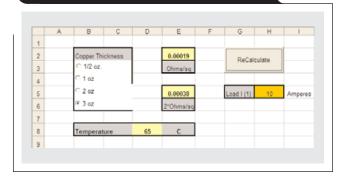

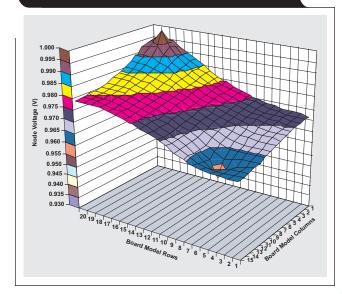

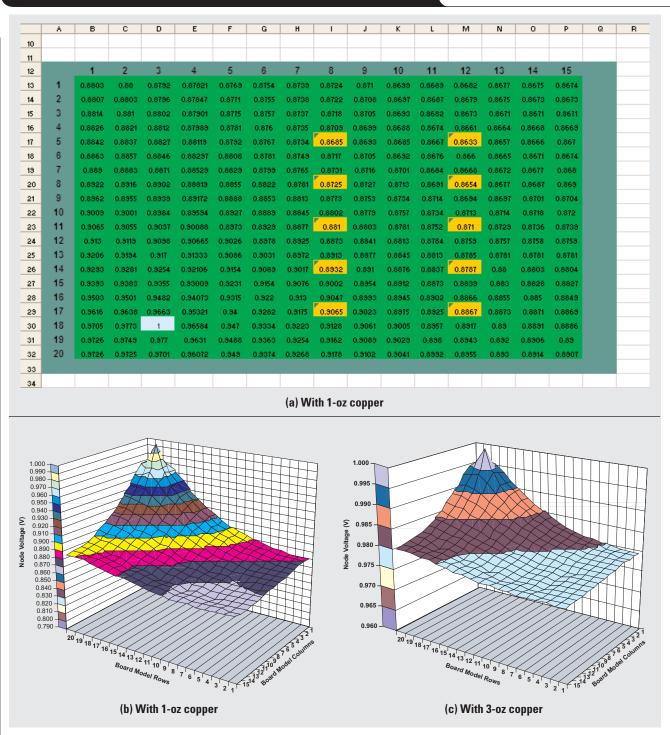

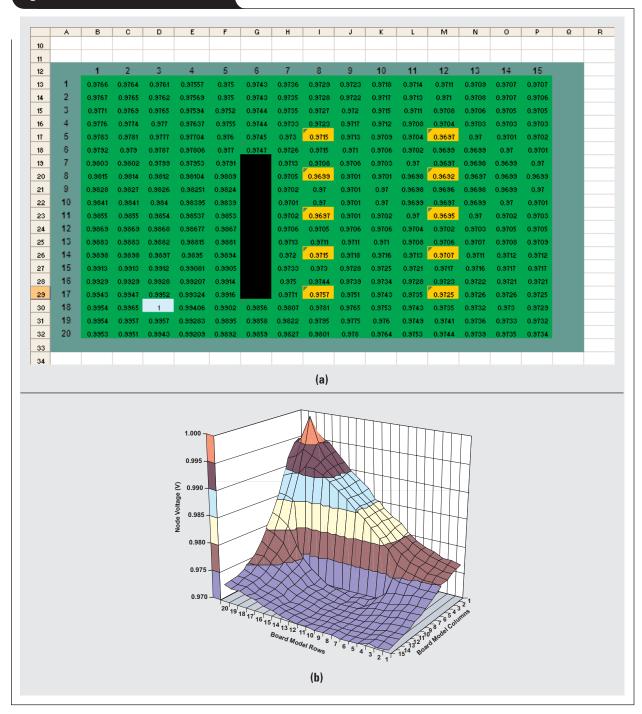

The trend toward smaller geometries in processor cores drives requirements for lower-voltage power supplies. For example, DSPs from Texas Instruments (TI) such as the TMS320TCI648x series require a 1-V core. As processor-core voltages drop, clock frequencies are typically increased to match the thermal capabilities of the packaging and of the overall cooling systems. That means higher currents in the power structures of printed circuit boards (PCBs). It is not uncommon to see 50- to 100-A current requirements for a 1-V rail when multiple processors are distributed on a single PCB. This article addresses the impact of these higher currents on the power- and ground-plane design and on the core-voltage-tolerance budget and describes a spreadsheet model that may be used to calculate voltage gradients.

# Requirements for processor-core voltage

The typical voltage-tolerance budget for the processor core is 3% for a 1-V rail, which equates to 30 mV for the total static and dynamic response of the power supply. TI's new power devices such as the PTH TurboTrans<sup>TM</sup> series (T2) modules, and new synchronous buck controllers such as the TPS40140, have been designed with internal references that allow for 1.5% tolerance under static line, load, and temperature conditions. The current guidance allocates the remaining 1.5% tolerance for the transient response of the supply. This, in combination with the bandwidth of the switching power supply, determines the amount of capacitance required to meet the core-voltage requirements. Local bypassing counteracts the inductive nature of large ground planes. Little attention is typically paid to the DC voltage drop in the power planes. As currents continue to increase and core voltages decrease, power- and ground-plane DC voltage drops will become a more significant portion of the total tolerance budget.

# Power- and ground-plane voltage-drop considerations

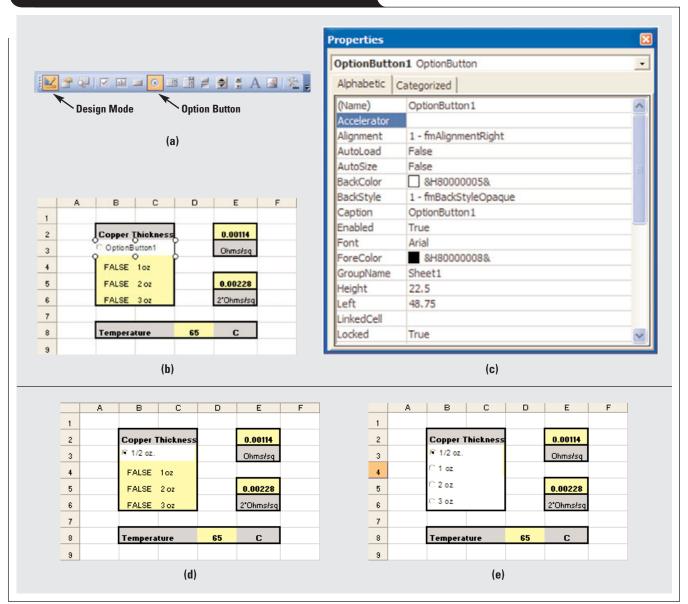

Power- and ground-plane copper thickness is the primary attribute that impacts the voltage drop. Another major factor is the placement of the processor loads relative to the power-supply output pins. Power converters such as the PTH series allow for remote sensing to mitigate board voltage drops, but there are few tools to aid the designer in the placement of these remote sensing lines. Most designers use an ohms-per-square figure for different

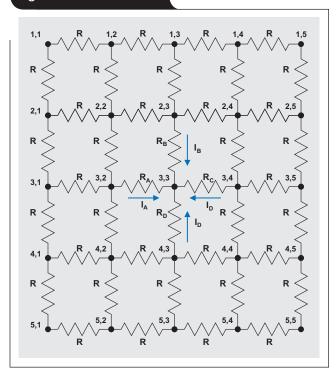

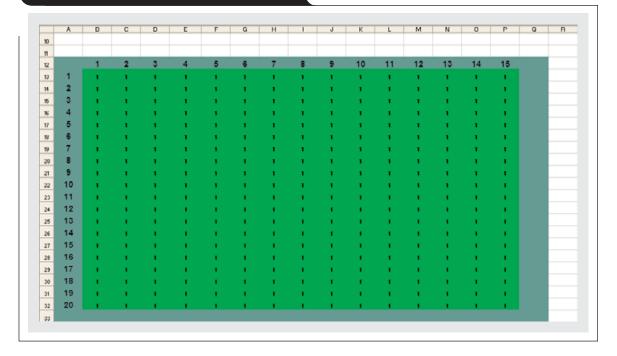

Figure 1. Resistor sheet

copper thicknesses to calculate an equivalent resistance and to determine the required copper weight. This technique works well for simple configurations; but when multiple processors or significant plane discontinuities are present (due to vias or other features), the simple ohmsper-square method may not be adequate to model the voltage drop in the power and ground planes.

### Commercial software

Commercial software for finite-element analysis may be used to compute the plane voltage drops for arbitrary geometries, but the software is expensive and requires a developed expertise. There is no simple tool to generate a PCB model and quickly assess the plane voltage drops.

# **SPICE** modeling

A model of the PCB may be constructed with an equivalent sheet resistance model (see Figure 1), with sources and loads connected to the appropriate nodes. The PCB

model can then be solved with a SPICE-based simulator. The difficulty in the SPICE method is that the schematic is unwieldy and the results are difficult to visualize.

# A spreadsheet-based model

This article details a method that uses Microsoft® Excel® spreadsheet software to determine plane voltage distribution on a PCB with arbitrary geometry and source/load placement. A little-used feature of Excel, circular references and iteration, is used to solve the network matrix. The method may also be used with other mathematical software. This article also develops the necessary equations and provides step-by-step instructions to calculate power/ground-plane voltage drop for arbitrary source and load conditions.

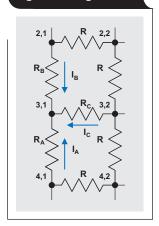

# Node equations for sheet resistance

Figure 1 is a schematic model of PCB node voltages interconnected by equivalent sheet resistances, R, with nodes expressed as *row*, *column*. This model divides the PCB into 25 nodes. Increasing the number of squares will provide more resolution. This array is sufficient to illustrate the general node equations applicable to larger models. The voltage at any node is determined by using Kirkoff's current law, which states that the sum of all currents into a node must equal zero. One of three equations is required to determine node voltage, which depends on the node location—central, edge, or corner.

### **Central-node equations**

For central node 3,3 in Figure 1, the current equation is

$$I_A + I_B + I_C + I_D = 0. {1}$$

Using Ohm's law yields

$$\frac{V_{3,2} - V_{3,3}}{R_A} + \frac{V_{2,3} - V_{3,3}}{R_B} + \frac{V_{3,4} - V_{3,3}}{R_C} + \frac{V_{4,3} - V_{3,3}}{R_D} = 0. \quad \textbf{(2)}$$

Solving Equation 2 for  $V_{3,3}$  yields

$$V_{3,3} = \frac{R_B R_C R_D V_{3,2} + R_A R_C R_D V_{2,3} + R_A R_B R_D V_{3,4} + R_A R_B R_C V_{4,3}}{R_B R_C R_D + R_A R_C R_D + R_A R_B R_D + R_A R_B R_C}. \eqno(3)$$

Equation 3 is the general form of the equation for a central node with arbitrary sheet resistance. This equation accommodates variations in square resistance that are due to localized heating or other nonuniformities. In the case of uniform sheet resistance, Equation 3 simplifies to

$$V_{3,3} = \frac{V_{3,2} + V_{2,3} + V_{3,4} + V_{4,3}}{4}.$$

(4)

# **Edge-node equations**

For edge node 3,1, Figure 2 depicts the currents flowing from the three adjacent nodes. The current equation for an edge node is

$$I_A + I_B + I_C = 0.$$

(5)

# Figure 2. Edge node

Using Ohm's law yields

$$\frac{V_{4,1} - V_{3,1}}{R_A} + \frac{V_{2,1} - V_{3,1}}{R_B} + \frac{V_{3,2} - V_{3,1}}{R_C} = 0.$$

(6)

Solving for V<sub>31</sub> yields

$$V_{3,1} = \frac{R_B R_C V_{4,1} + R_A R_C V_{2,1} + R_A R_B V_{3,2}}{R_B R_C + R_A R_C + R_A R_B}.$$

(7)

Equation 7 is the general form of the equation for an edge node with arbitrary sheet resistance. In the case of uniform sheet resistance, Equation 7 simplifies to

$$V_{3,1} = \frac{V_{4,1} + V_{2,1} + V_{3,2}}{3}.$$

(8)

### **Corner-node equations**

For corner node 5,1, Figure 3 depicts the currents flowing from the two adjacent nodes. The current equation for a corner node is

$$I_{A} + I_{B} = 0.$$

(9)

### Figure 3. Corner node

Using Ohm's law yields

$$\frac{V_{5,2} - V_{5,1}}{R_A} + \frac{V_{4,1} - V_{5,1}}{R_B} = 0.$$

(10)

Solving for  $V_{5,1}$  yields

$$V_{5,1} = \frac{R_B V_{5,2} + R_A V_{4,1}}{R_B + R_\Delta}.$$

(11)

Equation 11 is the general form of the equation for a corner node with arbitrary sheet resistance. In the case of uniform sheet resistance, Equation 11 simplifies to

$$V_{5,1} = \frac{V_{5,2} + V_{4,1}}{2}.$$

(12)

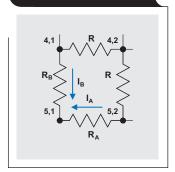

## Source nodes

The outputs of power supplies are modeled as fixed values (voltages) at the geometrically relevant nodes. Many power supplies utilize differential remote sensing. In the model, the fixed-voltage nodes may represent the local sense points, and the power-supply output is varied to set the desired voltage at those remote sensing points.

The remaining equations solve for node voltages where a load is present at the node.

# **Load equations**

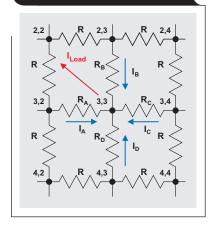

### **Central-node equations**

In the case of a central node with a load (Figure 4), the current equation is

$$I_A + I_B + I_C + I_D = I_{Load}.$$

(13)

Figure 4. Central load node

Using Ohm's law yields