#### **OBSOLETE**

User's Guide

SNAA030A-May 2006-Revised April 2013

# AN-1488 LM4681 Demonstration Board

#### 1 Quick Start Guide

- 1. Connect the I<sup>2</sup>C signal generation and interface board to a computer's parallel port.

- 2. Install LM4681 control software: "LM4681 Software ver1-1."

- 3. Apply a 3.0V to 5.0V power supply's positive voltage output to the "I2CVDD" pin on jumper JP6. Apply the power supply's ground return to the "GND" pin on JP6.

- 4. Apply a 9.0V to 15.5V power supply's positive voltage output to the "VDD" pin on JP1. Apply the power supply's ground return to the "GND" pin on JP1.

- 5. Connect the supplied 5-wire cable between the I<sup>2</sup>C signal generation and interface board and the 5-pin connector (JP7) on the LM4681 demonstration board.

- 6. Apply a stereo audio signal to jumpers JP4 and JP2. Apply the source's signal and ground to the "IN1" pin and the "GND" pin, respectively.

- 7. Connect a load ( $\geq 8\Omega$ ) between the pins on JP5 and another load between the pins on JP3.

- 8. Apply power. Make measurements. Plug in a pair of headphones. Enjoy.

#### 2 Introduction

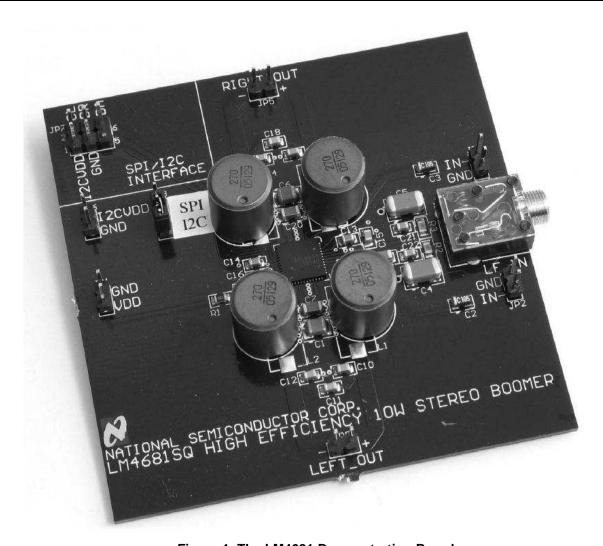

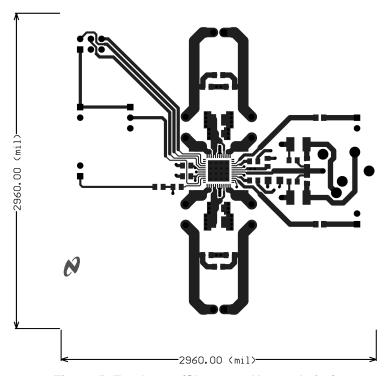

To help you investigate and evaluate the LM4681's performance and capabilities, a fully populated demonstration board is available from the Audio Products Group. This board is shown in Figure 1. Connected to an external power supply, a signal source and an I<sup>2</sup>C or SPI controller (or signal source), the LM4681 demonstration board easily demonstrates the amplifier's features.

TEXAS INSTRUMENTS

General Description www.ti.com

Figure 1. The LM4681 Demonstration Board

#### 3 General Description

The LM4681 is a Class D audio amplifier with an internal, digitally controlled volume control, and Class AB stereo headphone amplifier. The LM4681 is optimized to operate over a power supply voltage range of 9.0V to 15.5V. This amplifier is capable of delivering  $10W_{\text{RMS}}$  per channel into an  $8\Omega$  load at 10% THD when powered by a 14.0V power supply.

Boomer audio power amplifiers were designed specifically to provide high quality output power with a minimal amount of external components. The LM4681 is a high-efficiency Class D amplifier that is optimally suited for volume minimized design such as flat panel displays that can not tolerate heat sinks or portable system that must maximize battery life while producing high acoustic output.

The LM4681 includes a digitally controlled (I<sup>2</sup>C) 32–step volume control that optimizes system cost and minimizes PCB area.

The LM4681 features a shutdown mode for micropower dissipation, an internal thermal shutdown protection mechanism, and output stage fault detect and current limit protection.

#### 4 Operating Conditions

- Temperature Range –40°C ≤ T<sub>A</sub> ≤ 85°C

- Amplifier Power Supply Voltage 9.0V ≤ V<sub>DD</sub> ≤ 15.5V

www.ti.com Board Features

#### 5 Board Features

The LM4681 demonstration board has all of the necessary connections, using 100mil headers, to apply the power supply voltage, the audio input signals, and the I<sup>2</sup>C signal inputs. The Class D amplifier's output is available on 100 mil headers. The Class AB headphone's amplified audio signal is available on both a stereo headphone jack and 100 mil headers.

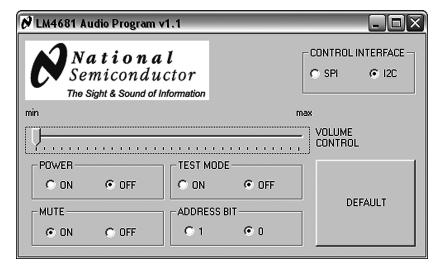

Also included with the demonstration board is an I<sup>2</sup>C signal generation board and software. With this board and the software, you can easily control the LM4681's shutdown function and stereo volume control. Figure 3 shows the software's graphical user interface (GUI).

#### 6 Schematic

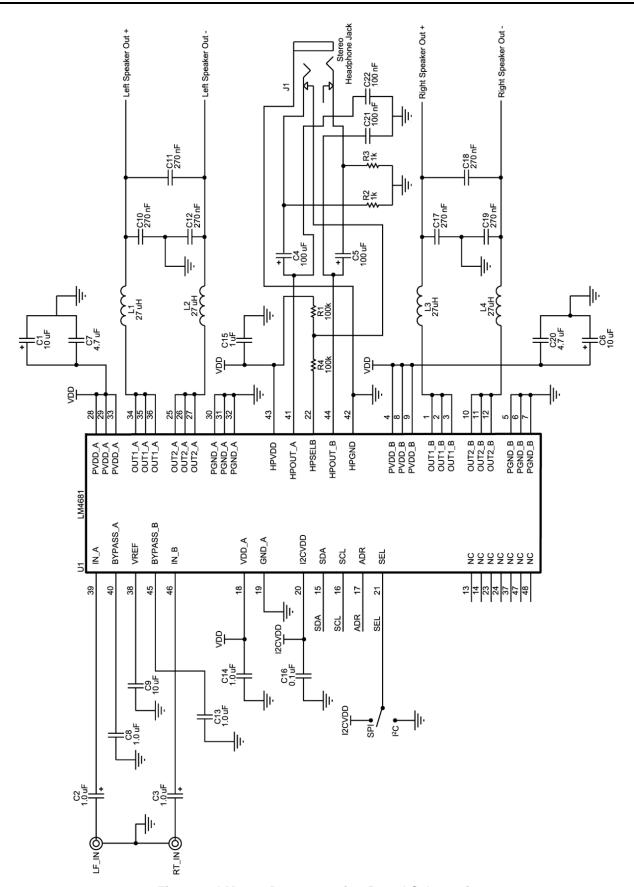

Figure 2 shows the LM4681 demonstration board schematic. For a list of the connections and their functions, see Table 1.

TEXAS INSTRUMENTS

Schematic www.ti.com

Figure 2. LM4681 Demonstration Board Schematic

www.ti.com Connections

#### 7 Connections

Connecting to the world is accomplished through the 100mil headers on the LM4681 demonstration board. The functions of the different headers are detailed in Table 1.

Table 1. LM4681 Demonstration Board Connections

| Jumper Designation | Function or Use                                                                                                                                                                                                                                                                                                    |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JP1                | Power supply connection. Connect an external power supply's positive voltage source to the JP1 pin labeled "VDD" and the supply's ground source to the pin labeled "GND."                                                                                                                                          |

| JP2                | This is the connection to the amplifier's input A (labeled as the "LF_IN" input on the demonstration board). Apply an external signal source's positive voltage to the JP2 pin labeled "IN" and the signal source's ground reference to the pin labeled "GND."                                                     |

| JP3                | This is the connection to the amplifier's output A (labeled as the "LEFT_OUT" output on the demonstration board). Connect the JP3 pin labeled "+" to the positive input of an external signal measurement device. Connect the JP3 pin labeled "-" to the negative input of an external signal measurement device.  |

| JP4                | This is the connection to the amplifier's input B (labeled as the "RT_IN" input on the demonstration board). Apply an external signal source's positive voltage to the JP4 pin labeled "IN" and the signal source's ground reference to the pin labeled "GND."                                                     |

| JP5                | This is the connection to the amplifier's output B (labeled as the "RIGHT_OUT" output on the demonstration board). Connect the JP5 pin labeled "+" to the positive input of an external signal measurement device. Connect the JP5 pin labeled "-" to the negative input of an external signal measurement device. |

| JP6                | If an external I <sup>2</sup> C power supply voltage is used, connect this supply's positive voltage source to the JP6 pin labeled "I2CVDD" and the supply's ground source to the pin labeled "GND." If no external supply is used, leave this jumper's pins unconnected.                                          |

| JP7                | This header is used for the I <sup>2</sup> C signal inputs. JP7-pin 1 is for an I <sup>2</sup> CV <sub>DD</sub> that is generated by the I <sup>2</sup> C signal source, JP7-pin 2 is for the SCL signal, JP7-pin 3 is for GND, JP7-pin 4 is for the ADR signal, and JP7-pin 6 is for the SDA signal.              |

| JP8                | This three-pin jumper selects either I <sup>2</sup> C or SPI digital interface protocol. Short pins 1 and 2 together SPI protocol is used. Short pins 2 and 3 together when I <sup>2</sup> C protocol is used.                                                                                                     |

### 8 Power Supply Sequencing

The LM4681 uses two power supply voltage:  $V_{DD}$  for the Class D power amplifier and the Class AB headphone amplifier and  $I^2CV_{DD}$  for the digital controls (volume, shutdown, etc.). To ensure proper functionality, apply  $I^2CV_{DD}$  first, followed by  $V_{DD}$ . The part will power-up with shutdown active, the volume control set to minimum, and mute active.

#### 9 I<sup>2</sup>C Signal Generation Board and Software

The I<sup>2</sup>C signal generation and interface board, along with the LM4681 software, will generate the address byte and the data byte used in the I<sup>2</sup>C control data transaction. To use the I<sup>2</sup>C signal generation and interface board, please plug it into a PC's parallel port (on either a notebook or a desktop computer).

The software comes with an installer. To install, unzip the file titled "LM4681\_Software\_ver1-1." After the file unzips, double-click the "setup.exe" file. After it launches, please follow the installer's instructions. Setup will create a folder named "LM4681" in the "Program" folder on the "C" disk (if the default is used) along with a shortcut of the same name in the "Programs" folder in the "Start" menu.

Figure 3. The LM4681 Demonstration Board Schematic

The LM4681 program includes controls for the amplifier's volume control, shutdown, mute, and which serial interface (I2C or SPI) is used. The control program's on-screen user interface is shown in Figure 3.

The **DEFAULT** button is used to return the LM4681 to its power-on reset state (minimum volume setting, mute on, and shutdown on).

The LM4681's stereo **VOLUME CONTROL** has 32 steps and a gain range of –48dB to +30dB (Class D) or –65dB to +13dB (Class AB headphone). It is controlled using the slider located at the top of the program's window. Each time the slider is moved from one tick mark to another, the program updates the amplifier's volume control.

The **POWER** control has two radio buttons. When OFF is selected, the LM4681 is placed in micropower shutdown. When ON is selected, the LM4681 is fully operational.

Use the program's **MUTE** section to mute the amplifier's output (Class D and AB headphone simultaneously). Mute ON mutes the amplifier outputs. Mute OFF unmutes the amplifier outputs and returns the output signal level to that set by the VOLUME CONTROL.

The last section of the software's interface is the **ADDRESS BIT**. This bit can be set to 1 or 0. The software will force the I<sup>2</sup>C interface board to apply a logic low or logic high to the LM4681's ADR pin according to the radio button that is selected. The LM4681 will respond to either of the addresses selected in the software's Address Bit control.

#### 10 PCB Layout Guidelines

This section provides general practical guidelines for PCB layouts that use various power and ground traces. Designers should note that these are only "rule-of-thumb" recommendations and the actual results are predicated on the final layout.

#### 10.1 Power and Ground Circuits

Star trace routing techniques (returning individual traces back to a central point rather than daisy chaining traces together in a serial manner) can have a major positive impact on low-level signal performance. Star trace routing refers to using individual traces that radiate from a signal point to feed power and ground to each circuit or even device. This technique may require greater design time, but should not increase the final price of the board.

www.ti.com Bill of Materials (BOM)

## 10.2 Avoiding Typical Design/Layout Problems

Avoid ground loops or running digital and analog traces parallel to each other (side-by-side) on the same PCB layer. When traces must cross over each other, do so at 90°. Running digital and analog traces at 90° to each other from the top to the bottom side as much as possible will minimize capacitive noise coupling and crosstalk.

## 11 Bill of Materials (BOM)

Table 2. Bill of Materials (BOM)

| Designator | Description Package                 |                               | Value (1) | Notes         |  |

|------------|-------------------------------------|-------------------------------|-----------|---------------|--|

| C1         | Polarized Capacitor (Surface Mount) | CC3225-1210 (Surface Mount)   | 10µF      | 25V, Tantalum |  |

| C2         | Polarized Capacitor (Surface Mount) | CC2012-0805 (Surface Mount)   | 1.0µF     | 10V, Tantalum |  |

| C3         | Polarized Capacitor (Surface Mount) | CC2012-0805 (Surface Mount)   | 1.0µF     | 10V, Tantalum |  |

| C4         | Polarized Capacitor (Surface Mount) | CC4532–1812 (Surface Mount)   | 100µF     | 10V, Tantalum |  |

| C5         | Polarized Capacitor (Surface Mount) | CC4532–1812 (Surface Mount)   | 100µF     | 10V, Tantalum |  |

| C6         | Polarized Capacitor (Surface Mount) | CC3225-1210 (Surface Mount)   | 10µF      | 25V, Tantalum |  |

| C7         | Capacitor                           | CC3216-1206 (Surface Mount)   | 4.7µF     | 50V, Ceramic  |  |

| C8         | Capacitor                           | CC2013-0805 (Surface Mount)   | 1.0µF     | 50V, Ceramic  |  |

| C9         | Capacitor                           | CC3216-1206 (Surface Mount)   | 10µF      | 10V, Tantalum |  |

| C10        | Capacitor                           | CC2013-0805 (Surface Mount)   | 270nF     | 50V, Ceramic  |  |

| C11        | Capacitor                           | CC2013-0805 (Surface Mount)   | 270nF     | 50V, Ceramic  |  |

| C12        | Capacitor                           | CC2013-0805 (Surface Mount)   | 270nF     | 50V, Ceramic  |  |

| C13        | Capacitor                           | CC2013-0805 (Surface Mount)   | 1.0µF     | 50V, Ceramic  |  |

| C14        | Capacitor                           | CC2013-0805 (Surface Mount)   | 1.0µF     | 50V, Ceramic  |  |

| C15        | Capacitor                           | CC2013-0805 (Surface Mount)   | 1µF       | 50V, Ceramic  |  |

| C16        | Capacitor                           | CC2013-0805 (Surface Mount)   | 0.1µF     | 50V, Ceramic  |  |

| C17        | Capacitor                           | CC2013-0805 (Surface Mount)   | 270nF     | 50V, Ceramic  |  |

| C18        | Capacitor                           | CC2013-0805 (Surface Mount)   | 270nF     | 50V, Ceramic  |  |

| C19        | Capacitor                           | CC2013-0805 (Surface Mount)   | 270nF     | 50V, Ceramic  |  |

| C20        | Capacitor                           | CC3216-1206 (Surface Mount)   | 4.7µF     | 50V, Ceramic  |  |

| C21        | Capacitor                           | CC2013-0805 (Surface Mount)   | 100nF     | 50V, Ceramic  |  |

| C22        | Capacitor                           | CC2013-0805 (Surface Mount)   | 100nF     | 50V, Ceramic  |  |

| J1         | 3-Conductor Headphone Jack          | STEREO HEADPHONE JACK (3.5MM) |           |               |  |

| JP1        | Header, 2-Pin                       | HDR1X2                        |           |               |  |

| JP2        | Header, 2-Pin                       | HDR1X2                        |           |               |  |

| JP3        | Header, 2-Pin                       | HDR1X2                        |           |               |  |

| JP4        | Header, 2-Pin                       | HDR1X2                        |           |               |  |

| JP5        | Header, 2-Pin                       | HDR1X2                        |           |               |  |

| JP6        | Header, 2-Pin                       | HDR1X2                        |           |               |  |

| JP7        | Header, 3-Pin, Dual row             | HDR2X3                        |           |               |  |

| JP8        | Header, 3-Pin                       | HDR1X3                        |           |               |  |

| L1         | Inductor                            | SMT_INDUCTOR                  | 27nH      |               |  |

| L2         | Inductor                            | SMT_INDUCTOR                  | 27nH      |               |  |

| L3         | Inductor                            | SMT_INDUCTOR                  | 27nH      |               |  |

| L4         | Inductor                            | SMT_INDUCTOR                  | 27nH      |               |  |

| R1         | Resistor                            | CC2013-0805                   | 100k      | 5%            |  |

| R2         | Resistor                            | CC2013-0805                   | 1k        | 5%            |  |

| R3         | Resistor                            | CC2013-0805                   | 1k        | 5%            |  |

|            | 1                                   | 4                             | 1         | 1             |  |

<sup>(1)</sup> Capacitor values in µF

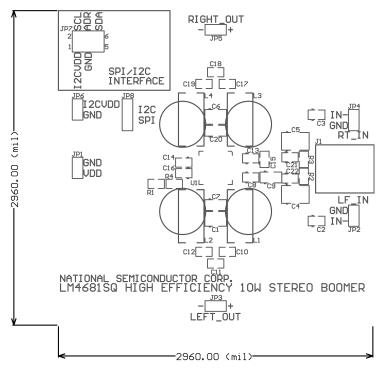

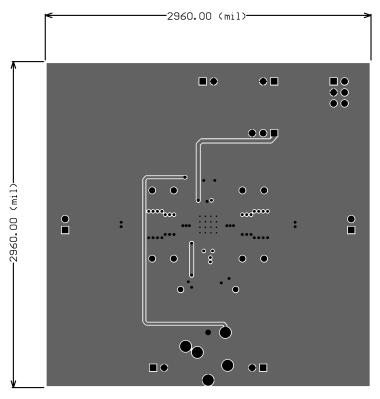

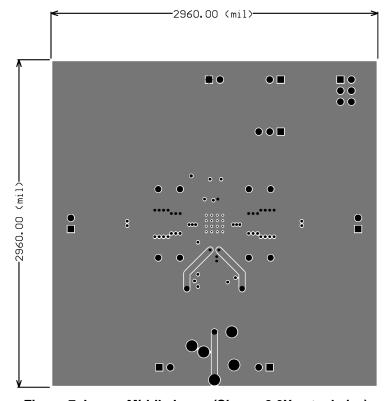

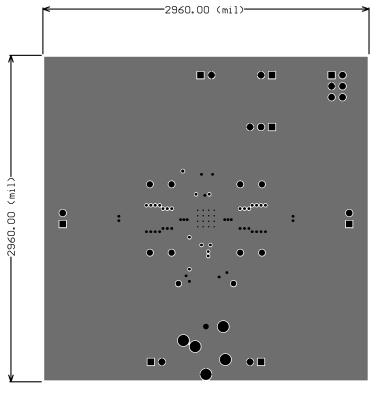

### 12 Demonstration Board PCB Layout

Figure 4 through Figure 8 show the different layers used to create the LM4681 four-layer demonstration board. Figure 4 is the silkscreen that shows parts location. Figure 5 is the top layer. Figure 6 is the upper inner layer. Figure 7 is the lower inner layer. Figure 8 is the bottom layer.

Figure 4. Top Silkscreen (Shown 2.6X actual size)

Figure 5. Top Layer (Shown 2.6X actual size)

Figure 6. Upper Middle Layer (Shown 2.6X actual size)

Figure 7. Lower Middle Layer (Shown 2.6X actual size)

Figure 8. Bottom Layer (Shown 2.6X actual size)

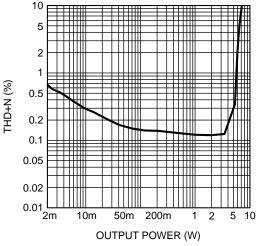

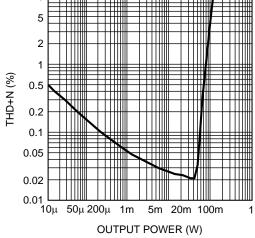

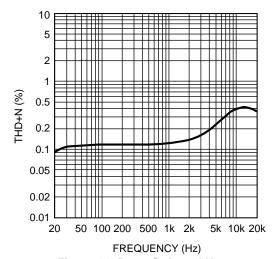

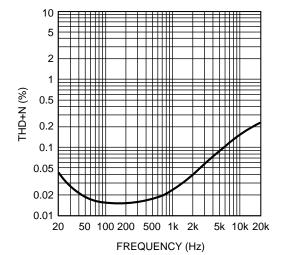

## 13 Typical Demonstration Board Audio Performance (C-CUPL Mode)

Typical Class D power amplifier and Class AB headphone amplifier THD+N versus Output Power performance curves at  $V_{DD}$  = 12V, are shown in Figure 9 and Figure 10, respectively. Typical Class D power amplifier and Class AB headphone amplifier mode THD+N versus Frequency performance curves at  $V_{DD}$  = 12V are shown in Figure 11 and Figure 12, respectively.

Figure 9. R<sub>L</sub> =  $8\Omega$ ,  $f_{\rm IN}$  = 1kHz,  $V_{\rm DD}$  = 12V Class D Amplifier THD+N vs Output Power

Figure 10.  $R_L$  = 32 $\Omega$ ,  $f_{IN}$  = 1kHz,  $V_{DD}$  = 12V Class AB Headphone Amplifier, THD+N vs Output Power

Figure 11.  $R_L = 8\Omega$ ,  $f_{\rm IN} = 1 {\rm kHz}$   $V_{\rm DD} = 12 {\rm V}$ ,  $P_{\rm O} = 1 {\rm W}$ Class D Amplifier HD+N vs Frequency

Figure 12.  $R_L$  = 32 $\Omega$ ,  $f_{IN}$  = 1kHz  $V_{DD}$  = 12V,  $P_O$  = 20mW Class AB Headphone Amplifier, THD+N vs Frequency

## 14 Revision History

| Rev | Date     | Description          |  |  |

|-----|----------|----------------------|--|--|

| 1.0 | 05/26/06 | Initial WEB release. |  |  |

www.ti.com

## Appendix A LM4681 I2C/SPI Control Register

Table 3 shows the actions that are implemented by manipulating the bits within the two internal  $I^2C$  control registers.

Table 3. LM4681 I<sup>2</sup>C/SPI Control Register Addressing and Data Format Chart

|                          | B7 | В6 | B5 | B4 | В3 | B2 | B1                  | В0                      |

|--------------------------|----|----|----|----|----|----|---------------------|-------------------------|

| I <sup>2</sup> C Address | 1  | 1  | 0  | 1  | 1  | 0  | ADR                 | 0                       |

| Mode Control Register    | 0  | Х  | 0  | Х  | Х  | X  | 0<br>Mute<br>Active | 0<br>Shutdown<br>Active |

| Volume Control Register  | 1  | 0  | 0  | V4 | V3 | V2 | V1                  | V0                      |

www.ti.com

## **Appendix B Volume Control Settings Binary Values**

The minimum volume setting is set to –64.94 (H.P. output) or –48.03 (Class D output) when 00000 is loaded into the volume control register. Incrementing the volume control register in binary fashion increases the volume control setting, reaching full scale at 11111. Table 4 shows the value of the gain for each of the 32 binary volume control settings.

Table 4. Binary Values for the Different Volume Control Gain Settings

| Gain (dB)  |                 |       |       |       |       |       |

|------------|-----------------|-------|-------|-------|-------|-------|

| HP Outputs | Class D Outputs | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| -64.94     | -48.03          | 0     | 0     | 0     | 0     | 0     |

| -64.94     | -48.03          | 0     | 0     | 0     | 0     | 1     |

| -56.94     | -36.03          | 0     | 0     | 0     | 1     | 0     |

| -47.94     | -31.03          | 0     | 0     | 0     | 1     | 1     |

| -42.94     | -26.03          | 0     | 0     | 1     | 0     | 0     |

| -37.94     | -21.03          | 0     | 0     | 1     | 0     | 1     |

| -33.94     | -17.03          | 0     | 0     | 1     | 1     | 0     |

| -31.94     | -15.03          | 0     | 0     | 1     | 1     | 1     |

| -28.94     | -12.03          | 0     | 1     | 0     | 0     | 0     |

| -25.94     | -9.03           | 0     | 1     | 0     | 0     | 1     |

| -22.94     | -6.03           | 0     | 1     | 0     | 1     | 0     |

| -20.94     | -4.03           | 0     | 1     | 0     | 1     | 1     |

| -18.94     | -2.03           | 0     | 1     | 1     | 0     | 0     |

| -16.94     | -0.03           | 0     | 1     | 1     | 0     | 1     |

| -14.94     | 1.97            | 0     | 1     | 1     | 1     | 0     |

| -12.94     | 3.97            | 0     | 1     | 1     | 1     | 1     |

| -10.94     | 5.97            | 1     | 0     | 0     | 0     | 0     |

| -8.94      | 7.97            | 1     | 0     | 0     | 0     | 1     |

| -6.94      | 9.97            | 1     | 0     | 0     | 1     | 0     |

| -4.94      | 11.97           | 1     | 0     | 0     | 1     | 1     |

| -2.94      | 13.97           | 1     | 0     | 1     | 0     | 0     |

| -0.94      | 15.97           | 1     | 0     | 1     | 0     | 1     |

| 1.06       | 17.97           | 1     | 0     | 1     | 1     | 0     |

| 3.06       | 19.97           | 1     | 0     | 1     | 1     | 1     |

| 6.06       | 22.97           | 1     | 1     | 0     | 0     | 0     |

| 7.07       | 23.97           | 1     | 1     | 0     | 0     | 1     |

| 8.06       | 24.97           | 1     | 1     | 0     | 1     | 0     |

| 9.06       | 25.97           | 1     | 1     | 0     | 1     | 1     |

| 10.06      | 26.97           | 1     | 1     | 1     | 0     | 0     |

| 11.06      | 27.97           | 1     | 1     | 1     | 0     | 1     |

| 12.06      | 28.97           | 1     | 1     | 1     | 1     | 0     |

| 13.06      | 29.97           | 1     | 1     | 1     | 1     | 1     |

www.ti.com

# Appendix C LLP Package, PCB, Layout, and Mounting Considerations

For more information on Leadless Leadframe Package (LLP), see AN-1187 Leadless Leadframe Package (LLP) (SNOA401)

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors <u>www.ti.com/omap</u> TI E2E Community <u>e2e.ti.com</u>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>