## AN-1558 Clocking High-Speed A/D Converters

### ABSTRACT

Extremely high-speed ADCs (>1 GSPS) demand a low-jitter sample clock in order to preserve signal-tonoise ratio (SNR). These 8- and 10-bit converters have best-case noise floors set by quantization noise. For an N-bit ADC sampling a full-scale sinusoid, the well known expression for SNR (in dB) is: SNR = 6.02N + 1.76. This sets the best case noise floor for an 8-bit ADC at -49.9 dBc. The noise floor degrades from this point due to factors such as jitter on the sample clock, intrinsic aperture jitter of the ADC, spurious components arising from non-linearities in the ADC quantizer, and other internal noise such as thermal noise. In this article, we look at the strategy for optimizing the performance of the sample clock based on PLL/VCO characteristics. This means minimizing overall integrated phase noise, which minimizes clock jitter.

### Contents

| 1 | Overview                                              | 2 |

|---|-------------------------------------------------------|---|

| 2 | References                                            | 5 |

|   | List of Figures                                       |   |

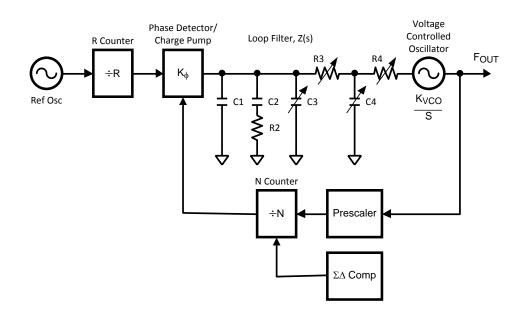

| 1 | LMX2531LQ1500E Block Diagram                          | 3 |

| 2 | Single-Sided Phase Noise Plot of a 1.5 GHz ADC Clock  | 4 |

|   | List of Tables                                        |   |

| 1 | Jitter SNR and Allowable Clock Jitter. With Total SNR | 2 |

| • |                                |   |

|---|--------------------------------|---|

| 2 | Noise Transfer Functions, T(f) | 3 |

WEBENCH is a registered trademark of Texas Instruments. All other trademarks are the property of their respective owners.

cult to achieve at a reasonable cost. However, achieving RMS clock jitter below 500 fs is possible using TI's LMX2531LQ1500E frequency synthesizer combined with a high quality crystal reference oscillator. The LMX2531LQ1500E is shown in Figure 1.

The aperture jitter specification for Texas Instruments ADC08D1500 8-bit, 1.5 GSPS converter is 400 femtoseconds (fs.). Using this value and a maximum input frequency of 748 MHz ( $f_{IN}$ ), Table 1 lists the allowable sample clock jitter for target SNR due to total jitter.

### Table 1. Jitter SNR and Allowable Clock Jitter, With Total SNR

|                                                                 |                              | Total SNR Due to Quantization Noise and Jitter (dB)                                                                            |  |

|-----------------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| Target Jitter SNR (dB)<br>(Aperture Jitter and Clock<br>Jitter) | Allowable Clock Jitter (fs.) | $SNR = 10 \log \left( \frac{\frac{1}{\frac{1}{10} + \frac{1}{\frac{SNR_{y}}{10}}} + \frac{1}{\frac{SNR_{Q}}{10}} \right) $ (4) |  |

| 54                                                              | 142                          | 48.5                                                                                                                           |  |

| 53                                                              | 259                          | 48.2                                                                                                                           |  |

| 52                                                              | 354                          | 47.8                                                                                                                           |  |

| 51                                                              | 447                          | 47.4                                                                                                                           |  |

| 50                                                              | 541                          | 46.9                                                                                                                           |  |

| 49                                                              | 640                          | 46.4                                                                                                                           |  |

| 48                                                              | 747                          | 45.8                                                                                                                           |  |

| 47                                                              | 862                          | 45.2                                                                                                                           |  |

| 46                                                              | 989                          | 44.5                                                                                                                           |  |

The root-mean-square (RMS) jitter of the sample clock combines with the intrinsic RMS aperture jitter of

The SNR due to total jitter is:

# $SNR_{dB} = 20 \cdot \log\left(\frac{1}{2\pi f_{in}\sigma_{T}}\right) = 20 \cdot \log\left(\frac{1}{2\pi f_{in}\sqrt{\sigma_{Cik}^{2} + \sigma_{aperture}^{2}}}\right)$

the ADC in a root-sum-square fashion to produce a total affective jitter. Total RMS jitter is:

Solving for the maximum allowable clock jitter given some target SNR and ADC aperture jitter:

| 46                                                  | 989 | 44.5                                                   |

|-----------------------------------------------------|-----|--------------------------------------------------------|

| The third column of Table ADC, using a quantization |     | R due to quantization noise and jitter for an 8-bit    |

| •                                                   | , , | otal SNR that is close to 49.9 dB is extremely diffice |

RUMENTS

(1)

(2)

(3)

**FEXAS**

2

Overview

**Overview**

$\sigma_{\rm T} = \sqrt{\sigma^2_{\rm Clk} + \sigma^2_{\rm aperture}}$

$\sigma_{\text{Cik}} = \sqrt{\frac{1}{(2\pi f_{\text{n}})^2 \bullet 10}} - \sigma^2_{\text{aperture}}$

1

www.ti.com

### Figure 1. LMX2531LQ1500E Block Diagram

For this example, use the LMX2531LQ1500E to generate a fixed 1.5 GHz sample clock that can drive any of TI's GSPS ADCs. Because the ADC clock is fixed, you can design the loop filter to achieve optimized phase noise performance, giving best jitter performance. Each functional block in Figure 1 contributes some form of noise. Table 2 lists the low and high frequency approximations for their noise transfer functions.

| Table 2. N | Noise Transfer | Functions, | T(f) |

|------------|----------------|------------|------|

|------------|----------------|------------|------|

| Noise Source         | Low Frequency Transfer Function<br>Approximation | High Frequency Transfer Function<br>Approximation |

|----------------------|--------------------------------------------------|---------------------------------------------------|

| Reference Oscillator | N/R                                              | G(s)                                              |

| R Divider            | N                                                | G(s)                                              |

| N Divider            | N                                                | G(s)                                              |

| Phase Detector       | Ν/ΚΦ                                             | G(s)                                              |

G(s) is the forward transfer function:

$$G(s) = \frac{K_{\phi} \bullet K_{VCO} \bullet Z(s)}{s}$$

Optimizing the PLL noise bandwidth means minimizing the following integral for each noise path through

$\int_{f^1}^{f^2} \mathbf{S}_{\mathsf{N}}(f) \cdot |\mathsf{T}(f)|^2 \, \mathrm{d}f$

the PLL:

(6)

3

(5)

Overview

www.ti.com

Sn(f) represents the specific noise source PSD and T(f) the noise transfer function. Using the approximations for T(f) from Table 2 gives us guidance for choosing the PLL parameters that optimize noise performance:

- Maximize the phase comparator charge pump gain (Kf) to minimize the noise contribution of the phase detector (up to a point).

- The N-divider and R-divider noise contributions are proportional to the value of N2. Choose a phase comparator frequency that results in the smallest possible integer value for N, subject to the maximum phase detector frequency.

- Choose a low noise reference oscillator at the compare frequency, or an integer multiple of the compare frequency. A multiple of the compare frequency provides additional benefit by reducing reference noise.

- Designing the loop filter to have a phase margin of approximately 80 degrees flattens its response and suppresses VCO noise near the loop bandwidth.

The final task is to design the loop transfer function T(f) subject to minimizing Equation 6 for each noise source, which is extremely difficult without the aid of automated tools. TI's Web-based design environment WEBENCH® features its EasyPLL tool that assists the user in selecting a PLL/VCO, entering design parameters, selecting loop components, and running simulations to test the design.

Using EasyPLL, a 1.5 GHz sample clock was designed using the LMX2531LQ1500E and a 60 MHz crystal oscillator as a reference, with the following final design parameters:

- $F_{OSC} = 60$  MHz, with phase noise = -158 dBc at 10 kHz offset.

- Compare frequency = 30 MHz, R = 2, N = 50

- 2nd order loop filter, C1= 220 pF, C2 = 150 nF, R2 = 1.0 kΩ, C3=C4=R3=R4=0.

- Loop bandwidth = 22.85 kHz

- K<sub>φ</sub> = 1.26 mA

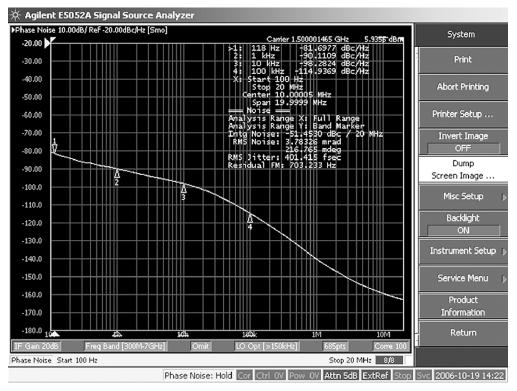

These values resulted in a clock with only 401 fs of jitter (100 Hz to 20 MHz bandwidth).

Figure 2 shows the single-sideband phase noise plot of the clock.

Figure 2. Single-Sided Phase Noise Plot of a 1.5 GHz ADC Clock

4

www.ti.com

### References

### 2 References

Dean Banerjee, *PLL Performance: Simulation and Design,* 4th Edition, Dogear Publishing, Indianapolis, 2006.

### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                                 | Applications                  |                                   |

|------------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com                | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com                    | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com                 |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconnectivity |                               |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated