A 100-MS/s 8-b CMOS Subranging ADC with Sustained Parametric Performance from 3.8V Down (Part Two of Two)

Literature Number: SNAA104

# **Technology Edge**

Copyright © 2001 IEEE. Reprinted from IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 36, NO. 3, MARCH 2001. This material is posted here with permission of the IEEE. Such permission of the IEEE does not in any way imply IEEE endorsement of any of National Semiconductor's products or services Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by sending a blank email message to pubs-permissions@ieee.org. By choosing to view this document, you agree to all provisions of the copyright laws protecting it.

#### **Note:** This is Part Two of Two (Continued from June 2001 Edition)

A 100-MS/s 8-b CMOS Subranging ADC with Sustained Parametric Performance from 3.8V Down to 2.2V (Robert C. Taft and Maria Rosaria Tursi, Data Conversion Systems)

Abstract-A 100-MS/s 8-b CMOS analog-to-digital converter (ADC) designed for very low supply voltage and power dissipation is presented. This single-ended-input ADC is based on the unified two-step subranging architecture, which processes the coarse and fine decisions in identical signal paths to maximize their matching. However, to minimize power and area, the coarse-to-fine overlap correction has been aggressively reduced to only one LSB. The ADC incorporates five established design techniques to maximize performance: bottom-plate sampling, distributed sampling, auto-zeroing, interpolation, and interleaving. Very low voltage operation required for a general purpose ADC was obtained with four additional and new circuit techniques. These are a dual-gain first-stage amplifier, differential T-gate boosting, a supply independent delay generator, and a digital delay-locked-loop controlled output driver. For a clock rate of 100 MS/s, 7.0 (7.3) effective bits for a 50 MHz (10 MHz) input are maintained from 3.8 V down to 2.2 V. At 2.2 V, this 100-MS/s converter dissipates 75 mW plus 9 mW for the reference ladder. For a typical supply of 2.7 V, it consumes just 1 mW per MS/s over the 10-160-MS/s clock frequency range. Differential nonlinearity below 0.5 LSB is maintained from 2.7 V down to 2.2 V, and it degrades only slightly to 0.8 LSB at 3.8-V supply. The converter is implemented in a 0.35-mm CMOS process, with double-poly capacitors and no low-threshold devices.

Index Terms-Analog-to-digital converters, CMOS analog integrated circuits, Nyquist converters, subranging A/D converters, switched capacitor circuits, two-step A/D converters.

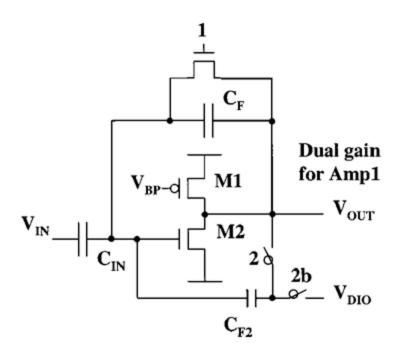

Fig. 5. Amp 1, a common-source nMOS , M2, with a pMOS current load, M1. Shown is feedback capacitor CF in addition to input capacitor, CIN. During phase 2, CF2 is used to reduce the gain of the amplifier, to enhance its linearity and bandwidth.

# V. DUAL-GAIN AMP1

Interpolation between largely varying input voltages at the input of amp 2 stress the linearity requirements of amp 1 during the coarse amplify in phase 2. Thus, errors can exceed one LSB for the matching of the coarse- and fine-compare results, especially at low supply. Since this exceeds the error budget, the lin-earity of amp 1 and amp 2 during coarse amplify was improved. Making amp 1 dual-gain by switching in a second feedback capacitor during phase 2, as shown in Fig. 5, greatly alleviates this constraint. The lower gain during coarse amplify results in not only better linearity, but also higher bandwidth and faster settling. During fine amplify, the higher gain of amp 1 is beneficial in reducing all offset errors of amp 2, amp 3, and the comparator. As long as the coarse-compare is within one LSB of the correct answer, the fine-compare fully determines the performance of the converter. Thus, since the fine amplifiers have a lower bandwidth and need accurate results, the settling time for the fine-amplify phase needed to be extended.

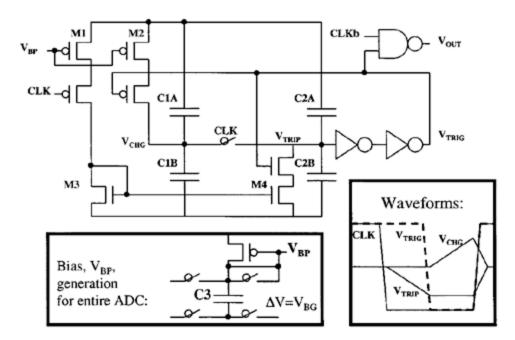

Fig. 6. Process, temperature, and supply independent delay generator used to generate a clock 1/4 period, to extend the length of phase 4. Key waveforms are plotted, and an approximate description of the bias generator for VBP is given.

#### VI. NON-DLL CLOCK-PERIOD DIVIDER

The fine amplify phase 4 is extended at the expense of phase 3, since the comparators regenerate very quickly. Even for the worst case, the comparators need only one-half of the clock high time for phase 3. A delay generator to halve the clock high time, preferably without the complexity of a delay-locked loop (DLL), was required. It needed to be not only process and supply insensitive, but also have the ability to adjust to large variations in ADC clock frequency. In Fig. 6, a very simple and robust period divider is shown along with the key waveforms required to create half a clock s low time (CLK is inverted as implemented). All capacitors are of equal value, and are connected between the supply rails for supply rejection. M4 discharges C2 when CLK goes low until it reaches the inverter trip point. At this point, VTRIG, the signal used to halve the CLK low time, is generated. For the remainder of CLK s low time, M2 charges up C1, with a charge transfer occurring from C1 to C2 when CLK goes high. This charge transfer returns C2 to its original voltage in preparation for the next CLK low. The delay is independent of the inverter trip point, depending only on the ratio of M1 to M2. With M1 and M2 equal, the CLK low time is halved.

The circuit has two vulnerabilities. First, if M1 exceeds three times the strength of M2, VTRIG will not lock and this will create large jitter. For all other ratios the circuit locks quickly and remains stable. Second, the voltage VTRIP could saturate due to variations in bias level VBP. This second problem is avoided by design, since the bias for the entire ADC is generated by a bandgap voltage applied across a capacitor matching the one used in the delay cell. The approximate schematic is given at the bottom of Fig. 6. Additional benefits of using this "switching" current generator are an ADC that reduces its quiescent power when operated below its maximum conversion rate and a more tightly controlled current. Over process, temperature, and voltage variations, resistors in CMOS processes generally have more variation in value than capacitors.

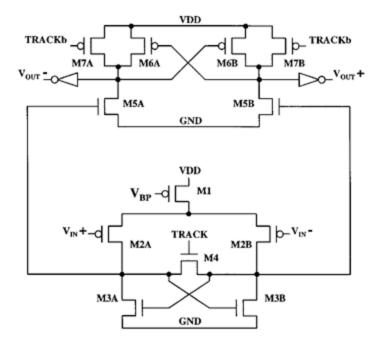

Fig. 7. The low-voltage low-offset comparator consists of two stages, the quiescent regenerator (below) and the dynamic level shifter (above).

# VII. LOW-VOLTAGE LOW-OFFSET COMPARATOR

One advantage of the 1.5-b-per-stage pipe architecture previously described in the introduction is that the comparator need not be very accurate. Later conversions can compensate for comparator offset errors made earlier in the pipe. For this and all flash-like converters, however, no such recovery exists, and a low-offset comparator is crucial. Fig. 7 shows a two-stage comparator, consisting of a guiescent regenerator followed by a dynamic level shifter. It is based on that of [8] and [9], but is lower voltage because the two-stage approach reduces the amount of device stacking. In addition, unlike in [8] and [9], clock signals TRACK and TRACKb can be simultaneous, reducing the complexity of the clock generation. Although the input and reference ladder are single-ended, the analog channel is actually pseudodifferential, with a reference channel consisting of amp 1, amp 2, and amp 3, which is not shown in Fig. 4. The input to the reference channel is a quiet ground, and the output of amp 3 is applied to the negative input of the regenerator, with the signal channel applied to the positive input. Input pair M2A and M2B, and cross-coupled M3A and M3B are large to minimize the offset of the regenerator. Further, M4 is small to reduce the dynamic offset errors resulting from an uneven TRACK clock coupling into both halves of the regenerator. Although the bias current set by VBP limits the slew-rate of the regenerator stage, only a small amount of regeneration is required to activate the level shifter, which rapidly generates CMOS logic levels.

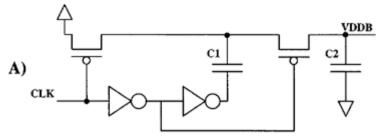

Conventional boost circuit

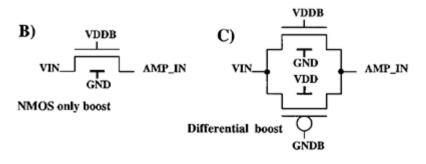

Fig. 8. (a) Conventional boost circuit. (b) nMOS-only T-gate.(c) Differential T-gate boosting with double back-bias effect used for this ADC.

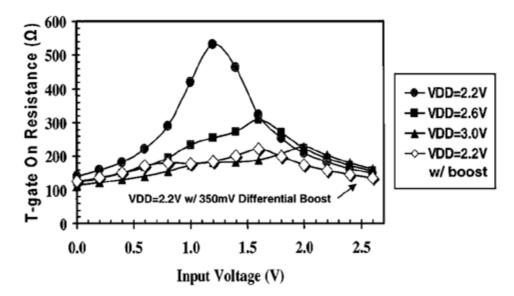

Fig. 9. Simulated T-gate on-resistance versus VIN for three supply voltages, 2.2, 2.6, and 3.0V. Note that the inclusion of a 350-mV differential boost for VDD=2.2V reduces the maximum RON and absolute RON variation more effectively than an 800-mV increase in supply voltage.

#### **VIII. DIFFERENTIAL T-GATE BOOSTING**

Fig. 8(a) shows a conventional boost generator, which can be used with an nMOS-only T-gate, Fig.

8(b). The nMOS-only transmission gate has been used with a dynamic boost voltage to obtain a constant VGs. This minimizes the variation of the input resistance, minimizing the distortion at high input frequencies.

The problem with the nMOS-only approach is the increased voltage stress, since the maximum supply and operating supply are converging for aggressive CMOS technologies. For an input voltage range which can lie anywhere between the supply rails, the nMOS-only approach is limited. Furthermore, the dynamic boost circuit is not well suited for distributed sampling.

The new approach is shown in Fig. 8(c). It uses a very small 350-mV differential boost voltages VDDB and GNDB. This requires a second, complementary boost circuit, as shown in Fig. 8(a), to generate the -350 mV below-ground boost voltage GNDB. Note that this approach minimizes the technology stress, since no transistor has both VDDB and GNDB applied to it. In addition, it has the added benefit of the body effect of the T-gate transistors, e.g., for the T-gate pMOS, a lower hard supply on the n-well results in a lower VBs, therefore a lower VTH. The same applies to the T-gate nMOS. Thus, at VDD = 2.2V, the reduction in T-gate on-resistance obtained with only the addition of 350-mV differential voltage stress is equivalent to increasing the supply voltage 800 mV without the use of differential T-gate boosting; see Fig. 9.

Because of the low controlled differential boost voltages of +/-350 mV, no special precaution or circuitry was required for routing these levels to the VIN T-gates. Therefore, these same boosted logic levels were used for all critical T-gates, including those in the analog MUX. This allowed the use of smaller T-gates for the same pass resistance, and therefore a substantial reduction in parasitic device capacitance.

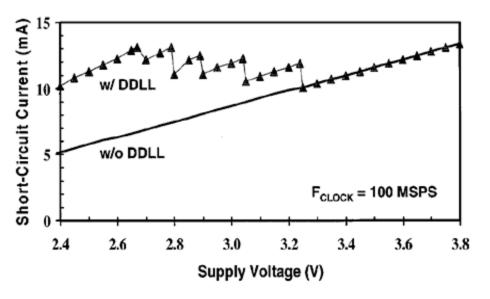

Fig. 10. Short-circuit output driver current versus supply with and without the digital delay lock-loop (DDLL) control active.

# **IX. DIGITAL DELAY-LOCK-LOOP OUTPUT DRIVER**

The variations in process and supply voltage present special challenges for the ADCs digital output driver design. At 100 MHz, capture of the ADCs digital output is not trivial. The output drivers must be strong enough to drive reasonable board loads (10 pF) in slow corners. In fast corners, however, they must be sufficiently weak to minimize digital noise from coupling back into the analog circuit. Sophisticated approaches using current source output drivers were rejected in this design because of the large required layout area. The approach here was to vary the output driver

strength from 3 to 11 parallel fingers, set by a DLL with a replica scaled output driver and an internal load capacitor of 2 pF. The resulting reduction in output driver strength variation at 100 MHz is nearly 3, as seen by plotting short-circuit current versus supply voltage, see Fig. 10. Note that not all transitions between m = 3 and 11 are seen, due to the need to lock the circuit on specific m values.

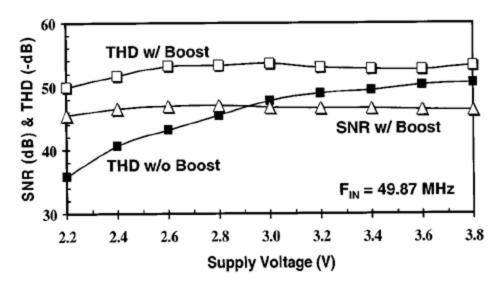

Fig. 11. Total harmonic distortion and signal-to-noise ratio at Nyquist versus supply voltage. As a comparison, the measured THD without using boosted supplies has been plotted.

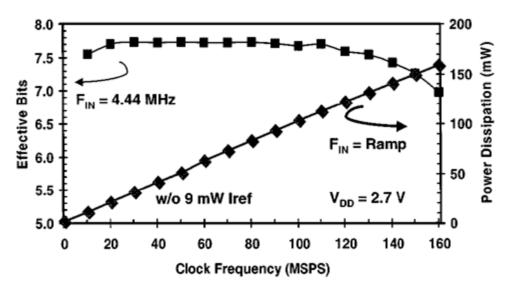

Fig. 12. Signal-to-noise and distortion (SINAD) expressed in effective bits, and total power dissipation for a ramp input, both versus clock frequency. The resistor reference power was omitted to show that the ADCs combined digital and analog power is proportional to  $F_{CLK}$ , at 1 mW/MHz. At  $F_{CLK} = 160$ MS/s, 7.0 effective bits are still maintained.

#### **X. EXPERIMENTAL RESULTS**

Fig. 11 shows the total harmonic distortion (THD) and signal-to-noise ratio (SNR) at Nyquist versus supply voltage, from 3.8 V down to 2.2 V. A VDD of 3.8 V just exceeds the maximum operating supply, especially with the addition of the 350-mV boost. However, it demonstrates the robustness of the circuit blocks. The effectiveness of the differential boost circuit is demonstrated by plotting the measured THD with the boost voltages replaced by the supplies. The effect of the switching bandgap current generator on power dissipation versus clock frequency is shown in Fig. 12. The power, at 1 mW per MS/s, is for a ramp input, and therefore does not include significant output driver current. This latter component is dominated by the capacitive load of the test board. Shown also is the signal-to-noise and distortion (SINAD) versus clock frequency for a video 4.44MHz - 0.5dBFS input. For converter rates of 10-160 MS/s, 7.0 effective bits are maintained.

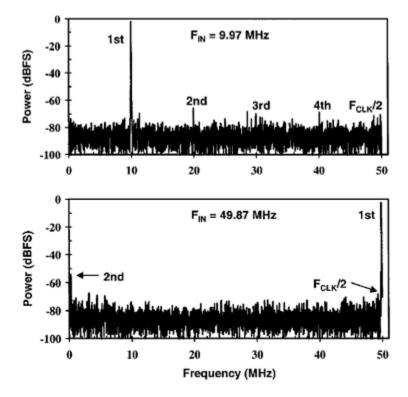

Fig. 13. FFT spectrum at 100 MS/s and 2.7 V, for FIN = 9.97 MHz (above) and FIN = 49.87 MHz (below). The spectrum is clean, and shows nearly no FCLK/2 component or FIN with FCLK mixing even at Nyquist.

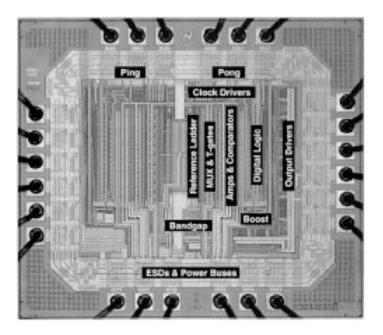

Fig. 14. Die photograph showing the location of key circuit blocks. Note the symmetry about the central polysilicon reference ladder, shared by both interleaved analog channels.

Spectrums for two different input frequencies, 10 and 50 MHz, are shown in Fig. 13. In both cases, no FCLK/2 components or with mixing is seen. This results from the good gain, offset, and timing matching of the two interleaved channels. For the 10-MHz spectrum, note the excellent third harmonic distortion of 67 dB, which plays an important role in communications. The second harmonic dominates due to the use a single-ended front end. A die photograph showing the location of key circuit blocks is shown in Fig. 14. The polysilicon reference ladder, in the center, is shared by both interleaved analog channels, indicated as "Ping" and "Pong." The digital circuits for the one LSB of MSB-to-LSB mismatch correction are indicated. Shown also are the boost capacitors used to the 350-mV differential boost, and the output drivers complete with their digital DLL control unit.

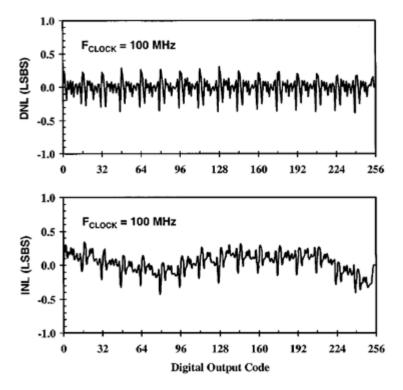

Fig. 15. Differential nonlinearity (above) and integral nonlinearity (below) at 2.7 V. The subranging architecture results in a small modulo  $2 \land (N/2) =$ 16 signature, due to the cyclical use of the  $2 \land$ (N/2) comparators to evaluate all  $2 \land N$  codes.

| VDD                              | 2.2 V                             | 2.7 V       | 3.8 V       |  |

|----------------------------------|-----------------------------------|-------------|-------------|--|

| ADC Clock (MSPS)                 | 100                               | 100         | 100         |  |

| Power w/o Ref. (mW)              | 75.2                              | 108.9       | 167.6       |  |

| Ladder Power (mW)                | 9.1                               | 9.1         | 9.1         |  |

| Max DNL (LSB)                    | -0.43/+0.40                       | -0.39/+0.30 | -0.51/+0.80 |  |

| Max INL (LSB)                    | -0.60/+0.41                       | -0.43/+0.34 | -0.58/+0.59 |  |

| THD (dB) @Fin=10MHz              | -51.1                             | -56.7       | -56.7       |  |

| SNR (dB)                         | 47.4                              | 48.2        | 46.7        |  |

| EffBits                          | 7.3                               | 7.6         | 7.4         |  |

| THD (dB) @Fin=50MHz              | -49.4                             | -55.8       | -52.5       |  |

| SNR (dB)                         | 45.2                              | 45.9        | 46.4        |  |

| EffBits                          | 7.0                               | 7.3         | 7.3         |  |

| Latency (cycles)                 | 2.5                               | 2.5         | 2.5         |  |

| Ladder Reference; VRB to VRT (V) | 0.3 to 1.9                        | 0.3 to 1.9  | 0.3 to 1.9  |  |

| Active area                      | 0.9 sq. mm                        |             |             |  |

| Die Area                         | 2.6 sq. mm                        |             |             |  |

| Technology                       | Lpoly=0.4um CMOS (2-poly,3-metal) |             |             |  |

|                                  | NO low Vt devices                 |             |             |  |

TABLE I ADC PERFORMANCE VERSUS SUPPLY VOLTAGE FROM 2.2 V UP TO 3.8 V

Fig. 15 shows the differential nonlinearity (DNL) and integral nonlinearity (INL) errors, again at 2.7

V. Both the maximum DNL and INL are about +/-0.4 LSB. Although the intent was to maintain parametric performance over a wide range of supply voltages, the ADC was optimized for a 2.7-V supply. Not all circuit blocks improve with increasing supply voltage. This is particularly true for DNL, where the contribution of charge-switch injection variation during the sampling phase cannot be auto-zeroed. The larger the supply, the larger the gate voltage above threshold for the sampling nMOS of Figs. 3 and 4, and the larger the injected charge and injected charge variation during sampling. This DNL effect is seen in Table I, which summarizes the ADC parametric results for three supply voltages. The converter actually maintains a DNL of +/-0.5 LSB down to 2.0 V, at which point its power consumption is only 60 mW.

## ACKNOWLEDGMENT

The authors wish to thank A. Glenny, D. Archer, B. Brandt, D. Boisvert, J. Lutsky, F. Bowman, J. Margolycz, and R. Cullen for technical assistance and discussions. The authors are very grateful to S. Dacy for proofreading and correcting early drafts. They are also very grateful for the technical support of DCS and the NSME, and for the management support of P. Holloway and P. Tucci.

## REFERENCES

[1] B. Razavi, *Principles of Data Conversion System Design*. New York: IEEE Press, 1995.

[2] T. B. Cho and P. R. Gray, "A 10-b 20-Msample/s 35-mW pipeline A/D converter," *IEEE J. Solid-State Circuits*, vol. 30, pp. 166-172, Mar. 1995.

[3] A. Dingwall and V. Zazzu, "An 8-MHz CMOS subranging 8-bit A/D converter," *IEEE J. Solid-State Circuits*, vol. 20, pp. 72-73, Dec. 1985.

[4] R. J. van de Plassche and R. E. J. van der Grift, "A high-speed 7-bit A/D converter," *IEEE J. Solid-State Circuits*, vol. 14, pp. 938-943, Dec. 1979.

[5] K. Bult, A. Buchwald, and J. Laskowski, "A 170-mW 10-b 50-Msample/s CMOS ADC in 1 mm ," in *ISSCC Dig. Tech. Papers*, Feb. 1997, pp. 136-137.

[6] S. Hosotani, T. Miki, A. Maeda, and N. Yazawa, "An 8-bit 20-MS/s CMOS A/D converter with 50-mW power consumption," *IEEE J. Solid-State Circuits*, vol. 25, pp. 167-172, Feb. 1990.

[7] K. Kusumoto *et al.*, "A 10-b 20-MHz 30-mW pipelined interpolating CMOS ADC," *IEEE J. Solid-State Circuits*, vol. 28, pp. 1200-1206, Dec. 1993.

[8] B. P. Brandt and J. Lutsky, "A 75-mW 10-b 209-MS/s CMOSsubranging ADC with 9.5 effective bits at Nyquist," *IEEE J. Solid-State Circuits*, vol. 34, pp. 1788-1953, Dec. 1999.

[9] G. Yin *et al.*, "A high-speed CMOS comparator with 8-b resolution," *IEEE J. Solid-State Circuits*, vol. 27, pp. 208-211, Feb. 1992.

**Robert C. Taft** (S 87-M 90-SM 96) was born in Vienna, Austria. He received the B.Sc. degree in mathematics and physics (Hon.) from the University of Victoria, Canada, in 1985, and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA. His thesis work focused on the germanium-silicon inversion-base transistor or BICFET structure. In 1990 he joined the APRDL division of Motorola and designed the bipolar transistor module for Mo-torola s 0.35um BiCMOS SRAM technology. His responsibilities broadened to include the 0.35um BiCMOS pilot baseline and to assisting the SRAM Memory Design group. In 1994, he joined East Coast Labs, an analog design startup company, now part of National Semiconductor. Since 1997 he has been working at the Munich, Germany, location of National Semiconductors on high-speed Nyquist data

converters.

**Maria Rosaria Tursi** (M 00) was born in Martina Franca, Taranto, Italy, in 1973. She received the degree in electronic engineering (*summa cum laude*) from the Politecnico of Bari, Italy, in 1999. Her thesis work focused on the design of digital output drivers for mixed-signal ICs. Since 1999, she has been with the ECL design group of National Semiconductor, Munich, Germany, where she is involved in the design of high-speed analog-to-digital converters in CMOS processes.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products               |                                 | Applications                  |                                   |

|------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                  | www.ti.com/audio                | Communications and Telecom    | www.ti.com/communications         |

| Amplifiers             | amplifier.ti.com                | Computers and Peripherals     | www.ti.com/computers              |

| Data Converters        | dataconverter.ti.com            | Consumer Electronics          | www.ti.com/consumer-apps          |

| DLP® Products          | www.dlp.com                     | Energy and Lighting           | www.ti.com/energy                 |

| DSP                    | dsp.ti.com                      | Industrial                    | www.ti.com/industrial             |

| Clocks and Timers      | www.ti.com/clocks               | Medical                       | www.ti.com/medical                |

| Interface              | interface.ti.com                | Security                      | www.ti.com/security               |

| Logic                  | logic.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Power Mgmt             | power.ti.com                    | Transportation and Automotive | www.ti.com/automotive             |

| Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                   | www.ti-rfid.com                 |                               |                                   |

| OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

| Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

|                        |                                 |                               | a O a Al a a m                    |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated