A 100-MS/s 8-b CMOS Subranging ADC with Sustained Parametric Performance from 3.8 V Down to 2.2 V (Part One of Two)

Literature Number: SNAA105

# **Technology Edge**

Copyright © 2001 IEEE. Reprinted from IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 36, NO. 3, MARCH 2001. This material is posted here with permission of the IEEE. Such permission of the IEEE does not in any way imply IEEE endorsement of any of National Semiconductor's products or services Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by sending a blank email message to pubs-permissions@ieee.org. By choosing to view this document, you agree to all provisions of the copyright laws protecting it.

## A 100-MS/s 8-b CMOS Subranging ADC with Sustained Parametric Performance from 3.8 V Down to 2.2 V BY: Robert C. Taft and Maria Rosaria Tursi, Data Conversion Systems

**Abstract** A 100-MS/s 8-b CMOS analog-to-digital converter (ADC) designed for very low supply voltage and power dissipation is presented. This single-ended-input ADC is based on the unified two-step subranging architecture, which processes the coarse and fine decisions in identical signal paths to maximize their matching. However, to minimize power and area, the coarse-to-fine overlap correction has been aggressively reduced to only one LSB. The ADC incorporates five established design techniques to maximize performance: bottom-plate sampling, distributed sampling, auto-zeroing, interpolation, and interleaving. Very low voltage operation required for a general purpose ADC was obtained with four additional and new circuit techniques. These are a dual-gain first-stage amplifier, differential T-gate boosting, a supply independent delay generator, and a digital delay-locked-loop controlled output driver. For a clock rate of 100 MS/s, 7.0 (7.3) effective bits for a 50 MHz (10 MHz) input are maintained from 3.8 V down to 2.2 V. At 2.2 V, this 100-MS/s converter dissipates 75 mW plus 9 mW for the reference ladder. For a typical supply of 2.7 V, it consumes just 1 mW per MS/s over the 10 160-MS/s clock frequency range. Differential nonlinearity below 0.5 LSB is maintained from 2.7 V down to 2.2 V, and it degrades only slightly to 0.8 LSB at 3.8-V supply. The converter is implemented in a 0.35-mm CMOS process, with double-poly capacitors and no low-threshold devices.

*Index Terms*Analog-to-digital converters, CMOS analog integrated circuits, Nyquist converters, subranging A/D converters, switched capacitor circuits, two-step A/D converters.

## I. INTRODUCTION

High-Speed Nyquist analog-to-digital converters (ADCs) play a decisive role in the overall performance of many imaging, video, and digital communications systems, and have been successfully developed using a number of

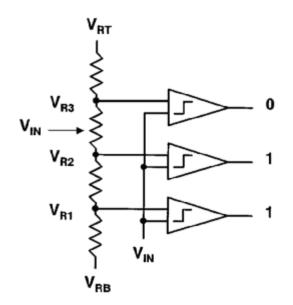

different architectures. Flash was the earliest of such architectures [1]. A resistor ladder with  $2^{N}$  1 taps provides

the reference voltages, which are directly compared to the input voltage by  $2^N$  1 comparators. This  $2^N$  1 wide "thermometer code" is encoded, usually in binary or gray code, to obtain an N-bit digital word which represents the input voltage relative to the reference voltages of the reference ladder. Fig. 1 shows the schematic for a simplified N = 2 bit example, where the input voltage lies between reference voltages V<sub>R3</sub> and V<sub>R2</sub>. Three

trends have affected monolithic Nyquist (in which inputs frequencies near half the conversion clock frequency need to be accurately digitized) ADCs. The first trend is an increase in the input frequency  $F_{IN}$  and hence

required conversion rate  $F_{\text{CLK}}$ . The second is an increase in resolution or number of bits N, as communication

and video systems evolve and become more sophisticated. The third and more recent trend is to design ADCs in aggressive CMOS technologies, with their corresponding reduction in power-supply voltage. This latter trend resulted in part from process consolidation, in which specialized analog processes were avoided due to the high cost of low-volume manufacturing. ADC designs in aggressive CMOS technologies enable the ultimate goal of integrating almost all of the analog functionality together with the digital cores.

Fig. 1. Schematic for a 2-b flash converter, which uses a resistor ladder to subdivide end-point reference voltages  $V_{RT}$  and  $V_{RB}$ . The comparators output thermometer code "0, 1, 1," corresponds to a  $V_{IN}$  between voltage taps  $V_{R3}$  and  $V_{R2}$ . Note that there is no over-range indication; the binary encoded output is "10."

## **II. SELECTING A LOW-VOLTAGE ADC ARCHITECTURE**

The choice of ADC architecture was motivated primarily by the third trend: Designing in an aggressive CMOS tech-nology, with its corresponding reductions in power-supply voltage. Classical 1.5-b-per-stage pipeline architectures require high-gain and high-bandwidth amplifiers [2], whose realization will become increasingly difficult with reductions in power-supply voltage and increasing speed. The highly parallel flash architecture lends itself to easily implemented low-voltage circuit blocks. Amplifiers preceding the comparators, used to reduce the referred-to-input comparator offsets, do not require large gain, so they can have a high bandwidth. However, the largest drawback of flash with respect to pipeline architectures is the exponential growth in the number of

comparators to  $2^{N}$  for increasing resolution, *N*. This growth in number of comparators translates directly to an exponential growth in power, area, and input capacitance of the flash converter. Two distinct enhancements to the flash architecture address this limitation, two-step subranging [3] and folding [4]. In two-step subranging, the

most significant bits (MSBs) are obtained first using  $2^{N/2}$  comparators. These MSBs are then used to subtract the coarse content of the input signal to create a residue, so that the least significant bits (LSBs) can be

obtained, again with  $2^{N/2}$  comparators. The total number of comparators required is only  $2 \cdot 2^{N/2}$ , nearly the

square root of  $2^{N}$  the flash requirement. This gives a commensurate saving in power, area, and input capacitance.

In folding, the residue for evaluating the LSBs, which is evaluated explicitly in the two-step method, is evaluated without *a priori* knowledge of the MSBs using collector cross-connected differential bipolar pairs. Thus, the MSBs and LSBs can be evaluated simultaneously. Although this technique has been successfully migrated from bipolar to CMOS, using nMOS differential pairs [5], the residue generation using drain cross-connected differential nMOS pairs generates analog signals much higher in frequency than the input signal. This necessitates a sample-and-hold amplifier at the front end for good Nyquist performance, and may limit the folding architectures for very high conversion speeds. For these latter reasons, folding was not pursued as the basis for this low-voltage ADC design.

#### **III. UNIFIED SUBRANGING ARCHITECTURE**

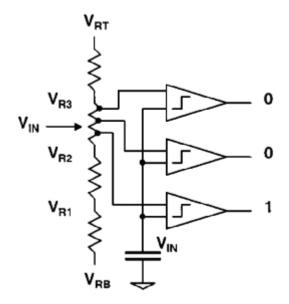

In implementing the (two-step) subranging ADC architecture, the same reference ladder provides both the MSBs "coarse" and LSBs "fine" reference voltages. A 4-b converter example starting with the flash conversion of Fig. 1

is shown in Fig. 2, where the 2-b LSBs are evaluated by comparing  $V_{IN}$  to the appropriate segment of the

reference ladder. This requires an analog MUX between the four possible resistor segments and the comparator bank. The MSBs, obtained previously as in Fig. 1, control this MUX, select the appropriate resistor segment, and are then added to the LSBs to obtain the complete digital output code.

Fig. 2. Schematic for the second comparison of a 4-b subranging converter, showing the evaluation of the two LSBs. The two MSBs "10" were obtained as shown in Fig. 1. The MSBs are not subtracted from  $V_{IN}$ . Rather, the input voltage  $V_{IN}$  is held, and the comparator reference inputs are switched onto the appropriate segment of the reference ladder. The binary representation of the LSBs is "01," which together with the MSBs "10" forms the 4-b digital output code "1001."

A concern with this approach is the need for matching between the MSBs and LSBs conversion. For inputs near the re-sistor segment boundary, a small mismatch results in the MSBs conversion selecting the incorrect resistor segment for the LSBs evaluation. Most subranging converters address this problem by extending the range of the LSBs segment beyond the MSBs segment boundary by several LSBs, , in both directions. In case of a mismatch, the LSBs result is then taken as the definitive answer, and the MSBs result is either incremented or decremented one digit. This "error correction" requires a wider analog MUX bus for generating the fine reference

voltages and significantly more comparators,  $2^{N/2} + 2 * k$ .

To address the MSBs to LSBs matching concern, Hosotani s [6] "unified" architecture was used. The same analog channel evaluates both the MSBs and LSBs, so that the input signal need not be sampled and routed to two different comparator banks, resulting in inherently good matching. One fully unified channel can sample  $V_{IN}$  and autonomously process all bits, making this architecture well suited to interleaving. Despite using a

unified architecture, Hosotani uses k = 3 additional fine references in the analog MUX, requiring a total of 21 comparators. To avoid this extra circuitry and power, no extra fine codes outside of the range imposed by the coarse-compare are examined. Seventeen comparators (k = 1) are used, which is no more overhead than that required for over/underflow indication. Only one LSB of MSBs-to-LSBs mismatch correction is obtained implicitly by using the output of comparators 1 and 17, which also generate the over-range indication.

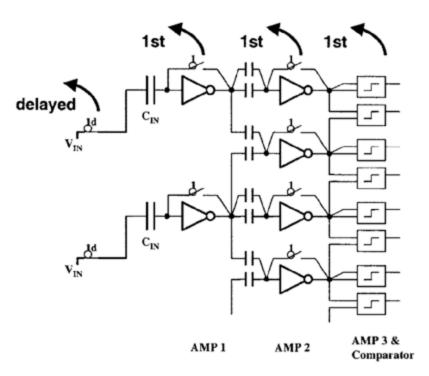

Fig. 3. Phase 1 distributed "bottom-plate" sampling, in which the sampling switch at the virtual ground of amplifier 1 is opened before opening the T-gate to  $V_{IN}$ , to avoid signal-dependent charge injection. Since the sampling switches around amplifiers 1, 2, and 3 are all opened simultaneously, the architecture is auto-zeroing:  $C_{IN}$  stores  $V_{IN}$ , whereas the input capacitors of amplifier 2 store the offset voltage of amplifier 1, and the input capacitors of amplifier 3 (inside the comparator block) store the offset voltage of amplifier 2.

## IV. INCORPORATING ESTABLISHED ADC CIRCUIT TECHNIQUES

Here five established enabling ADC circuit techniques are briefly discussed, before describing this paper s contributions in more detail. The five techniques are bottom-plate sampling, distributed sampling, auto-zeroing, interpolation, and interleaving. Fig. 3 shows a subsection of the analog channel during sampling (designated as phase 1). By using distributed sampling, no sample-and-hold amplifier (SHA) is required, since the sampling function is performed by the first amplifier stage. This saves power and alleviates the input range restriction imposed by SHAs. However, the sampling instant for all parallel paths must be identically matched. This sampling instant is set by opening the shorting switch on amp 1, after which  $V_{IN}$  can no longer transfer net charge onto  $C_{IN}$ . Since the sampling switch is always at the virtual ground of the amplifier, it injects a constant charge onto  $C_{IN}$ , independent of the signal voltage. Often referred to as "bottom-plate" sampling, this technique

avoids the distortion of signal-dependent charge injection. The opening of the T-gate connection of CIN to VIN at

the end of phase 1 is delayed with respect to the sampling instant, and is indicated by "1d."

The offset difference between amp 1 and amp 2, resulting from statistical and process variations of their constituent tran-sistors, is sampled onto the input capacitors of amp 2 during the sampling phase. By thus "auto-zeroing" the offset of amp 1, the linearity errors in the ADC transfer function otherwise introduced by offsets between the parallel amp 1s are fully eliminated. Similarly, amp 2 s offset voltage is auto-zeroed by storing it on the input capacitors of amp 3. Amp 3 is not auto-zeroed, but the effect of its offset, referred to input, is reduced by the two previous gain stages.

After sampling, the CIN s are connected to the coarse reference voltages, creating a difference voltage. This

difference voltage is amplified by amplifiers 1 through 3 and applied to 17 comparators. Rather than generating all 17 voltages independently, for the 4-b MSBs plus over-range, interpolation by-2 between amp 1 and amp 2, and again by-2 between amp 2 and amp 3, reduces the number of input capacitors by 4x; see [7], [8]. As shown,

the interpolation between the outputs of two adjacent amplifiers is accomplished by connecting their outputs to two equal-valued capacitors forming the input of the next amplifier stage. Not only does interpolation reduce the front-end loading on the input signal  $V_{IN}$  and the reference voltages, but reduces power, area, and the dc nonlinearity errors as described in [5], [8].

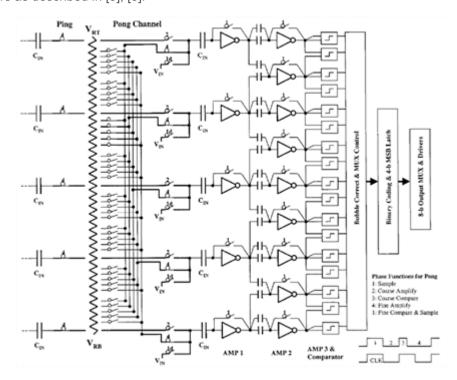

Fig. 4. Unified subranging ADC architecture, showing one complete analog channel (Pong, right), and part of the second interleaved channel (Ping, left). Both channels share the polysilicon reference resistor ladder with top node  $V_{RT}$  and bottom node  $V_{RB}$ . The switches connected to the  $C_{IN}$  s are T-gates, whose number indicates during which phase they are closed. The functions for each of Pong s phases are described bottom right).

Fig. 4 shows a detailed diagram of the fully unified ADC architecture. To achieve one conversion per clock cycle for the two-step algorithm, two channels are interleaved. Each works at one-half the conversion rate, and 180 out of phase. As shown, the two interleaved analog channels, Ping and Pong, are connected to a common reference ladder. The Ping channel is performing a coarse amplify using the coarse voltage taps on the reference ladder at the same time that the Pong channel is performing a fine amplify. Polysilicon resistor ladder terminals V<sub>RT</sub> and

V<sub>RR</sub> define the conversion range. The switches leading to the input capacitor C<sub>IN</sub> are T-gates, and their

corresponding numbers show the phase during which they are closed. The Pong channel is shown in complete detail, including a functional description of each phase. During phase 1,  $V_{IN}$  is sampled by a distributed network

formed by the five input capacitors, as previously described. In phase 2, the difference between each sampled voltage and the indicated major tap points on the reference ladder are amplified by amps 1, 2, and 3. During phase 3, this resulting difference is regenerated in 17 comparators to obtain the MSBs as demonstrated in Fig. 1. Because of the by-4 capacitive interpolation, the 17 digital outputs required just five front-end sampling capacitors. The coarse bits are latched at the end of phase 3. In phase 4, one of the 16 MUXs is switched onto the MUX bus, to generate the fine difference voltages, so that the four LSBs can be obtained by the comparators during the following phase 1.

To be continued in the July edition of the National Edge.

#### REFERENCES

- 1. B. Razavi, Principles of Data Conversion System Design. New York: IEEE Press, 1995.

- 2. T. B. Cho and P. R. Gray, "A 10-b 20-Msample/s 35-mW pipeline A/D converter," IEEE J. Solid-State Circuits, vol. 30, pp. 166 172, Mar.

1995.

- 3. A. Dingwall and V. Zazzu, "An 8-MHz CMOS subranging 8-bit A/D converter," IEEE J. Solid-State Circuits, vol. 20, pp. 72 73, Dec. 1985.

- 4. R. J. van de Plassche and R. E. J. van der Grift, "A high-speed 7-bit A/D converter," *IEEE J. Solid-State Circuits*, vol. 14, pp. 938 943, Dec. 1979.

- 5. K. Bult, A. Buchwald, and J. Laskowski, "A 170-mW 10-b 50-Msample/s CMOS ADC in 1 mm," in *ISSCC Dig. Tech. Papers*, Feb. 1997, pp. 136 137.

- S. Hosotani, T. Miki, A. Maeda, and N. Yazawa, "An 8-bit 20-MS/s CMOS A/D converter with 50-mW power consumption," *IEEE J.* Solid-State Circuits, vol. 25, pp. 167 172, Feb. 1990.

- K. Kusumoto *et al.*, "A 10-b 20-MHz 30-mW pipelined interpolating CMOS ADC," *IEEE J. Solid-State Circuits*, vol. 28, pp. 1200 1206, Dec. 1993.

- B. P. Brandt and J. Lutsky, "A 75-mW 10-b 209-MS/s CMOSsubranging ADC with 9.5 effective bits at Nyquist," IEEE J. Solid-State Circuits, vol. 34, pp. 1788 1953, Dec. 1999.

- 9. G. Yin et al., "A high-speed CMOS comparator with 8-b resolution," IEEE J. Solid-State Circuits, vol. 27, pp. 208 211, Feb. 1992.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products               |                                 | Applications                  |                                   |

|------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                  | www.ti.com/audio                | Communications and Telecom    | www.ti.com/communications         |

| Amplifiers             | amplifier.ti.com                | Computers and Peripherals     | www.ti.com/computers              |

| Data Converters        | dataconverter.ti.com            | Consumer Electronics          | www.ti.com/consumer-apps          |

| DLP® Products          | www.dlp.com                     | Energy and Lighting           | www.ti.com/energy                 |

| DSP                    | dsp.ti.com                      | Industrial                    | www.ti.com/industrial             |

| Clocks and Timers      | www.ti.com/clocks               | Medical                       | www.ti.com/medical                |

| Interface              | interface.ti.com                | Security                      | www.ti.com/security               |

| Logic                  | logic.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Power Mgmt             | power.ti.com                    | Transportation and Automotive | www.ti.com/automotive             |

| Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                   | www.ti-rfid.com                 |                               |                                   |

| OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

| Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

|                        |                                 | u Hama Dawa                   | a O a Al a a m                    |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated