# AN-214 Transmission Line Drivers and Receivers for TIA/EIA Standards RS-422 and RS-423

## **ABSTRACT**

This application note discusses the TIA/EIA standards and underscores the more important design requirements for balanced and unbalanced transmission lines, and shows that the Texas Instruments DS1691 driver and DS78LS120 receiver meet or exceed all of those requirements.

|                 | Contents                                                                                                      |    |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|

| 1               | Introduction                                                                                                  |    |  |  |  |  |  |

| 2               | The Requirements                                                                                              |    |  |  |  |  |  |

| 3               | Cable Length                                                                                                  |    |  |  |  |  |  |

| 4               | Data Signaling Rate                                                                                           |    |  |  |  |  |  |

| 5               | Characteristics                                                                                               |    |  |  |  |  |  |

| 6<br>7          | Signal Rise Time DS1691A/DS78LS120                                                                            |    |  |  |  |  |  |

| 8               | DS78LS120/DS88LS120                                                                                           |    |  |  |  |  |  |

| 9               | Fail-Safe Operation                                                                                           |    |  |  |  |  |  |

| 10              | Conclusion                                                                                                    |    |  |  |  |  |  |

|                 |                                                                                                               |    |  |  |  |  |  |

| List of Figures |                                                                                                               |    |  |  |  |  |  |

| 1               | Balanced Digital Interface Circuit                                                                            | 2  |  |  |  |  |  |

| 2               | Unbalanced Digital Interface Circuit                                                                          | 3  |  |  |  |  |  |

| 3               | Data Signaling Rate vs Cable Length                                                                           | 4  |  |  |  |  |  |

| 4               | Definition of Baud, Bits per Second (bps), Hertz (Hz) for NRZ and Manchester Coding                           | 5  |  |  |  |  |  |

| 5               | Signal Distortion Due to Duty Cycle                                                                           | 5  |  |  |  |  |  |

| 6               | Unbalanced Driver Output Signal Waveform                                                                      | 6  |  |  |  |  |  |

| 7               | Balanced Driver Output Signal Waveform                                                                        | 7  |  |  |  |  |  |

| 8               | Receiver Input Sensitivity Measurement                                                                        | 8  |  |  |  |  |  |

| 9               | Signal Rise Time on Transmission Line vs Line Length                                                          | 8  |  |  |  |  |  |

| 10              | DS3691 Connected for Balanced Mode Operation                                                                  | ç  |  |  |  |  |  |

| 11              | DS3691 Connected for Unbalanced Mode Operation (Non-inverting)                                                | 10 |  |  |  |  |  |

| 12              | Using an External Capacitor to Control Rise Time of DS3691                                                    | 10 |  |  |  |  |  |

| 13              | DS3691 Rise Time vs External Capacitor                                                                        | 11 |  |  |  |  |  |

| 14              | Comparison of Drivers without TRI-STATE Common-Mode Output Range (top waveforms) to DS3691 (bottom waveforms) | 11 |  |  |  |  |  |

| 15              | DS78LS120/DS88LS120 Dual Differential Line Receiver                                                           | 12 |  |  |  |  |  |

| 16              | Application of DS88LS120 Receiver Response Control and Hysteresis                                             | 13 |  |  |  |  |  |

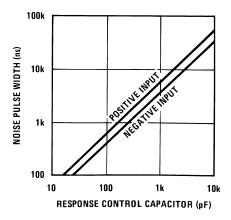

| 17              | Noise Pulse Width vs Response Control Capacitor                                                               |    |  |  |  |  |  |

| 18              | Fail-Safe Using the DS88LS120 Threshold Offset for Unbalanced Lines                                           | 14 |  |  |  |  |  |

| 19              | Fail-Safe Using the DS88LS120 Threshold Offset for Balanced Lines                                             | 14 |  |  |  |  |  |

TRI-STATE is a registered trademark of Texas Instruments. All other trademarks are the property of their respective owners.

Introduction www.ti.com

## 1 Introduction

With the advent of the microprocessor, logic designs have become both sophisticated and modular in concept. Frequently the modules making up the system are very closely coupled on a single printed circuit board or cardfile. In a majority of these cases a standard bus transceiver will be adequate. However because of the distributed intelligence ability of the microprocessor, it is becoming common practice for the peripheral circuits to be physically separated from the host processor with data communications being handled over cables (for example, plant environmental control or security system). And often these cables are measured in hundreds or thousands of feet as opposed to inches on a backplane. At this point the component wavelengths of the digital signals may become shorter than the electrical length of the cable and consequently must be treated as transmission lines. Further, these signals are exposed to electrical noise sources which may require greater noise immunity than the single chassis system.

## 2 The Requirements

The requirements for transmission lines and noise immunity have been adequately recognized by *AN-108 Transmission Line Characteristics* (SNOA746) and TIA/EIA standards TIA/EIA-422-B (balanced) and TIA/EIA-423-B (unbalanced). In this application note the generic terms of RS-422 and RS-423 will be used to represent the respective TIA/EIA standards. A summary review of these notes will show that the controlling factors in a voltage digital interface are:

- · The cable length

- The data signaling rate

- · The characteristic of the interconnection cable

- · The rise time of the signal

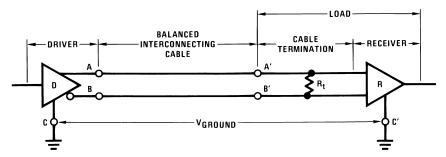

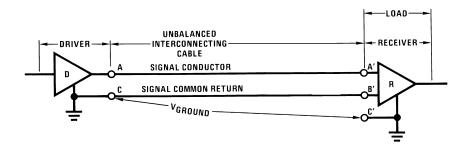

RS-422 and RS-423 contain several useful guidelines relative to the choice of balanced circuits versus unbalanced circuits. Figure 1 and Figure 2 are the digital interface for balanced (1) and unbalanced (2) circuits.

Even though the unbalanced interface circuit is intended for use at lower modulation rates than the balanced circuit, its use is not recommended where the following conditions exist:

- 1. The interconnecting cable is exposed to noise sources which may cause a voltage sufficient to indicate a change of binary state at the load.

- 2. It is necessary to minimize interference with other signals, such as data versus clock.

- 3. The interconnecting cable is too long electrically for unbalanced operation (Figure 3).

#### Legend:

R<sub>t</sub> = Transmission line termination and/or receiver input impedance

$V_{GROUND}$  = Ground potential difference

A, B = Driver interface

A', B' = Load interface

C = Driver circuit ground

C' = Load circuit ground

Figure 1. Balanced Digital Interface Circuit

www.ti.com Cable Length

Legend:

R<sub>t</sub> = Transmission line termination and/or receiver input impedance

$V_{GROUND}$  = Ground potential difference

A, C = Driver interface

A', B' = Load interface

C = Driver circuit ground

C' = Load circuit ground

Figure 2. Unbalanced Digital Interface Circuit

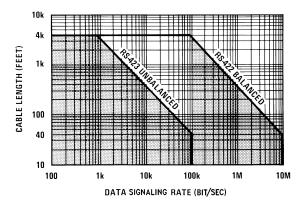

## 3 Cable Length

While there is no maximum cable length specified, guidelines are given with respect to conservative operating distances as a function of data signaling rate. Figure 3 is a composite of the guidelines provided by RS-422 and RS-423 for data signaling rate versus cable length. The data is for 24 AWG twisted pair cable terminated for worst case (due to IR drop) in a  $100\Omega$  load, with rise and fall times equal to or less than one half unit interval at the applied data rate.

The maximum cable length between driver and load is a function of the data signaling rate. But it is influenced by:

- 1. A maximum common noise range of ±7 volts

- (a) The amount of common-mode noiseDifference of driver and receiver ground potential plus driver offset voltage and coupled peak random noise.

- (b) Ground potential differences between driver and load.

- (c) Cable balance

- Differential noise caused by imbalance between the signal conductor and the common return (ground)

- 2. Cable termination

- At rates above 200 kbps or where the rise time is 4 times the one way propagation delay time of the cable

- 3. Tolerable signal distortion

Data Signaling Rate www.ti.com

Figure 3. Data Signaling Rate vs Cable Length

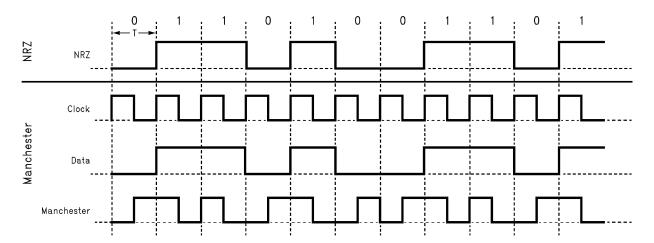

## 4 Data Signaling Rate

The TIA/EIA Standards recommend that the unbalanced voltage interface will normally be utilized on data, timing or control circuits where the data signaling rate on these circuits is below 100 kbps, and balanced voltage digital interface on circuits up to 10 Mbps. The voltage digital interface drivers and receivers meeting the electrical characteristics of this standard need not meet the entire data signaling range specified. They may be designed to operate over narrower ranges to more economically satisfy specific applications, particularly at the lower data signaling rates.

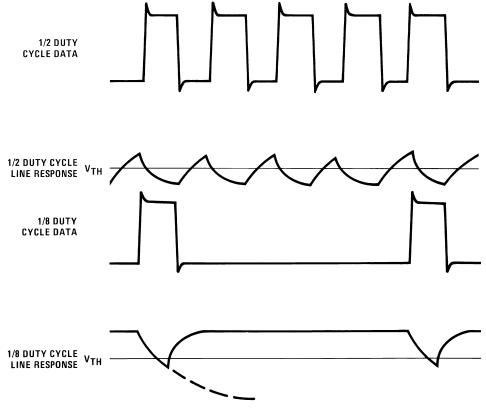

As pointed out in AN-108, the duty cycle of the transmitted signal contributes to the distortion. The effect is the result of rise time. Due to delay and attenuation caused by the cable, it is possible due to AC averaging of the signal, to be unable to reach one binary level before it is changed to another. If the duty cycle is ½ (50%) and the receiver threshold is midway between logic levels, the distortion is small. However if the duty cycle were ½ (12.5%), the signal would be considerably distorted.

#### 5 Characteristics

## 5.1 Driver Unbalanced (RS-423)

The unbalanced driver characteristics as specified by RS-423 are as follows:

- A driver circuit should be a low impedance ( $50\Omega$  or less) unbalanced voltage source that will produce a voltage applied to the interconnecting cable in the range of 4V to 6V.

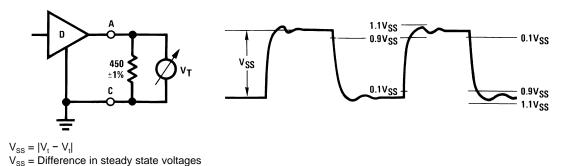

- With a test load of 450Ω connected between the driver output terminal and the driver circuit ground, the magnitude of the voltage (VT) measured between the driver output and the driver circuit ground shall not be less than 90% of the open circuit voltage magnitude (≥ 3.6V) for either binary state.

- During transitions of the driver output between alternating binary states, the signal measured across a 450Ω test load connected between the driver output and circuit ground should be such that the voltage monotonically changes between 0.1 and 0.9 of V<sub>ss</sub>. Thereafter, the signal shall not vary more than 10% of V<sub>ss</sub> from the steady state value, until the next binary transition occurs, and at no time shall the instantaneous magnitude of VT and VT exceed |6V|, nor be less than |3.6V|. V<sub>ss</sub> is defined as the voltage difference between the two steady state values of the driver output.

www.ti.com Characteristics

|            | Baud | Bits per Second | Hertz |

|------------|------|-----------------|-------|

| CLOCK      | _    | _               | 1/T   |

| NRZ        | 1/T  | 1/T             | _     |

| Manchester | 2/T  | 1/T             | _     |

bps (bits per second) - Data Information Rate "the number of bits passed along in one second." baud-Modulation Rate "the reciprocal of the minimum pulse width."

For NRZ bps = bauds

Figure 4. Definition of Baud, Bits per Second (bps), Hertz (Hz) for NRZ and Manchester Coding

Figure 5. Signal Distortion Due to Duty Cycle

Characteristics www.ti.com

Figure 6. Unbalanced Driver Output Signal Waveform

## 5.2 Driver Balanced(RS-422)

The balanced driver characteristics as specified by RS-422 are as follows:

- A driver circuit should result in a low impedance ( $100\Omega$  or less) balanced voltage source that will produce a differential voltage applied to the interconnecting cable in the range of 2V to 10V.

- With a test load of 2 resistors,  $50\Omega$  each, connected in series between the driver output terminals, the magnitude of the differential voltage (VT) measured between the 2 output terminals shall not be less than either 2.0V or 50% of the magnitude of  $V_O$ , whichever is greater. For the opposite binary state the polarity of VT shall be reversed ( $\overline{VT}$ ). The magnitude of the difference in the magnitude of VT and  $\overline{VT}$  shall be less than 0.4V. The magnitude of the driver offset voltage ( $V_{OS}$ ) measured between the center point of the test load and driver circuit ground shall not be greater than 3.0V. The magnitude of the difference in the magnitude of  $V_{OS}$  for one binary state and  $\overline{V_{OS}}$  for the opposing binary state shall be less than 0.4V.

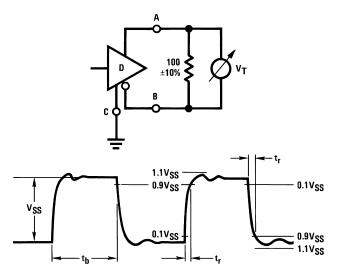

- During transitions of the driver output between alternating binary states, the differential signal

measured across a 100Ω test load connected between the driver output terminals shall be such that

the voltage monotonically changes between 0.1 and 0.9 of V<sub>ss</sub> within 10% of the unit interval or 20 ns,

whichever is greater. Thereafter the signal voltage shall not vary more than 10% of V<sub>ss</sub> from the steady

state value, until the next binary transition occurs, and at no time shall the instantaneous magnitude of

VT or VT exceed 6V, nor less than 2V.

#### 5.3 Interconnecting Cable

The characteristics of the interconnecting cable should result in a transmission line with a characteristic impedance in the general range of  $100\Omega$  to frequencies greater than 100 kHz, and a DC series loop resistance not exceeding  $240\Omega$ . The cable may be composed of twisted or untwisted pair (flat cable) and is not further specified within the standards.

- Conductor size of the 2 wires 24 AWG or larger, and wire resistance not to exceed  $30\Omega$  per 1000 feet per conductor.

- Mutual pair capacitance between 1 wire in the pair to the other should be less than 20 pF/ft.

www.ti.com Characteristics

t<sub>b</sub> = Time duration of the unit interval at the applicable modulation rate.

$t_r \le 0.1 t_b$  when  $t_b \ge 200 \text{ ns}$

$t_r \le 20 \text{ ns when } t_b < 200 \text{ ns}$

V<sub>SS</sub> = Difference in steady state voltages

$V_{SS} = |V_t - V_t|$

Figure 7. Balanced Driver Output Signal Waveform

#### 5.4 Receiver

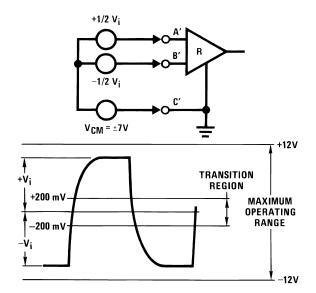

The receiver characteristics are identical for both balanced (RS-422) and unbalanced (RS-423) circuits. The electrical characteristics of a single receiver without termination or optional fail-safe provisions are specified as follows:

- Over an entire common-mode voltage range of -7V to +7V, the receiver shall not require a differential input voltage of more than 200 mV to correctly assume the intended binary state. The common-mode voltage (V<sub>CM</sub>) is defined as the algebraic mean of the 2 voltages appearing at the receiver input terminals with respect to the receiver circuit ground. Reversing the polarity of VT shall cause the receiver to assume the opposite binary state. This allows for operations where there are ground differences caused by IR drop and noise of up to ±7V

- To maintain correct operation for differential input signal voltages ranging between 200 mV and 6V in magnitude.

- The maximum voltage present between either receiver input terminal and receiver circuit ground shall

not exceed 10V (3V signal plus 7V common-mode) in magnitude nor cause the receiver to

operationally fail. Additionally, the receiver shall tolerate a maximum differential signal of 12V applied

across its input terminals without being damaged.

- The total load including up to 10 receivers shall not have a resistance less than  $90\Omega$  for balanced, and  $450\Omega$  for unbalanced at its input points and shall not require a differential input voltage of greater than 200 mV for all receivers to assume the correct binary state.

Signal Rise Time www.ti.com

Figure 8. Receiver Input Sensitivity Measurement

# 6 Signal Rise Time

The signal rise time is a high frequency component which causes interference (near end cross-talk) to be coupled to adjacent channels in the interconnecting cable. The near-end crosstalk is a function of both rise time and cable length, and in considering wave shaping, both should be considered. Since in the balanced voltage digital interface the output is complementary, there is practically no cross-talk coupled and therefore wave shaping is limited to unbalanced circuits.

Per RS-423 the rise time of the signal should be controlled so that the signal has reached 90% of  $V_{\rm SS}$  between 10% and 30% of the unit interval at the maximum data signaling rate. Below 1 kbps the time to reach 90%  $V_{\rm SS}$  shall be between 100  $\mu$ s and 300  $\mu$ s. If a driver is to operate over a range of data signaling rates and employ a fixed amount of wave shaping which meets the specification for the maximum data signaling rate of the operating range, the wave shaping is considered adequate for all lesser modulation rates.

However a major cause of distortion is the effect the transmission line has on the rise time of the transmitted signal. Figure 9 shows the effect of line attenuation and delay to a voltage step as it progresses down the cable. The increase of the rise time with distance will have a considerable effect on the distortion at the receiver. Therefore in fixing the amount of wave shaping employed, caution should be taken not to use more than the minimum required.

Figure 9. Signal Rise Time on Transmission Line vs Line Length

www.ti.com DS1691A/DS78LS120

## 7 DS1691A/DS78LS120

#### 7.1 The Driver

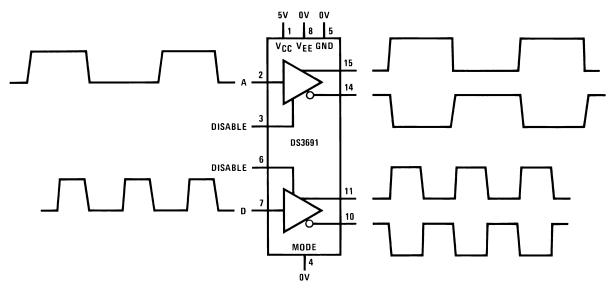

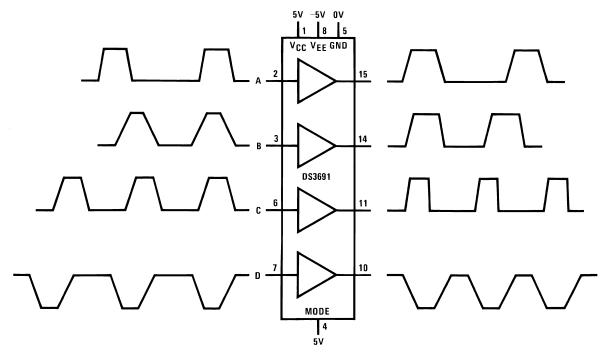

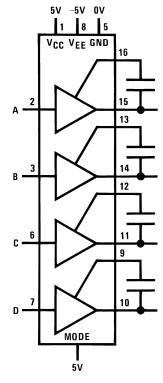

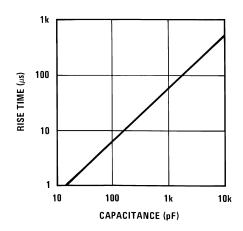

The DS1691A/DS3691 are low power Schottky TTL line drivers designed to meet the above listed requirements of both standards. They feature 4 buffered outputs with high source and sink current capability with internal short circuit protection. The DS1691/DS3691 employ a mode selection pin which allows the circuit to become either a pair of balanced drivers (Figure 10) or four independent unbalanced drivers (Figure 11). When configured for unbalanced operation (Figure 12) a rise time control pin allows the use of an external capacitor to control rise time for suppression of near end cross-talk to adjacent channels in the interconnect cable. Figure 13 is the typical rise time vs external capacitor used for wave shaping. Note that the rise time control capacitors are connected betwen the control pins and the respective outputs.

The DS3691 configured for RS-422 is connected  $V_{CC} = 5V V_{EE} = 0V$ , and configured for RS-423 is connected  $V_{CC} = 5V V_{EE} = -5V$ . For applications with greater cable lengths the DS1691/DS3691 may be connected with a  $V_{CC}$  of 5 volts and  $V_{EE}$  of -5 volts. This will create an output which is symmetrical about ground, similar to Mil Standard 188-114. This mode is also allowed by the "B" revision of RS-422 (TIA/EIA-422-B) which relaxed to open circuit voltage from 6V to 10V in magnitude.

When configured as balanced drivers (Figure 10), each of the drivers is equipped with an independent TRI-STATE® control pin. By use of this pin it is possible to force the driver into its high impedance mode for applications using party line techniques. If the driver is used in multi-point applications (multiple drivers) the use of the response control capacitors is not allowed.

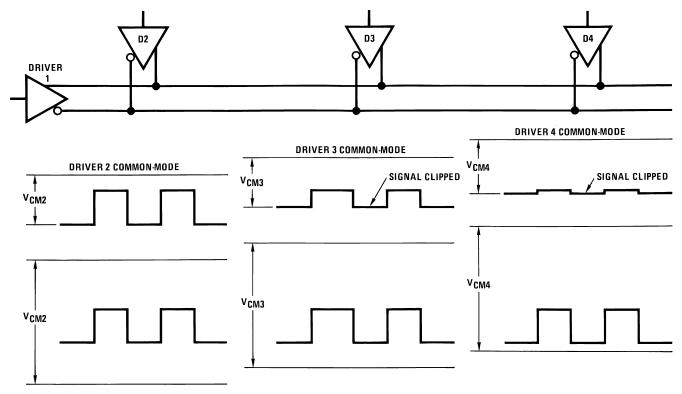

If the common-mode voltage, between driver 1 and all other drivers in the circuit, is small then several line drivers (and receivers) may be incorporated into the system. However, if the common-mode voltage exceeds the TRI-STATE® common-mode range of any driver, then the signal will become attenuated by that driver to the extent the common-mode voltage exceeds its common-mode range (see Figure 14, top waveform).

It is important then to select a driver with a common-mode range equal to or larger than the common-mode voltage requirement of the system. In the case of RS-422 and RS-423 the minimum common-mode range would be ±7V. The DS1691/DS3691 driver is tested to a common-mode range of ±10V and will operate within the requirements of such a system (see Figure 14, bottom waveform).

Figure 10. DS3691 Connected for Balanced Mode Operation

DS1691A/DS78LS120 www.ti.com

Figure 11. DS3691 Connected for Unbalanced Mode Operation (Non-inverting)

Figure 12. Using an External Capacitor to Control Rise Time of DS3691

www.ti.com DS1691A/DS78LS120

Figure 13. DS3691 Rise Time vs External Capacitor

Figure 14. Comparison of Drivers without TRI-STATE Common-Mode Output Range (top waveforms) to DS3691 (bottom waveforms)

DS78LS120/DS88LS120 www.ti.com

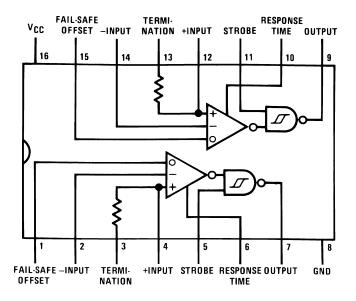

Top View

Figure 15. DS78LS120/DS88LS120 Dual Differential Line Receiver

#### 8 DS78LS120/DS88LS120

#### 8.1 The Receiver

The DS78LS120/DS88LS120 are high performance, dual differential TTL compatible line receivers which meet or exceed the above listed requirements for both balanced and unbalanced voltage digital interface.

The line receiver will discriminate a  $\pm 200$  millivolt input signal over a full common-mode range of  $\pm 10$  volts and a  $\pm 300$  millivolt signal over a full common-mode range of  $\pm 15$  volts.

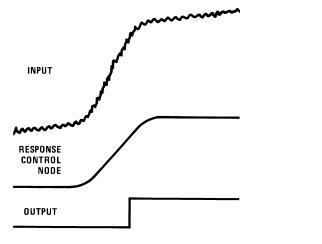

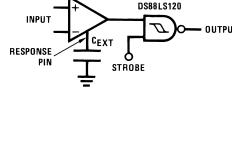

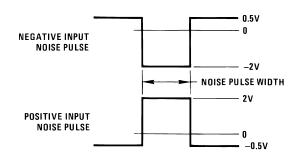

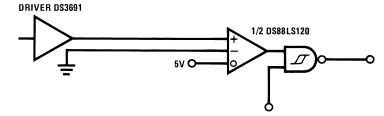

The DS78LS120/DS88LS120 include response control for applications where controlled rise and fall times and/or high frequency noise rejection are desirable. Switching noise which may occur on the input signal can be eliminated by the 50 mV (referred to input) of hysteresis built into the output gate (Figure 16). The DS78LS120/DS88LS120 makes use of a response control pin for the addition of an external capacitor, which will not affect the line termination impedance of the interconnect cable. Noise pulse width rejection versus the value of the response control capacitor is shown in Figure 17 . The combination of the filter followed by hysteresis will optimize performance in a worst case noise environment. The DS78C120/DS88C120 is identical in performance to the DS78LS120/DS88LS120, except it's compatible with CMOS logic gates.

www.ti.com Fail-Safe Operation

Figure 16. Application of DS88LS120 Receiver Response Control and Hysteresis

Figure 17. Noise Pulse Width vs Response Control Capacitor

## 9 Fail-Safe Operation

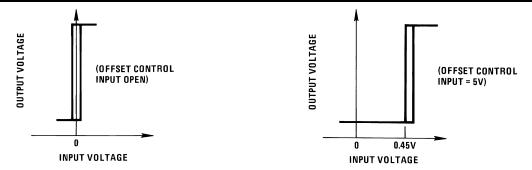

Some communication systems require elements of a system to detect the loss of signals in the transmission lines. And it is desirable to have the system shut-down in a fail-safe mode if the transmission line is open or short. To facilitate the detection of input opens or shorts, the DS78LS120/DS88LS120 incorporates an input threshold voltage offset. This feature will force the line receiver to a specific logic state if presence of either fault condition exists.

The receiver input threshold is  $\pm 200$  mV and an input signal greater than  $\pm 200$  mV insures the receiver will be in a specific logic state. When the offset control input is connected to a  $V_{CC} = 5V$ , the input thresholds are offset from 200 mV to 700 mV, referred to the non-inverting input, or -200 mV to -700 mV, referred to the inverting input. Therefore, if the input is open or short, the input will remain in a specific state (see Figure 18).

It is recommended that the receiver be terminated in  $500\Omega$  or less to insure it will detect an open circuit in the presence of noise.

For unbalanced operation, the receiver would be in an indeterminate logic state if the offset control input was open. Connecting the offset to +5V, offsets the receiver threshold 0.45V. The output is forced to a logic zero state if the input is open or short.

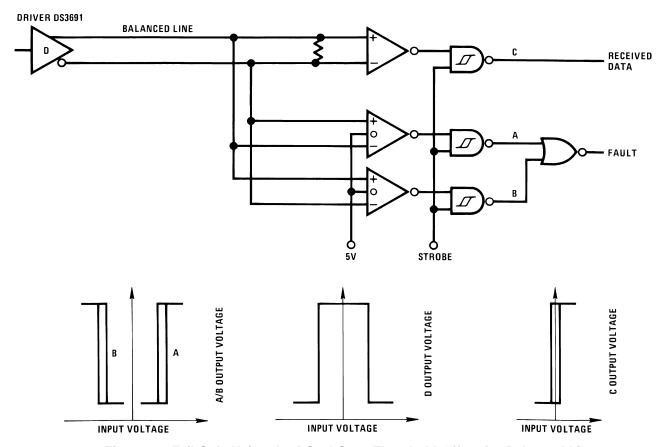

For balanced operation with inputs short or open, receiver C will be in an indeterminate logic state. Receivers A and B will be in a logic zero state allowing the NOR gate to detect the short or open fault condition. The "strobe" input will disable the A and B receivers and therefore may be used to "sample" the fail-safe detector (see Figure 19).

Conclusion www.ti.com

Figure 18. Fail-Safe Using the DS88LS120 Threshold Offset for Unbalanced Lines

Figure 19. Fail-Safe Using the DS88LS120 Threshold Offset for Balanced Lines

#### 10 Conclusion

This application note provides a brief overview of TIA/EIA-422-B and TIA/EIA-423-B. At the time of publication of this application note the Rev. B standards were draft standard proposals only. For complete/current information on the respective standards, please refer to the respective standards, as minor differences may exist between this document and the final versions.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <u>www.ti.com/omap</u> TI E2E Community <u>e2e.ti.com</u>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>