# Analog Engineer's Circuit Window Comparator with Integrated Reference Circuit

# **Design Goals**

| Input                             |                      | Output                            |                      | Supply          |                                             |

|-----------------------------------|----------------------|-----------------------------------|----------------------|-----------------|---------------------------------------------|

| V <sub>MON Min</sub>              | V <sub>MON Max</sub> | V <sub>OUT Min</sub>              | V <sub>OUT Max</sub> | V <sub>DD</sub> | V <sub>REF</sub>                            |

| 0 V                               | 6 V                  | 0 V                               | 3.3 V                | 3.3 V           | 400 mV                                      |

| Lower Threshold (V <sub>L</sub> ) |                      | Upper Threshold (V <sub>H</sub> ) |                      | Divider Load Cu | rrent (I <sub>MAX</sub> ) at V <sub>H</sub> |

| 3.2 V                             |                      | 4.1 V                             |                      | 10 µA           |                                             |

## **Design Description**

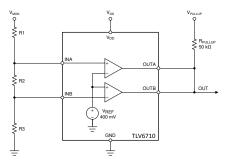

This circuit utilizes the TLV6710, which contains two comparators and a precision internal reference of 400mV. The monitored voltage ( $V_{MON}$ ) is divided down by  $R_1$ ,  $R_2$ , and  $R_3$ . The voltage across  $R_2$  and  $R_3$  is compared to the 400 mV internal reference voltage ( $V_{REF}$ ). If the input signal ( $V_{MON}$ ) is within the window, the output is high. If the signal level is outside of the window, the output is low.

The TLV6710 will be utilized for this example, which conveniently contains two comparators and a common precision internal reference trimmed to a 400 mV threshold. Two discrete comparators and an external reference may also be used.

# **Design Notes**

- 1. Make sure the comparator input voltage range is not violated at the highest expected V<sub>MON</sub> voltage.

- 2. If the outputs are to be combined together (ORed), open collector or open drain output devices *must* be used.

- 3. It is also recommended to repeat the following calculations using the minimum and maximum resistor tolerance values and comparator positive and negative offset voltages.

- 4. The TLV6710 has built-in asymmetrical hysteresis, resulting in the rising edge V<sub>L</sub> and falling edge V<sub>H</sub> being slightly shifted. Comparators without hysteresis will meet the calculated thresholds.

1

# **Design Steps**

The resistor divider will be calculated in separate  $V_H$  and  $V_L$  segments to create 400 mV at the appropriate comparator input at the desired threshold voltage.

1. The total divider resistance R<sub>TOTAL</sub> is calculated from the upper threshold voltage and divider current:

$$R_{TOTAL} = R_1 + R_2 + R_3 = \frac{V_H}{I_{MAX}} = \frac{4.1V}{10\mu A} = 410k\Omega$$

2. The upper threshold voltage is set by the *bottom* divider resistor  $R_3$  going into the INB pin. From the reference voltage and the divider current, the value of  $R_3$  is calculated from:

$$R_3 = \frac{V_{REF}}{I_{MAX}} = \frac{400mV}{10\mu A} = 40k\Omega$$

3. The *middle* resistor  $R_2$  is found by looking at  $R_2$  and  $R_1$  as one resistor, and calculating the value for that total resistance for  $V_{REF}$  at  $V_L$ , then subtracting out the known  $R_3$ :

$$R_2 = \left( \left( \frac{R_{TOTAL}}{V_L} \times V_{REF} \right) - R_3 \right) = \left( \left( \frac{410 k \Omega}{3.2 V} \times 400 m V \right) - 40 k \Omega \right) = 11.25 k \Omega$$

4. R<sub>1</sub> is found by taking the total resistance and subtracting the sum of R<sub>2</sub> and R<sub>3:</sub>

$$R_1 = R_{TOTAL} - (R_2 + R_3) = 410k\Omega - (11.25k\Omega + 40k\Omega) = 358.75k\Omega$$

Because these are calculated ideal resistor values, the next closest 0.1% standard resistor values will be used. The following table summarizes the changes due to the resistor value changes and the resulting trip point voltage change.

| Resistor       | Calculated Ideal Value | Nearest Standard 0.1% (E192) Value |  |

|----------------|------------------------|------------------------------------|--|

| R <sub>1</sub> | 358.750 kΩ             | 361 kΩ                             |  |

| R <sub>2</sub> | 11.25 kΩ               | 11.3 kΩ                            |  |

| R <sub>3</sub> | 40 kΩ                  | 40.2 kΩ                            |  |

#### **Nearest 0.1% Resistor Values**

Because the values of the divider string resistors were changed, the resulting new threshold voltages must be calculated. The thresholds are found by multiplying the divider ratio by the reference voltage:

$$V_{H} = \left(\frac{R1 + R2 + R3}{R3}\right) \times V_{REF} = \left(\frac{361k\Omega + 11.3k\Omega + 40.2k\Omega}{40.2k\Omega}\right) \times 0.4V = 10.26119 \times 0.4V = 4.1045 \quad V_{REF} = 10.26119 \times 0.4V = 10.26119 \times 0.4V = 4.1045 \quad V_{REF} = 10.26119 \times 0.4V = 10.26119 \times 0.26119 \times 0.200 \times 0.200$$

$$V_L = \left(\frac{R1 + R2 + R3}{R2 + R3}\right) \times V_{REF} = \left(\frac{361k\Omega + 11.3k\Omega + 40.2k\Omega}{11.3k\Omega + 40.2k\Omega}\right) \times 0.4V = 8.0097 \times 0.4V = 3.2039 \quad V_{REF} = \left(\frac{361k\Omega + 11.3k\Omega + 40.2k\Omega}{11.3k\Omega + 40.2k\Omega}\right) \times 0.4V = 8.0097 \times 0.4V = 3.2039 \quad V_{REF} = \left(\frac{361k\Omega + 11.3k\Omega + 40.2k\Omega}{11.3k\Omega + 40.2k\Omega}\right) \times 0.4V = 8.0097 \times 0.4V = 3.2039 \quad V_{REF} = \left(\frac{361k\Omega + 11.3k\Omega + 40.2k\Omega}{11.3k\Omega + 40.2k\Omega}\right) \times 0.4V = 8.0097 \times 0.4V = 3.2039 \quad V_{REF} = \left(\frac{361k\Omega + 11.3k\Omega + 40.2k\Omega}{11.3k\Omega + 40.2k\Omega}\right) \times 0.4V = 8.0097 \times 0.4V = 3.2039 \quad V_{REF} = 0.0097 \times 0.4V = 3.2039 \quad V_{REF}$$

| Threshold      | Using Ideal Resistors | Using Standard Resistors | Percent Change |

|----------------|-----------------------|--------------------------|----------------|

| V <sub>H</sub> | 4.1 V                 | 4.1045 V                 | +0.109%        |

| VL             | 3.2 V                 | 3.2039 V                 | +0.121%        |

## Ideal and Standard Resistor Thresholds

To ensure that the maximum 6V  $V_{MON}$  voltage does not violate the TLV6710 1.7 V maximum input voltage rating, the  $V_{MON\_MAX}$  and the  $V_L$  division ratio found in step 4 above are used to calculate the maximum voltage at the TLV6710 input:

$$V_{INPUT\_MAX} = \frac{V_{MON\_MAX}}{V_{L\_RATIO}} = \frac{6}{8.0097} = 749.1 \quad mV$$

The value 749 mV is less than 1.7 V, so the input voltage is well below the input maximum. If using discrete comparators, make sure the voltage is within the specified input common mode range ( $V_{ICR}$ ) of the device used.

2

# **Design Simulations**

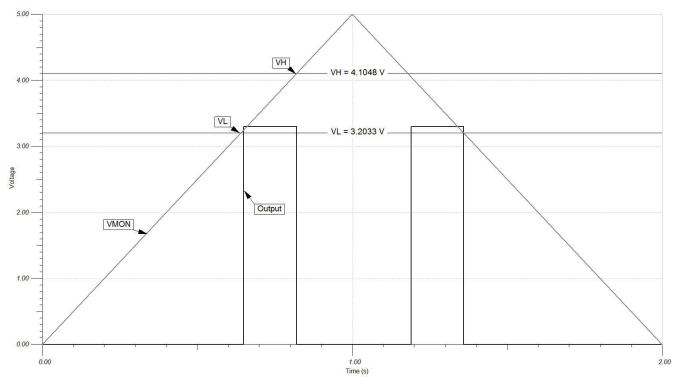

# **Transient Simulation Results**

Note: The Rising edge  $V_L$  and falling edge  $V_H$  thresholds are slightly shifted due to the built-in asymmetrical hysteresis of the TLV6710. Comparators without hysteresis will meet the calculated thresholds.

3

# **Design References**

For more information on many comparator topics including input voltage range, output types and propagation delay, please visit TI Precision Labs - Comparator Applications.

See Analog Engineer's Circuit Cookbooks for TI's comprehensive circuit library.

See TINA-TI<sup>™</sup> TLV6710 Reference Design circuit simulation file, Literature Number SNVMB09.

#### **Design Featured Comparator**

| TLV6710           |               |  |

|-------------------|---------------|--|

| V <sub>ss</sub>   | 2 V to 36 V   |  |

| V <sub>inCM</sub> | 0 V to 1.7 V  |  |

| V <sub>out</sub>  | 0 V to 25 V   |  |

| Vref              | 400 mV ±0.25% |  |

| Ιq                | 11 µA         |  |

| l <sub>b</sub>    | 1 nA          |  |

| Prop Delay        | 10 µs         |  |

| #Channels         | 2             |  |

| TLV6710           |               |  |

#### **Design Alternate Comparator**

| TLV6700           |               |  |

|-------------------|---------------|--|

| V <sub>ss</sub>   | 1.8 V to 18 V |  |

| V <sub>inCM</sub> | 0 V to 6.5 V  |  |

| V <sub>out</sub>  | 0 V to 18 V   |  |

| Vref              | 400 mV ±0.5%  |  |

| Ιq                | 5.5 μΑ        |  |

| ۱ <sub>b</sub>    | 1 nA          |  |

| Prop Delay        | 29 µs         |  |

| #Channels         | 2             |  |

| TLV6700           |               |  |

# **Design Alternate Comparator**

| TLV1702           |                    |  |

|-------------------|--------------------|--|

| V <sub>ss</sub>   | 2.7 V to 36 V      |  |

| V <sub>inCM</sub> | Rail to Rail       |  |

| V <sub>out</sub>  | Open Drain to 36 V |  |

| V <sub>os</sub>   | ±3.5 mV            |  |

| l <sub>q</sub>    | 75 µA              |  |

| ۱ <sub>b</sub>    | 15 nA              |  |

| Prop Delay        | 0.4 µs             |  |

| #Channels         | 2                  |  |

| TLV1702           |                    |  |

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated