# Shared Memory Interface with the TMS320C54x DSP

APPLICATION REPORT: SPRA441

Veikko Koivumaa

Digital Signal Processing Solutions April 1998

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain application using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1998, Texas Instruments Incorporated

#### **TRADEMARKS**

TI is a trademark of Texas Instruments Incorporated.

Other brands and names are the property of their respective owners.

#### **CONTACT INFORMATION**

US TMS320 HOTLINE (281) 274-2320

US TMS320 FAX (281) 274-2324

US TMS320 BBS (281) 274-2323

US TMS320 email dsph@ti.com

# **Contents**

| Abstract                                                  | 7 |

|-----------------------------------------------------------|---|

| Product Support                                           | 8 |

| Related Documentation                                     |   |

| World Wide Web                                            |   |

| Email                                                     |   |

| Design Problem                                            | 9 |

| The Quick Solution                                        | g |

| SRAM Used as a Global Memory Area without Using HOLD Mode |   |

| FIFO Used as Shared Memory                                |   |

| Dual-Port RAM Used as Shared Memory                       |   |

# Figures

| Figure 1. | DSP Shared Memory Area Using External SRAM without HOLD | . 10 |

|-----------|---------------------------------------------------------|------|

| Figure 2. | Bi-directional FIFO between a TMS320C54x DSP and a Host | . 11 |

| Figure 3. | Read – Read Cycle for DSP/FIFO Interface                | . 12 |

| Figure 4. | Write Cycle for DSP/FIFO Interface                      | . 12 |

| •         | Shared Memory Interface Using Dual-Port RAM             |      |

# Shared Memory Interface with the TMS320C54x DSP

#### **Abstract**

This document describes how to share memory (SRAM, FIFO, Dual-Port RAM) between a Texas Instruments (TI™) TMS320C54x digital signal processor (DSP) and Host or other DSP.

There are several ways to implement this task. The simplest way is to use a C54x with a Host Port Interface, if it is suitable for the design and the 2Kx16 block of memory is large enough. This internal memory area is then available with no glue logic required.

# **Product Support**

#### **Related Documentation**

The following list specifies product names, part numbers, and literature numbers of corresponding TI documentation.

- □ TMS320C54X DSP CPU and Peripheral Reference Set Volume I, April 1997, Literature number spru131d

- Data Sheet, TMS320C54x Fixed-Point Digital Signal Processors, July 1997, Literature number SPRS039A

- □ Shared Memory Interface with a TMS320C5x DSP, Designer Notebook Page DNP63

#### **World Wide Web**

Our World Wide Web site at **www.ti.com** contains the most up to date product information, revisions, and additions. Users registering with TI&ME can build custom information pages and receive new product updates automatically via email.

#### **Email**

For technical issues or clarification on switching products, please send a detailed email to **dsph@ti.com**. Questions receive prompt attention and are usually answered within one business day.

# **Design Problem**

How do you share memory (SRAM, FIFO, Dual-Port RAM) between a TMS320C54x DSP and Host (Micro or DSP)?

#### The Quick Solution

There are several ways to implement this task. The simplest way is to use a C54x family member with the Host Port Interface provided it is suitable for the design and the 2Kx16bit block of memory is large enough. This internal memory area of the DSP is then available to the external processor with virtually no glue logic required in most cases.

If you need the DSP to share external memory with a Host and the DSP can use the HOLD mode, then this situation is similar to that described in Designer Notebook Page DNP63 (Shared Memory Interface with a TMS320C5x DSP). If in HOLD mode, the DSP can continue execution of the program from internal memory by resetting the Hold Mode (HM) bit. (For more information on how to use the HPI, see the *TMS320C54X DSP CPU and Peripheral Reference Set*, Volume 1, 1997, section 8.5. HOLD mode is described in section 10.6.)

For the purposes of this application note, a 40Mhz (40MIP) C54x processor is considered. The zero wait state access time for a C54x-40 read from external memory is 15ns (using MSTRB). The required setup time for a read is 5ns. For writes the DSP uses two external bus cycles. I/O reads and writes take two cycles (using IOSTRB).

# SRAM Used as a Global Memory Area without Using HOLD Mode

When SRAM is shared without HOLD mode, buffers need to be used for the address and data lines. Figure 1 describes how two LC54x DSPs share a 32Kx16-memory device. The DSPs are synchronized to run with the same clock, so the CLKOUT from the left DSP is the source for the right DSP.

SRAM is located in the upper half of 64KW Data space (DS). SRAM accesses are arbitrated and synchronized to the clock with a Programmable Logic Device (PLD). Here the DSPs have equal priority to memory. Only one access from a DSP is allowed at a time with the next memory cycle going to the other DSP if both are asking for the memory within the same arbitration period. Data Strobe DS\_, Address A15, and Memory Strobe MSTRB\_ indicates a valid memory request. These signals are decoded to the Chip Select CS\_ line of SRAM. Write timing for the SRAM is CS\_ controlled.

The PLD also controls the access from buffers to SRAM with Output Enable OE\_ lines. READY indicates to the DSP that the memory cycle can be served. Note that the DSP will perform ready-detection only if at least two software wait states are programmed into Software Wait State Register (SWWRS) for the upper half of data memory space.

The LC54x Address lines (A0-A14), Data lines (D0-D15), and the R/W\_ line are all buffered to the SRAM. The R/W\_ line also controls the direction of the buffer. Using buffers allows both DSPs to also have local external program memories (64KW) and data memory (32KW on lower half of data space).

TMS320LC541-40 TMS320LC541-40 **PLD** READY READY ATF22LV10C  $\overline{\mathbf{DS}}$ DS MSTRB MSTRB A15 CLKIN CLKOUT OE DIR DIR  $\overline{OE}$ R/W R/W SN74ALVCH16245 SN74ALVCH16245 A0-A14 A0-A14 D0-D15 D0-D15 BUFFER **BUFFER** IDT71V008S10 **SRAM**

Figure 1. DSP Shared Memory Area Using External SRAM without HOLD

# **FIFO Used as Shared Memory**

Figure 2 shows how to use a bi-directional FIFO for communication between a TMS320C54x DSP and a Host. The FIFO is an SN74ABT7819-12, clocked bi-directional FIFO with 512x18x2 organization. The DSP data bus is only 16 bits, so the A16-A17 lines of FIFO are connected to Vcc with resistors. The DSP has control over port A. This means it writes to FIFOA-B and reads from FIFOB-A. The first read takes two cycles and then successive reads take only one cycle.

FIFO TMS320C541-40 PORT A PORT B CLKOUT W/RA R/W MSTRE DS A15 RSTA BIG HFΔ INTO INT1 ORA D0-D15 A0-A15 A16 A17 WENA RENA PENA SN74ABT7819-12

Figure 2. Bi-directional FIFO between a TMS320C54x DSP and a Host

If there are no interrupts, the buffer will be read as empty. For reads, the first value needs to be discarded because it is not yet valid data. However, after this initial state reads are single cycle. Writes always take two cycles (0WS).

The Almost-Full/Empty flag (AF/AEA) is not used as we indicate Half-Full state of FIFOA-B with HFA line to BIO\_ input of the DSP. When FIFOA-B becomes full, Input-Ready port A (IRA) goes low. The DSP is interrupted with the INTO\_ line and this disables writes to the FIFO. When FIFOB-A becomes empty, the Output-Ready port A(ORA) goes low. The DSP is interrupted with the INT1\_ line to stop reads to the FIFO.

The DSP also controls the FIFOA-B reset line RSTA\_ with XF output. The FIFO is located in the upper 32KW half of data space with A15 address line. Valid DSP access to the FIFO is indicated with valid address, Data Strobe DS\_, and Memory Strobe MSTRB .

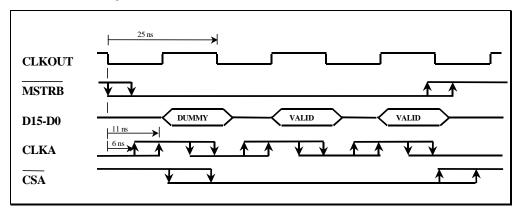

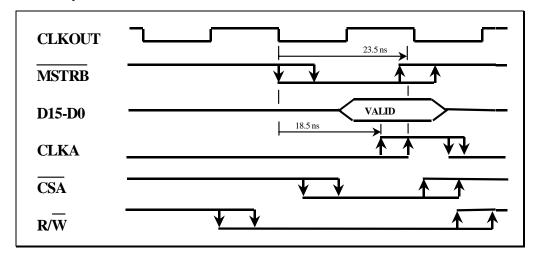

The critical FIFO timings that need to be considered are the 9ns read access time and 3ns data setup time for write. The FIFO is clocked with the CLKA Low (L) to High (H) transition. Setup time for Chip Select CSA\_ is 6ns. The timing for a read cycle is shown in Figure 3 and for a write cycle in Figure 4. The gate delay is allowed to be a minimum 3ns and maximum 5.5ns. To make handling gate delays easier, you can achieve for NOR/OR gates faster delays, for example, with min/max within the range 1ns - 4ns. The savings of 1.5ns on the maximum value can then be added to the maximum value of the AND/NAND. This could provide a delay range of 3.0 -7.0ns for the AND and NAND gates.

Figure 3. Read – Read Cycle for DSP/FIFO Interface

Figure 4. Write Cycle for DSP/FIFO Interface

The C54x read cycle is activated with MSTRB\_ going low 0-5ns after CLKOUT goes low. MSTRB\_ stays active for as long as we have successive reads. The most critical timing is with CLKA. The L to H transition may happen at earliest 3ns after CLKOUT H to L to eliminate extra clock, after we stop the reading. MSTRB\_ L to H timing is -2/+3ns to CLKOUT H to L. The L to H on CLKA may happen latest 11ns after CLKOUT H to L. This meets the maximum access time 9ns and setup time 5ns for C54x data read.

For the C54x write cycle, MSTRB\_ goes low and high for every write cycle, which takes two CLKOUT cycles. When CSA\_ is active, the extra clock (from 1<sup>st</sup> CLKOUT cycle) needs to be eliminated. Taking inverted MSTRB\_ to NAND input does this. Write data is valid after 10ns from second CLKOUT H to L plus 3ns for data setup giving valid data after 13ns. CLKA L to H comes earliest at 18.5ns and latest at 23.5ns after starting the second CLKOUT cycle.

Local external data memory can exist with the FIFO. If you want to use a smaller area from data space, then more address lines need to be decoded.

### **Dual-Port RAM Used as Shared Memory**

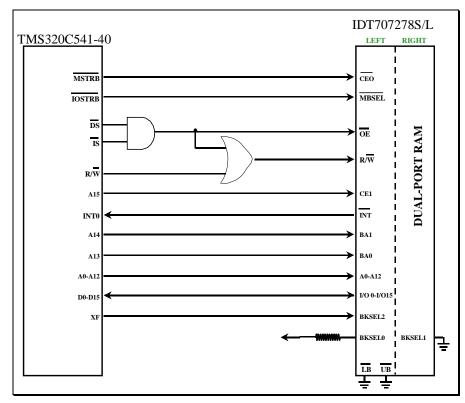

This interface uses a 32Kx16 Dual-Port SRAM (DPRAM) with external bank selects from IDT (IDT707278S/L). The interface is shown in Figure 5. The DSP is connected to the Left port. The Host sharing the RAM is connected to the Right port. The memory area consists of four 8Kx16 banks, to which multiple devices can connect by using the bank select inputs BKSEL0-3.

Figure 5. Shared Memory Interface Using Dual-Port RAM

In this design the DSP and Host have their own 8K block to be used as a local memory. BKSEL0 is used for Left port and BKSEL1 for Right port. Two upper 8K blocks are used for exchanging data between the processors. The DSP has control over BKSEL2 via the XF line. The Host must be able to control BKSEL3 by toggling it. DPRAM is located in the upper 32KW of the DSP data space, so address line A15 works as CE1 Chip Select. Memory Strobe MSTRB\_ works as a second Chip Select CE0\_. I/O space is used for Mailbox control logic. I/O Strobe IOSTRB\_ is connected to MBSEL\_ to activate a valid Mailbox access. Address lines A13-A14 are used to choose an 8K bank with Bank Addresses BA0-BA1.

The access time of the DPRAM is 15ns from chip select, so no wait state is needed with a 40MIPS C54x. Access time from OE\_signal is 9ns, so we have 6ns for the AND gate to connect data and I/O spaces.

When the mailing (data in BKSEL2 RAM block) to the Right port is ready, the DSP changes XF from H to L to give access to the Right port and sends Mailbox2 interrupt. The Host will then change the BKSEL3 signal L to H to give this RAM area to the Left port and sends Mailbox3 interrupt. The DSP will be interrupted on the INTO\_ interrupt line. The DSP will clear Mailbox3 interrupt and read the new data from Host processor. After reading data, the DSP writes new data to BKSEL3 RAM. When this access has completed, the DSP sends the Mailbox3 interrupt. If the Host is quicker than the DSP in reading and writing the data, it will initiate the change of RAM blocks sooner. The response from the DSP should be the same as the Host's response to an interrupt from DSP.

The configuration shown allows you to add external data memory to the lower 32KW of the DSP data space. External program space is also available. Here I/O space is used without decoding. The timing to add a decoder is not critical, with I/O accesses at two cycles.