Application Report SPRA585

# Connecting TMS320C54x DSP with Flash Memory

Jason Jiang

Customer Application Center TI (Shanghai)

# Abstract

Flash memory offers better cost per bit than traditional EPROM when storage density increases. Flash memory competes with EPROM with lower power consumption, and smaller package and program content after assembling. These features make flash memory a good selection in applications like GPS receiver, hand-held MP3 player, and Set-Top Boxes. The Texas Instruments (TI<sup>TM</sup>) TMS320C54x family of digital signal processors (DSPs) offers fast operation speed and low power consumption that makes this DSP ideal for portable applications where flash memory also fits. This application report provides a reference on interfacing a DSP with flash memory.

#### Contents

| Introduction to Flash Memory            | 2 |  |

|-----------------------------------------|---|--|

| Control Logic Signals                   |   |  |

| Command Set                             |   |  |

| Program/Erase                           |   |  |

| Connecting TMS320C54x with Flash Memory |   |  |

| Software Design                         |   |  |

| Appendix A Assembly Code                | 7 |  |

#### Figures

| Figure 1. | Connections Between TMS320C54x and 28F400B3 | .3 |

|-----------|---------------------------------------------|----|

| Figure 2. | Programming Flow Chart                      | .4 |

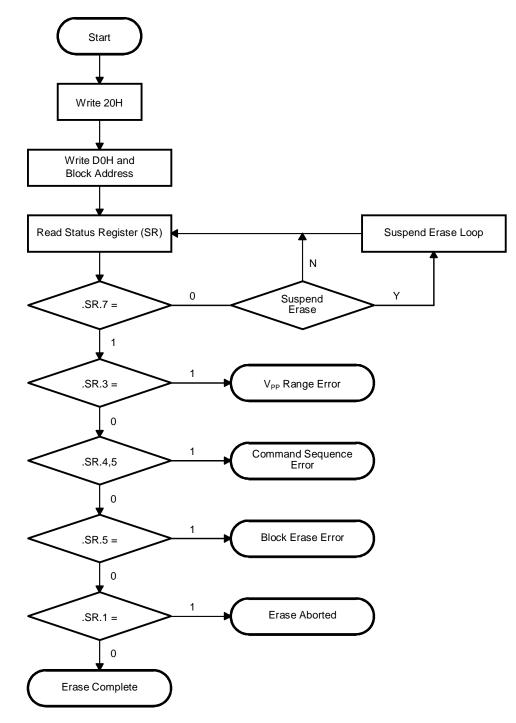

| Figure 3. | Erasing Flow Chart                          | .5 |

#### Tables

| Table 1. | Intel 28F400B3 Control Logic Signals | .2 |

|----------|--------------------------------------|----|

|          | 28F400B3 Command Set                 |    |

|          | 28F400B3 Program/Erase Bus Cycles    |    |

# **Introduction to Flash Memory**

Many vendors provide flash memory. Although the control logic is not identical, it is similar. This application report uses the Intel<sup>™</sup> 28F400B3 that is 4M bits of flash memory.

## **Control Logic Signals**

The control logic signals of the 28F400B3 are carried on six pins as listed in Table 1.

Table 1. Intel 28F400B3 Control Logic Signals

| Symbol | Туре | Description                                                                     |

|--------|------|---------------------------------------------------------------------------------|

| /CE    | Ι    | Chip enable                                                                     |

| /OE    | I    | Output enable                                                                   |

| /WE    | I    | Write enable                                                                    |

| /RP    | Ι    | Reset/Deep power down. It is connected to logic high ensuring normal operation. |

| /WP    | Ι    | Write protection. It is connected to logic high to enable programming content.  |

| VPP    |      | Program/Erase power supply. It is connected to Vcc simplifying power design.    |

When in read mode, the 28F400B3 read timing is compliant with typical memory read timing (that is, /CE and /OE are logic low and /WE is logic high). When in program/erase mode, the 28F400B3 timing is similar to typical memory write time (that is, /CE and /WE are logic low and /OE is logic high).

### **Command Set**

The behavior of flash memory is controlled by a command set. It is the host's responsibility to issue the correct command set that instructs the flash memory into a specific mode. In this application report only a subset of the command set is supported, as listed in Table 2.

Table 2. 28F400B3 Command Set

| Code | Device Mode | Description                                 |

|------|-------------|---------------------------------------------|

| FF   | Read Array  | Device is compatible with EPROM             |

| 40   | Program     | Device writes data into specific address    |

| 20   | Erase       | Device erases entire section before program |

### **Program/Erase**

Flash memory is organized into several sections. The section size is dependent on specific devices. Before programming flash memory, the entire section should be erased. Therefore, programming flash memory is performed section after section.

Both program and erase are two-bus cycle operations (see Table 3).

#### Table 3. 28F400B3 Program/Erase Bus Cycles

|         | 1 <sup>st</sup> Bus Cycle |         |      | 1 <sup>st</sup> Bus Cycle 2 <sup>nd</sup> Bus Cy |         | Bus Cycle |  |

|---------|---------------------------|---------|------|--------------------------------------------------|---------|-----------|--|

| Command | Operation                 | Address | Data | Operation                                        | Address | Data      |  |

| Program | Write                     | Х       | 40H  | Write                                            | PA      | PD        |  |

| Erase   | Write                     | Х       | 20H  | Write                                            | BA      | D0H       |  |

Note: PA = program address, PD = program data, BA = block address

After program/erase is initiated, the read operation can be used to check programming/erasing status. When program/erase is finished, the host should launch a read command to place the flash memory into normal read operation.

# Connecting TMS320C54x with Flash Memory

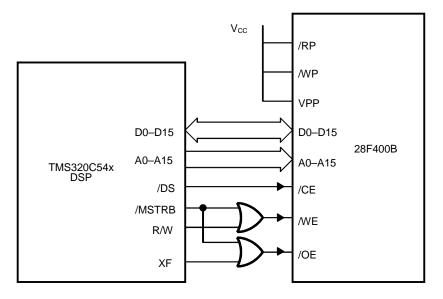

The 28F400B3 is connected to 'C54x as an external data memory (see Figure 1). The address bus and data bus are connected to the 'C54x external bus, and /CE is connected to the /DS pin on the 'C54x. The XF pin on the 'C54x is used to enable programming. When XF is driven low, the flash memory should be in read mode. When XF is driven high, the flash memory can be erased and programmed. In order to match 28F400B3 timing requirements, XF is ORed with /MSTRB before being connected to /OE. The R/W pin is ORed with /MSTRB before being connected to /WE.

Figure 1. Connections Between TMS320C54x and 28F400B3

### **Software Design**

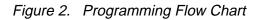

The program and erase timings are controlled by the 'C54x. The DSP program is run from on-chip memory. The programming flow chart is shown in Figure 2 and the erasing flow chart is shown in Figure 3.

Connecting TMS320C54x DSP with Flash Memory

**i**j

*i*j

# References

- 1) TMS320C54x Reference Set, Volume 1:CPU and Peripherals. (SPRU131)

- 2) Intel SMART 3 Advanced Boot Block 4-Mbit, 8-Mbit, 16-Mbit Flash Memory Family. (290580-003)

# Appendix A Assembly Code

|        | .mmregs<br>.def<br>.text | Start               |                              |

|--------|--------------------------|---------------------|------------------------------|

| Start  | :                        |                     |                              |

|        | STM                      | #00FEH, SP          |                              |

|        | STM                      |                     | ;set s/w wait state = 5      |

|        | CALL                     | Set_Read_Mode       | ;put into normal read mode   |

| ;      | •                        |                     |                              |

| ;      | •                        |                     |                              |

|        | STM                      | #0, AR1             | ;arl is set to block address |

|        | CALL                     | Erase               |                              |

|        | STM                      |                     | arl is set to data address   |

|        | LD                       |                     | ;bl contains data to program |

|        | CALL                     | Program             |                              |

|        | CALL                     | Set_Read_Mode       |                              |

| ;<br>; | •                        |                     |                              |

|        | •<br>ead_Mode            | •                   |                              |

| Sec_N  | SSBX                     | XF                  | ;enable command write        |

|        | LD                       | #OFFH, A            | ;read array command code     |

|        | STM                      | #4000H, AR1         | ;any external memory         |

|        | STL                      | A, *AR1             | ;write command code          |

|        | RPT                      | #4                  |                              |

|        | NOP                      |                     | ;delay CPU                   |

|        | RSBX                     | XF                  | disable command write        |

|        | RET                      |                     |                              |

| Erase  | :                        |                     |                              |

|        | PSHM                     | AR1                 | ;save block address          |

|        | SSBX                     | XF                  | ;enable command write        |

|        | LD                       | #20H, A             | ;set command code            |

|        | STM                      | #4000H, AR1         | ;any external address        |

|        | STL                      | A, *AR1             | ;first byte = 20h            |

|        | LD                       | #0D0H, A            | ;second byte = 0d0h          |

|        | STL                      | A, *AR1             |                              |

|        | RPT                      | #4                  |                              |

|        | NOP                      |                     | ;delay CPU                   |

|        | RSBX                     | XF                  | disable command write;       |

| E_RS:  | TD                       | 4 J J J             | tack shakes                  |

|        | LD                       | *AR1, A             | ;get status                  |

|        | ADD                      | А, #0, В<br>#80Н, В | ;b=a                         |

|        | AND<br>BC                | E_SC, BNEQ          | ;test sr.7                   |

|        | AND                      | <u>н</u> 40н, А     | ;erase suspend?              |

|        | BC                       | Error, ANEQ         | Verase suspend:              |

|        | B                        | E RS                | ;read sr again               |

| E SC:  | D                        |                     | ficua bi again               |

|        | AND                      | #3AH, A             | ;mask error bits             |

|        | BC                       | Error, ANEQ         |                              |

|        | POPM                     | AR1                 | ;restore address             |

|        | RET                      |                     |                              |

|        |                          |                     |                              |

Ü

| Program: |       |             |                                |  |  |

|----------|-------|-------------|--------------------------------|--|--|

|          | SSBX  | XF          | ;enable command write          |  |  |

|          | LD    | #40H, A     | ;set program command code      |  |  |

|          | STL   | A, *AR1     | ;arl point to external address |  |  |

|          | RPT   | #4          |                                |  |  |

|          | NOP   |             | ;delay CPU                     |  |  |

|          | STL   | B, *AR1     | ;write date                    |  |  |

|          | RPT   | #4          |                                |  |  |

|          | NOP   |             | ;delay CPU                     |  |  |

|          | RSBX  | XF          | disable command write          |  |  |

| P_RS:    |       |             |                                |  |  |

|          | LD    | *AR1, A     | ;get status                    |  |  |

|          | ADD   | А, #0, В    | ;b=a                           |  |  |

|          | AND   | #80h, B     |                                |  |  |

|          | BC    | P_RS, BNEQ  | ;read sr again                 |  |  |

| P_SC:    |       |             |                                |  |  |

|          | AND   |             | ;mask error bits               |  |  |

|          | BC    | Error, ANEQ |                                |  |  |

|          | RET   |             |                                |  |  |

|          |       |             |                                |  |  |

| Error    |       | \$          | and the second                 |  |  |

|          | В     | Ŷ           | ;self loop                     |  |  |

|          | .sect | ".vec"      |                                |  |  |

|          | В     | Start       |                                |  |  |

|          |       |             |                                |  |  |

.end

#### **INTERNET**

TI Semiconductor Home Page www.ti.com/sc TI Distributors www.ti.com/sc/docs/distmenu.htm PRODUCT INFORMATION CENTERS Americas Phone +1(972) 644-5580 Fax +1(972) 480-7800 Email sc-infomaster@ti.com Europe, Middle East, and Africa Phone Deutsch +49-(0) 8161 80 3311 +44-(0) 1604 66 3399 English Español +34-(0) 90 23 54 0 28 +33-(0) 1-30 70 11 64 Francais +33-(0) 1-30 70 11 67 Italiano Fax +44-(0) 1604 66 33 34 epic@ti.com Email Japan Phone International +81-3-3344-5311 Domestic 0120-81-0026 Fax International +81-3-3344-5317 Domestic 0120-81-0036 Email pic-japan@ti.com

Asia Phone International +886-2-23786800 Domestic Australia 1-800-881-011 TI Number -800-800-1450 10810 China TI Number -800-800-1450 Hong Kong 800-96-1111 TI Number -800-800-1450 India 000-117 TI Number -800-800-1450 Indonesia 001-801-10 TI Number -800-800-1450 Korea 080-551-2804 Malaysia 1-800-800-011 TI Number -800-800-1450 New Zealand 000-911 TI Number -800-800-1450 Philippines 105-11 TI Number -800-800-1450 Singapore 800-0111-111 TI Number -800-800-1450 Taiwan 080-006800 Thailand 0019-991-1111 TI Number -800-800-1450 Fax 886-2-2378-6808 Email tiasia@ti.com

TI is a trademark of Texas Instruments Incorporated.

Intel is a trademark of Intel Corp.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty, or endorsement thereof.

Copyright © 1999 Texas Instruments Incorporated