# Implementing a Software UART on the TMS320C54x with the McBSP and DMA

Robert J. DeNardo

DSP Applications – Semiconductor Group

#### ABSTRACT

This report discusses the implementation of a universal asynchronous receiver and transmitter (UART) on a TMS320C54x<sup>™</sup> DSP using the McBSP and DMA and provides a software UART implementation in C-callable assembly code. In order to implement an asynchronous interface such as a UART using a serial device, software must be written to detect and generate the appropriate framing bits. The initialization of the McBSP and DMA and provides a and the timing at which each is enabled is critical to the correct operation of the UART. A thorough examination of these issues is given in this report as well as an explanation of the code.

#### Contents

| 1  | Introd                                   | uction                                                              | . 3                              |

|----|------------------------------------------|---------------------------------------------------------------------|----------------------------------|

| 2  | UART                                     | Functionality                                                       | . 3                              |

| 3  | Implei                                   | mentation                                                           | . 5                              |

| 4  | McBS                                     | Ρ                                                                   | . 6                              |

| 5  | DMA                                      |                                                                     | 12                               |

| 6  | Trans                                    | mit Process                                                         | 16                               |

|    | 6.1                                      | Procedure at Start of Transmission                                  | 17                               |

|    | 6.2                                      | Procedure at End of Transmission                                    | 19                               |

| 7  | Receiv                                   | ve Process                                                          | 20                               |

|    | 7.1                                      | Procedure When Packet Received                                      | 20                               |

|    | 7.2                                      | Procedure To Read Received Packet                                   | 22                               |

| 8  | Overv                                    | iew of Code                                                         | 22                               |

| 9  | Equat                                    | es                                                                  | 22                               |

|    | 9.1                                      | MCBSP_CHOICE                                                        | 22                               |

|    | 9.2                                      | DMA_RX_CHOICE                                                       | 23                               |

|    | 9.3                                      | DMA_TX_CHOICE                                                       |                                  |

|    | 9.4                                      | INTOSEL                                                             |                                  |

|    | 9.5                                      |                                                                     |                                  |

|    |                                          | PARITY                                                              |                                  |

|    | 9.6                                      | HSTOPBITS                                                           | 23                               |

|    | 9.6<br>9.7                               | HSTOPBITS                                                           | 23<br>23                         |

|    | 9.6<br>9.7<br>9.8                        | HSTOPBITS<br>DATABITS<br>BAUDRATE                                   | 23<br>23<br>23                   |

|    | 9.6<br>9.7<br>9.8<br>9.9                 | HSTOPBITS<br>DATABITS<br>BAUDRATE<br>INTERRUPT_BASED                | 23<br>23<br>23<br>23             |

|    | 9.6<br>9.7<br>9.8<br>9.9<br>9.10         | HSTOPBITS<br>DATABITS<br>BAUDRATE<br>INTERRUPT_BASED<br>DMA_PTR_MOD | 23<br>23<br>23<br>23<br>23       |

| 10 | 9.6<br>9.7<br>9.8<br>9.9<br>9.10<br>9.11 | HSTOPBITS<br>DATABITS<br>BAUDRATE<br>INTERRUPT_BASED                | 23<br>23<br>23<br>23<br>23<br>23 |

TMS320C54x is a trademark of Texas Instruments.

|     | 10.1         | _UARTLSR                                                                                                                                     | 23 |

|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 11  | Private      | variables                                                                                                                                    | 24 |

|     |              | rxchar                                                                                                                                       |    |

|     |              | rxbufhalf                                                                                                                                    |    |

|     |              | txbufhalf                                                                                                                                    |    |

|     | 11.4<br>11.5 | numTxPkts                                                                                                                                    |    |

|     | 11.6         | RxBuffer[2*RxPKTBITS]                                                                                                                        |    |

|     |              | decoderMask                                                                                                                                  |    |

|     | 11.8         | mask1011b                                                                                                                                    | 25 |

|     | 11.9         | mask0100b                                                                                                                                    |    |

|     | 11.10        | one                                                                                                                                          | 25 |

| 12  |              | Routines                                                                                                                                     |    |

|     |              | _UARTInit(inputs: none; outputs: none)                                                                                                       |    |

|     |              | _UARTStart(inputs: A<0:start Rx, A==0:start Rx & Tx, A>0:start Tx; outputs: none)                                                            |    |

|     | 12.3<br>12.4 | _UARTStop(inputs: A<0(stop Rx), A==0(stop Rx & Tx), A>0(stop Tx); outputs: none)<br>_UARTSetBaudRate(inputs: A=clock divisor; outputs: none) |    |

|     | 12.5         | _UARTSetBreak(inputs: A!=0:send break, A==0:end break; outputs: none)                                                                        |    |

|     | 12.6         | _UARTTxChar(inputs: A=char to transmit; outputs: none)                                                                                       |    |

|     | 12.7         | _UARTRxChar(inputs: none; outputs: A=last received char)                                                                                     |    |

|     |              | _UARTDMATxISR(inputs: none; outputs: none)                                                                                                   |    |

|     |              | _UARTDMARxISR(inputs: none; outputs: none)                                                                                                   |    |

|     |              | _UARTRBFint(inputs: none; outputs: none)                                                                                                     |    |

|     |              | _UARTLSIint(inputs: none; outputs: none)                                                                                                     |    |

| 13  |              | Routines                                                                                                                                     |    |

| 13  | 13.1         | ParityCalc(inputs: A=received char (data & parity bits only);                                                                                | 21 |

|     | 10.1         | outputs: TC=0 (even parity), TC=1(odd parity))                                                                                               | 27 |

|     | 13.2         | ParityCheck(inputs: A=received char (data & parity bits only);                                                                               |    |

|     |              | outputs: AL=received char (data bits only))                                                                                                  | 27 |

| 14  | Usage        | of UART Code                                                                                                                                 | 27 |

| 15  | Perfor       | nance                                                                                                                                        | 28 |

|     |              | Memory                                                                                                                                       |    |

|     | 15.2         | Cycle Count                                                                                                                                  | 28 |

| 16  | Verific      | ation                                                                                                                                        | 30 |

| 17  | RS232        | Connections                                                                                                                                  | 30 |

| 18  | Refere       | nces                                                                                                                                         | 31 |

| Арр | endix A      | Flowcharts for Routines                                                                                                                      | 32 |

| App | endix E      | B UART Code (uart.asm)                                                                                                                       | 35 |

| Арр | endix C      | Include File (UARTSetup.inc)                                                                                                                 | 56 |

| Арр | endix C      | Command File (uart.cmd)                                                                                                                      | 57 |

| Арр | endix E      | Example Use C Code (ExampleC.c)                                                                                                              | 58 |

| Арр | endix F      | Example Use ASM Code (ExampleASM.asm)                                                                                                        | 62 |

| Арр | endix G      | Example Interrupt Vectors Table (vectors.asm)                                                                                                | 67 |

#### List of Figures

| Figure 1. UART Data Packet                                             | 4  |

|------------------------------------------------------------------------|----|

| Figure 2. McBSP Receive Frame Structure                                | 7  |

| Figure 3. Timing of Signal Perfectly Synchronized to Serial Port Clock | 8  |

| Figure 4. Timing of Signal with Offset and Rate Skew                   | 8  |

| Figure 5. McBSP Frame Restrictions                                     | 9  |

| Figure 6. DMA Circular Buffers                                         | 13 |

| Figure 7. UART Initialization                                          | 16 |

| Figure 8. Procedure at Start of Transmission                           | 18 |

| Figure 9. Procedure at End of Transmission                             | 19 |

| Figure 10. Procedure When Packet Received                              | 21 |

| Figure 11. Procedure to Read Received Packet                           | 22 |

| Figure 12. UART Status Register                                        | 24 |

| Figure 13. RS232 Interface Circuit                                     | 31 |

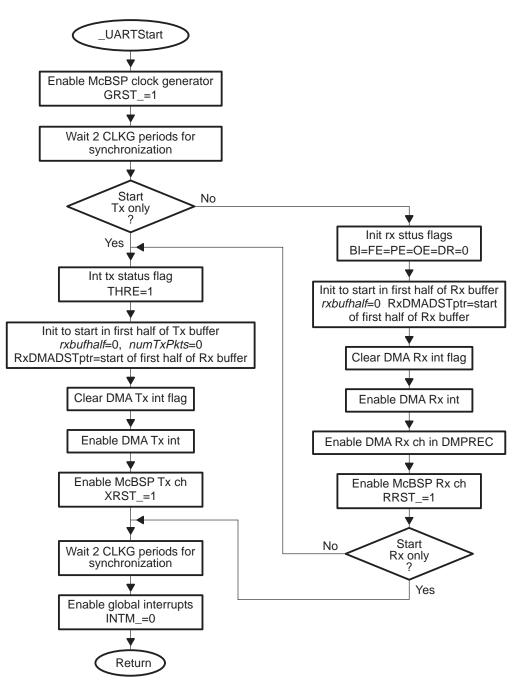

| Figure A–1. Procedure to Start UART                                    | 32 |

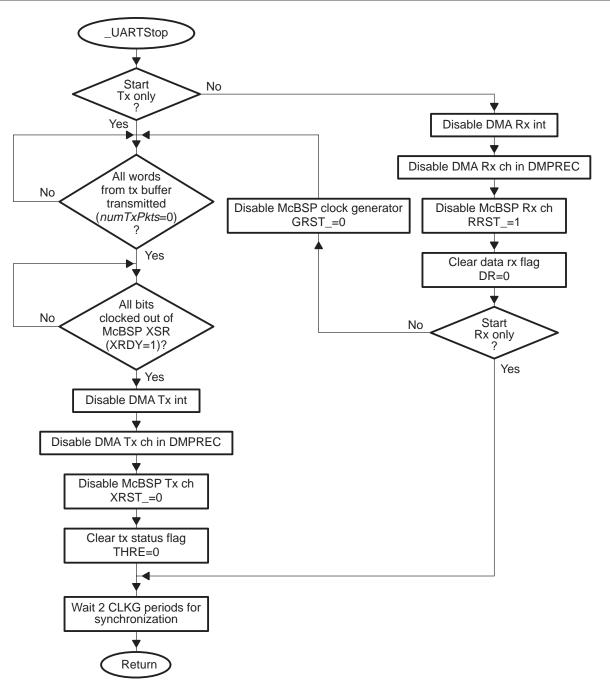

| Figure A–2. Procedure to Stop UART                                     | 33 |

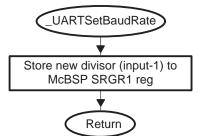

| Figure A–3. Procedure to Change Baud Rate                              | 34 |

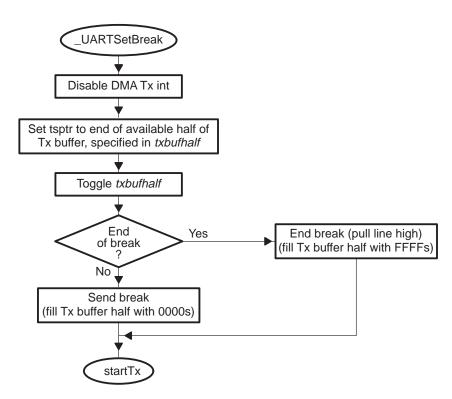

| Figure A–4. Procedure to Send a Break                                  | 34 |

#### List of Tables

| Table 1. | Divisor Limits for Given Baud Rate and Clock Rate | . 10 |

|----------|---------------------------------------------------|------|

| Table 2. | McBSP Initialization                              | . 11 |

| Table 3. | DMA Initialization                                | . 15 |

| Table 4. | UART Memory Consumption                           | . 28 |

| Table 5. | UART Routine Cycle Counts                         | . 29 |

| Table 6. | Performance of Software UART                      | . 29 |

## 1 Introduction

The TMS320C54x DSP provides a flexible synchronous serial interface through the McBSPs. However, interfacing the DSP to an asynchronous device, such as a UART, requires more than just correct initialization of the McBSP. Synchronous communication relies on three separate signals to transmit and receive data: data, frame sync and clock. Asynchronous communication, however, transmits the data on a single line without any clocking. For the receiver to know when the data begins and ends, start and stop bits must frame the data. The purpose of this report is to explain in detail how to hook up an asynchronous device to the McBSP of the DSP and how to correctly process this data using the DMA and software.

## 2 UART Functionality

A UART (universal asynchronous receiver and transmitter) is nothing more than a serial asynchronous interface. It is responsible for correctly formatting the data for transmission and decoding it on reception.

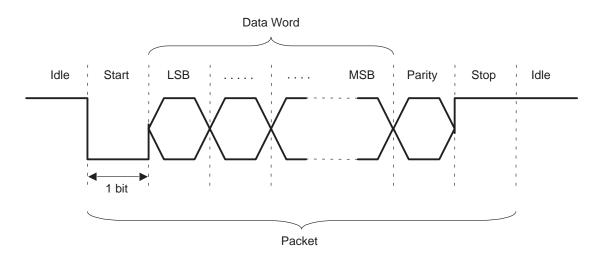

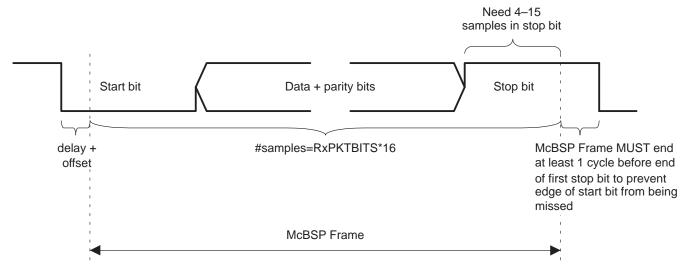

The data received or transmitted by the UART requires a start bit (logic low) at the front of the packet and a stop bit (logic high) at the end. The data packet is sent from least significant bit to most significant bit. For error checking purposes, a parity bit may also be added. The signal on the line is always high unless data is present. An example of such a packet is shown in Figure 1.

Figure 1. UART Data Packet

Typically, a UART has the following capabilities:

• Variable length data

The character to be sent can be of length 5, 6, 7, or 8 bits.

• Variable number of stop bits

There can be 1, 1.5, or 2 stop bits.

• Programmable baud rate

A register is provided for a divisor that divides down the master clock to generate the intended baud rate.

Autobaud detect

This feature allows the UART to automatically detect the baud rate of the transmitter.

• Parity generation

When sending a character, the UART has the ability to send a parity bit for error checking purposes. The parity settings are none, even, odd, space, or mark. If no parity is generated, the parity bit is omitted from the packet. Even parity ensures that the number of 1's in the transmitted word is even. Odd parity ensures that the number of 1's in the transmitted word is odd. Space parity always sets the parity bit to 0. Mark parity always sets the parity bit to 1.

• Parity detection

When a character is received, the UART will check the parity bit and make sure it matches the parity setting of the connection. If the parity bit does not match, an error is set inside a status register.

Set Break

This will send a stream of 0s which is longer than the packet length (start bit + data bits + parity bit + stop bits). It provides a means of indicating a special event to the receiver (such as change in baud rate).

Break indicator

The UART has the ability to detect a break condition (when a stream of 0s longer than the packet length is received). This indicates a special condition to the UART and is reported in a status register.

• Framing Error detection

Signals if an invalid stop bit was detected and reports it in a status register.

Overrun detection

Signals that another word was received before the prior word was read out. Reports the error in a status register.

Interrupt-based or polling-based operation

The UART can be serviced either when it generates an interrupt to the DSP for a receive, transmit, or error event, or it can be serviced by polling the status bits to determine when an event occurs.

Character FIFO

A FIFO is used to buffer the receive and transmit characters, relieving the host from servicing the UART for each new character.

Modem Functionality

This is provided through four inputs (CTS\_, DSR\_, DCD\_, and RI\_) and four outputs (DTR\_, RTS\_, OUT1\_, and OUT2\_). These signals allow the UART to setup hardware flow control with a device emulating a modem.

This implementation of a software UART provides all of these features except for Autobaud detect, FIFO mode, and Modem Functionality. It is modeled after the TL16C450 ACE<sup>(1)</sup>. The number of data and stop bits and the parity is selectable at compile time. If desired, INTERRUPT\_BASED mode allows the user to handle receive, transmit, and error events within an ISR.

## 3 Implementation

In order to emulate this asynchronous interface, a way to generate and detect the framing bits must be devised. Because the serial port is not synchronized to the UART signals, we cannot guarantee the serial port clock will align perfectly with the edge of the start bit. This creates an offset between the asynchronous signal and the synchronous serial port. Also, the DSP serial port clock frequency will in almost all cases not be exactly matched to the baud rate of the asynchronous signal, causing rate skew in the signal. The best way to reduce the offset and rate skew is to oversample the bit stream. In this implementation an oversampling of 16 will be used, as this is optimum for a 16 bit DSP in terms of data storage and manipulation as well as for providing robustness to the process. The oversampling also gives the UART the ability to run at slower speeds.

For the receive process, the McBSP will oversample the data bits and the DMA will store them in a memory buffer for later handling. When a complete packet is read in, the DMA will interrupt the DSP so it can interpret the packet. The procedure is opposite for the transmit process; the DSP fills a buffer with the oversampled bit stream and then enables the DMA to begin transferring this data out the serial port.

A number of issues arise with this implementation which must be dealt with:

- How to interface the McBSP to the asynchronous data line

- How to initialize the DMA for receiving and transmitting the packets

- How to create and transmit a packet

- How to receive and decode a packet

## 4 McBSP

A serial port typically has three signals it either creates or receives for each direction of data: data, frame sync, clock. The asynchronous signal, however, is present on only one line, on which it has its own framing signals. To properly communicate between these interfaces, these signals must be properly mapped and interpreted.

The biggest challenge in interfacing a synchronous device to an asynchronous signal is not in the transmission but rather in the reception. Transmission is a simple process in terms of the timings of the signals; the serial port can transmit according to its clock and the receiver will correctly decode the signal, as long as the start and stop bits are appropriately placed and the sampling rate is appropriate. The receiver timings are more complicated. The asynchronous signal, by nature, can be received at any time, and most likely will not be aligned with the serial port clock. Also, there can be slight differences in the baud rate compared to the sample rate of the serial port, causing the received data to "slide". Because of these issues, the serial port receive channel and software must be setup appropriately to recognize these constraints and to work around them.

The length of the packets (PKTBITS) are #start bits + #data bits + #parity bits + #stop bits. There is 1 start bit and 1, 1.5, or 2 stop bits. If parity generation and detection are enabled, an extra parity bit is added. The number of data bits can be 1-15 without parity, or 1-14 with parity. Each of these bits will be oversampled and represented by 16 bits on the DSP.

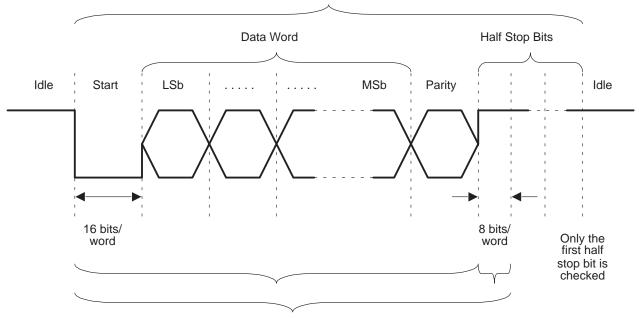

For transmission, the UART must be able to send half stop bits. Therefore, the McBSP transmit port is set for dual phase frames, with the first phase having 16 bit words and the second phase having 8 bit words. The length of the first phase is (#start bits + #data bits + #parity bits) words and the length of the second phase is (2\*#stop bits) words. The total length of the transmit frame (TxPKTBITS) in words is the sum of these phases. The data transmit (DX) pin of the DSP is tied to the transmit data line of the interface. The transmit frame sync (FSX) and clock (CLKX) pins are not used.

From Figure 1 we can see that the asynchronous signal line is always high unless a data packet has been sent across. When a packet is sent, the start bit is sent first, so the signal will go low. This is similar to an active-low frame sync. The McBSP gives us the flexibility to choose the polarity of the frame sync signal as active-low. By tying the receive data line to the data receive (DR) and frame sync (FSR) pins of the McBSP receive channel, we can trigger the McBSP to start receiving the packet whenever the line goes low. To prevent the McBSP from re-triggering, it is set to ignore all frame syncs during the receive packet.

During decoding, the center of each oversampled bit is checked. Only the first half of the stop bit is received and checked, which gives more flexibility in the sampling rate, as will be seen below. The total number of bits the McBSP receives in a frame will be RxPKTBITS=(#start bits + #data bits + #parity bits + 0.5). Therefore, the McBSP receive port is set to have dual phase frames with the first phase of length (#start bits + #data bits + #parity bits) words and the second phase of length 1 word. The word size of the first phase is 16 and the second phase is 8. Since the start bit is part of the data packet, ideally there will be a 0-bit delay between the received frame sync and the data. However, on the 5410 errors are generated on receive (missed frame syncs) unless the delay is set to 1 bit. See Figure 2 for an example of how the McBSP receive frame aligns with the data packet.

Total bits in packet = PKTBITS

McBSP Receive Frame = RxPKTBITS\*16 samples

#### Figure 2. McBSP Receive Frame Structure

The sampling rate of the McBSP is critical to the correct operation of the software UART. The McBSP will ignore all subsequent frame syncs during the reception of the frame we have defined above. To get the maximum data rate, it must be able to detect the next start bit, which could immediately follow the stop bit. The frames syncs and receive data are latched on the falling edges of the serial port clock. For a frame sync to be detected, the signal must be high for at least one clock cycle before it goes low again. This resets the frame sync logic. Therefore, the McBSP must be finished reading in the first data packet before the transition from the stop bit to the next start bit occurs.

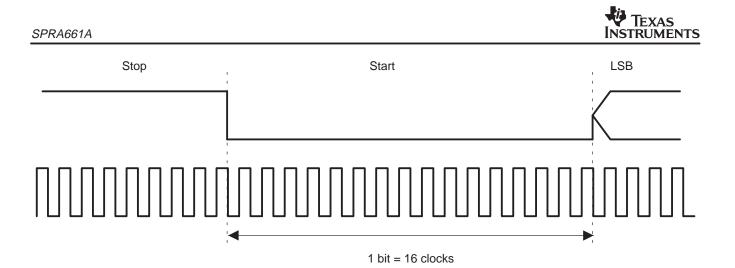

In an ideal case, the clock edges of the serial port line up with the bit edges of the data packet, there are exactly 16 clock periods for each bit in the packet, and the offset between the beginning of the start bit and the falling edge of the serial port clock is minimal. See Figure 3 for an example of this timing.

Figure 3. Timing of Signal Perfectly Synchronized to Serial Port Clock

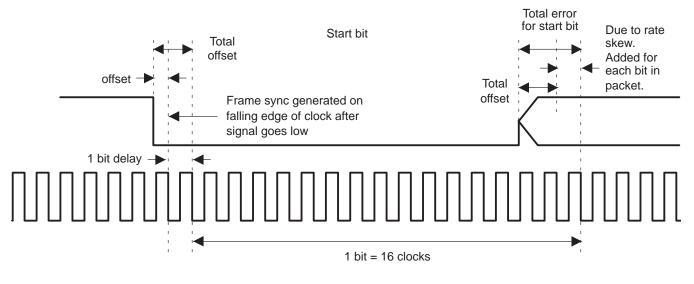

In the practical case, an offset between the beginning of the start bit and the clock's falling edge exists. The serial port must also be set for a data delay of 1, causing another clock period of offset. This offset is the same no matter how many bits are in the packet. The serial port clock will not generate exactly 16 periods per data bit because the divisor used to create the clock rate has limited resolution (integer) and cannot produce a clock of exactly the baud rate times 16. Therefore, the serial port clock may be slower or faster than 16 times the baud rate. This rate skew causes a timing error that is added for each bit in the packet. If the clock is too slow, there are less than 16 samples per data bit, causing the McBSP to possibly sample past the end of the stop bit and into the next start bit. Because the McBSP was ignoring frame syncs during this time, it misses the transition to the next start bit. The next frame sync is generated whenever another high to low transition is encountered, most likely in the middle of the next data word. See Figure 4 for an example of this more practical signal timing.

Note that the serial port clock is a little slower than the speed needed to oversample the data bits by 16

#### Figure 4. Timing of Signal with Offset and Rate Skew

To prevent start bits from being missed, the McBSP must run fast enough such that the last sample in the frame is confined to the stop bit. See Figure 5 for an example of the minimum speed of the McBSP.

Figure 5. McBSP Frame Restrictions

The minimum speed of the serial port should account for the maximum offset between the beginning of the start bit and the frame sync, the delay between the frame sync and first data sample, and the minimum time between the end of the frame and the next start bit. Given 16 samples per data bit, the equation is:

The units of measure are in seconds. This can be rearranged, as follows, with the delays and offsets now measured in number of serial port samples.

$$\left(16\frac{samples}{bit} * RxPKTBITS + offset + delay + extraFrameSyncSample\right) * samplelength < \frac{PKBITS}{baudrate}$$

(2)

The maximum offset is 1 sample, as is the delay. The extra frame sync sample in the left part of the equation is for the frame sync to reset before the next start bit edge, and is one sample in length. The sample length is the number of seconds per serial port sample, which is DIV/DSPCLK. We need to solve for the divisor (DIV).

$$DIV \leq \frac{PKTBITS * DSPCLK}{baudrate\left(16\frac{samples}{bit} * RxPKTBITS + 3\right)}$$

(3)

To get the most stringent limit, the most number of bits should be assumed to be in a packet with 1 stop bit. For example, given a baud rate of 19200, a DSPCLK of 75MHz and 17 packet bits (1 start, 14 data, 1 parity, 1 stop: PKTBITS=17, RxPKTBITS=16.5), we get:

$$DIV \le 248.71 \tag{4}$$

Which can only be encoded as an integer, so

$DIV \leq 248$

(5)

The decoding scheme will check the middle 4 bits of the received words, except for the ½ stop bit, which has its last 4 samples, tested. The maximum speed must ensure that the last 4 samples of the frame lie within the stop bit. This is the same as saying that the McBSP frame minus those 4 samples must fit within the packet bits prior to the stop bit. The limiting case would have an offset of 0 (still a delay of 1, though), so the equation is:

$$\left(16\frac{samples}{bit} * RxPKTBITS - 4 + delay\right) * \frac{DIV}{DSPCLK} \ge \frac{(PKTBITS - STOPBITS)}{baudrate}$$

(6)

or

$$DIV \ge \frac{(PKTBITS - STOPBITS) * DSPCLK}{baudrate * \left(16\frac{samples}{bit} * RXPKTBITS - 3\right)}$$

(7)

For the most stringent limit, assume the maximum number of bits in a packet (1 start, 14 data, 1 parity, 2 stop bits: PKTBITS=18, STOPBITS=2, RxPKTBITS=16.5). Or for the example above,

$$DIV \ge 239.46 \tag{8}$$

Which must be an integer

$$DIV \ge 240$$

(9)

Note that increasing the number of stop bits will increase the length of time between the end of the McBSP frame and the beginning of another start bit. This will raise the maximum DIV value because RxPKTBITS (only checks first half stop bit) remains the same, but PKTBITS increases. The maximum and minimum DIV values for common baud rates are listed in Table 1, as well as what the divisor should be to get the exact baud rate with 16 samples per bit. It is important to use a divisor as close to the exact baud rate as possible so that the UART transmits properly.

#### Table 1. Divisor Limits for Given Baud Rate and Clock Rate

|           | 75                 | MHz DSP Clo      | ock                | 100-MHz DSP Clock  |                  |                    |  |

|-----------|--------------------|------------------|--------------------|--------------------|------------------|--------------------|--|

| Baud Rate | Divisor<br>Minimum | Exact<br>Divisor | Divisor<br>Maximum | Divisor<br>Minimum | Exact<br>Divisor | Divisor<br>Maximum |  |

| 19200     | 240                | 244.14           | 248                | 320†               | 325.52†          | 331†               |  |

| 38400     | 120                | 122.07           | 124                | 160                | 162.76           | 165                |  |

| 57600     | 80                 | 81.38            | 82                 | 107                | 108.51           | 110                |  |

| 115200    | 40                 | 40.69            | 41                 | 54                 | 54.25            | 55                 |  |

<sup>†</sup> This divisor is too large to be used on the 54xx McBSP (max is 256)

In order to setup the McBSP, the transmit and receive channels, as well as the frame sync generator and clock generator, must be in reset when registers associated with that portion are written to. It is important to wait for at least 2 CLKG periods after putting that portion in reset or taking it out of reset. This allows time for internal synchronization of the McBSP. The McBSP registers are initialized to the settings in Table 2. See the *TMS320C54x DSP Enhanced Peripherals* guide for detailed information on the McBSP.

| Register | Bit Field | Value                       | Comment                                                                                                    |

|----------|-----------|-----------------------------|------------------------------------------------------------------------------------------------------------|

| SRGR1    | FWID      | 0                           | unused                                                                                                     |

|          | CLKGDV    | DIV-1                       | Generate clock period according to above Equations                                                         |

| SRGR2    | GSYNC     | 0                           | Sample rate clock free running                                                                             |

|          | CLKSP     | 0                           | Unused                                                                                                     |

|          | CLKSM     | 1                           | Sample rate clock derived from CPU clock                                                                   |

|          | FSGM      | 0                           | Transmit frame sync due to DXR-to-XSR copy                                                                 |

|          | FPER      | 0                           | unused                                                                                                     |

| SPCR1    | DLB       | 0                           | No loopback                                                                                                |

|          | RJUST     | 00                          | Right justify data                                                                                         |

|          | CLKSTP    | 00                          | Clock stop mode disabled                                                                                   |

|          | DXENA     | 0                           | DX enabler off                                                                                             |

|          | ABIS      | 0                           | A-bis mode disabled                                                                                        |

|          | RINTM     | 00                          | RINT driven by RRDY                                                                                        |

|          | RRST_     | 0                           | Receiver disabled                                                                                          |

| SPCR2    | FREE      | 0                           | FREE mode disabled                                                                                         |

|          | SOFT      | 1                           | SOFT mode enabled                                                                                          |

|          | FRST_     | 0                           | Frame sync generator in reset                                                                              |

|          | GRST_     | 0                           | Clock generator in reset                                                                                   |

|          | XINTM     | 00                          | XINT driven by XRDY                                                                                        |

|          | XRST_     | 0                           | Transmitter disabled                                                                                       |

| PCR      | XIOEN     | 0                           | No Tx pins used for GPIO                                                                                   |

|          | RIOEN     | 0                           | No Rx pins used for GPIO                                                                                   |

|          | FSXM      | 1                           | Transmit frame sync determined by FSGM                                                                     |

|          | FSRM      | 0                           | Receive frame sync generated by external device                                                            |

|          | CLKXM     | 1                           | CLKX is output driven by sample rate generator                                                             |

|          | CLKRM     | 1                           | CLKR is output driven by sample rate generator                                                             |

|          | FSXP      | 1                           | FSX is active low                                                                                          |

|          | FSRP      | 1                           | FSR is active low                                                                                          |

|          | CLKXP     | 0                           | Transmit data sampled on rising edge of CLKX                                                               |

|          | CLKRP     | 0                           | Receive data sampled on falling edge of CLKR                                                               |

| RCR1     | RFRLEN1   | RxPKTBITS-<br>RxHSTOPBITS-1 | Phase 1 of receive frame includes start bit, data bits, and parity bit (not half stop bit) (RxHSTOPBITS=1) |

|          | RWDLEN1   | 010                         | Words in phase 1 are 16 bits                                                                               |

#### Table 2. McBSP Initialization

| Register | Bit Field | Value                       | Comment                                                                                      |

|----------|-----------|-----------------------------|----------------------------------------------------------------------------------------------|

| RCR2     | RPHASE    | 1                           | Dual phase frames                                                                            |

|          | RFRLEN2   | RxHSTOPBITS-1               | Phase 2 of receive frame includes 1 half stop bit                                            |

|          | RWDLEN2   | 000                         | Words in phase 2 are 8 bits                                                                  |

|          | RCOMPAND  | 00                          | No companding                                                                                |

|          | RFIG      | 1                           | Ignore receive frame syncs during receive frame                                              |

|          | RDATDLY   | 01                          | 1-bit delay between FSR and data                                                             |

| XCR1     | XFRLEN1   | TxPKTBITS-<br>TxHSTOPBITS-1 | Phase 1 of transmit frame includes start bit, data bits, and parity bit (not half stop bits) |

|          | XWDLEN1   | 010                         | Words in phase 1 are 16 bits                                                                 |

| XCR2     | XPHASE    | 1                           | Dual phase frames                                                                            |

|          | XFRLEN2   | TxHSTOPBITS-1               | Phase 2 of receive frame includes half stop bits                                             |

|          | XWDLEN2   | 000                         | Words in phase 2 are 8 bits                                                                  |

|          | XCOMPAND  | 00                          | No companding                                                                                |

|          | XFIG      | 1                           | Ignore transmit frame syncs during transmit frame                                            |

|          | XDATDLY   | 00                          | 0-bit delay between FSX and data                                                             |

Table 2. McBSP Initialization (Continued)

## 5 DMA

The DMA is needed to shuttle data between memory and the McBSP without CPU intervention. Each time a complete packet is read in, the DMA will interrupt the DSP so it can process the received packet. Each time a packet is transmitted, the DMA will interrupt the DSP so it knows another packet may be sent out.

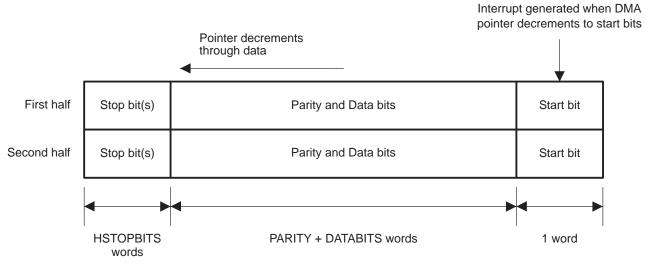

A new packet is received when the DMA has transferred RxPKTBITS words to a buffer from the McBSP DRR register, and a packet has been transmitted when the DMA moves TxPKTBITS words to the McBSP DXR register. The DMA can be set to transfer data from/to the McBSP when the RRDY/XRDY signal becomes active. Interrupts can be generated by the DMA either by setting the DMA to interrupt at the end of a block transfer (use autoinit or manually re-init the DMA) or by using ABU mode. We use ABU mode to preserve the autoinit registers for other uses. Each half of the receive and transmit buffers will hold one packet, and the DMA will interrupt when its pointer passes into each half.

There is one caveat to using ABU mode. On the 5410, if the pointer into the buffer is post-incremented, the interrupts will NOT occur on the half buffer points. Instead, when the pointer moves into the second half of the buffer the interrupt is not generated until it reaches the second word of that half. This is unlike the other TMS320C54xx processors, where the interrupt occurs when the pointer gets to the first word in each half. However, if the pointer is post-decremented, the interrupts do occur in the correct location. So, our buffers will be filled and emptied from back to front. See Figure 6 for a depiction of the buffer orientation. For the transmitter, HSTOPBITS (number of half-stop bits) is set by the user. For the receiver HSTOPBITS is always 1. Note that in autobuffering mode, the DMA buffers must be aligned on power-of-2 boundaries greater than the buffer size (i.e. buffer size of 16-31 must be on a 32 word boundary).

Figure 6. DMA Circular Buffers

Another issue arises due to the DMA triggering on XRDY and RRDY events. The DMA only recognizes the event if the DMA channel is enabled when that event occurs. If a DMA channel is disabled when the event occurs, and the DMA channel is subsequently enabled, it will not recognize that the event has occurred and it will need to be "kickstarted". The DMA receive channel is never disabled, so it will never need to be kickstarted. Kickstarting the DMA for transmit consists of manually writing a word to the McBSP and then enabling the DMA channel. When the McBSP writes out that word, it will generate the XRDY event again, this time with the DMA enabled. Note that the McBSP generates the XRDY and RRDY events when it is brought out of reset. Therefore, when the UART is started, the DMA should be enabled before the McBSP is brought out of reset.

On the receive side, the McBSP is constantly running and always has the DMA enabled. The DMA interrupts the DSP when a packet is read in and the DSP then decodes the oversampled packet and performs error checking. Note that the receive DMA channel only moves data into the buffer when the McBSP gets new frame syncs, which only occurs when a new packet is received. Because the DMA buffer has 2 halves, the receive data is double buffered.

The transmit side is a little more complicated. When the McBSP is out of reset, it is constantly clocking out data sent to it. If the DMA is enabled, it will continuously move data to the McBSP when XEVT (XRDY) occurs. Because a packet should only be transmitted when it is valid, either the DMA or the McBSP must be stopped until valid data is in the buffer.

Though stopping the McBSP seems like the best choice (i.e. no point in running the McBSP when not using it), latency issues in starting and stopping as well as issues with ensuring the entire data packet has been transmitted make it less desirable. For instance, when taking the McBSP transmitter out of reset, 2 serial port bit clocks must go by before it is running properly. The same is true when it is halted. If these times are not adhered to, the XRDY event is not properly generated, which causes the DMA to fail. Depending on the baud rate, 4 bit clocks between reset and running can be a very long time (i.e. almost 1000 DSP cycles for 19200 baud).

Also, a DMA transmit channel interrupt means the DMA has moved TxPKTBITS words to the McBSP. It does not mean the McBSP is finished transmitting all of the bits. When the DMA pointer moves into the next half of the buffer (generating the interrupt), it has just moved the last bit of the packet into the McBSP DXR (note the last 2 bits in the packet are always two 8 sample long stop bits). That means the second to last word in the packet has just moved into the XSR register. Therefore, there are 16 samples to transmit before the McBSP is done. We must wait until the McBSP DXR and XSR registers are empty before halting the McBSP, or these bits will be corrupted. That is 4000 cycles at a 19200 baud rate. These delays make this approach less desirable.

The approach we use is to halt the DMA transmit channel when there is no valid data. When the DMA transmit channel interrupts the DSP, it has just moved the last bit in the packet to the McBSP, and is therefore done with the packet. By halting the DMA now, the McBSP can still clock out the remaining bits without making the DSP wait. The only issue with this method is when to restart the DMA.

The DMA transmit buffer has 2 halves, allowing double buffering of the transmit data. As long as there is an empty half, more transmit data can be written into the buffer. If the DMA transmit channel generates an interrupt but there is still another word in the buffer to transmit, the DMA need not be disabled. However, if the DMA has just transmitted the last valid word in the buffer, the DMA must be halted and then restarted when a new transmission is desired.

If the DMA has been halted and a new packet is to be transmitted, we must restart the DMA, making sure it correctly catches the XRDY events. To sync the DMA to the XRDY event, the DMA must be kickstarted by manually writing the first data bit to the McBSP and then enabling the DMA. Because it is possible that the last packet still has a bit in the DXR register, we cannot write to DXR until we are sure it is empty. This is done by waiting until XRDY=1.

It may be possible to speed this process up by only kickstarting the DMA if XRDY=1 when we want to transmit (i.e. the DMA has missed the XRDY event). But, there is always the possibility that XRDY may toggle between our read of it and the enabling of the DMA, so it is safer to always kickstart it. For example, if XRDY=0, we may figure enabling the DMA now will ensure that it catches the XRDY event. However, if XRDY goes from 0 to 1 right after we check it and before we enable the DMA, we can miss the event anyway.

The DMA is initialized as in Table 3. See the *TMS320C54x DSP Enhanced Peripherals* guide for detailed information on the DMA.

| Table 3. | DMA | Initialization |

|----------|-----|----------------|

|----------|-----|----------------|

| Register   | Bit Field   | Value                | Comment                                                   |

|------------|-------------|----------------------|-----------------------------------------------------------|

| DMSRC (Rx) | DMSRC       | McBSPDRR1            | Get data from McBSP DRR register                          |

| DMDST (Rx) | DMDST       | RxBuffer+RxPKTBITS-1 | Start pointer at end of first half of buffer              |

| DMCTR (Rx) | DMCTR       | 2*RxPKTBITS          | Buffer length is twice the packet length                  |

| DMSFC (Rx) | DSYN        | REVT                 | Sync on RRDY for the McBSP (depends on which McBSP using) |

|            | DBLW        | 0                    | 16 bit words                                              |

|            | Frame Count | 0000000              | Unused                                                    |

| DMMCR (Rx) | AUTOINIT    | 0                    | Autoinit disabled                                         |

|            | DINM        | 1                    | Interrupt generated based on IMOD bit                     |

|            | IMOD        | 1                    | Interrupt at buffer full and half-full                    |

|            | CTMOD       | 1                    | ABU mode                                                  |

|            | SIND        | 000                  | Source address not modified                               |

|            | DMS         | 01                   | Source address in data space                              |

|            | DIND        | 010                  | Destination address post-decremented                      |

|            | DMD         | 01                   | Destination address in data space                         |

| DMSRC (Tx) | DMSRC       | TxBuffer+TxPKTBITS-1 | Start pointer at end of first half of buffer              |

| DMDST (Tx) | DMDST       | McBSPDXR1            | Put data into McBSP DXR register                          |

| DMCTR (Tx) | DMCTR       | 2*TxPKTBITS          | Buffer length is twice the packet length                  |

| DMSFC (Tx) | DSYN        | XEVT                 | Sync on XRDY for the McBSP (depends on which McBSP using) |

|            | DBLW        | 0                    | 16 bit words                                              |

|            | Frame Count | 0000000              | unused                                                    |

| DMMCR (Tx) | AUTOINIT    | 0                    | Autoinit disabled                                         |

|            | DINM        | 1                    | Interrupt generated based on IMOD bit                     |

|            | IMOD        | 1                    | Interrupt at buffer full and half-full                    |

|            | CTMOD       | 1                    | ABU mode                                                  |

|            | SIND        | 010                  | Source address post-decremented                           |

|            | DMS         | 01                   | Source address in data space                              |

|            | DIND        | 000                  | Destination address not modified                          |

|            | DMD         | 01                   | Destination address in data space                         |

When the UART is started, the McBSP and DMA are initialized as in Table 2 and Table 3. To start the UART, the DMA must have the receive channel enabled and make sure the correct interrupts are selected from the multiplexed interrupts. This is done in the DMPREC register. Depending upon which DMA channel is used for reception, its enable bit must be set and the proper interrupt selection must be made so that the DMA receive and transmit channels have their interrupts generated. For example, DMA channel 4 can be used for receive and DMA channel 5 for transmit, which means DPREC must be set to 0x0010 to enable the receive channel and INTOSEL set to 00 (selects DMA channels 4 and 5 to have interrupts). The interrupt vector table must of course be appropriately setup to handle these interrupts.

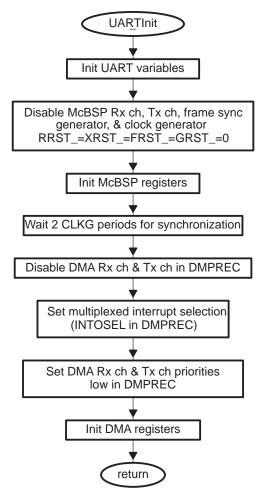

The DMA channels should be disabled before they are setup. See Figure 7 for a depiction of the overall initialization process.

Figure 7. UART Initialization

#### 6 Transmit Process

There are two portions to the transmit process: how to place a new packet in the transmit buffer, and what to do when a packet has just been transmitted. The first case is taken care of whenever the user calls the routine to perform a transmit (\_UARTTxChar). The second occurs in the DMA transmit channel ISR (\_UARTDMATxISR).

#### 6.1 Procedure at Start of Transmission

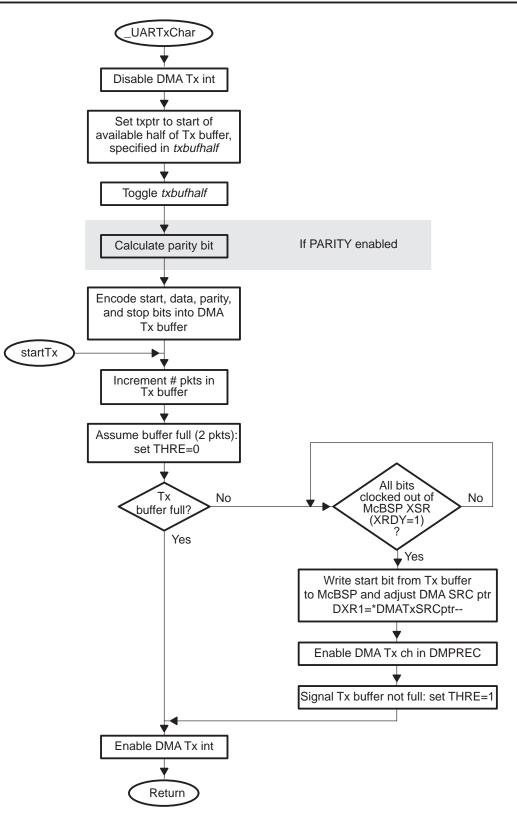

The flow to create a new packet for transmission is depicted in Figure 8.

The transmission routine should not be entered into unless there is space in the transmit buffer, verified by polling THRE (Transmit Holding Register Empty) for a 1. Entering the routine with THRE equal to 0 will disrupt the transmission process, causing the DMA pointer to be aligned improperly.

To put a new packet in the buffer, the next available half of the buffer is first checked from a flag (*txbufhalf*).

If parity is to be generated, a routine that calculates the parity bit is called. The parity bit is generated based on a successive approximation scheme. This method is detailed in the Texas Instruments Application Brief, *Parity Generation on the TMS320C54x* by David Nerge. The parity bit is added above the data bits.

Next, each bit in the packet is encoded and placed in the transmit buffer. The encoding of the bits is a simple process; 0xFFFF replaces a 1, and 0x0000 replaces a 0. The start bit is written to the end of the DMA buffer half, followed by the data bits and the parity bit (if used). Finally, the stop bits (in 8 bit words) are added. So a packet of 1 start bit, 8 data bits, and 1 stop bit will require 11 words in the buffer half (stop bit has two 8 bit halves).

If there is another packet in the buffer which has not yet been fully transmitted (i.e. with the addition of the new packet, there are now 2 packets), then the DMA transmit ISR has not disabled the DMA. In this case, nothing else needs to be done. The DMA will continue to output the new packet when it has finished outputting the old packet. Because there are 2 packets in the buffer, the THRE flag is cleared to indicate that it is full. This flag should be consulted before every call to the transmit routine to ensure space exists in the buffer.

If there is not another older packet to transmit in the buffer, then the DMA transmit ISR has shut down the DMA, and it will need to be kickstarted by writing to DXR. The DXR register cannot be written to until all bits of the previous packet still in the DXR register are shifted out. This can be checked by waiting until XRDY=1. When that occurs, the start bit is written to DXR, the DMA pointer is decremented to the first data bit, and the transmit DMA channel is enabled.

Note that the DMA transmit interrupt was disabled during this routine to prevent it from occurring between the increment of the number of packets in the transmit buffer and the check of the number of packets. If the number of packets was incremented to 2 (full buffer) and then a DMA transmit interrupt occurred, the ISR would decrement the number of packets but would not disable the DMA because it still sees another packet in the buffer. When the ISR returns, the transmit routine sees only 1 packet in the buffer, so it thinks it needs to restart the DMA, even though it was never disabled. This will cause a problem because the DMA will start moving the new packet to the McBSP, but the kickstart of the DMA would overwrite the data. Disabling the DMA transmit interrupt prevents this from happening.

Figure 8. Procedure at Start of Transmission

#### 6.2 Procedure at End of Transmission

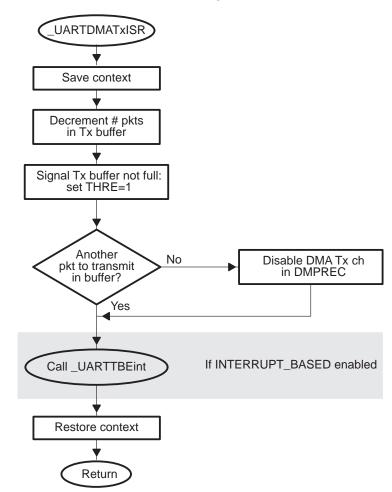

The second transmission case occurs when a packet has been completely read out of the DMA transmit buffer, freeing up space for another transmission. When this occurs, the DMA transmit channel ISR is entered. See Figure 9 for a depiction of the flow of this routine.

When the DMA transmit channel interrupts the DSP, a packet has been completely read out by the DMA. The interrupt service routine that is subsequently entered must check if any more packets are ready for transmission, and if not, disable the DMA.

First, the number of transmit packets in the DMA buffer is decremented.

Then, the status of the transmitter is always set to THRE equals 1, as there must be an available space in the transmit buffer now that a packet has been removed.

If the number of transmit packets is now 0, there is no more data to transmit, so the DMA is disabled in DMPREC.

Finally, if the INTERRUPT\_BASED mode is enabled, the \_UARTTBEint routine is called, allowing the user to process a transmit event during the ISR.

Figure 9. Procedure at End of Transmission

## 7 Receive Process

As with the transmit process, there are two cases for reception: what to do when a new packet has just been received, and how to read out a packet from the buffer. The first case is taken care of by the DMA receive channel interrupt service routine whenever a new packet is received (\_UARTDMARxISR). The second case takes place whenever the user calls a routine to read a packet from the buffer (\_UARTRxChar).

#### 7.1 Procedure When Packet Received

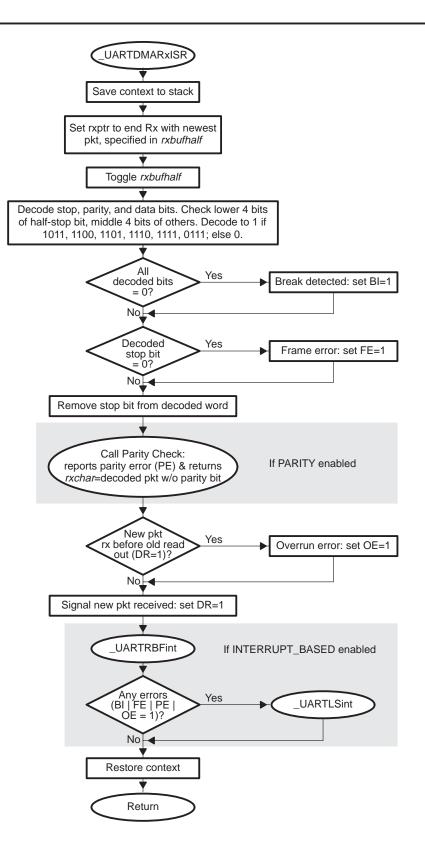

When the DMA has moved an entire packet of data into its receive buffer, it interrupts the DSP. The ISR associated with this must decode the received packet from the oversampled version into one word of data and perform any necessary error checking. This is depicted in Figure 10.

First, the buffer half with the newly received packet is determined by checking rxbufhalf.

Next, the bits are decoded. Only the lower (last) 4 samples of the half stop bit are checked to decode it. The other bits in the packet have their middle 4 samples checked.

The decoding routine must account for the rate skew in the signal. A 16-bit word may contain only a portion of a data bit, so the decoder needs to manage this shifting of the samples. The word is decoded to a 1 if the middle four samples are 1100b, 1110b, 1111b, or 0111b. This accounts for the shifting of the data. Also, to simplify the decoder 1101b and 1011b are decoded to a 1. These patterns should not occur, as there should be approximately 16 samples in a row with the same value. Unless noise on the line corrupts a sample, 1101b and 1011b will never be received. Any other pattern is decoded as a 0.

The decoded bits are compiled into a decoded word and are stored in the *rxchar* variable. The data bits are in the lowest part of the word, followed by the parity bit and stop bit.

Next, error checking is performed. The different conditions checked are framing errors, break indications, parity errors and overrun.

A framing error is detected if the stop bit was not present (i.e. not decoded as a 1). The framing error (FE) flag is set if this is the case.

A break is detected if all of the bits in the packet are zero. This includes the data, parity and stop bits. The start bit is not checked, as it must be zero for the word to be received. The break indicator (BI) flag is set when a break is detected.

A parity error is detected if the parity of the received word does not match the parity setting of the UART. If there is a parity error (PE), a flag is set in the status register.

Overrun occurs if the last packet received has not been read out and another packet is received and decoded. If an overrun error occurs (OE), a flag is set in the status register.

The data ready flag (DR) is set to note that there is a new packet ready that has not been read by the user yet.

Finally, If the INTERRUPT\_BASED mode is enabled, the \_UARTRBFint routine is called, allowing the user to process a receive event during an ISR. If any of the status bits were set during reception (OE|FE|PE|BI), the \_UARTLSIint routine is called so that the user can perform any error handling routines in the receive ISR. None of the status bits are cleared (except DR and THRE) by the code. It is the user's responsibility to handle these error conditions.

Figure 10. Procedure When Packet Received

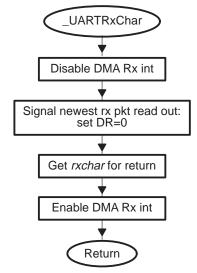

## 7.2 Procedure To Read Received Packet

The receive routine simply reads the character from *rxchar* and resets the DR flag. This routine should only be entered if DR is a 1. See Figure 11 for a graphical depiction.

Figure 11. Procedure to Read Received Packet

The DMA receive interrupt is disabled during the receive routine to prevent this interrupt from occurring between the clearing of DR and the return of the character. If a new receive interrupt did occur at that point, the receive data would be overwritten but an overrun error would not be noted because DR was 0. Since the DR flag would be set by the ISR, the same data would then be read out a second time once this routine returned.

## 8 Overview of Code

The code supporting this report implements the UART in the manner described by the document, except for a couple exceptions.

Though this report details the case where the DMA pointers are post-decremented, the code provides a way to use the DMA with post-incremented pointers, if desired. This is selected with the DMA\_PTR\_MOD equate in the *UARTsetup.inc* file. Note that if the 5410 is used, the pointers must be post-decremented in order for the UART to work properly.

Also, the DMA in ABU mode on the 5402 works differently than that of the 5410. It generates early DMA interrupts if the DMA pointer is started in the second half of the DMA buffer. For this reason, the code provides a selectable workaround, which ensures the DMA is only restarted with the pointer in the first half of the buffer. This workaround is selected with the DMA\_ABU\_FIX equate in the *UARTsetup.inc* file.

There are 11 equates, 1 public variable, 10 private variables, 12 public routines, and 2 private routines in the code. The public routines are all C-callable. All routines are written in C54x assembly code.

## 9 Equates

## 9.1 MCBSP\_CHOICE

McBSP to use for UART (0-2, depending on 54xx choice).

#### 9.2 DMA\_RX\_CHOICE

DMA channel to use for receive (0-5).

#### 9.3 DMA\_TX\_CHOICE

DMA channel to use for transmit (0-5). Must be different than DMA\_RX\_CHOICE.

#### 9.4 INTOSEL

Selection of DMA/McBSP multiplexed interrupts (0-3). The choices are device dependent and specified in the *TMS320C54x DSP Enhanced Peripherals*<sup>(2)</sup> guide.

#### 9.5 PARITY

Specifies the type of parity checked and generated (0=no parity, 1=even, 2=odd, 3=mark, 4=space).

#### 9.6 HSTOPBITS

Number of 1/2 stop bits (2,3 or 4) used in transmission. Gives either 1,1.5, or 2 stop bits.

#### 9.7 DATABITS

Number of data bits (1-14 with parity, or 1-15 w/o parity) in each packet.

#### 9.8 BAUDRATE

Baud rate divisor used to divide down CPU clock to get McBSP clock. Should be approximately DSPCLK/(16\*baudrate). See equations 3 and 7.

#### 9.9 INTERRUPT\_BASED

Gives the user the option to process the UART events within the DMA receive and transmit ISRs (0=only use polling to check status of UART, 1=run ISR's for the interrupt events on UART).

#### 9.10 DMA\_PTR\_MOD

Direction for DMA pointer modification (0=post-decrement, 1=post-increment). 5410 can only use post-decrement in order for each character to be properly processed.

#### 9.11 DMA\_ABU\_FIX

Adds workaround for ABU difference in 5402 (0=no fix, 1=add fix). Difference occurs when DMA ABU started with DMA pointer in second half of buffer. The workaround ensures the DMA pointer is never started in the second half.

#### **10** Public Variables

#### 10.1 \_UARTLSR

The software UART reports status to the DSP through the UART Line Status Register. This register is organized as in Figure 12.

|          | 15       | 6 | 5    | 4  | 3  | 2  | 1  | 0  |

|----------|----------|---|------|----|----|----|----|----|

| _UARTLSR | Reserved |   | THRE | BI | FE | PE | OE | DR |

#### Figure 12. UART Status Register

The bit definitions are:

• DR - Data Ready

Set when a new packet is received and decoded by the UART. Cleared when the \_UARTRxChar routine is called. This bit should be polled prior to calling the \_UARTRxChar routine to determine if a new character is available.

• OE - Overrun Error

Set when another packet is received by the UART before the previous packet was read out. This bit must be manually cleared.

• PE - Parity Error

Set when the parity of the received packet does not match the settings in the UART. This bit must be manually cleared.

• FE - Framing Error

Set when an invalid stop bit is detected. This bit must be manually cleared.

BI - Break Indicator

Set when a break is detected. This bit must be manually cleared.

• THRE - Transmit Holding Register Empty

Set when space is available in the transmit buffer for another packet. Cleared by the \_UARTTxChar routine if the transmit buffer is filled (2 packets). This bit should be polled prior to calling the \_UARTTxChar routine to determine if a new packet can be sent.

## **11 Private Variables**

#### 11.1 rxchar

Holds the last character received by the UART.

#### 11.2 rxbufhalf

A flag signaling the valid half of the DMA receive buffer (the half with the newest packet). It is 0 for the first half and 1 for the second half. For post-decremented DMA pointers, the first half is the half at the higher addresses. For post-incremented pointers, the first half is the half at the lower addresses.

#### 11.3 txbufhalf

A flag signaling the valid half of the DMA transmit buffer (the next half to write in). It is 0 for the first half and1 for the second half. For post-decremented DMA pointers, the first half is the half at the higher addresses. For post-incremented pointers, the first half is the half at the lower addresses.

#### 11.4 numTxPkts

Holds the number of packets currently in the transmit buffer. The maximum number is 2. Used by the transmit routine to determine when to disable the DMA transmit channel (when *numTxPkts* decrements to 0) and when the buffer is full (when *numTxPkts* increments to 2). THRE is cleared to 0 whenever *numTxPkts* becomes 2.

#### 11.5 TxBuffer[2\*TxPKTBITS]

The DMA transmit buffer. It has a size of 2\*TxPKTBITS and must be aligned on a 2<sup>n</sup> word boundary greater than 2\*TxPKTBITS.

#### 11.6 RxBuffer[2\*RxPKTBITS]

The DMA receive buffer. It has a size of 2\*RxPKTBITS and must be aligned on a 2<sup>n</sup> word boundary greater than 2\*RxPKTBITS.

#### 11.7 decoderMask

Used in decoding routine to mask out center samples for testing. Saves cycles to use a variable rather than an immediate value.

#### 11.8 mask1011b

Used in the decoding routine to determine if bit is 1 or 0. Saves cycles to use a variable rather than an immediate value.

#### 11.9 mask0100b

Used in the decoding routine to determine if bit is 1 or 0. Saves cycles to use a variable rather than an immediate value.

#### 11.10 one

Used in the decoding routine to create decoded character. Saves cycles to use a variable rather than an immediate value.

## **12 Public Routines**

#### 12.1 \_UARTInit(inputs: none; outputs: none)

Initializes the software UART, specifically the McBSP, DMA, and decoder variables. Should be run once prior to running \_UARTStart for the first time. See Figure 7.

#### 12.2 \_UARTStart(inputs: A<0:start Rx, A==0:start Rx & Tx, A>0:start Tx; outputs: none)

Starts the software UART. Takes A as an input to determine if transmit (A>0), receive (A<0) or both (A=0) should be started. Initializes the status register and enables global interrupts. For transmit or receive, enables the McBSP clock generator, initializes the valid half of the DMA buffer, sets the DMA pointer to the end of the first half of the buffer, enables the DMA transmit/receive channel interrupt in the IMR register, and takes the McBSP transmit/receive channels out of reset. For transmit, also zeros out the number of packets in the transmit buffer. For receive, also enables the DMA Rx channel in DMPREC. This routine may be run whenever the UART is to be restarted (i.e. after the \_UARTStop or \_UARTInit routines). See Figure A–1 in Appendix A.

## 12.3 \_UARTStop(inputs: A<0(stop Rx), A==0(stop Rx & Tx), A>0(stop Tx); outputs: none)

Stops the UART. Takes A as an input to determine if transmit (A>0), receive (A<0) or both (A=0) should be stopped. For transmit, waits until all packets in the transmit buffer are transmitted. For transmit or receive, disables the DMA transmit/receive interrupt and channel and puts the McBSP transmit/receive ports in reset. If both receive and transmit are stopped, it disables the McBSP clock generator. Use \_UARTStart to restart the UART. This routine should not be called from within an ISR, as it requires interrupts to be enabled in order to run properly. See Figure A–2 in Appendix A.

## 12.4 \_UARTSetBaudRate(inputs: A=clock divisor; outputs: none)

Sets a new baud rate for the UART. Divisor must be in accumulator A on entry and must conform to equations 3 and 7. The UART (receive and transmit) must be stopped using \_UARTStop before this routine can be run. See Figure A–3 in Appendix A.

#### 12.5 \_UARTSetBreak(inputs: A!=0:send break, A==0:end break; outputs: none)

Sends a break to the receiver. With a non-zero input, sends a packet of all 0's with the stop bit set to 0. With an input of zero, sends a string of 1's. To send a long break, loop over this routine with a non-zero input for as many packet lengths as the break is desired to be, then call again with an input of zero to end the break. It is necessary to end the break by sending a string of 1's so that the line goes high before a new character is sent. If the line didn't go high, the next character will be misinterpreted because its start bit will be missed. This routine should only be called when THRE is 1, indicating space available for another transmit packet. See Figure A–4 in Appendix A.

#### 12.6 \_UARTTxChar(inputs: A=char to transmit; outputs: none)

Transmits a character given in accumulator A. Adds start, stop and parity bits and stores the oversampled data in the valid half of the DMA transmit buffer. The DMA transmit channel is appropriately enabled, as specified in Figure 8. This routine should only be called when THRE is 1, indicating space available for another transmit packet.

#### 12.7 \_UARTRxChar(inputs: none; outputs: A=last received char)

Receives the newest character. Returns the last character read and resets the DR flag. This routine should only be called when DR is 1, indicating a new packet has been received. See Figure 11 for a description of the process.

#### 12.8 \_UARTDMATxISR(inputs: none; outputs: none)

Must be branched to from the DMA channel interrupt vector used for the transmit channel. Entered when the DMA sends a packet. Sets the THRE flag and disables the DMA transmit channel if no more packets are in the transmit buffer. See Figure 9 for a description of the process.

#### 12.9 \_UARTDMARxISR(inputs: none; outputs: none)

Must be branched to from the DMA channel interrupt vector used for the receive channel. Entered when the DMA receives a new packet. Decodes the received bits, checks for error conditions, stores the received character to *rxchar*, and sets the DR flag. See Figure 10 for a description of the process.

#### 12.10\_UARTRBFint(inputs: none; outputs: none)

Called from \_UARTDMARxISR if INTERRUPT\_BASED mode is enabled, allowing receive event processing within an ISR. \_UARTRxChar may be called from within this routine to receive a new character. Because it is run from within an ISR, the context must be saved and restored within this routine.

#### 12.11 \_UARTTBEint(inputs: none; outputs: none)

Called from \_UARTDMATxISR if INTERRUPT\_BASED mode is enabled, allowing transmit event processing within an ISR. \_UARTTxChar or \_UARTSetBreak may be called from within this routine to send a new character. Because it is run from within an ISR, the context must be saved and restored within this routine.

#### 12.12\_UARTLSIint(inputs: none; outputs: none)

Called from \_UARTDMARxISR if INTERRUPT\_BASED mode is enabled, allowing error condition processing within an ISR. Because it is run from within an ISR, the context must be saved and restored within this routine.

## **13 Private Routines**

## 13.1 ParityCalc(inputs: A=received char (data & parity bits only); outputs: TC=0 (even parity), TC=1(odd parity))

Performs parity calculation using the successive approximation technique described in the Texas Instruments Application Brief, *Parity Generation on the TMS320C54x*<sup>(3)</sup> by David Nerge. The TC bit will equal 1 if the current parity is odd, and 0 if the current parity is even.

## 13.2 ParityCheck(inputs: A=received char (data & parity bits only); outputs: AL=received char (data bits only))

Checks the parity of the received word against the parity setting of the UART and strips off the parity bit. Invalid parity is reported in the PE status bit.

## 14 Usage of UART Code

The UART routines are contained in *uart.asm*, located in Appendix B. The routines are all C callable.

There is an include file with the UART code (*UARTsetup.inc* in Appendix C) in which parameters of the code must be set. These include choices of the McBSP to use, the DMA channels to use, the type of parity to generate and detect (if any), the baud rate divisor, the number of stop and data bits, and whether to use polling or interrupt mode.

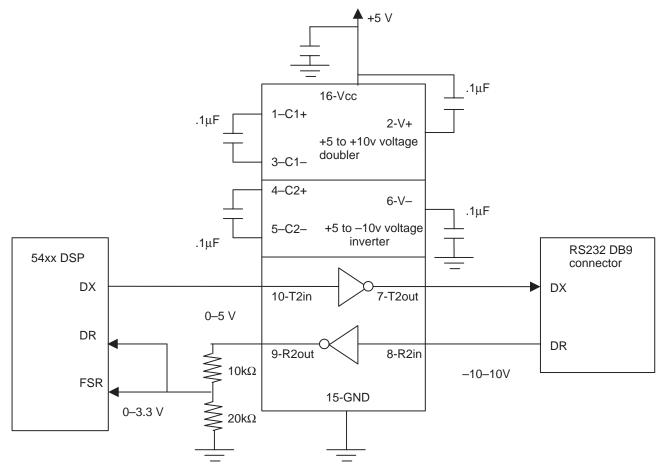

An example of using the software UART is included in the files *ExampleC.asm* in Appendix D (C code interface) and *ExampleASM.asm* in Appendix E (ASM code interface). An example interrupt vector table is included in *vectors.asm*, in Appendix F. An example command file is included in *uart.cmd*, in Appendix G. The example files perform a loopback of received data and were tested by hooking up an RS232 interface to a PC running HyperTerminal (see the RS232 Connections section for more information on the hookup). If any error is received, the UART generates a break back to the host.

The PLL and processor are initialized before starting the UART. See the *TMS320C54x DSP CPU and Peripherals*<sup>(4)</sup> guide for information on the PLL and interrupts. See the *TMS320C54x DSP Enhanced Peripherals*<sup>(2)</sup> guide for detailed information on choosing which DMA channel and McBSP is available for your particular device, as well as which interrupts are multiplexed and how they are selected in INTOSEL.

Then, the \_UARTInit routine is called. Once this is done, calling \_UARTStart with A=0 will enable the UART to start receiving and transmitting packets.

There are two types of examples in the code. One uses a polling method to transmit and receive characters; the other uses an interrupt method.

For the polling method, to transmit a character, first check that the THRE bit in *\_UARTLSR* equals 1. If so, load the character to accumulator A and call *\_UARTTxChar*.

To receive a new character, check that the DR bit in *\_UARTLSR* equals 1 and then call \_UARTRxChar. The new character is returned in accumulator A.

For the INTERRUPT\_BASED mode, to transmit a block of characters, the first two characters in the buffer are manually written by calling the transmit routine twice (fills the transmit buffer). The ISR writes a new character to the buffer whenever space opens up, keeping the UART at the maximum transmit rate (consecutive characters). When the buffer is emptied, the ISR exits without transmitting a new character. No more interrupts will occur after that, which is why the first characters must be manually written.

The receive ISR writes the characters into a buffer automatically. A variable is used to check how many characters are in the buffer and perform different routines based on this number.

To halt the UART, call \_UARTStop with A=0.

## 15 Performance

#### 15.1 Memory

The memory used by the UART code depends on the number of total bits in a packet and especially whether parity generation and detection is enabled, as these are compile-time options. The approximate size in words, assuming the DMA ABU Fix is not used, is given in Table 4.

|             | Not Interru | pt Based | Interrupt Based |        |  |  |

|-------------|-------------|----------|-----------------|--------|--|--|

| Memory Type | No Parity   | Parity   | No Parity       | Parity |  |  |

| Program     | 414         | 439      | 422             | 447    |  |  |

| Data        | 15+4D+4P+4S |          |                 |        |  |  |

#### Table 4. UART Memory Consumption

D=#data bits, S=#stop bits, P=1 if parity enabled Memory consumption is measured in words (1 word=2 bytes)

#### 15.2 Cycle Count

The number of cycles each UART routine consumes, with no DMA ABU fix, is listed in Table 5.

|                      | Not Interrupt Based |                      |  |  |  |  |

|----------------------|---------------------|----------------------|--|--|--|--|

| Routine              | Maximum Data Rate   | Individual Char Sent |  |  |  |  |

| _UARTInit            | 759                 | 759                  |  |  |  |  |

| _UARTStart (rx & tx) | 1096                | 1096                 |  |  |  |  |

| _UARTStop (rx & tx)  | 583                 | 583                  |  |  |  |  |

| _UARTSetBaudRate     | 10                  | 10                   |  |  |  |  |

| _UARTSetBreak        | 45+D+P+2S           | 72+D+P+2S*           |  |  |  |  |

| _UARTTxChar          | 43+7D+28P+2S        | 71+7D+28P+2S*        |  |  |  |  |

| _UARTRxChar          | 15                  | 15                   |  |  |  |  |

| _UARTDMATxISR        | 22                  | 22                   |  |  |  |  |

| _UARTDMARxISR        | 74+10D+42P          | 74+10D+42P           |  |  |  |  |

| ParityCalc           | 14                  | 14                   |  |  |  |  |

| ParityCheck          | 14                  | 14                   |  |  |  |  |

Table 5. UART Routine Cycle Counts

D=#data bits, S=#stop bits, P=1 if parity enabled

\* Will take longer if bits of prev char still being transmitted by McBSP

In Table 5, the Maximum Data Rate is achieved when characters are transmitted consecutively, with no idle time on the data lines. The extra savings in cycle count is achieved due to the fact that the UART does not need to shut down and restart the DMA transmit channel.

From Table 5, it can be seen that to transmit consecutive packets with 8 data bits, 1 stop bit and with parity enabled (total of 11 bits with start bit) will cost 129+22=151 cycles per packet, or 151/11=13.7 cycles/bit. At 19200 baud rate that is 13.7\*19200=0.26 MIPS. At 115200 baud rate that is 1.58 MIPS.

To receive a packet of 8 data bits, 1 stop bit and with parity enabled will cost 15+196=211 cycles per packet, or 211/11=19.2 cycles/bit. At 19200 baud rate that is 18.7\*19200=0.37 MIPS. At 115200 baud rate that is 2.21 MIPS.

The cycles and MIPS for the UART transmit and receive processes are displayed in Table 6.

|       |         |       |                 |         | MIPS     |             |          |         |