# TMS320 Cross-Platform Daughtercard Specification Revision 1.0

Dave Bell

Digital Signal Processing Solutions

#### ABSTRACT

A standard has been established for daughtercards made to function with TMS320C6000<sup>™</sup> and TMS320C5000<sup>™</sup> systems. The daughtercard specification is based on the interfaces provided with several existing DSP motherboards: the TMS320C6201 EVM, TMS320C6201 McEVM, TMS320C6701 EVM, TMS320C6211 DSK, TMS320C6711 DSK, TMS320C5402 DSK, and TMS320C6202 EVM. The document is divided into two primary sections: existing interfaces and future interfaces. The focus of the first section is to clearly document what is present on the motherboards that exist today as well as how to design a daughtercard that is compatible with all or some of these motherboards. The second section sets guidelines for how to move forward with designing new DSP motherboards aiming to provide a compatible interface. This specification is necessary to allow daughtercards to be designed to function with as many systems as possible. This includes systems based on different DSPs as well as systems from different vendors. The layout of a daughtercard is specified such that a card may reside within a PC chassis when attached to a PCI motherboard, though the interface is not restricted to PCI platforms. Signals are brought to the daughtercard through two 80-pin headers, with one header primarily for peripheral signals and the other primarily for the external memory interface. The daughtercard interface on the DSP motherboard has several set requirements concerning signal drive, timing delay, and voltage tolerance. Daughtercards designed with knowledge of the possible different interfaces available can be guaranteed to work on any C6000<sup>™</sup> or C5000<sup>™</sup> system designed to this specification. However, it is important for the engineer building the daughtercard to design logic, perform timing analysis, and develop software drivers considering the differences between the DSP interfaces and development boards (Evaluation Modules (EVMs) and DSP Starter Kits (DSKs)).

TMS320C6000, TMS320C5000, C6000, and C5000 are trademarks of Texas Instruments.

#### Contents

| 1 | Introduction                                      | 2  |

|---|---------------------------------------------------|----|

| 2 |                                                   |    |

|   | 2.1 Physical Layout                               |    |

|   | 2.2 Existing Interfaces                           |    |

|   | 2.3 Existing Interface Summary                    |    |

|   | 2.4 Memory Interface                              | 16 |

|   | 2.5 Physical Daughtercard Layout                  | 20 |

|   | 2.6 Daughtercard Connectors and Component Height  | 21 |

|   | 2.7 Stackable Daughtercards                       | 22 |

|   | 2.8 Daughtercard Design for Existing Motherboards | 22 |

|   | 2.9 Daughtercard Signals                          | 27 |

|   | 2.10 Signal Characteristics                       | 27 |

| 3 | Future Daughtercard Interfaces |  |

|---|--------------------------------|--|

|   | 3.1 Interface Signals          |  |

|   | 3.2 Signal Characteristics     |  |

|   | 3.3 Power Supply               |  |

|   | 3.4 Physical Requirements      |  |

| 4 | Summary                        |  |

### **List of Figures**

## List of Tables

| Table 1. | TMS320C6201 EVM Peripheral Connector (J2) Pinout  | 5 |

|----------|---------------------------------------------------|---|

|          | TMS320C6201 EVM Memory Connector (J1) Pinout      |   |

|          | TMS320C6211 DSK Peripheral Connector (J2) Pinout  |   |

|          | TMS320C6211 DSK Memory Connector (J1) Pinout      |   |

|          | TMS320C6711 DSK Peripheral Connector (J2) Pinout  |   |

|          | TMS320C6711 DSK Memory Connector (J1) Pinout      |   |

|          | PCI/C6202-EVM Peripheral Connector (J2) Pinout    |   |

|          | PCI/C6202-EVM Memory Connector (J1) Pinout        |   |

|          | TMS320C5402 DSK Peripheral Connector (J2) Pinout  |   |

|          | TMS320C5402 DSK Memory Connector (J1) Pinout      |   |

|          | Existing Daughtercard Interface Features          |   |

|          | Daughtercard Interface Connector Part Numbers     |   |

|          | PCI Motherboard and Daughtercard Component Height |   |

|          | Stacked Daughtercard Component Height             |   |

|          | Peripheral Signal Descriptions                    |   |

|          | EMIF Signal Descriptions                          |   |

|          | Minimum Power Supply Requirements                 |   |

|          |                                                   |   |

# 1 Introduction

The basis for the common TMS320 daughtercard interface was the interface implemented on the Texas Instruments TMS320C6201 EVM. This EVM provided daughtercard connectors with signals for the asynchronous memory interface of the EMIF and most on-chip peripheral signals, allowing developers to design interfaces without designing an actual DSP board. This interface provides a cost-effective way to prototype a system.

Since this time, several DSP products have been created with similar interfaces. As other C6000 development platforms are being brought to market, along with similar platforms for the C5000 DSPs, commonalties in the daughtercard connectors allow daughtercards designed for one motherboard to be used on the others.

This application report documents details on how to design a daughtercard to work with all or some existing DSP development boards, as well as how to design DSP boards with compatible interfaces.

The TMS320 daughtercard standard applies to all of the C6000 and C5000 devices. The daughtercard interface allows communication to asynchronous memory or I/O peripherals, serial port interfaces, timers, multiple interrupts, and general-purpose I/O. This specification describes the several existing interfaces that provide slightly different capabilities, as well as details on how to design a daughtercard to connect to all of them. A recommended signal placement is also presented for future development boards, along with details on signal characteristics and power requirements.

# 2 Existing Daughtercard Interfaces

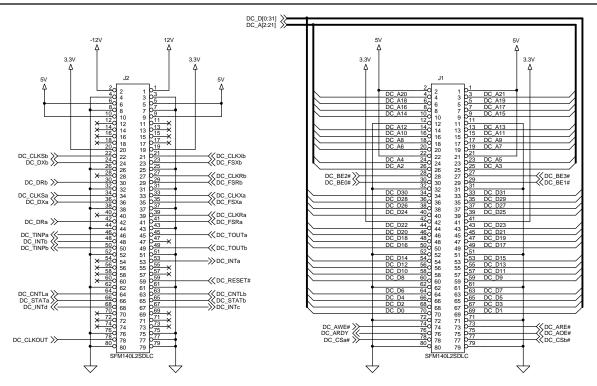

The daughtercard interfaces on all existing DSP motherboards consist of two 80-pin headers. One header contains the memory interface signals, while the other contains peripheral signals. The dimensions of the daughtercard layout area are designed to facilitate being incorporated on a PCI card within a PC chassis. The interface is not intended to be restricted to such platforms, however. Any DSP board can be equipped with a compliant daughtercard interface provided that the signal pinout and physical requirements are met.

# 2.1 Physical Layout

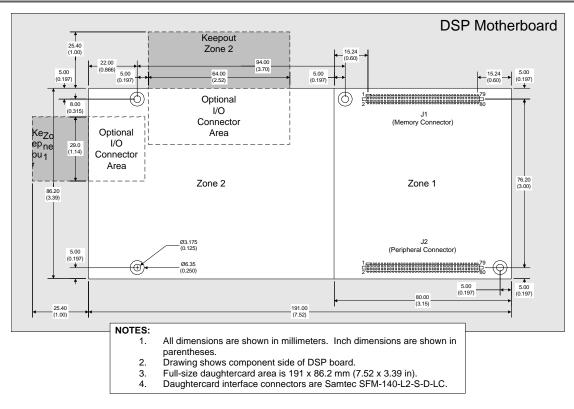

The layout of the daughtercard interface on a DSP motherboard is shown in Figure 1. Note that the layout shows the top of the DSP board and *not* the daughtercard<sup>1</sup>. The diagram shows the physical dimensions of the daughtercard area and the placement of the daughtercard connectors. The daughtercard interface on the DSP motherboard consists of two 80-pin connectors from Samtec. The part number for the connectors is SFM-140-L2-S-D-LC. Details on the required mating connectors on the daughtercard are provided in the daughtercard section. The DSP motherboards all support daughtercards that have dimensions up to 191 x 86.2mm (7.52 x 3.39in). This in no way affects the size requirement of the motherboard itself. It is possible that the motherboard only be large enough to accommodate the daughtercard connectors, so long as the mounted components meet the height restrictions.

The diagram shows two keepout zones on the motherboard, which are intended to allow access to I/O connectors on the daughtercard. The keepout zones are not to be physically occupied by any daughtercard component. For existing motherboards, Keepout Zone 1 on the short edge (left edge on the diagram) is only available on the C6201 EVM, C6201 McEVM, and C6701 EVM. The Keepout Zone 2 on the long edge is available on all existing C6000 motherboards. The restriction placed on the motherboard within these keepout zones is that the component height within the keepout zone is within the maximum component height for Zone 1, defined in the mating section of this document.

<sup>&</sup>lt;sup>1</sup> See Figure 2 for a layout drawing of a daughtercard.

# 2.2 Existing Interfaces

Several DSP motherboards are currently in production, each with common (but not identical) interfaces. Most of the differences between the interfaces stem from the fact that different DSPs have different signals available. It is possible, however, to design a variety of useful daughtercards to work with some or all of these development boards, even across DSP platforms.

# TMS320C6201 EVM, C6201 McEVM, C6701 EVM

The C6201 EVM, C6201 McEVM, and C6701 EVM<sup>2</sup> were the first boards designed with the daughtercard interface in this specification. The interfaces on these cards provide a 32-bit asynchronous memory interface, two serial ports, two timers, and interrupt, and various status and control signals. All signals present are documented in the C6201 datasheet except for DC\_CNTL[1:0] and DC\_STAT[1:0], which are general-purpose inputs and outputs, respectively.

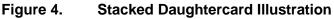

The EVM daughtercard interface pinout is provided in Table 1 and Table 2.

<sup>&</sup>lt;sup>2</sup> The daughtercard interfaces on the C6201 EVM, C6201 McEVM, and C6701 EVM are all identical. Throughout this document, any reference to the C6201 EVM also applies to both the C6201 McEVM and C6701 EVM.

| Pin | Signal   | I/O | Description                 | Pin | Signal  | I/O | Description                 |

|-----|----------|-----|-----------------------------|-----|---------|-----|-----------------------------|

| 1   | 12V      | Vcc | 12V voltage supply pin      | 2   | -12V    | Vcc | -12V voltage supply pin     |

| 3   | GND      | Vss | System ground               | 4   | GND     | Vss | System ground               |

| 5   | 5V       | Vcc | 5V voltage supply pin       | 6   | 5V      | Vcc | 5V voltage supply pin       |

| 7   | GND      | Vss | System ground               | 8   | GND     | Vss | System ground               |

| 9   | 5V       | Vcc | 5V voltage supply pin       | 10  | 5V      | Vcc | 5V voltage supply pin       |

| 11  | N/C      | -   | No connect                  | 12  | N/C     | -   | No connect                  |

| 13  | N/C      | -   | No connect                  | 14  | N/C     | -   | No connect                  |

| 15  | N/C      | -   | No connect                  | 16  | N/C     | -   | No connect                  |

| 17  | N/C      | -   | No connect                  | 18  | N/C     | -   | No connect                  |

| 19  | 3.3V     | Vcc | 3.3V voltage supply pin     | 20  | 3.3V    | Vcc | 3.3V voltage supply pin     |

| 21  | CLKX0    | I/O | McBSP0 transmit clock       | 22  | N/C     | -   | No connect                  |

| 23  | FSX0     | I/O | McBSP0 transmit frame sync  | 24  | DX0     | 0   | McBSP0 transmit             |

| 25  | GND      | Vss | System ground               | 26  | GND     | Vss | System ground               |

| 27  | CLKR0    | I/O | McBSP0 receive clock        | 28  | N/C     | -   | No connect                  |

| 29  | FSR0     | I/O | McBSP0 receive frame sync   | 30  | DR0     | I.  | McBSP0 receive data         |

| 31  | GND      | Vss | System ground               | 32  | GND     | Vss | System ground               |

| 33  | CLKX1    | I/O | McBSP1 transmit clock       | 34  | N/C     | -   | No connect                  |

| 35  | FSX1     | I/O | McBSP1 transmit frame sync  | 36  | DX1     | 0   | McBSP1 transmit data        |

| 37  | GND      | Vss | System ground               | 38  | GND     | Vss | System ground               |

| 39  | CLKR1    | I/O | McBSP1 receive clock        | 40  | N/C     | -   | No connect                  |

| 41  | FSR1     | I/O | McBSP1 receive frame sync   | 42  | DR1     | I   | McBSP1 receive data         |

| 43  | GND      | Vss | System ground               | 44  | GND     | Vss | System ground               |

| 45  | TOUT0    | 0   | Timer 0 output              | 46  | TINP0   | I   | Timer 0 input               |

| 47  | N/C      | -   | No connect                  | 48  | N/C     | -   | No connect                  |

| 49  | TOUT1    | 0   | Timer 1 output              | 50  | TINP1   | I   | Timer 1 input               |

| 51  | GND      | Vss | System ground               | 52  | GND     | Vss | System ground               |

| 53  | EXT_INT7 | I   | External interrupt 7        | 54  | IACK    | 0   | Interrupt acknowledge       |

| 55  | INUM3    | 0   | Interrupt number bit 3      | 56  | INUM2   | 0   | Interrupt number bit 2      |

| 57  | INUM1    | 0   | Interrupt number bit 1      | 58  | INUM0   | 0   | Interrupt number bit 0      |

| 59  | RESET    | 0   | System reset                | 60  | PD      | 0   | Power down status           |

| 61  | GND      | Vss | System ground               | 62  | GND     | Vss | System ground               |

| 63  | CNTL1    | 0   | Daughtercard control 1      | 64  | CNTL0   | 0   | Daughtercard control        |

| 65  | STAT1    | I   | Daughtercard status 1       | 66  | STAT0   | I   | Daughtercard status         |

| 67  | N/C      | -   | No connect                  | 68  | N/C     | -   | No connect                  |

| 69  | CE2#     | 0   | Chip enable 2               | 70  | CE3#    |     | Chip enable 3               |

| 71  | DMAC3    | 0   | DMA condition for channel 3 | 72  | DMAC2   | 0   | DMA condition for channel 2 |

| 73  | DMAC1    | 0   | DMA condition for channel 1 | 74  | DMAC0   | 0   | DMA condition for channel 0 |

| 75  | GND      | Vss | System ground               | 76  | GND     | Vss | System ground               |

| 77  | GND      | Vss | System ground               | 78  | CLKOUT2 | 0   | CPU clock / 2               |

| 79  | GND      | Vss | System ground               | 80  | GND     | Vss | System ground               |

# Table 1. TMS320C6201 EVM Peripheral Connector (J2) Pinout

| Table 2. | TMS320C6201 | <b>EVM Memory</b> | y Connector | ( <b>J</b> 1) | ) Pinout |

|----------|-------------|-------------------|-------------|---------------|----------|

|----------|-------------|-------------------|-------------|---------------|----------|

| Pin      | Signal       | I/O | Description              | Pin      | Signal       | I/O         | Description             |

|----------|--------------|-----|--------------------------|----------|--------------|-------------|-------------------------|

| 1        | 5V           | Vcc | 5V voltage supply pin    | 2        | 5V           | Vcc         | 5V voltage supply pin   |

| 3        | EA21         | 0   | EMIF address pin 21      | 4        | EA20         | 0           | EMIF address pin 20     |

| 5        | EA19         | 0   | EMIF address pin 19      | 6        | EA18         | 0           | EMIF address pin 18     |

| 7        | EA17         | 0   | EMIF address pin 17      | 8        | EA16         | 0           | EMIF address pin 16     |

| 9        | EA15         | 0   | EMIF address pin 17      | 10       | EA14         | 0           | EMIF address pin 14     |

| 11       | GND          | Vss | System ground            | 12       | GND          | Vss         | System ground           |

| 13       | EA13         | 0   | EMIF address pin 13      | 14       | EA12         | 0           | EMIF address pin 12     |

| 15       | EA11         | 0   | EMIF address pin 11      | 16       | EA10         | 0           | EMIF address pin 10     |

| 17       | EA9          | 0   | EMIF address pin 9       | 18       | EA8          | 0           | EMIF address pin 8      |

| 19       | EA7          | 0   | EMIF address pin 7       | 20       | EA6          | 0           | EMIF address pin 6      |

| 21       | 5V           | Vcc | 5V voltage supply pin    | 20       | 5V           | Vcc         | 5V voltage supply pin   |

| 23       | EA5          | 0   | EMIF address pin 5       | 24       | EA4          | 0           | EMIF address pin 4      |

| 25<br>25 | EA3          | 0   | EMIF address pin 3       | 24<br>26 | EA2          | 0           | EMIF address pin 2      |

| 27       | BE3#         | 0   | EMIF byte enable 3       | 28       | BE2#         | 0           | EMIF byte enable 2      |

| 27       | BE3#<br>BE1# | 0   | EMIF byte enable 3       | 30       | BE2#<br>BE0# | 0           | EMIF byte enable 0      |

| 29<br>31 | GND          | Vss | System ground            | 32       | GND          | Vss         | System ground           |

|          |              | 1/O |                          | 34       |              | V 55<br>I/O |                         |

| 33       | ED31         |     | EMIF data pin 31         |          | ED30         |             | EMIF data pin 30        |

| 35       | ED29         | I/O | EMIF data pin 29         | 36       | ED28<br>ED26 | I/O         | EMIF data pin 28        |

| 37       | ED27         | I/O | EMIF data pin 27         | 38       |              | I/O         | EMIF data pin 26        |

| 39       | ED25         | I/O | EMIF data pin 25         | 40       | ED24         | I/O         | EMIF data pin 24        |

| 41       | 3.3V         | Vcc | 3.3V voltage supply pin  | 42       | 3.3V         | Vcc         | 3.3V voltage supply pin |

| 43       | ED23         | I/O | EMIF data pin 23         | 44       | ED22         | I/O         | EMIF data pin 22        |

| 45       | ED21         | I/O | EMIF data pin 21         | 46       | ED20         | I/O         | EMIF data pin 20        |

| 47       | ED19         | I/O | EMIF data pin 19         | 48       | ED18         | I/O         | EMIF data pin 18        |

| 49       | ED17         | I/O | EMIF data pin 17         | 50       | ED16         | I/O         | EMIF data pin 16        |

| 51       | GND          | Vss | System ground            | 52       | GND          | Vss         | System ground           |

| 53       | ED15         | I/O | EMIF data pin 15         | 54       | ED14         | I/O         | EMIF data pin 14        |

| 55       | ED13         | I/O | EMIF data pin 13         | 56       | ED12         | I/O         | EMIF data pin 12        |

| 57       | ED11         | I/O | EMIF data pin 11         | 58       | ED10         | I/O         | EMIF data pin 10        |

| 59       | ED9          | I/O | EMIF data pin 9          | 60       | ED8          | I/O         | EMIF data pin 8         |

| 61       | GND          | Vss | System ground            | 62       | GND          | Vss         | System ground           |

| 63       | ED7          | I/O | EMIF data pin 7          | 64       | ED6          | I/O         | EMIF data pin 6         |

| 65       | ED5          | I/O | EMIF data pin 5          | 66       | ED4          | I/O         | EMIF data pin 4         |

| 67       | ED3          | I/O | EMIF data pin 3          | 68       | ED2          | I/O         | EMIF data pin 2         |

| 69       | ED1          | I/O | EMIF data pin 1          | 70       | ED0          | I/O         | EMIF data pin 0         |

| 71       | GND          | Vss | System ground            | 72       | GND          | Vss         | System ground           |

| 73       | ARE#         | 0   | EMIF async read enable   | 74       | AWE#         | 0           | EMIF async write enable |

| 75       | AOE#         | 0   | EMIF async output enable | 76       | ARDY         |             | EMIF asynchronous ready |

| 77       | N/C          | -   | No connect               | 78       | CE1#         | 0           | Chip enable 1           |

| 79       | GND          | Vss | System ground            | 80       | GND          | Vss         | System ground           |

### TMS320C6211 DSK

The interface of the TMS320C6211 DSK was designed using most of the same signals as the EVM. The main differences between the C6211 DSK and the C6201 EVM interfaces are that signals not physically present on the C6211 were removed, there is only one McBSP available, an additional external memory chip enables is available, and all of the DSP interrupts are available. The connectors also include the hold interface signals, though the board does not facilitate a daughtercard mastering the memory on the DSK. These signals can only be used to control daughtercard memory. The daughtercard connectors for the C6211 DSK are shown in Table 3 and Table 4.

| Pin | Signal   | I/O | Description                | Pin | Signal   | I/O | Description             |

|-----|----------|-----|----------------------------|-----|----------|-----|-------------------------|

| 1   | 12V      | Vcc | 12V voltage supply pin     | 2   | -12V     | Vcc | -12V voltage supply pin |

| 3   | GND      | Vss | System ground              | 4   | GND      | Vss | System ground           |

| 5   | 5V       | Vcc | 5V voltage supply pin      | 6   | 5V       | Vcc | 5V voltage supply pin   |

| 7   | GND      | Vss | System ground              | 8   | GND      | Vss | System ground           |

| 9   | 5V       | Vcc | 5V voltage supply pin      | 10  | 5V       | Vcc | 5V voltage supply pin   |

| 11  | N/C      | -   | No connect                 | 12  | HOLD#    | I   | EMIF hold request       |

| 13  | N/C      | -   | No connect                 | 14  | HOLDA#   | 0   | EMIF hold acknowledge   |

| 15  | N/C      | -   | No connect                 | 16  | BUSREQ   | 0   | EMIF bus request        |

| 17  | N/C      | -   | No connect                 | 18  | N/C      | -   | No connect              |

| 19  | 3.3V     | Vcc | 3.3V voltage supply pin    | 20  | 3.3V     | Vcc | 3.3V voltage supply pin |

| 21  | N/C      | -   | No connect                 | 22  | N/C      | -   | No connect              |

| 23  | N/C      | -   | No connect                 | 24  | N/C      | -   | No connect              |

| 25  | GND      | Vss | System ground              | 26  | GND      | Vss | System ground           |

| 27  | N/C      | -   | No connect                 | 28  | N/C      | -   | No connect              |

| 29  | N/C      | -   | No connect                 | 30  | N/C      | -   | No connect              |

| 31  | GND      | Vss | System ground              | 32  | GND      | Vss | System ground           |

| 33  | CLKX1    | I/O | McBSP1 transmit clock      | 34  | N/C      | -   | No connect              |

| 35  | FSX1     | I/O | McBSP1 transmit frame sync | 36  | DX1      | 0   | McBSP1 transmit data    |

| 37  | GND      | Vss | System ground              | 38  | GND      | Vss | System ground           |

| 39  | CLKR1    | I/O | McBSP1 receive clock       | 40  | N/C      | -   | No connect              |

| 41  | FSR1     | I/O | McBSP1 receive frame sync  | 42  | DR1      | I   | McBSP1 receive data     |

| 43  | GND      | Vss | System ground              | 44  | GND      | Vss | System ground           |

| 45  | TOUT0    | 0   | Timer 0 output             | 46  | TINP0    | I   | Timer 0 input           |

| 47  | NMI      | 1   | Non-maskable interrupt     | 48  | EXT_INT5 | I   | External interrupt 5    |

| 49  | TOUT1    | 0   | Timer 1 output             | 50  | TINP1    | I   | Timer 1 input           |

| 51  | GND      | Vss | System ground              | 52  | GND      | Vss | System ground           |

| 53  | EXT_INT4 | I   | External interrupt 4       | 54  | N/C      | -   | No connect              |

| 55  | N/C      | -   | No connect                 | 56  | N/C      | -   | No connect              |

| 57  | N/C      | -   | No connect                 | 58  | N/C      | -   | No connect              |

| 59  | RESET    | 0   | System reset               | 60  | N/C      | -   | No connect              |

| 61  | GND      | Vss | System ground              | 62  | GND      | Vss | System ground           |

| 63  | CNTL1    | 0   | Daughtercard control 1     | 64  | CNTL0    | 0   | Daughtercard control    |

#### Table 3. TMS320C6211 DSK Peripheral Connector (J2) Pinout

SPRA711

| Pin | Signal   | I/O | Description           | Pin | Signal   | I/O | Description          |

|-----|----------|-----|-----------------------|-----|----------|-----|----------------------|

| 65  | STAT1    | I   | Daughtercard status 1 | 66  | STAT0    | I   | Daughtercard status  |

| 67  | EXT_INT6 | 1   | External interrupt 6  | 68  | EXT_INT7 | 1   | External interrupt 7 |

| 69  | CE3#     | 0   | Chip enable 3         | 70  | N/C      | -   | No connect           |

| 71  | N/C      | -   | No connect            | 72  | N/C      | -   | No connect           |

| 73  | N/C      | -   | No connect            | 74  | N/C      | -   | No connect           |

| 75  | GND      | Vss | System ground         | 76  | GND      | Vss | System ground        |

| 77  | GND      | Vss | System ground         | 78  | ECLKOUT  | 0   | EMIF clock           |

| 79  | GND      | Vss | System ground         | 80  | GND      | Vss | System ground        |

# Table 4. TMS320C6211 DSK Memory Connector (J1) Pinout

| Pin | Signal | I/O | Description             | Pin | Signal | I/O | Description             |

|-----|--------|-----|-------------------------|-----|--------|-----|-------------------------|

| 1   | 5V     | Vcc | 5V voltage supply pin   | 2   | 5V     | Vcc | 5V voltage supply pin   |

| 3   | EA21   | 0   | EMIF address pin 21     | 4   | EA20   | 0   | EMIF address pin 20     |

| 5   | EA19   | 0   | EMIF address pin 19     | 6   | EA18   | 0   | EMIF address pin 18     |

| 7   | EA17   | 0   | EMIF address pin 17     | 8   | EA16   | 0   | EMIF address pin 16     |

| 9   | EA15   | 0   | EMIF address pin 15     | 10  | EA14   | 0   | EMIF address pin 14     |

| 11  | GND    | Vss | System ground           | 12  | GND    | Vss | System ground           |

| 13  | EA13   | 0   | EMIF address pin 13     | 14  | EA12   | 0   | EMIF address pin 12     |

| 15  | EA11   | 0   | EMIF address pin 11     | 16  | EA10   | 0   | EMIF address pin 10     |

| 17  | EA9    | 0   | EMIF address pin 9      | 18  | EA8    | 0   | EMIF address pin 8      |

| 19  | EA7    | 0   | EMIF address pin 7      | 20  | EA6    | 0   | EMIF address pin 6      |

| 21  | 5V     | Vcc | 5V voltage supply pin   | 22  | 5V     | Vcc | 5V voltage supply pin   |

| 23  | EA5    | 0   | EMIF address pin 5      | 24  | EA4    | 0   | EMIF address pin 4      |

| 25  | EA3    | 0   | EMIF address pin 3      | 26  | EA2    | 0   | EMIF address pin 2      |

| 27  | BE3#   | 0   | EMIF byte enable 3      | 28  | BE2#   | 0   | EMIF byte enable 2      |

| 29  | BE1#   | 0   | EMIF byte enable 1      | 30  | BE0#   | 0   | EMIF byte enable 0      |

| 31  | GND    | Vss | System ground           | 32  | GND    | Vss | System ground           |

| 33  | ED31   | I/O | EMIF data pin 31        | 34  | ED30   | I/O | EMIF data pin 30        |

| 35  | ED29   | I/O | EMIF data pin 29        | 36  | ED28   | I/O | EMIF data pin 28        |

| 37  | ED27   | I/O | EMIF data pin 27        | 38  | ED26   | I/O | EMIF data pin 26        |

| 39  | ED25   | I/O | EMIF data pin 25        | 40  | ED24   | I/O | EMIF data pin 24        |

| 41  | 3.3V   | Vcc | 3.3V voltage supply pin | 42  | 3.3V   | Vcc | 3.3V voltage supply pin |

| 43  | ED23   | I/O | EMIF data pin 23        | 44  | ED22   | I/O | EMIF data pin 22        |

| 45  | ED21   | I/O | EMIF data pin 21        | 46  | ED20   | I/O | EMIF data pin 20        |

| 47  | ED19   | I/O | EMIF data pin 19        | 48  | ED18   | I/O | EMIF data pin 18        |

| 49  | ED17   | I/O | EMIF data pin 17        | 50  | ED16   | I/O | EMIF data pin 16        |

| 51  | GND    | Vss | System ground           | 52  | GND    | Vss | System ground           |

| 53  | ED15   | I/O | EMIF data pin 15        | 54  | ED14   | I/O | EMIF data pin 14        |

| 55  | ED13   | I/O | EMIF data pin 13        | 56  | ED12   | I/O | EMIF data pin 12        |

| 57  | ED11   | I/O | EMIF data pin 11        | 58  | ED10   | I/O | EMIF data pin 10        |

| 59  | ED9    | I/O | EMIF data pin 9         | 60  | ED8    | I/O | EMIF data pin 8         |

| 61  | GND    | Vss | System ground           | 62  | GND    | Vss | System ground           |

| Pin | Signal | I/O | Description              | Pin | Signal | I/O | Description             |

|-----|--------|-----|--------------------------|-----|--------|-----|-------------------------|

| 63  | ED7    | I/O | EMIF data pin 7          | 64  | ED6    | I/O | EMIF data pin 6         |

| 65  | ED5    | I/O | EMIF data pin 5          | 66  | ED4    | I/O | EMIF data pin 4         |

| 67  | ED3    | I/O | EMIF data pin 3          | 68  | ED2    | I/O | EMIF data pin 2         |

| 69  | ED1    | I/O | EMIF data pin 1          | 70  | ED0    | I/O | EMIF data pin 0         |

| 71  | GND    | Vss | System ground            | 72  | GND    | Vss | System ground           |

| 73  | ARE#   | 0   | EMIF async read enable   | 74  | AWE#   | 0   | EMIF async write enable |

| 75  | AOE#   | 0   | EMIF async output enable | 76  | ARDY   | I   | EMIF asynchronous ready |

| 77  | N/C    | -   | No connect               | 78  | CE2#   | 0   | Chip enable 2           |

| 79  | GND    | Vss | System ground            | 80  | GND    | Vss | System ground           |

#### TMS320C6711 DSK

The interface on the TMS320C6711 DSK is identical to that of the C6211 DSK with the second McBSP added and the hold interface signals removed. The other minor differences include CE3 moving and NMI being removed.

The C6711 DSK daughtercard connectors are shown in Table 5 and Table 6.

| Pin | Signal | I/O | Description                | Pin | Signal   | I/O | Description             |

|-----|--------|-----|----------------------------|-----|----------|-----|-------------------------|

| 1   | 12V    | Vcc | 12V voltage supply pin     | 2   | -12V     | Vcc | -12V voltage supply pin |

| 3   | GND    | Vss | System ground              | 4   | GND      | Vss | System ground           |

| 5   | 5V     | Vcc | 5V voltage supply pin      | 6   | 5V       | Vcc | 5V voltage supply pin   |

| 7   | GND    | Vss | System ground              | 8   | GND      | Vss | System ground           |

| 9   | 5V     | Vcc | 5V voltage supply pin      | 10  | 5V       | Vcc | 5V voltage supply pin   |

| 11  | N/C    | -   | No connect                 | 12  | N/C      | -   | No connect              |

| 13  | N/C    | -   | No connect                 | 14  | N/C      | -   | No connect              |

| 15  | N/C    | -   | No connect                 | 16  | N/C      | -   | No connect              |

| 17  | N/C    | -   | No connect                 | 18  | N/C      | -   | No connect              |

| 19  | 3.3V   | Vcc | 3.3V voltage supply pin    | 20  | 3.3V     | Vcc | 3.3V voltage supply pin |

| 21  | CLKX0  | I/O | McBSP0 transmit clock      | 22  | N/C      | -   | No connect              |

| 23  | FSX0   | I/O | McBSP0 transmit frame sync | 24  | DX0      | 0   | McBSP0 transmit         |

| 25  | GND    | Vss | System ground              | 26  | GND      | Vss | System ground           |

| 27  | CLKR0  | I/O | McBSP0 receive clock       | 28  | N/C      | -   | No connect              |

| 29  | FSR0   | I/O | McBSP0 receive frame sync  | 30  | DR0      | I   | McBSP0 receive data     |

| 31  | GND    | Vss | System ground              | 32  | GND      | Vss | System ground           |

| 33  | CLKX1  | I/O | McBSP1 transmit clock      | 34  | N/C      | -   | No connect              |

| 35  | FSX1   | I/O | McBSP1 transmit frame sync | 36  | DX1      | 0   | McBSP1 transmit data    |

| 37  | GND    | Vss | System ground              | 38  | GND      | Vss | System ground           |

| 39  | CLKR1  | I/O | McBSP1 receive clock       | 40  | N/C      | -   | No connect              |

| 41  | FSR1   | I/O | McBSP1 receive frame sync  | 42  | DR1      | I   | McBSP1 receive data     |

| 43  | GND    | Vss | System ground              | 44  | GND      | Vss | System ground           |

| 45  | TOUT0  | 0   | Timer 0 output             | 46  | TINP0    | I   | Timer 0 input           |

| 47  | N/C    | -   | No connect                 | 48  | EXT_INT5 | I   | External interrupt 5    |

| 49  | TOUT1  | 0   | Timer 1 output             | 50  | TINP1    | I   | Timer 1 input           |

#### Table 5. TMS320C6711 DSK Peripheral Connector (J2) Pinout

SPRA711

| Pin | Signal   | I/O | Description            | Pin | Signal   | I/O | Description          |

|-----|----------|-----|------------------------|-----|----------|-----|----------------------|

| 51  | GND      | Vss | System ground          | 52  | GND      | Vss | System ground        |

| 53  | EXT_INT4 | I   | External interrupt 4   | 54  | N/C      | -   | No connect           |

| 55  | N/C      | -   | No connect             | 56  | N/C      | -   | No connect           |

| 57  | N/C      | -   | No connect             | 58  | N/C      | -   | No connect           |

| 59  | RESET    | 0   | System reset           | 60  | N/C      | -   | No connect           |

| 61  | GND      | Vss | System ground          | 62  | GND      | Vss | System ground        |

| 63  | CNTL1    | 0   | Daughtercard control 1 | 64  | CNTL0    | 0   | Daughtercard control |

| 65  | STAT1    | I   | Daughtercard status 1  | 66  | STAT0    | I   | Daughtercard status  |

| 67  | EXT_INT6 | I   | External interrupt 6   | 68  | EXT_INT7 | I   | External interrupt 7 |

| 69  | N/C      | -   | No connect             | 70  | N/C      | -   | No connect           |

| 71  | N/C      | -   | No connect             | 72  | N/C      | -   | No connect           |

| 73  | N/C      | -   | No connect             | 74  | N/C      | -   | No connect           |

| 75  | GND      | Vss | System ground          | 76  | GND      | Vss | System ground        |

| 77  | GND      | Vss | System ground          | 78  | ECLKOUT  | 0   | EMIF clock           |

| 79  | GND      | Vss | System ground          | 80  | GND      | Vss | System ground        |

# Table 6. TMS320C6711 DSK Memory Connector (J1) Pinout

| Pin | Signal | I/O | Description             | Pin | Signal | I/O | Description             |

|-----|--------|-----|-------------------------|-----|--------|-----|-------------------------|

| 1   | 5V     | Vcc | 5V voltage supply pin   | 2   | 5V     | Vcc | 5V voltage supply pin   |

| 3   | EA21   | 0   | EMIF address pin 21     | 4   | EA20   | 0   | EMIF address pin 20     |

| 5   | EA19   | 0   | EMIF address pin 19     | 6   | EA18   | 0   | EMIF address pin 18     |

| 7   | EA17   | 0   | EMIF address pin 17     | 8   | EA16   | 0   | EMIF address pin 16     |

| 9   | EA15   | 0   | EMIF address pin 15     | 10  | EA14   | 0   | EMIF address pin 14     |

| 11  | GND    | Vss | System ground           | 12  | GND    | Vss | System ground           |

| 13  | EA13   | 0   | EMIF address pin 13     | 14  | EA12   | 0   | EMIF address pin 12     |

| 15  | EA11   | 0   | EMIF address pin 11     | 16  | EA10   | 0   | EMIF address pin 10     |

| 17  | EA9    | 0   | EMIF address pin 9      | 18  | EA8    | 0   | EMIF address pin 8      |

| 19  | EA7    | 0   | EMIF address pin 7      | 20  | EA6    | 0   | EMIF address pin 6      |

| 21  | 5V     | Vcc | 5V voltage supply pin   | 22  | 5V     | Vcc | 5V voltage supply pin   |

| 23  | EA5    | 0   | EMIF address pin 5      | 24  | EA4    | 0   | EMIF address pin 4      |

| 25  | EA3    | 0   | EMIF address pin 3      | 26  | EA2    | 0   | EMIF address pin 2      |

| 27  | BE3#   | 0   | EMIF byte enable 3      | 28  | BE2#   | 0   | EMIF byte enable 2      |

| 29  | BE1#   | 0   | EMIF byte enable 1      | 30  | BE0#   | 0   | EMIF byte enable 0      |

| 31  | GND    | Vss | System ground           | 32  | GND    | Vss | System ground           |

| 33  | ED31   | I/O | EMIF data pin 31        | 34  | ED30   | I/O | EMIF data pin 30        |

| 35  | ED29   | I/O | EMIF data pin 29        | 36  | ED28   | I/O | EMIF data pin 28        |

| 37  | ED27   | I/O | EMIF data pin 27        | 38  | ED26   | I/O | EMIF data pin 26        |

| 39  | ED25   | I/O | EMIF data pin 25        | 40  | ED24   | I/O | EMIF data pin 24        |

| 41  | 3.3V   | Vcc | 3.3V voltage supply pin | 42  | 3.3V   | Vcc | 3.3V voltage supply pin |

| 43  | ED23   | I/O | EMIF data pin 23        | 44  | ED22   | I/O | EMIF data pin 22        |

| 45  | ED21   | I/O | EMIF data pin 21        | 46  | ED20   | I/O | EMIF data pin 20        |

| 47  | ED19   | I/O | EMIF data pin 19        | 48  | ED18   | I/O | EMIF data pin 18        |

| 49  | ED17   | I/O | EMIF data pin 17        | 50  | ED16   | I/O | EMIF data pin 16        |

| Pin | Signal | I/O | Description              | Pin | Signal | I/O | Description             |

|-----|--------|-----|--------------------------|-----|--------|-----|-------------------------|

| 51  | GND    | Vss | System ground            | 52  | GND    | Vss | System ground           |

| 53  | ED15   | I/O | EMIF data pin 15         | 54  | ED14   | I/O | EMIF data pin 14        |

| 55  | ED13   | I/O | EMIF data pin 13         | 56  | ED12   | I/O | EMIF data pin 12        |

| 57  | ED11   | I/O | EMIF data pin 11         | 58  | ED10   | I/O | EMIF data pin 10        |

| 59  | ED9    | I/O | EMIF data pin 9          | 60  | ED8    | I/O | EMIF data pin 8         |

| 61  | GND    | Vss | System ground            | 62  | GND    | Vss | System ground           |

| 63  | ED7    | I/O | EMIF data pin 7          | 64  | ED6    | I/O | EMIF data pin 6         |

| 65  | ED5    | I/O | EMIF data pin 5          | 66  | ED4    | I/O | EMIF data pin 4         |

| 67  | ED3    | I/O | EMIF data pin 3          | 68  | ED2    | I/O | EMIF data pin 2         |

| 69  | ED1    | I/O | EMIF data pin 1          | 70  | ED0    | I/O | EMIF data pin 0         |

| 71  | GND    | Vss | System ground            | 72  | GND    | Vss | System ground           |

| 73  | ARE#   | 0   | EMIF async read enable   | 74  | AWE#   | 0   | EMIF async write enable |

| 75  | AOE#   | 0   | EMIF async output enable | 76  | ARDY   | 1   | EMIF asynchronous ready |

| 77  | CE3#   | 0   | Chip enable 3            | 78  | CE2#   | 0   | Chip enable 2           |

| 79  | GND    | Vss | System ground            | 80  | GND    | Vss | System ground           |

### TMS320C6202 EVM (Blue Wave Systems)

The C6202 EVM (PCI/C6202-EVM<sup>™</sup>) by Blue Wave Systems also includes a daughtercard interface, which is based on the C6201 EVM interface but uses the expansion bus for the asynchronous parallel memory interface. The remaining signals are the same as on the C6201 EVM with the addition of more chip selects, more interrupts, and no general-purpose I/O signals. The daughtercard connectors include all expansion bus signals, which provide the host interface to the daughtercard. Documentation describing the use of the daughtercard on the PCI/C6202-EVM is available from Blue Wave Systems.

The daughtercard connectors for the PCI/C6202-EVM are shown in Table 7 and Table 8.

| Pin | Signal | I/O | Description                | Pin | Signal  | I/O | Description             |

|-----|--------|-----|----------------------------|-----|---------|-----|-------------------------|

| 1   | 12V    | Vcc | 12V voltage supply pin     | 2   | -12V    | Vcc | -12V voltage supply pin |

| 3   | GND    | Vss | System ground              | 4   | GND     | Vss | System ground           |

| 5   | 5V     | Vcc | 5V voltage supply pin      | 6   | 5V      | Vcc | 5V voltage supply pin   |

| 7   | GND    | Vss | System ground              | 8   | GND     | Vss | System ground           |

| 9   | 5V     | Vcc | 5V voltage supply pin      | 10  | 5V      | Vcc | 5V voltage supply pin   |

| 11  | N/C    | -   | No connect                 | 12  | XHOLD#  | 1   | XBUS hold request       |

| 13  | N/C    | -   | No connect                 | 14  | XHOLDA# | 0   | XBUS hold acknowledge   |

| 15  | N/C    | -   | No connect                 | 16  | N/C     | -   | No connect              |

| 17  | N/C    | -   | No connect                 | 18  | N/C     | -   | No connect              |

| 19  | 3.3V   | Vcc | 3.3V voltage supply pin    | 20  | 3.3V    | Vcc | 3.3V voltage supply pin |

| 21  | CLKX0  | I/O | McBSP0 transmit clock      | 22  | N/C     | -   | No connect              |

| 23  | FSX0   | I/O | McBSP0 transmit frame sync | 24  | DX0     | 0   | McBSP0 transmit         |

| 25  | GND    | Vss | System ground              | 26  | GND     | Vss | System ground           |

| 27  | CLKR0  | I/O | McBSP0 receive clock       | 28  | N/C     | -   | No connect              |

| 29  | FSR0   | I/O | McBSP0 receive frame sync  | 30  | DR0     | I   | McBSP0 receive data     |

Table 7. PCI/C6202-EVM Peripheral Connector (J2) Pinout

SPRA711

| Pin | Signal   | I/O | Description                 | Pin | Signal   | I/O | Description                 |

|-----|----------|-----|-----------------------------|-----|----------|-----|-----------------------------|

| 31  | GND      | Vss | System ground               | 32  | GND      | Vss | System ground               |

| 33  | CLKX1    | I/O | McBSP1 transmit clock       | 34  | N/C      | -   | No connect                  |

| 35  | FSX1     | I/O | McBSP1 transmit frame sync  | 36  | DX1      | 0   | McBSP1 transmit data        |

| 37  | GND      | Vss | System ground               | 38  | GND      | Vss | System ground               |

| 39  | CLKR1    | I/O | McBSP1 receive clock        | 40  | N/C      | -   | No connect                  |

| 41  | FSR1     | I/O | McBSP1 receive frame sync   | 42  | DR1      | I   | McBSP1 receive data         |

| 43  | GND      | Vss | System ground               | 44  | GND      | Vss | System ground               |

| 45  | TOUT0    | 0   | Timer 0 output              | 46  | TINP0    | I   | Timer 0 input               |

| 47  | NMI      | I   | Non-maskable interrupt      | 48  | EXT_INT6 | 1   | External interrupt 6        |

| 49  | TOUT1    | 0   | Timer 1 output              | 50  | TINP1    | I   | Timer 1 input               |

| 51  | GND      | Vss | System ground               | 52  | GND      | Vss | System ground               |

| 53  | EXT_INT7 | I   | External interrupt 7        | 54  | IACK     | 0   | Interrupt acknowledge       |

| 55  | INUM3    | 0   | Interrupt number bit 3      | 56  | INUM2    | 0   | Interrupt number bit 2      |

| 57  | INUM1    | 0   | Interrupt number bit 1      | 58  | INUM0    | 0   | Interrupt number bit 0      |

| 59  | RESET    | 0   | System reset                | 60  | PD       | 0   | Power down status           |

| 61  | GND      | Vss | System ground               | 62  | GND      | Vss | System ground               |

| 63  | N/C      | -   | No connect                  | 64  | N/C      | -   | No connect                  |

| 65  | N/C      | -   | No connect                  | 66  | N/C      | -   | No connect                  |

| 67  | EXT_INT5 | I   | External interrupt 5        | 68  | EXT_INT4 | I   | External interrupt 4        |

| 69  | XCE2#    | 0   | XBUS Chip enable 2          | 70  | XCE3#    |     | XBUS Chip enable 3          |

| 71  | DMAC3    | 0   | DMA condition for channel 3 | 72  | DMAC2    | 0   | DMA condition for channel 2 |

| 73  | DMAC1    | 0   | DMA condition for channel 1 | 74  | DMAC0    | 0   | DMA condition for channel 0 |

| 75  | GND      | Vss | System ground               | 76  | GND      | Vss | System ground               |

| 77  | GND      | Vss | System ground               | 78  | CLKOUT2  | 0   | CPU clock / 2               |

| 79  | GND      | Vss | System ground               | 80  | GND      | Vss | System ground               |

# Table 8. PCI/C6202-EVM Memory Connector (J1) Pinout

| Pin | Signal | I/O | Description            | Pin | Signal | I/O | Description           |

|-----|--------|-----|------------------------|-----|--------|-----|-----------------------|

| 1   | 5V     | Vcc | 5V voltage supply pin  | 2   | 5V     | Vcc | 5V voltage supply pin |

| 3   | N/C    | -   | No connect             | 4   | N/C    | -   | No connect            |

| 5   | XFCLK  | 0   | XBUS FIFO clock        | 6   | XCLKIN | I   | XBUS input clock      |

| 7   | XCE2#  | 0   | XBUS chip enable 2     | 8   | XCE3#  | 0   | XBUS chip enable 3    |

| 9   | N/C    | -   | No connect             | 10  | N/C    | -   | No connect            |

| 11  | GND    | Vss | System ground          | 12  | GND    | Vss | System ground         |

| 13  | XW/R   | I   | XBUS read/write strobe | 14  | XCNTL  | I   | XBUS control          |

| 15  | XAS#   | I/O | XBUS address strobe    | 16  | XCS#   | I   | XBUS host chip select |

| 17  | XHOLDA | I/O | XBUS hold acknowledge  | 18  | XHOLD  | I/O | XBUS hold request     |

| 19  | XBOFF  | I   | XBUS back off          | 20  | XBLAST | I/O | XBUS last-in-burst    |

| 21  | 5V     | Vcc | 5V voltage supply pin  | 22  | 5V     | Vcc | 5V voltage supply pin |

| 23  | XA5    | I/O | XBUS address pin 5     | 24  | XA4    | I/O | XBUS address pin 4    |

| 25  | XA3    | I/O | XBUS address pin 3     | 26  | XA2    | I/O | XBUS address pin 2    |

| 27  | XBE3#  | I/O | XBUS byte enable 3     | 28  | XBE2#  | I/O | XBUS byte enable 2    |

| 29  | XBE1#  | I/O | XBUS byte enable 1     | 30  | XBE0#  | I/O | XBUS byte enable 0    |

| Pin | Signal | I/O | Description              | Pin | Signal | I/O | Description             |

|-----|--------|-----|--------------------------|-----|--------|-----|-------------------------|

| 31  | GND    | Vss | System ground            | 32  | GND    | Vss | System ground           |

| 33  | XD31   | I/O | XBUS data pin 31         | 34  | XD30   | I/O | XBUS data pin 30        |

| 35  | XD29   | I/O | XBUS data pin 29         | 36  | XD28   | I/O | XBUS data pin 28        |

| 37  | XD27   | I/O | XBUS data pin 27         | 38  | XD26   | I/O | XBUS data pin 26        |

| 39  | XD25   | I/O | XBUS data pin 25         | 40  | XD24   | I/O | XBUS data pin 24        |

| 41  | 3.3V   | Vcc | 3.3V voltage supply pin  | 42  | 3.3V   | Vcc | 3.3V voltage supply pin |

| 43  | XD23   | I/O | XBUS data pin 23         | 44  | XD22   | I/O | XBUS data pin 22        |

| 45  | XD21   | I/O | XBUS data pin 21         | 46  | XD20   | I/O | XBUS data pin 20        |

| 47  | XD19   | I/O | XBUS data pin 19         | 48  | XD18   | I/O | XBUS data pin 18        |

| 49  | XD17   | I/O | XBUS data pin 17         | 50  | XD16   | I/O | XBUS data pin 16        |

| 51  | GND    | Vss | System ground            | 52  | GND    | Vss | System ground           |

| 53  | XD15   | I/O | XBUS data pin 15         | 54  | XD14   | I/O | XBUS data pin 14        |

| 55  | XD13   | I/O | XBUS data pin 13         | 56  | XD12   | I/O | XBUS data pin 12        |

| 57  | XD11   | I/O | XBUS data pin 11         | 58  | XD10   | I/O | XBUS data pin 10        |

| 59  | XD9    | I/O | XBUS data pin 9          | 60  | XD8    | I/O | XBUS data pin 8         |

| 61  | GND    | Vss | System ground            | 62  | GND    | Vss | System ground           |

| 63  | XD7    | I/O | XBUS data pin 7          | 64  | XD6    | I/O | XBUS data pin 6         |

| 65  | XD5    | I/O | XBUS data pin 5          | 66  | XD4    | I/O | XBUS data pin 4         |

| 67  | XD3    | I/O | XBUS data pin 3          | 68  | XD2    | I/O | XBUS data pin 2         |

| 69  | XD1    | I/O | XBUS data pin 1          | 70  | XD0    | I/O | XBUS data pin 0         |

| 71  | GND    | Vss | System ground            | 72  | GND    | Vss | System ground           |

| 73  | XRE#   | 0   | XBUS async read enable   | 74  | XWE#   | 0   | XBUS async write enable |

| 75  | XOE#   | 0   | XBUS async output enable | 76  | XRDY   | I/O | XBUS asynchronous ready |

| 77  | XCE1#  | 0   | XBUS chip enable 1       | 78  | XCE0#  | 0   | XBUS chip enable 0      |

| 79  | GND    | Vss | System ground            | 80  | GND    | Vss | System ground           |

### TMS320C5402 DSK

The C5402 DSK is the first C5000 DSP board to include a compatible daughtercard interface. This board has an interface based on that of the C6201 EVM, as well. There are several differences based on the fact that the C54x has a different memory interface than the C6000 DSPs, and the functionality of the peripherals differ slightly. The interface still provides a 32-bit data bus, though accesses are optimized for the default width of 16 bits. There are a number of different signals available that are not present on the C6201 EVM interface are documented in the C5402 datasheet except for DCINT, which is a system-to-daughtercard interrupt generated in hardware.

The daughtercard interface on the C5402 DSK also contains the signal DC\_DET#, which is used to detect the presence of a daughtercard. This pin must be either physically connected to ground (recommended, as it is a ground pin on most interfaces) or pulled low in order for the C5402 DSK to provide the daughtercard with power. If the C5402 DSK does not detect a 'low' on this pin, then no voltage is provided to the daughtercard.

The daughtercard connectors for the C5402 DSK are shown in Table 9 and Table 10.

|     | •       | ables | 9. TM5320C3402 D5K P       | onpri |         |     |                         |

|-----|---------|-------|----------------------------|-------|---------|-----|-------------------------|

| Pin | Signal  | I/O   | Description                | Pin   | Signal  | I/O | Description             |

| 1   | 12V     | Vcc   | 12V voltage supply pin     | 2     | -12V    | Vcc | -12V voltage supply pin |

| 3   | GND     | Vss   | System ground              | 4     | GND     | Vss | System ground           |

| 5   | 5V      | Vcc   | 5V voltage supply pin      | 6     | 5V      | Vcc | 5V voltage supply pin   |

| 7   | GND     | Vss   | System ground              | 8     | GND     | Vss | System ground           |

| 9   | 5V      | Vcc   | 5V voltage supply pin      | 10    | 5V      | Vcc | 5V voltage supply pin   |

| 11  | N/C     | -     | No connect                 | 12    | N/C     | -   | No connect              |

| 13  | N/C     | -     | No connect                 | 14    | N/C     | -   | No connect              |

| 15  | N/C     | -     | No connect                 | 16    | N/C     | -   | No connect              |

| 17  | N/C     | -     | No connect                 | 18    | N/C     | -   | No connect              |

| 19  | 3.3V    | Vcc   | 3.3V voltage supply pin    | 20    | 3.3V    | Vcc | 3.3V voltage supply pin |

| 21  | CLKX0   | I/O   | McBSP0 transmit clock      | 22    | N/C     | -   | No connect              |

| 23  | FSX0    | I/O   | McBSP0 transmit frame sync | 24    | DX0     | 0   | McBSP0 transmit         |

| 25  | GND     | Vss   | System ground              | 26    | GND     | Vss | System ground           |

| 27  | CLKR0   | I/O   | McBSP0 receive clock       | 28    | N/C     | -   | No connect              |

| 29  | FSR0    | I/O   | McBSP0 receive frame sync  | 30    | DR0     | I   | McBSP0 receive data     |

| 31  | GND     | Vss   | System ground              | 32    | GND     | Vss | System ground           |

| 33  | CLKX1   | I/O   | McBSP1 transmit clock      | 34    | N/C     | -   | No connect              |

| 35  | FSX1    | I/O   | McBSP1 transmit frame sync | 36    | DX1     | 0   | McBSP1 transmit data    |

| 37  | GND     | Vss   | System ground              | 38    | GND     | Vss | System ground           |

| 39  | CLKR1   | I/O   | McBSP1 receive clock       | 40    | N/C     | -   | No connect              |

| 41  | FSR1    | I/O   | McBSP1 receive frame sync  | 42    | DR1     | I   | McBSP1 receive data     |

| 43  | GND     | Vss   | System ground              | 44    | GND     | Vss | System ground           |

| 45  | TOUT    | 0     | Timer output               | 46    | N/C     | -   | No connect              |

| 47  | N/C     | -     | No connect                 | 48    | INT1#   | I   | Interrupt 1             |

| 49  | XF      | 0     | External flag              | 50    | BIO#    | I   | Branch control          |

| 51  | GND     | Vss   | System ground              | 52    | GND     | Vss | System ground           |

| 53  | INT0#   | I     | Interrupt 0                | 54    | IACK    | 0   | Interrupt acknowledge   |

| 55  | N/C     | -     | No connect                 | 56    | IOSTRB# | 0   | I/O strobe              |

| 57  | MSC#    | 0     | Microstate complete        | 58    | IAQ#    | 0   | Instruction acquisition |

| 59  | RESET   | 0     | System reset               | 60    | DCINT#  | 0   | Daughtercard interrupt  |

| 61  | GND     | Vss   | System ground              | 62    | GND     | Vss | System ground           |

| 63  | CNTL1   | 0     | Daughtercard control 1     | 64    | CNTL0   | 0   | Daughtercard control    |

| 65  | STAT1   | I     | Daughtercard status 1      | 66    | STAT0   | Ι   | Daughtercard status     |

| 67  | INT2#   | I     | Interrupt 2                | 68    | INT3#   | I   | Interrupt 3             |

| 69  | PS#     | 0     | Program memory select      | 70    | IS#     | 0   | I/O memory select       |

| 71  | N/C     | -     | No connect                 | 72    | N/C     | -   | No connect              |

| 73  | N/C     | -     | No connect                 | 74    | N/C     | -   | No connect              |

| 75  | DC_DET# | 1     | Daughtercard detect        | 76    | GND     | Vss | System ground           |

| 77  | GND     | Vss   | System ground              | 78    | CLKOUT  | 0   | Output clock            |

| 79  | GND     | Vss   | System ground              | 80    | GND     | Vss | System ground           |

# Table 9. TMS320C5402 DSK Peripheral Connector (J2) Pinout

|     |        | lable | 10. TWIS320C5402 DSK     | MEIII |        |     | 51) F 11001             |

|-----|--------|-------|--------------------------|-------|--------|-----|-------------------------|

| Pin | Signal | I/O   | Description              | Pin   | Signal | I/O | Description             |

| 1   | 5V     | Vcc   | 5V voltage supply pin    | 2     | 5V     | Vcc | 5V voltage supply pin   |

| 3   | A19    | 0     | EMIF address pin 19      | 4     | A18    | 0   | EMIF address pin 18     |

| 5   | A17    | 0     | EMIF address pin 17      | 6     | A16    | 0   | EMIF address pin 16     |

| 7   | A15    | 0     | EMIF address pin 15      | 8     | A14    | 0   | EMIF address pin 14     |

| 9   | A13    | 0     | EMIF address pin 13      | 10    | A12    | 0   | EMIF address pin 12     |

| 11  | GND    | Vss   | System ground            | 12    | GND    | Vss | System ground           |

| 13  | A11    | 0     | EMIF address pin 11      | 14    | A10    | 0   | EMIF address pin 10     |

| 15  | A9     | 0     | EMIF address pin 9       | 16    | A8     | 0   | EMIF address pin 8      |

| 17  | A7     | 0     | EMIF address pin 7       | 18    | A6     | 0   | EMIF address pin 6      |

| 19  | A5     | 0     | EMIF address pin 5       | 20    | A4     | 0   | EMIF address pin 4      |

| 21  | 5V     | Vcc   | 5V voltage supply pin    | 22    | 5V     | Vcc | 5V voltage supply pin   |

| 23  | A3     | 0     | EMIF address pin 3       | 24    | A2     | 0   | EMIF address pin 2      |

| 25  | A1     | 0     | EMIF address pin 1       | 26    | A0     | 0   | EMIF address pin 0      |

| 27  | A21    | 0     | EMIF address pin 21      | 28    | A20    | 0   | EMIF address pin 20     |

| 29  | GND    | Vss   | System ground            | 30    | GND    | Vss | System ground           |

| 31  | GND    | Vss   | System ground            | 32    | GND    | Vss | System ground           |

| 33  | D31    | I/O   | EMIF data pin 31         | 34    | D30    | I/O | EMIF data pin 30        |

| 35  | D29    | I/O   | EMIF data pin 29         | 36    | D28    | I/O | EMIF data pin 28        |

| 37  | D27    | I/O   | EMIF data pin 27         | 38    | D26    | I/O | EMIF data pin 26        |

| 39  | D25    | I/O   | EMIF data pin 25         | 40    | D24    | I/O | EMIF data pin 24        |

| 41  | 3.3V   | Vcc   | 3.3V voltage supply pin  | 42    | 3.3V   | Vcc | 3.3V voltage supply pin |

| 43  | D23    | I/O   | EMIF data pin 23         | 44    | D22    | I/O | EMIF data pin 22        |

| 45  | D21    | I/O   | EMIF data pin 21         | 46    | D20    | I/O | EMIF data pin 20        |

| 47  | D19    | I/O   | EMIF data pin 19         | 48    | D18    | I/O | EMIF data pin 18        |

| 49  | D17    | I/O   | EMIF data pin 17         | 50    | D16    | I/O | EMIF data pin 16        |

| 51  | GND    | Vss   | System ground            | 52    | GND    | Vss | System ground           |

| 53  | D15    | I/O   | EMIF data pin 15         | 54    | D14    | I/O | EMIF data pin 14        |

| 55  | D13    | I/O   | EMIF data pin 13         | 56    | D12    | I/O | EMIF data pin 12        |

| 57  | D11    | I/O   | EMIF data pin 11         | 58    | D10    | I/O | EMIF data pin 10        |

| 59  | D9     | I/O   | EMIF data pin 9          | 60    | D8     | I/O | EMIF data pin 8         |

| 61  | GND    | Vss   | System ground            | 62    | GND    | Vss | System ground           |

| 63  | D7     | I/O   | EMIF data pin 7          | 64    | D6     | I/O | EMIF data pin 6         |

| 65  | D5     | I/O   | EMIF data pin 5          | 66    | D4     | I/O | EMIF data pin 4         |

| 67  | D3     | I/O   | EMIF data pin 3          | 68    | D2     | I/O | EMIF data pin 2         |

| 69  | D1     | I/O   | EMIF data pin 1          | 70    | D0     | I/O | EMIF data pin 0         |

| 71  | GND    | Vss   | System ground            | 72    | GND    | Vss | System ground           |

| 73  | RE#    | 0     | EMIF async read enable   | 74    | WE#    | 0   | EMIF async write enable |

| 75  | OE#    | 0     | EMIF async output enable | 76    | RDY    | 1   | EMIF asynchronous ready |

| 77  | MSTRB# | 0     | Memory strobe            | 78    | DS#    | 0   | Data memory select      |

| 79  | GND    | Vss   | System ground            | 80    | GND    | Vss | System ground           |

|  | Table 10. | TMS320C5402 DSK Memory | v Connector ( | J1) | <b>Pinout</b> |

|--|-----------|------------------------|---------------|-----|---------------|

|--|-----------|------------------------|---------------|-----|---------------|

# 2.3 Existing Interface Summary

The features of each of the existing daughtercard interfaces are provided in Table 11. The text following the table describes the differences in detail. Address ranges are provided per memory space, and represent the range of contiguous memory available to the daughtercard. Note that the address ranges are provided in bytes, regardless of the addressing capabilities of the interfaces. Details on the addressable memory of each card are outlined following the table.

|              |              | C6201 EVM                            | C6211 DSK   | C6711 DSK   | C5402 DSK                               | C6202 EVM                            |

|--------------|--------------|--------------------------------------|-------------|-------------|-----------------------------------------|--------------------------------------|

| Memory       | Width        | 8/16/32 <sup>3</sup>                 | 8/16/32     | 8/16/32     | 16/32                                   | 32                                   |

| interface    | Addressing   | Byte                                 | Byte        | Byte        | 16-bit                                  | Byte                                 |

|              | Accesses     | Byte                                 | Byte        | Byte        | 16-bit word                             | 32-bit word                          |

|              |              | 16-bit word                          | 16-bit word | 16-bit word | 32-bit word                             |                                      |

|              |              | 32-bit word                          | 32-bit word | 32-bit word |                                         |                                      |

|              | Chip selects | 1-3                                  | 2           | 2           | 3                                       | 4                                    |

|              | Memory types | Async                                | Async       | Async       | Async                                   | Async/<br>Sync FIFO                  |

|              | Addressable  | CE1: 3MB                             | CE2: 4MB    | CE2: 4MB    | DS: 2MB                                 | XCE0: 64B                            |

|              | Memory       | CE2: 4MB                             | CE3: 4MB    | CE3: 4MB    | PS: 1MB                                 | XCE1: 64B                            |

|              |              | CE3: 4MB                             |             |             | IS: 2MB                                 | XCE2: 64B                            |

|              |              |                                      |             |             |                                         | XCE3: 64B                            |

| Serial Ports | 5            | 2 McBSPs                             | 1 McBSP     | 2 McBSPs    | 2 McBSPs                                | 2 McBSPs                             |

| Timers       |              | 2 TINP                               | 2 TINP      | 2 TINP      | 1 TOUT                                  | 2 TINP                               |

|              |              | 2 TOUT                               | 2 TOUT      | 2 TOUT      |                                         | 2 TOUT                               |

| Interrupts   | DC to DSP    | 1                                    | 5           | 4           | 4                                       | 5                                    |

|              | DSP to DC    | 0                                    | 0           | 0           | 1                                       | 0                                    |

| DSP/Syster   | n status     | IACK,<br>INUM,<br>DMAC,<br>RESET, PD | RESET       | RESET       | IACK, IAQ,<br>XF, BIO,<br>MSC,<br>RESET | IACK,<br>INUM,<br>DMAC,<br>RESET, PD |

| GPIO         |              | 2 input                              | 2 input     | 2 input     | 2 input                                 | None                                 |

|              |              | 2 output                             | 2 output    | 2 output    | 2 output                                |                                      |

| Host I/F     |              | None                                 | None        | None        | None                                    | 32-bit                               |

| Table 11. | <b>Existing Daughtercard Interface Features</b> |

|-----------|-------------------------------------------------|

|-----------|-------------------------------------------------|

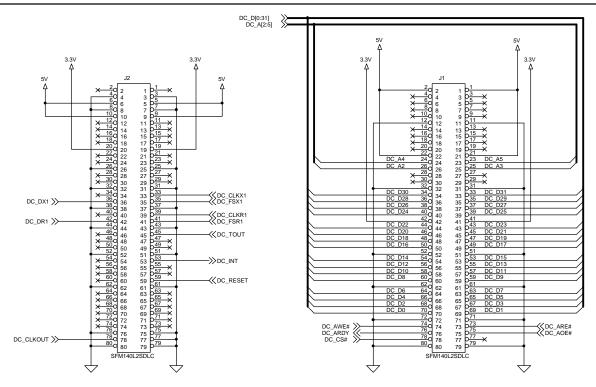

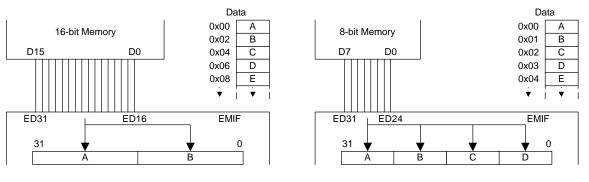

# 2.4 Memory Interface

The memory interfaces currently available with the existing daughtercard interfaces vary between boards due to architectural differences between the DSPs. These differences are:

• **C6201 EVM:** The EVM provides an asynchronous memory interface capable of communicating with 32-bit memory. There is one primary chip select, with up to two more optionally available (selectable between system and daughtercard memory). The interface is byte addressable, with 20 address lines and individual byte enables. The memory is controlled with separate output, read, and write enables. A ready input to the DSP is

<sup>&</sup>lt;sup>3</sup> All RAM is 32-bit only. 8- and 16-bit modes are supported for ROM only

available to indicate a memory is not ready. 8-bit and 16-bit ROM is also supported. For these modes the memory is always aligned with the lowest-numbered data lines.

The addressable memory is not identical between the three memory areas. The primary memory space (CE1#) has 3MB of addressable memory available for use. This 3MB comprises the daughtercard addresses of DC\_EA[21:2] = 0x00000 - 0xEFFFF (byte address range = 0x000000 - 0x1FFFFF). The second and third memory spaces (CE2# and CE3#, respectively), which are optionally available to the daughtercard, allow the use of the full daughtercard address range of 4MB: DC\_EA[21:2] = 0x000000 - 0xFFFFF (byte address range = 0x000000 - 0x3FFFFF).

• **C6211 DSK, C6711 DSK:** The C6211 DSK and C6711 DSK provide an asynchronous memory interface capable of communicating with 8-, 16-, or 32-bit memory. There are two chip selects. The interface is byte addressable, with 20 address lines and individual byte enables. The memory is controlled with separate output, read, and write enables. A ready input to the DSP is available to indicate a memory is not ready. When using 8-bit or 16-bit memory the physical connection of the memory depends on the endianness of the DSP. For little endian mode of operation, the memory is attached to the low-numbered data lines. For big endian mode, the memory is attached to the high-numbered data lines.

The addressable memory for both memory spaces are identical, offering the full 4MB of memory to the daughtercards:  $DC_EA[21:2] = 0x000000 - 0xFFFFF$  (byte address range = 0x000000 - 0x3FFFFF).

• **C5402 DSK:** The C5402 has a 16-bit memory interface, which is available to the daughtercard. This includes three memory areas (data, program, and I/O), 20 address lines (16-bit word addressing), and strobes for control. There are two types of strobes present. One is the read, write, and output enables as in the C6201 EVM. Additionally there is an I/O strobe and a memory strobe. The C5402 DSK also supports 32-bit wide memory. The additional data lines are present on the connectors and on-board logic controls accessing 32-bit words rather than 16-bit words. This is included to support cards initially designed for use with the C6201 EVM.

The addressable memory is not identical between the three memory areas. The data memory space (DS#) offers the full address range to the daughtercard:  $DC_A[19:0] = 0x00000 - 0xFFFFF$ . Data memory on the daughtercard can be accessed either as 16-bit or 32-bit words, which results in 1M x 16 or 1M x 32 bits of addressable memory. The two upper address bits  $DC_A[21:20]$  are used for 32-bit data accesses only, and are generated by hardware on the motherboard.

The I/O memory space (IS#) also offers the full address range to the daughtercard:  $DC_A[19:0] = 0x00000 - 0xFFFFF$ . This memory can only be accessed as 16-bit words, resulting in 1M x 16 bits of addressable memory.

The program memory space (PS#) has a reduced address range available to the daughtercard due to the program memory located on the motherboard. Half of the external program memory space is available:  $DC_A[19:0] = 0x80000 - 0xFFFFF$ . The memory can only be accessed as 16-bit words, resulting in 512k x 16 bits of addressable memory.

• **C6202 EVM:** The C6202 EVM uses the expansion bus as the parallel interface, which has several differences from the external memory interface. It supports 32-bit data only, is word

addressable, and has a limited address range of 16 words. The asynchronous memory control is identical to that of the C6201 EVM. Additionally, synchronous FIFOs are supported by the memory interface.

The addressable memory of the expansion bus is limited to 16 x 32-bit words per chip enable. This constitutes a daughtercard address range of  $DC_EA[21:2] = 0x00000 - 0x0000F$  for each of the four chip enables.

#### Serial Ports

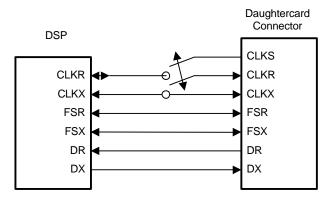

All of the interfaces documented provide a serial interface to the daughtercard. There are some architectural differences in the DSPs that cause the functionality present to vary slightly, as described in the following list:

- **C6201 EVM, C6202 EVM, C6711 DSK:** The C6201 EVM, C6202 EVM, and C6711 DSK provide two 7-signal serial ports to the daughtercard. This includes clock, frame, and data signals for both the transmit and receive data streams, as well as a clock input to operate the serial port asynchronously to the DSP. Of the two serial interfaces present, one is dedicated to the daughtercard and one is selectable between the daughtercard and system hardware. The serial port signals may optionally be used as general-purpose I/O.

- **C6211 DSK:** The C6211 DSK provides one instance of the 7-signal serial port described above. This serial port is dedicated to the daughtercard.

- **C5402 DSK:** The C5402 DSK provides two 6-signal serial ports to the daughtercard. The serial ports are identical to those listed above, minus the external clock source input. If the clocks and or frame signals are to be generated internally by the DSP, they must be based on the internal clock.

#### Timers

The on-chip timers are made available to the daughtercard as well. The architectural differences between the timers of the DSPs are:

- C6201 EVM, C6211 DSK, C6711 DSK, C6202 EVM: Each of the two timers available consist of an input signal and an output signal. The input can be used as either a general-purpose input or as an event to be counted internally. Likewise the output signal can either be a general-purpose output, a periodic pulse, or a clock output.

- **C5402 DSK:** The C5402 DSK provides only one timer signal, TOUT0. This signal can provide a periodic pulse every time the counter for timer 0 underflows.

### Interrupts

There are various levels of interrupt resources present on the different daughtercard interfaces.

• **C6201 EVM:** The C6201 EVM provides a single interrupt for the daughtercard to provide events to the DSP.

- **C6211 DSK:** The C6211 DSK provides five interrupts for the daughtercard to signal events. This includes the four maskable interrupts plus the non-maskable (system) interrupt.

- **C6711 DSK:** The C6711 DSK provides four external interrupts for the daughtercard. It does not provide the non-maskable interrupt.

- **C5402 DSK:** The C5402 DSK provides four external interrupts for the daughtercard to generate events to the DSP. Additionally there is an interrupt to the daughtercard for the DSP or system to provide events to the daughtercard.

- C6202 EVM: The C6202 EVM provides four maskable interrupts as well as the nonmaskable interrupt for the daughtercard.

#### Status and Control Signals

The interfaces have several degrees of status signals, as follows:

- **C6201 EVM, C6202 EVM:** The C6201 EVM provides all the status signals present on the DSP. There is an interrupt acknowledge and interrupt number signals to indicate interrupts being serviced by the CPU. The DMA action complete signals are also provided to notify the daughtercard of DMA status and conditions. The DMA signals can also be use as general-purpose outputs. The system reset is provided to the daughtercard to synchronize with system resets. The powerdown signal is provided to inform the daughtercard when the DSP enters a low power mode (PD2 or PD3).

- **C6211 DSK, C6711 DSK:** The C6211 and C6711 DSKs do not have the status indicators that are present on the C6201. The DSKs provide only the reset signal to the daughtercard.

- **C5402 DSK:** The C5402 DSK provides several signals to the daughtercard for status and control. There are the interrupt acknowledge, instruction acquisition, branch control input, external flag output, microstate complete, and reset signals.

#### General-Purpose I/O

Several of the interfaces have general-purpose signals present to communicate between the DSP (or system) and the daughtercard.

- C6201 EVM, C6211 DSK, C6711 DSK, C5402 DSK: These EVMs and DSKs have two general-purpose inputs and two outputs for communication. These are referred to as status and control signals, respectively.

- **C6202 EVM:** The C6202 EVM does not have any general-purpose I/O. For this functionality it is necessary to use a peripheral signal in GPIO mode.

#### Host Interface

The C6202 EVM is currently has the only daughtercard interface that includes a host port. The expansion bus used for the parallel memory interface portion of the daughtercard interface is dual-purpose. It allows the DSP to access external asynchronous memory or synchronous FIFOs, and it also acts as a host port. The expansion bus can be used as a 32-bit asynchronous host port interface or a 32-bit synchronous host interface.

# 2.5 Physical Daughtercard Layout

Daughtercards designed to attach to a DSP motherboard must conform to the requirements documented in this section. The daughtercard interface consists of two signal connectors that present both an external memory interface as well as numerous peripheral signals. The physical dimensions of the daughtercard allow mounting the card on a PCI DSP motherboard while allowing the attached motherboard and daughtercard to fit within a single PCI slot of a PC. While the specification is not restricted to PCI applications, the physical dimensions of the daughtercard must fit within the maximum dimensions outlined below to be compliant.

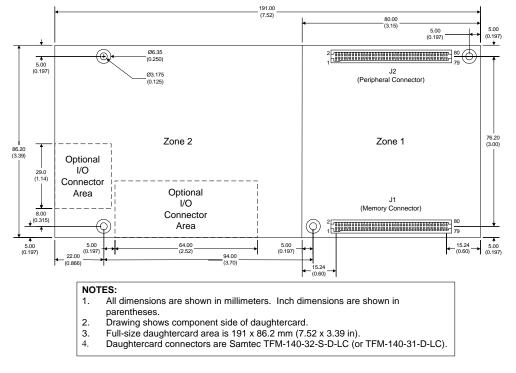

A daughtercard may be designed to use some or all of the signals presented by the daughtercard interfaces on the DSP motherboards. Likewise, a daughtercard may be physically any size that fits within the maximum dimension of 191 x 86.2mm. Mounting holes are provided on both the daughtercard and the DSP board to allow stability. The daughtercard layout is shown in Figure 2. Note that the diagram shows the component side of the daughtercard.

Figure 2. Daughtercard Layout

# 2.6 Daughtercard Connectors and Component Height

The interface on the daughtercard consists of two of any 80-pin TFM series connectors from Samtec. It is highly recommended that the largest connectors be used, as they allow the most height for components on the daughtercard. The recommended part numbers are shown in Table 12. The connectors listed for the daughtercard offer a sufficient mating height to meet the PCI's maximum component height of 14.48mm (0.57in). This mating height allows for passive components on the back side of the daughtercard that is to be attached to a PCI motherboard. Details on height restrictions of components in the daughtercard area are provided later in the document.

| Table 12. | Daughtercard Interface Connector Part Numbers |

|-----------|-----------------------------------------------|

|-----------|-----------------------------------------------|

| Location        | Part Number                       | Mating Height     |

|-----------------|-----------------------------------|-------------------|

| DSP Motherboard | SFM-140-L2-S-D-LC                 |                   |

| Daughtercard    | TFM-140-32-S-D-LC (surface mount) | 11.81mm (0.465in) |

|                 | TFM-140-31-S-D-LC (through-hole)  | 11.43mm (0.450in) |

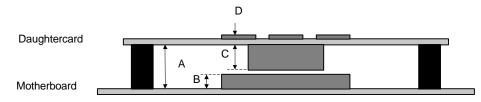

Figure 3 depicts a mounted daughtercard designed to attach to a PCI DSP board and fit within a single PCI slot. It is assumed that a minimum of 1.27mm (0.050in)<sup>4</sup> clearance is maintained between components. The component heights for the pair are provided in Table 13.

| Label | Description                                            | Dimension         | Dimension         |

|-------|--------------------------------------------------------|-------------------|-------------------|

|       |                                                        | (Zone 1)          | (Zone 2)          |

| А     | Mated Height                                           | 11.81mm (0.465in) | 11.81mm (0.465in) |

| В     | Maximum motherboard Component Height                   | 3.81mm (0.150in)  | 4.78mm (0.180in)  |

| С     | Maximum Daughtercard Component Height                  | 6.73mm (0.265in)  | 5.97mm (0.235in)  |

| D     | Maximum "bottom-side" daughtercard component<br>height | 1.00mm (0.039in)  | 1.00mm (0.039in)  |

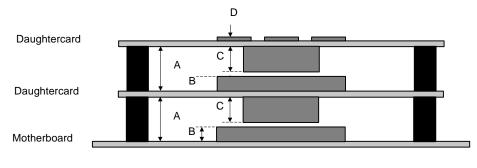

If a daughtercard is designed that is not required to fit within a single PCI slot, then there is more flexibility with the 'D' dimension shown. In this case, components on the back side of the board can be any height, allowing any size component or connector to be present on the daughtercard.