# Variable-Length Decoding on the TMS320C6000 DSP Platform

Oliver Sohm

TMS320C6000 Software Applications

#### ABSTRACT

The TMS320C62x<sup>™</sup> and the TMS320C64x<sup>™</sup> DSPs are well suited for high-performance applications such as image and video decoding. Efficient implementation of core decoding steps such as inverse discrete cosine transform (DCT), variable-length decoding, dequantization, and motion compensation is essential for achieving the best possible performance. This application report focuses on optimized implementations of variable-length decoding for the standards MPEG-2 (ISO/IEC 11172 Part 2: Video), ITU-T H.263, and JPEG[1–3]. Ready-to-use solutions are presented as well as an in-depth treatment of optimization techniques.

Optimization of variable-length decoding (VLD) routines can be difficult, because of their inherently serial data flow which makes exploiting parallelism on VLIW-type architectures more challenging. Techniques for optimization and robustness are discussed including bitstream buffer management, look-up table organization, handling of irregular loops, error behavior and exploiting parallelism across multiple decoding steps by integrating VLD with run-length expansion, inverse zigzag, dequantization, saturation and mismatch control. By applying these optimization techniques very good performance can be achieved. For instance, the performance of the MPEG-2 VLD presented here is 10 cycles per decoded symbol plus an overhead of 37 cycles per decoded block for non-intra coded macroblocks. For decoding a 4 Mbit/s MPEG-2 bitstream and assuming 5 bits per coded symbol, the processor load is only about 1.7% on a 600 MHz C64x. This level of performance combined with the flexibility of a software implementation can be a significant advantage over VLD co-processors.

Source code of implementations and examples are available in the attached zip archive. The latest versions of the MPEG-2 VLD routines can be found in the *TMS320C62x Image/Video Processing Library* and *TMS320C64x Image/Video Processing Library*.

|   |                                     | Contents                                                |      |  |  |

|---|-------------------------------------|---------------------------------------------------------|------|--|--|

| 1 | Intro                               | oduction                                                | 4    |  |  |

| 2 | MP                                  | EG-2 Variable-Length Decoding                           | 7    |  |  |

|   | 2.1                                 | Decoding Process                                        | 7    |  |  |

|   |                                     | 2.1.1 Decoding and Dequantization of Intra DC           | 7    |  |  |

|   |                                     | 2.1.2 Decoding and Dequantization of Other Coefficients | 8    |  |  |

|   | 2.2 Possible Ways of Implementation |                                                         |      |  |  |

|   | 2.3                                 | Bitstream Management                                    | . 10 |  |  |

|   |                                     |                                                         |      |  |  |

TMS320C62x and TMS320C64x are trademarks of Texas Instruments.

Trademarks are the property of their respective owners.

| 2.4.1       Length Computation         2.4.2       Run-Level Decoding         2.4.3       Inverse Zigzag, Dequantization, Saturation and Mismatch Control         2.5       First Coefficients         2.5.1       Intra Blocks         2.5.2       Non-Intra Blocks         2.5.1       Intra VLD         2.6.2       Non-Intra VLD         2.6.1       Intra VLD         2.6.2       Non-Intra VLD         2.7.1       Critical Recurrence Path         2.7.2       Circular-Addressing Mode         2.7.3       General Optimizations         2.7.4       Partitioned Linear Assembly Code for AC Decoding Loop         2.7.5       Live-Out Variables         2.7.6       Error Behavior Analysis         2.7.7       Software Pipelined AC Decoding Loop (Intra)         2.7.8       Implementation Notes and Special Requirements         2.8       Optimizations for C64x         2.8.1       Implementation Notes and Special Requirements         2.9       Performance Summary         2.10       Performance Considerations for Cached Architectures         3       H.263 Variable-Length Decoding         3.1       Decoding Process         3.2       Bitstream Management <t< th=""><th></th><th>2.4</th><th>Intra and Non-Intra AC Decoding Loop</th><th> 11</th></t<> |   | 2.4  | Intra and Non-Intra AC Decoding Loop                                  | 11 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|-----------------------------------------------------------------------|----|

| 2.4.3       Inverse Zigzag, Dequantization, Saturation and Mismatch Control         2.5.5       First Coefficients         2.5.1       Intra Blocks         2.6.2       Non-Intra Blocks         2.6.1       Intra VLD         2.6.2       Non-Intra VLD         2.6.3       Non-Intra VLD         2.6.4       Intra VLD         2.6.7       Optimizations for C62x         2.7.1       Critical Recurrence Path         2.7.2       Circular-Addressing Mode         2.7.3       General Optimizations         2.7.4       Partitioned Linear Assembly Code for AC Decoding Loop         2.7.5       Live-Out Variables         2.7.7       Software Pipelined AC Decoding Loop (Intra)         2.7.8       Implementation Notes and Special Requirements         2.8.0       Performance Summary         2.10       Performance Considerations for Cached Architectures         3       H.263 Variable-Length Decoding         3.1       Decoding Process         3.2       Bitstream Management         3.3       Length Computation         3.4       Last-Run-Level Decoding         3.5       Escape Sequence         3.6       Inverse Zigzag and Dequantization         3.7<                                                                                                   |   |      | 2.4.1 Length Computation                                              | 11 |

| 2.5       First Coefficients         2.5.1       Intra Blocks         2.5.2       Non-Intra Blocks         2.6       C Model Code         2.6.1       Intra VLD         2.6.2       Non-Intra VLD         2.7.4       Circular-Addressing Mode         2.7.7       Circular-Addressing Mode         2.7.8       Enror Behavior Analysis         2.7.4       Partitioned Linear Assembly Code for AC Decoding Loop         2.7.5       Live-Out Variables         2.7.6       Error Behavior Analysis         2.7.7       Software Pipelined AC Decoding Loop (Intra)         2.7.8       Implementation Notes and Special Requirements         2.8       Optimizations for C64x         2.8       Implementation Notes and Special Requirements         2.9       Performance Considerations for Cached Architectures         3       H.263 Variable-Length Decoding         3.1       Decoding Process         3.2       Bitstream Management         3.3       Length Computation         3.4       Last-Run-Level Decoding         3.5       Escape Sequence         3.6       Inverse Zigzag and Dequantization         3.7       Froro Detection and Behavior         3.8                                                                                                         |   |      | 2.4.2 Run-Level Decoding                                              | 13 |

| 2.5.1       Intra Blocks         2.6.2       Non-Intra Blocks         2.6.1       Intra VLD         2.6.2       Non-Intra VLD         2.7       Optimizations for C62x         2.7.1       Critical Recurrence Path         2.7.2       Circular-Addressing Mode         2.7.3       General Optimizations         2.7.4       Partitioned Linear Assembly Code for AC Decoding Loop         2.7.5       Live-Out Variables         2.7.6       Error Behavior Analysis         2.7.7       Software Pipelined AC Decoding Loop (Intra)         2.7.8       Implementation Notes and Special Requirements         2.8.1       Implementation Notes and Special Requirements         2.8.2       Performance Summary         2.10       Performance Considerations for Cached Architectures         3       H.263 Variable-Length Decoding         .3.1       Decoding Process         .3.2       Bitstream Management         .3.3       Length Decoding         .3.4       Last-Run-Level Decoding         .3.5       Escape Sequence         .3.6       Inverse Zigzag and Dequantization         .3.7       Error Detection and Behavior         .3.8       C Model Code                                                                                                            |   |      | 2.4.3 Inverse Zigzag, Dequantization, Saturation and Mismatch Control | 15 |

| 2.5.2       Non-Intra Blocks         2.6.1       Intra VLD         2.6.2       Non-Intra VLD         2.7.1       Critical Recurrence Path         2.7.2       Circular-Addressing Mode         2.7.3       General Optimizations         2.7.4       Partitioned Linear Assembly Code for AC Decoding Loop         2.7.5       Live-Out Variables         2.7.6       Error Behavior Analysis         2.7.7       Software Pipelined AC Decoding Loop (Intra)         2.7.8       Implementation Notes and Special Requirements         2.8       Optimizations for C64x         2.8.1       Implementation Notes and Special Requirements         2.9       Performance Considerations for Cached Architectures         3       H.263 Variable-Length Decoding         3.1       Decoding Process         3.2       Bitstream Management         3.3       Length Computation         3.4       Last-Run-Level Decoding         3.5       Escape Sequence         3.6       Inverse Zigzag and Dequantization         3.7       Fror Detection and Behavior         3.8       Godel Code         3.9       Assembly Implementations         4       JPEG Variable-Length Decoding                                                                                                     |   | 2.5  | First Coefficients                                                    | 16 |

| 2.6 C Model Code         2.6.1 Intra VLD         2.6.2 Non-Intra VLD         2.7 Optimizations for C62x         2.7.1 Critical Recurrence Path         2.7.2 Circular-Addressing Mode         2.7.3 General Optimizations         2.7.4 Partitioned Linear Assembly Code for AC Decoding Loop         2.7.5 Live-Out Variables         2.7.6 Error Behavior Analysis         2.7.7 Software Pipelined AC Decoding Loop (Intra)         2.7.8 Implementation Notes and Special Requirements         2.8 Optimizations for C64x         2.8.1 Implementation Notes and Special Requirements         2.9 Performance Summary         2.10 Performance Considerations for Cached Architectures         3 H.263 Variable-Length Decoding         3.1 Decoding Process         3.2 Bitstream Management         3.3 Length Computation         3.4 East-Run-Level Decoding         3.5 Escape Sequence         3.6 Inverse Zigzag and Dequantization         3.7 Firor Detection and Behavior         3.8 C Model Code         3.9 Assembly Implementations         4 JPEG Variable-Length Decoding         4.1 Bitstream Management         4.2 Look-Up Table Layout         4.3 Initialization         4.3.1 Initialization         4.3.2 Decoding Loop                                    |   |      | 2.5.1 Intra Blocks                                                    | 16 |

| 2.6.1       Intra VLD         2.6.2       Non-Intra VLD         2.7       Optimizations for C62x         2.7.1       Critical Recurrence Path         2.7.2       Circular-Addressing Mode         2.7.3       General Optimizations         2.7.4       Partitioned Linear Assembly Code for AC Decoding Loop         2.7.5       Live-Out Variables         2.7.6       Error Behavior Analysis         2.7.7       Software Pipelined AC Decoding Loop (Intra)         2.7.8       Implementation Notes and Special Requirements         2.8       Optimizations for C64x         2.8.1       Implementation Notes and Special Requirements         2.9       Performance Summary         2.10       Performance Considerations for Cached Architectures         3       I. Decoding Process         3.1       Decoding Process         3.2       Bitstream Management         3.3       Largt And Dequantization         3.4       Last-Run-Level Decoding         3.5       Escape Sequence         3.6       Inverse Zigzag and Dequantization         3.7       Fror Detection and Behavior         3.8       C Model Code         3.9       Assembly Implementations <td< td=""><td></td><td></td><td>2.5.2 Non-Intra Blocks</td><td> 19</td></td<>                            |   |      | 2.5.2 Non-Intra Blocks                                                | 19 |

| 2.6.2 Non-Intra VLD         2.7 Optimizations for C62x         2.7.1 Critical Recurrence Path         2.7.2 Circular-Addressing Mode         2.7.3 General Optimizations         2.7.4 Partitioned Linear Assembly Code for AC Decoding Loop         2.7.5 Live-Out Variables         2.7.6 Error Behavior Analysis         2.7.7 Software Pipelined AC Decoding Loop (Intra)         2.7.8 Implementation Notes and Special Requirements         2.8 Optimizations for C64x         2.8.1 Implementation Notes and Special Requirements         2.9 Performance Considerations for Cached Architectures         3.1 Decoding Process         3.2 Bitstream Management         3.3 Length Computation         3.4 Last-Run-Level Decoding         3.5 Escape Sequence         3.6 Inverse Zigzag and Dequantization         3.7 Error Detection and Behavior         3.8 C Model Code         3.9 Assembly Implementations         4 JPEG Variable-Length Decoding         4.1 Bitstream Management         4.2 Lock-Up Table Layout         4.3 Implementation         4.4 C Model Code         4.5 Assembly Implementations         5 Review of Implementation Techniques         5.1 Inherent Problems         5.1.2 While Loop                                                     |   | 2.6  | C Model Code                                                          | 20 |

| 2.7       Optimizations for C62x         2.7.1       Critical Recurrence Path         2.7.2       Circular-Addressing Mode         2.7.3       General Optimizations         2.7.4       Partitioned Linear Assembly Code for AC Decoding Loop         2.7.5       Live-Out Variables         2.7.6       Error Behavior Analysis         2.7.7       Software Pipelined AC Decoding Loop (Intra)         2.7.8       Implementation Notes and Special Requirements         2.8.1       Implementation Notes and Special Requirements         2.8       Optimizations for C64x         2.8.1       Implementation Notes and Special Requirements         2.9       Performance Summary         2.10       Performance Considerations for Cached Architectures         3       H.263 Variable-Length Decoding         3.1       Decoding Process         3.2       Bitstream Management         3.3       Length Computation         3.4       Last-Run-Level Decoding         3.5       Escape Sequence         3.6       Inverse Zigzag and Dequantization         3.7       Error Detection and Behavior         3.8       C Model Code         3.9       Assembly Implementations         4       J Bitstre                                                                         |   |      | 2.6.1 Intra VLD                                                       | 22 |

| 2.7.1       Critical Recurrence Path         2.7.2       Circular-Addressing Mode         2.7.3       General Optimizations         2.7.4       Partitioned Linear Assembly Code for AC Decoding Loop         2.7.5       Live-Out Variables         2.7.6       Error Behavior Analysis         2.7.7       Software Pipelined AC Decoding Loop (Intra)         2.7.8       Implementation Notes and Special Requirements         2.8       Optimizations for C64x         2.8.1       Implementation Notes and Special Requirements         2.9       Performance Summary         2.10       Performance Considerations for Cached Architectures         3       H.263 Variable-Length Decoding         3.1       Decoding Process         3.2       Bitstream Management         3.3       Length Computation         3.4       Last-Run-Level Decoding         3.5       Escape Sequence         3.6       Inverse Zigzag and Dequantization         3.7       Fror Detection and Behavior         3.8       C Model Code         3.9       Assembly Implementations         4       JPEG Variable-Length Decoding         4.1       Bitstream Management         4.2       Look-Up Table Layout                                                                                   |   |      | 2.6.2 Non-Intra VLD                                                   | 29 |

| 2.7.2       Circular-Addressing Mode         2.7.3       General Optimizations         2.7.4       Partitioned Linear Assembly Code for AC Decoding Loop         2.7.5       Live-Out Variables         2.7.6       Error Behavior Analysis         2.7.7       Software Pipelined AC Decoding Loop (Intra)         2.7.8       Implementation Notes and Special Requirements         2.8       Optimizations for C64x         2.8.1       Implementation Notes and Special Requirements         2.9       Performance Summary         2.10       Performance Considerations for Cached Architectures         3.1       Decoding Process         3.2       Bitstream Management         3.3       Length Computation         3.4       Last-Run-Level Decoding         3.5       Escape Sequence         3.6       Inverse Zigzag and Dequantization         3.7       Error Detection and Behavior         3.8       C Model Code         3.9       Assembly Implementations         4       JPEG Variable-Length Decoding         4.1       Bitstream Management         4.2       Look-Up Table Layout         4.3       Implementation         4.3.1       Initialization <t< td=""><td></td><td>2.7</td><td>Optimizations for C62x</td><td> 37</td></t<>                          |   | 2.7  | Optimizations for C62x                                                | 37 |

| <ul> <li>2.7.3 General Optimizations .</li> <li>2.7.4 Partitioned Linear Assembly Code for AC Decoding Loop .</li> <li>2.7.5 Live-Out Variables .</li> <li>2.7.6 Error Behavior Analysis .</li> <li>2.7.7 Software Pipelined AC Decoding Loop (Intra) .</li> <li>2.7.8 Implementation Notes and Special Requirements .</li> <li>2.8 Optimizations for C64x .</li> <li>2.8.1 Implementation Notes and Special Requirements .</li> <li>2.9 Performance Summary .</li> <li>2.10 Performance Considerations for Cached Architectures .</li> <li>3 H.263 Variable-Length Decoding .</li> <li>3.1 Decoding Process .</li> <li>3.2 Bitstream Management .</li> <li>3.3 Length Computation .</li> <li>3.4 Last-Run-Level Decoding .</li> <li>3.5 Escape Sequence .</li> <li>3.6 Inverse Zigzag and Dequantization .</li> <li>3.7 Error Detection and Behavior .</li> <li>3.8 C Model Code .</li> <li>3.9 Assembly Implementations .</li> <li>4 JPEG Variable-Length Decoding</li></ul>                                                                                                                                                                                                                                                                                                         |   |      | 2.7.1 Critical Recurrence Path                                        | 37 |

| <ul> <li>2.7.4 Partitioned Linear Assembly Code for AC Decoding Loop</li> <li>2.7.5 Live-Out Variables</li> <li>2.7.6 Error Behavior Analysis</li> <li>2.7.7 Software Pipelined AC Decoding Loop (Intra)</li> <li>2.7.8 Implementation Notes and Special Requirements</li> <li>2.8 Optimizations for C64x</li> <li>2.8.1 Implementation Notes and Special Requirements</li> <li>2.9 Performance Summary</li> <li>2.10 Performance Considerations for Cached Architectures</li> <li>3 H.263 Variable-Length Decoding</li> <li>3.1 Decoding Process</li> <li>3.2 Bitstream Management</li> <li>3.3 Length Computation</li> <li>3.4 Last-Run-Level Decoding</li> <li>3.5 Escape Sequence</li> <li>3.6 Inverse Zigzag and Dequantization</li> <li>3.7 Error Detection and Behavior</li> <li>3.8 C Model Code</li> <li>3.9 Assembly Implementations</li> <li>4 JPEG Variable-Length Decoding</li> <li>4.3 Imitialization</li> <li>4.3.2 Decoding Loop</li> <li>4.4 C Model Code</li> <li>4.5 Assembly Implementations</li> <li>5 Review of Implementation Techniques</li> <li>5.1.1 Recurrence Path</li> <li>5.1.2 While Loop</li> </ul>                                                                                                                                                    |   |      | 2.7.2 Circular-Addressing Mode                                        | 39 |

| <ul> <li>2.7.5 Live-Out Variables</li> <li>2.7.6 Error Behavior Analysis</li> <li>2.7.7 Software Pipelined AC Decoding Loop (Intra)</li> <li>2.7.8 Implementation Notes and Special Requirements</li> <li>2.8 Optimizations for C64x</li> <li>2.8.1 Implementation Notes and Special Requirements</li> <li>2.9 Performance Summary</li> <li>2.10 Performance Considerations for Cached Architectures</li> <li>3 H.263 Variable-Length Decoding</li> <li>3.1 Decoding Process</li> <li>3.2 Bitstream Management</li> <li>3.3 Length Computation</li> <li>3.4 Last-Run-Level Decoding</li> <li>3.5 Escape Sequence</li> <li>3.6 Inverse Zigzag and Dequantization</li> <li>3.7 Error Detection and Behavior</li> <li>3.8 C Model Code</li> <li>3.9 Assembly Implementations</li> </ul> 4 JPEG Variable-Length Decoding <ul> <li>4.1 Bitstream Management</li> <li>4.2 Look-Up Table Layout</li> <li>4.3 Implementation</li> <li>4.3.1 Initialization</li> <li>4.3.2 Decoding Loop</li> <li>4.4 C Model Code</li> <li>4.5 Assembly Implementations</li> </ul> 5 Review of Implementation Techniques <ul> <li>5.1 Inherent Problems</li> <li>5.1.2 While Loop</li> </ul>                                                                                                                   |   |      | 2.7.3 General Optimizations                                           | 40 |

| <ul> <li>2.7.6 Error Behavior Analysis</li> <li>2.7.7 Software Pipelined AC Decoding Loop (Intra)</li> <li>2.7.8 Implementation Notes and Special Requirements</li> <li>2.8 Optimizations for C64x</li> <li>2.8.1 Implementation Notes and Special Requirements</li> <li>2.9 Performance Summary</li> <li>2.10 Performance Considerations for Cached Architectures</li> <li>3 H.263 Variable-Length Decoding</li> <li>3.1 Decoding Process</li> <li>3.2 Bitstream Management</li> <li>3.3 Length Computation</li> <li>3.4 Last-Run-Level Decoding</li> <li>3.5 Escape Sequence</li> <li>3.6 Inverse Zigzag and Dequantization</li> <li>3.7 Error Detection and Behavior</li> <li>3.8 C Model Code</li> <li>3.9 Assembly Implementations</li> <li>4 JPEG Variable-Length Decoding</li> <li>4.1 Bitstream Management</li> <li>4.2 Look-Up Table Layout</li> <li>4.3 Implementation</li> <li>4.3.1 Initialization</li> <li>4.3.2 Decoding Loop</li> <li>4.4 C Model Code</li> <li>4.5 Assembly Implementations</li> </ul>                                                                                                                                                                                                                                                                 |   |      | 2.7.4 Partitioned Linear Assembly Code for AC Decoding Loop           | 40 |

| <ul> <li>2.7.7 Software Pipelined AC Decoding Loop (Intra)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |      | 2.7.5 Live-Out Variables                                              | 42 |

| <ul> <li>2.7.8 Implementation Notes and Special Requirements</li> <li>2.8 Optimizations for C64x</li> <li>2.8.1 Implementation Notes and Special Requirements</li> <li>2.9 Performance Summary</li> <li>2.10 Performance Considerations for Cached Architectures</li> <li>3 H.263 Variable-Length Decoding</li> <li>3.1 Decoding Process</li> <li>3.2 Bitstream Management</li> <li>3.3 Length Computation</li> <li>3.4 Last-Run-Level Decoding</li> <li>3.5 Escape Sequence</li> <li>3.6 Inverse Zigzag and Dequantization</li> <li>3.7 Error Detection and Behavior</li> <li>3.8 C Model Code</li> <li>3.9 Assembly Implementations</li> </ul> 4 JPEG Variable-Length Decoding <ul> <li>4.1 Bitstream Management</li> <li>4.2 Look-Up Table Layout</li> <li>4.3 Implementation</li> <li>4.3.2 Decoding Loop</li> <li>4.4 C Model Code</li> <li>4.5 Assembly Implementations</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                               |   |      | 2.7.6 Error Behavior Analysis                                         | 43 |

| <ul> <li>2.8 Optimizations for C64x <ul> <li>2.8.1 Implementation Notes and Special Requirements</li> <li>2.9 Performance Summary</li> <li>2.10 Performance Considerations for Cached Architectures</li> </ul> </li> <li>3 H.263 Variable-Length Decoding <ul> <li>3.1 Decoding Process</li> <li>3.2 Bitstream Management</li> <li>3.3 Length Computation</li> <li>3.4 Last-Run-Level Decoding</li> <li>3.5 Escape Sequence</li> <li>3.6 Inverse Zigzag and Dequantization</li> <li>3.7 Error Detection and Behavior</li> <li>3.8 C Model Code</li> <li>3.9 Assembly Implementations</li> </ul> </li> <li>4 JPEG Variable-Length Decoding <ul> <li>4.1 Bitstream Management</li> <li>4.2 Look-Up Table Layout</li> <li>4.3 Implementation</li> <li>4.3.1 Initialization</li> <li>4.3.2 Decoding Loop</li> <li>4.4 C Model Code</li> <li>4.5 Assembly Implementations</li> </ul> </li> <li>5 Review of Implementation Techniques <ul> <li>5.1 Inherent Problems</li> <li>5.1.2 While Loop</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                        |   |      | 2.7.7 Software Pipelined AC Decoding Loop (Intra)                     | 44 |

| <ul> <li>2.8.1 Implementation Notes and Special Requirements</li> <li>2.9 Performance Summary</li> <li>2.10 Performance Considerations for Cached Architectures</li> <li>3 H.263 Variable-Length Decoding</li> <li>3.1 Decoding Process</li> <li>3.2 Bitstream Management</li> <li>3.3 Length Computation</li> <li>3.4 Last-Run-Level Decoding</li> <li>3.5 Escape Sequence</li> <li>3.6 Inverse Zigzag and Dequantization</li> <li>3.7 Error Detection and Behavior</li> <li>3.8 C Model Code</li> <li>3.9 Assembly Implementations</li> <li>4 JPEG Variable-Length Decoding</li> <li>4.1 Bitstream Management</li> <li>4.2 Look-Up Table Layout</li> <li>4.3 Implementation</li> <li>4.3.2 Decoding Loop</li> <li>4.4 C Model Code</li> <li>4.5 Assembly Implementations</li> </ul> 5 Review of Implementation Techniques 5.1 Inherent Problems 5.1.2 While Loop                                                                                                                                                                                                                                                                                                                                                                                                                     |   |      | 2.7.8 Implementation Notes and Special Requirements                   | 46 |

| <ul> <li>2.9 Performance Summary</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 2.8  | Optimizations for C64x                                                | 46 |

| <ul> <li>2.10 Performance Considerations for Cached Architectures</li> <li>3.1 Decoding Process</li> <li>3.2 Bitstream Management</li> <li>3.3 Length Computation</li> <li>3.4 Last-Run-Level Decoding</li> <li>3.5 Escape Sequence</li> <li>3.6 Inverse Zigzag and Dequantization</li> <li>3.7 Error Detection and Behavior</li> <li>3.8 C Model Code</li> <li>3.9 Assembly Implementations</li> <li>4 JPEG Variable-Length Decoding</li> <li>4.1 Bitstream Management</li> <li>4.2 Look-Up Table Layout</li> <li>4.3 Implementation</li> <li>4.3.1 Initialization</li> <li>4.3.2 Decoding Loop</li> <li>4.4 C Model Code</li> <li>5 Assembly Implementations</li> </ul> 5 Review of Implementation Techniques 5.1 Inherent Problems <ul> <li>5.1.2 While Loop</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |      | 2.8.1 Implementation Notes and Special Requirements                   | 50 |

| <ul> <li>3 H.263 Variable-Length Decoding</li> <li>3.1 Decoding Process</li> <li>3.2 Bitstream Management</li> <li>3.3 Length Computation</li> <li>3.4 Last-Run-Level Decoding</li> <li>3.5 Escape Sequence</li> <li>3.6 Inverse Zigzag and Dequantization</li> <li>3.7 Error Detection and Behavior</li> <li>3.8 C Model Code</li> <li>3.9 Assembly Implementations</li> <li>4 JPEG Variable-Length Decoding</li> <li>4.1 Bitstream Management</li> <li>4.2 Look-Up Table Layout</li> <li>4.3 Implementation</li> <li>4.3.1 Initialization</li> <li>4.3.2 Decoding Loop</li> <li>4.4 C Model Code</li> <li>4.5 Assembly Implementations</li> </ul> 5 Review of Implementation Techniques 5.1 Inherent Problems <ul> <li>5.1.1 Recurrence Path</li> <li>5.1.2 While Loop</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 2.9  | Performance Summary                                                   | 50 |

| <ul> <li>3.1 Decoding Process</li> <li>3.2 Bitstream Management</li> <li>3.3 Length Computation</li> <li>3.4 Last-Run-Level Decoding</li> <li>3.5 Escape Sequence</li> <li>3.6 Inverse Zigzag and Dequantization</li> <li>3.7 Error Detection and Behavior</li> <li>3.8 C Model Code</li> <li>3.9 Assembly Implementations</li> </ul> 4 JPEG Variable-Length Decoding <ul> <li>4.1 Bitstream Management</li> <li>4.2 Look-Up Table Layout</li> <li>4.3 Implementation</li> <li>4.3.1 Initialization</li> <li>4.3.2 Decoding Loop</li> <li>4.4 C Model Code</li> <li>4.5 Assembly Implementations</li> </ul> 5 Review of Implementation Techniques 5.1 Inherent Problems <ul> <li>5.1.1 Recurrence Path</li> <li>5.1.2 While Loop</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | 2.10 | Performance Considerations for Cached Architectures                   | 51 |

| <ul> <li>3.1 Decoding Process</li> <li>3.2 Bitstream Management</li> <li>3.3 Length Computation</li> <li>3.4 Last-Run-Level Decoding</li> <li>3.5 Escape Sequence</li> <li>3.6 Inverse Zigzag and Dequantization</li> <li>3.7 Error Detection and Behavior</li> <li>3.8 C Model Code</li> <li>3.9 Assembly Implementations</li> </ul> 4 JPEG Variable-Length Decoding <ul> <li>4.1 Bitstream Management</li> <li>4.2 Look-Up Table Layout</li> <li>4.3 Implementation</li> <li>4.3.1 Initialization</li> <li>4.3.2 Decoding Loop</li> <li>4.4 C Model Code</li> <li>4.5 Assembly Implementations</li> </ul> 5 Review of Implementation Techniques 5.1 Inherent Problems <ul> <li>5.1.1 Recurrence Path</li> <li>5.1.2 While Loop</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |      |                                                                       |    |

| <ul> <li>3.2 Bitstream Management</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3 | H.20 | 63 Variable-Length Decoding                                           |    |

| <ul> <li>3.3 Length Computation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |      |                                                                       |    |

| <ul> <li>3.4 Last-Run-Level Decoding .</li> <li>3.5 Escape Sequence .</li> <li>3.6 Inverse Zigzag and Dequantization .</li> <li>3.7 Error Detection and Behavior .</li> <li>3.8 C Model Code .</li> <li>3.9 Assembly Implementations .</li> </ul> 4 JPEG Variable-Length Decoding . <ul> <li>4.1 Bitstream Management .</li> <li>4.2 Look-Up Table Layout .</li> <li>4.3 Implementation .</li> <li>4.3.1 Initialization .</li> <li>4.3.2 Decoding Loop .</li> <li>4.4 C Model Code .</li> <li>4.5 Assembly Implementations .</li> </ul> 5 Review of Implementation Techniques . <ul> <li>5.1 Inherent Problems .</li> <li>5.1.1 Recurrence Path .</li> <li>5.1.2 While Loop .</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | -    | 0                                                                     |    |

| <ul> <li>3.5 Escape Sequence</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |      | V I                                                                   |    |

| <ul> <li>3.6 Inverse Zigzag and Dequantization</li> <li>3.7 Error Detection and Behavior</li> <li>3.8 C Model Code</li> <li>3.9 Assembly Implementations</li> <li><b>JPEG Variable-Length Decoding</b></li> <li>4.1 Bitstream Management</li> <li>4.2 Look-Up Table Layout</li> <li>4.3 Implementation</li> <li>4.3.1 Initialization</li> <li>4.3.2 Decoding Loop</li> <li>4.4 C Model Code</li> <li>4.5 Assembly Implementations</li> </ul> <b>5 Review of Implementation Techniques</b> 5.1 Inherent Problems 5.1.1 Recurrence Path 5.1.2 While Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |      |                                                                       |    |

| <ul> <li>3.7 Error Detection and Behavior</li> <li>3.8 C Model Code</li> <li>3.9 Assembly Implementations</li> <li><b>JPEG Variable-Length Decoding</b></li> <li>4.1 Bitstream Management</li> <li>4.2 Look-Up Table Layout</li> <li>4.3 Implementation</li> <li>4.3.1 Initialization</li> <li>4.3.2 Decoding Loop</li> <li>4.4 C Model Code</li> <li>4.5 Assembly Implementations</li> </ul> 5 Review of Implementation Techniques <ul> <li>5.1 Inherent Problems</li> <li>5.1.1 Recurrence Path</li> <li>5.1.2 While Loop</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |      |                                                                       |    |

| <ul> <li>3.8 C Model Code</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      |                                                                       |    |

| <ul> <li>3.9 Assembly Implementations</li> <li>JPEG Variable-Length Decoding</li> <li>4.1 Bitstream Management</li> <li>4.2 Look-Up Table Layout</li> <li>4.3 Implementation</li> <li>4.3.1 Initialization</li> <li>4.3.2 Decoding Loop</li> <li>4.4 C Model Code</li> <li>4.5 Assembly Implementations</li> </ul> 5 Review of Implementation Techniques 5.1 Inherent Problems 5.1.1 Recurrence Path 5.1.2 While Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | -    |                                                                       |    |

| <ul> <li>JPEG Variable-Length Decoding</li> <li>4.1 Bitstream Management</li> <li>4.2 Look-Up Table Layout</li> <li>4.3 Implementation</li> <li>4.3.1 Initialization</li> <li>4.3.2 Decoding Loop</li> <li>4.4 C Model Code</li> <li>4.5 Assembly Implementations</li> </ul> 5 Review of Implementation Techniques 5.1 Inherent Problems 5.1.1 Recurrence Path 5.1.2 While Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |      |                                                                       |    |

| <ul> <li>JPEG Variable-Length Decoding</li> <li>4.1 Bitstream Management</li> <li>4.2 Look-Up Table Layout</li> <li>4.3 Implementation</li> <li>4.3.1 Initialization</li> <li>4.3.2 Decoding Loop</li> <li>4.4 C Model Code</li> <li>4.5 Assembly Implementations</li> </ul> 5 Review of Implementation Techniques 5.1 Inherent Problems 5.1.1 Recurrence Path 5.1.2 While Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 3.9  | Assembly Implementations                                              | 61 |

| <ul> <li>4.1 Bitstream Management</li> <li>4.2 Look-Up Table Layout</li> <li>4.3 Implementation</li> <li>4.3.1 Initialization</li> <li>4.3.2 Decoding Loop</li> <li>4.4 C Model Code</li> <li>4.5 Assembly Implementations</li> </ul> 5 Review of Implementation Techniques 5.1 Inherent Problems 5.1.1 Recurrence Path 5.1.2 While Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | IDE  |                                                                       |    |

| <ul> <li>4.2 Look-Up Table Layout</li> <li>4.3 Implementation</li> <li>4.3.1 Initialization</li> <li>4.3.2 Decoding Loop</li> <li>4.4 C Model Code</li> <li>4.5 Assembly Implementations</li> </ul> 5 Review of Implementation Techniques 5.1 Inherent Problems 5.1.1 Recurrence Path 5.1.2 While Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4 |      |                                                                       |    |

| <ul> <li>4.3 Implementation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |      | •                                                                     |    |

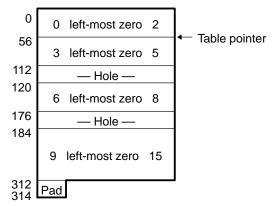

| <ul> <li>4.3.1 Initialization</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |      |                                                                       |    |

| <ul> <li>4.3.2 Decoding Loop</li> <li>4.4 C Model Code</li> <li>4.5 Assembly Implementations</li> <li>5 Review of Implementation Techniques</li> <li>5.1 Inherent Problems</li> <li>5.1.1 Recurrence Path</li> <li>5.1.2 While Loop</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 4.3  | •                                                                     |    |

| <ul> <li>4.4 C Model Code</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      |                                                                       |    |

| <ul> <li>4.5 Assembly Implementations</li> <li>5 Review of Implementation Techniques</li> <li>5.1 Inherent Problems</li> <li>5.1.1 Recurrence Path</li> <li>5.1.2 While Loop</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 11   |                                                                       |    |

| 5 Review of Implementation Techniques<br>5.1 Inherent Problems<br>5.1.1 Recurrence Path<br>5.1.2 While Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |      |                                                                       |    |

| 5.1 Inherent Problems         5.1.1 Recurrence Path         5.1.2 While Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 4.5  |                                                                       |    |

| 5.1 Inherent Problems         5.1.1 Recurrence Path         5.1.2 While Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5 | Rev  | view of Implementation Techniques                                     |    |

| 5.1.1Recurrence Path5.1.2While Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      |                                                                       |    |

| 5.1.2 While Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |      |                                                                       |    |

| 5.2 Look-up Table Lavout and Indexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |      | 5.1.2 While Loop                                                      |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 5.2  | Look-up Table Layout and Indexing                                     | 73 |

|   |     | erences                                                             |    |

|---|-----|---------------------------------------------------------------------|----|

| 6 | Con | clusion                                                             | 75 |

|   | 5.5 | Error Behavior                                                      | 75 |

|   |     | Integrating Run-Length Expansion, Inverse Zigzag and Dequantization |    |

|   |     | 5.3.3 Register Allocation                                           |    |

|   |     | 5.3.2 Bank Conflicts                                                | 74 |

|   |     | 5.3.1 Funtional Unit Bottlenecks                                    |    |

|   | 5.3 | Processor Resources                                                 | 74 |

## List of Figures

| Figure 1. | Typical Image/Video Compression System  | . 4 |

|-----------|-----------------------------------------|-----|

| Figure 2. | Huffman VLD Procedure                   | . 6 |

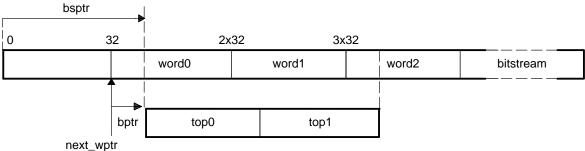

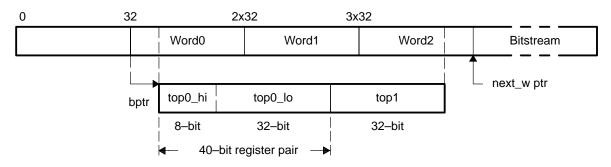

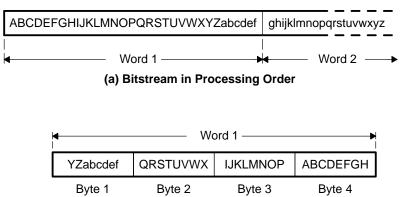

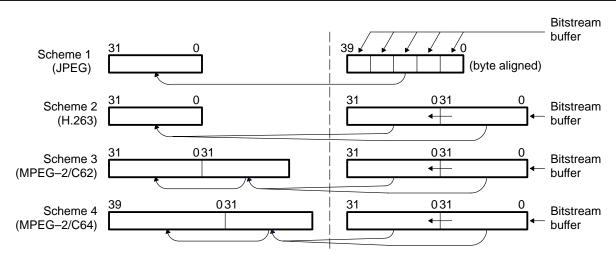

| Figure 3. | Bitstream Buffering                     | 10  |

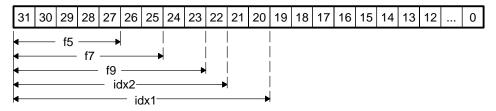

| Figure 4. | Critical Recurrence Path                | 39  |

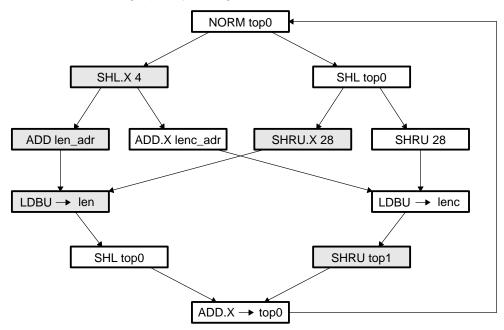

| Figure 5. | Bitstream Management for C64x           | 48  |

| Figure 6. | H.263 Bitstream Organization            | 53  |

| Figure 7. | Classification of a H.263 VLC Code Word | 54  |

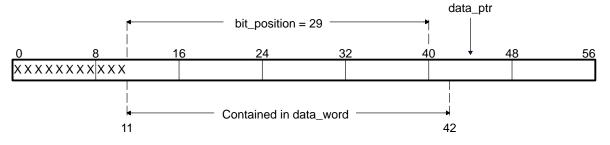

| Figure 8. | JPEG VLD Bitstream Management           | 62  |

| Figure 9. | Structure of JPEG Code Words            | 63  |

| Figure 10 | . JPEG VLD Look-Up Table Layout         | 63  |

| Figure 11 | . Different Bitstream Buffering Schemes | 73  |

## List of Tables

| Table 1  | Example of MPEG-2 VLC Codes and Corresponding RUN-LEVEL Pairs                                                                | . 5 |

|----------|------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2  | MPEG-2 Table B-15 VLC Codes                                                                                                  | 12  |

| Table 3  | Run-Level Look-Up                                                                                                            | 14  |

| Table 4  | Intra DC Decoding for Luminance Blocks (cc = 0, Table B–12)                                                                  | 17  |

| Table 5  | Intra DC Decoding for Chrominance Blocks (cc=1 and cc=2, Table B-13)                                                         | 17  |

| Table 6  | Overlapping Multiple Iterations of the AC Decoding Loop                                                                      | 38  |

| Table 7  | Estimated Number of Stall Cycles Caused by Cold-Cache Misses for Each Data Structure During Decode of One Macroblock on C64x | 52  |

| Table 8  | VLD Performance Comparison on C64x for Flat Memory and Cached-Memory Systems (test bitstream gi_9.m2v)                       | 52  |

| Table 9  | VLD Speculative Reads                                                                                                        | 57  |

| Table 10 | Overview of Problem Areas for VLD Implementations and Their Impact<br>(o = no impact, + = low impact, ++ = high impact)      | 71  |

## 1 Introduction

Variable-length decoding (VLD) is typically one of the most time consuming functions of an image/video decoder, and has therefore been usually implemented in hardware. This application report discusses how VLD routines for JPEG, H.263 and MPEG-2 can be very efficiently implemented in software on the TMS320C6000<sup>™</sup>. Due to the serial nature of the VLD, exploiting parallelism on VLIW-type processors can be challenging. However, good performance can be achieved through careful optimization of the algorithm and integrating it with other decoding functions such as inverse zigzag, dequantization, saturation and mismatch control. For instance, one MPEG-2 non-intra coded macroblock containing 120 coded symbols can be decoded in 1454 cycles on the C64x<sup>™</sup>. Note that the routine fully decodes all coefficients which can then be directly fed into the inverse DCT stage. For decoding a 4 Mbit/s MPEG-2 bitstream and assuming 5 bits per coded symbol, the processor load is only about 1.7% on a 600-MHz C64x device. This level of performance, combined with the flexibility of a software implementation, can be a significant advantage over VLD co-processors.

This section first describes the variable-length decoding process that is commonly used in image and video compression standards and then identifies common implementation problems. The next three sections then present detailed implementation examples for an MPEG-2, H.263, and JPEG VLD routine. The application report finishes with a summary and review of the optimization techniques used in the examples.

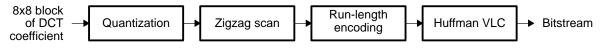

Most standards, such as JPEG, MPEG and H.263 employ the coding procedure shown in Figure 1.

Figure 1. Typical Image/Video Compression System

After run-length encoding, we obtain a pair of values, the number of consecutive zeros (RUN) before the next non-zero quantized DCT coefficient and the magnitude (LEVEL) of that coefficient. Each value pair (also called EVENT) is then assigned a variable-length code word which is obtained through table look-up. The look-up tables (LUT) are specified by the standard, although JPEG also allows user-specified tables. Table 1 shows an extraction of an MPEG-2 VLC table. The attached s denotes the sign of the LEVEL.

TMS320C6000 and C64x are trademarks of Texas Instruments.

| VLC              | Run | Level |

|------------------|-----|-------|

| 10s              | 0   | 1     |

| 010s             | 1   | 1     |

| 110s             | 0   | 2     |

| 0111s            | 0   | 3     |

| 00101s           | 2   | 1     |

| 00110s           | 1   | 2     |

| 11101s           | 0   | 5     |

| 0000100s         | 7   | 1     |

| 0000111s         | 2   | 2     |

| 1111000s         | 9   | 1     |

| 1111100s         | 0   | 9     |

| 00100000s        | 1   | 5     |

| 00100001s        | 11  | 1     |

| 11111011s        | 0   | 13    |

| 11111111s        | 0   | 15    |

| 000000100s       | 5   | 2     |

| 0000001100s      | 2   | 4     |

| 0000001101s      | 16  | 1     |

| 000000011011s    | 26  | 1     |

| 000000011111s    | 22  | 1     |

| 0000000010000s   | 0   | 31    |

| 0000000011111s   | 0   | 16    |

| 00000000010000s  | 0   | 40    |

| 000000000010000s | 1   | 18    |

| 000000000010001s | 1   | 17    |

## Table 1. Example of MPEG-2 VLC Codes and Corresponding RUN-LEVEL Pairs

For less frequently occurring RUN-LEVEL pairs that are not given in the table, the values for RUN and LEVEL are directly inserted in the bitstream, preceded by a special ESCAPE VLC code.

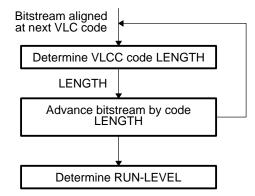

The decoding process follows the reverse flow of the flow shown in Figure 1. A generalized Huffman variable-length decoding (VLD) procedure is shown in Figure 2. First, the length of the VLC code has to be determined, and the bitstream advanced to the next code. Then RUN and LEVEL are obtained through table look-up. The process stops when all symbols of a block have been decoded. The end of a block is typically marked through a special end-of-block (EOB) code.

Figure 2. Huffman VLD Procedure

The procedure is not a typical DSP task, and therefore makes implementation difficult. The amount of instruction-level parallelism that can be exploited is limited due to the serial nature of the decoding loop. That is, before the next VLC code can be decoded, the length of the previous one must first have been determined and the bitstream advanced accordingly. This constitutes a recurrence path in the loop which limits the minimum initiation interval (II) that can be achieved by software pipelining. Furthermore, the number of symbols within a block, and thus the number of iterations, are unknown until an EOB code is detected, i.e., the loop is irregular (WHIILE loop). This further complicates software pipelining, since additional instructions and registers are required to preserve live-out variables.

As can be seen in Figure 2, the length of the recurrence path is determined by how many cycles are required for computing the length of the VLC code, and for advancing the bitstream. It is therefore essential for the overall performance of the VLD function to keep these two tasks as short as possible. Determining the length of the VLC code is commonly done by table look-up. The table layout and the indexing scheme chosen, as well as the way the bitstream buffer is managed affects the length of the recurrence path.

The actual RUN and LEVEL values are determined again through look-up tables. The most basic indexing scheme would be to use the VLC code as index. However, if the longest VLC code is, for instance 16 as it is the case for MPEG-2, the table would have  $2^{16} = 65,536$  entries. This is excessively large and not practical for most implementations. Therefore, the look-up tables have to be compressed by reducing the redundancy contained in Huffman code words. One common way to achieve this is create several sub-tables which group the VLC codes according to their number of leading zeros or ones.

Examples for how look-up tables may be organized, and bitstream buffers may be managed, are given in the next three sections, which discuss VLD implementations for MPEG-2, H.263 and JPEG. Also shown is how performance can be further increased by integrating run-length decoding, inverse zigzag, and dequantization into the VLD loop. This is possible since (due to the serial nature of VLD) many instruction slots remain unused.

The implementations discussed in the following sections are for illustrative purposes, and do not necessarily make use of all possible optimizations. For readers who are interested in only one particular implementation, it is noted that each section is self-contained, and can be followed without reading other sections. Readers who wish to implement a different variable-length decoding routine not specifically discussed in this application report, are referred to section 6, which reviews the implementation techniques used in the various implementations. Also, the section covering MPEG-2 Variable-Length Decoding (section 2) goes into more detail about trade-offs and implementation issues that arise, and how they can be addressed.

# 2 MPEG-2 Variable-Length Decoding

## 2.1 Decoding Process