# TMS320DM6467T Power Consumption Summary

DSPS Applications

#### ABSTRACT

This application report discusses the power consumption of the Texas Instruments TMS320DM6467T digital media System-on-Chip (DMSoC). Power consumption on the DM6467T device is highly application-dependent; therefore, a spreadsheet that estimates power consumption is provided along with this document. To obtain good results from the spreadsheet, realistic usage parameters must be entered (see Section 2.1). The low-core voltage and other power design optimizations allow these devices to operate with industry-leading performance, while maintaining a low power-to-performance ratio.

The data presented in the accompanying spreadsheet was measured from strong units, representative of devices at the maximum end of power consumption for production units. No production units will have average power consumption that exceeds the spreadsheet values; therefore, the spreadsheet values may be used for board thermal analysis and power supply design as a maximum long-term average.

The spreadsheet discussed in this application report can be downloaded from the following URL: <u>http://www.ti.com/lit/zip/SPRAB64</u>.

|              | Core    | Configuration | CPU<br>Frequency | Power (mW) <sup>(1)</sup> |        |       |         |  |

|--------------|---------|---------------|------------------|---------------------------|--------|-------|---------|--|

| Sample       | Voltage |               |                  | Core                      | IO18   | IO33  | Total   |  |

| DM6467TZUT1/ | 1.3 V   | Static        | 0                | 655.22                    | 50.76  | 84.16 | 790.15  |  |

|              |         | Standby       | 33 MHz           | 1038.51                   | 104.09 | 84.16 | 1226.77 |  |

|              |         | DSP+ARM+DDR   | 1 GHz            | 2329.88                   | 385.24 | 84.69 | 2799.82 |  |

### Table 1. Typical Activity

<sup>(1)</sup> Static power consumption varies with process, temperature and voltage. Readings shown here are taken at room temperature (25°C). In standby power consumption, both static and clock in power is considered. In DSP + ARM + DDR power consumption, DSP is running at 1 GHz with 60% utilization ARM is running typical activity, DDR2 is configured at 400 MHz with 50% utilization, 50% writes, 32 bit width, and 50% bit switching.

|   | Contents                               |     |

|---|----------------------------------------|-----|

| 1 | Model Activity                         | 2   |

| 2 | Using the Power Estimation Spreadsheet | 3   |

| 3 | Using The Results                      | 5   |

|   | Example                                |     |

| 5 | Thermal Considerations                 | 7   |

| 6 | Limitations                            | . 9 |

| 7 | References                             | 10  |

|   |                                        |     |

#### List of Figures

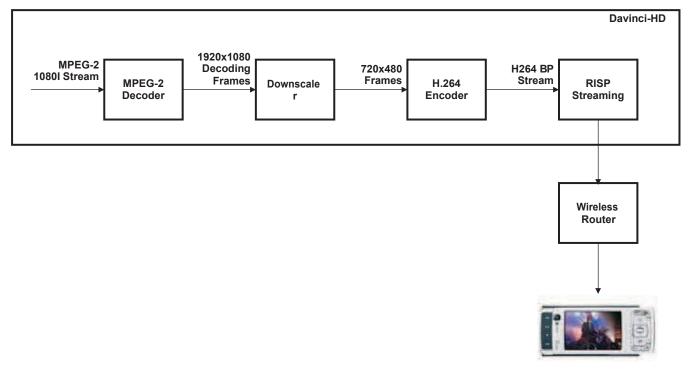

| 1 | Sample Application(s) Block Diagram | . 6 |

|---|-------------------------------------|-----|

| 2 | Heat Sink Example Information       | 9   |

#### List of Tables

| 1 | Typical Activity                                  |   |

|---|---------------------------------------------------|---|

| 2 | Power Consumption of HD-SD Transcoder Application | ' |

### 1 Model Activity

#### 1.1 Activity-Based Models

Power consumption for the TMS320DM6467T can vary widely depending on the use of on-chip resources. Therefore, you cannot estimate power consumption accurately without an understanding of the components of the DMSoC in use and the usage patterns for those components. By providing the usage parameters that describe how and what on the DMSoC is being used, accurate consumption numbers can be obtained for power-supply and thermal analysis.

This model breaks down power consumption into two major components: baseline power and activity power. Using this model, various applications that use the DMSoC differently can get accurate predictions across the spectrum of possible power consumption on the DM6467T.

### 1.2 Baseline Power

Baseline power consumption is power that is independent of chip activity such as static power (leakage), phase-locked loop (PLL), oscillator power, DDR2 DLL consumption, and clock tree power to various subsystem components (e.g., SCR) that cannot be turned off via the on-chip power management module. While independent of chip activity, baseline power is dependent on the device operating frequency, voltage, and temperature. Therefore, you can affect baseline power only by changing the PLL(s) output frequency, the core voltage, or the operating temperature.

### 1.3 Activity Power

Activity consumption is power that is consumed by active parts of the DMSoC: CPU(s), EMIF, peripherals, etc. Activity power is independent of temperature, but dependent on voltage and activity levels. In the spreadsheet, activity power is separated by the major modules within the device. Therefore, the individual module power consumption can be estimated independently; this helps with tailoring power consumption to specific applications. The parameters used to determine the activity level of a module are frequency, utilization, read/write balance, bus size, and switching probability. Note that not all parameters apply to all modules.

- Frequency: The operating frequency of a module or the frequency of external interface to that module.

- Status: Indicates whether the module is in an enabled or disabled state.

- % Utilization: The relative amount of time the module is active or in use versus off or idle.

- % Write: The relative amount of time (considering active time only) the module is transmitting versus receiving.

- Bits: The number of data bits being used in a selectable-width interface.

- % Switch: The probability that any one data bit will change state from one cycle to the next.

Not all modules include all of the parameters.

### 1.4 DM6467T Parts

There are different types of TMS320DM6467T parts available that suit different applications and environment conditions.

- Normal part

- Industrial Temp part (-D parts)

For more details on the part numbers, see the Device Nomenclature in the *TMS320DM6467T Digital Media System-on-Chip Data Manual* (<u>SPRS605</u>).

**Normal** Parts operate at 1.3 V core voltage and up to 1 GHz core frequency under 0°C to 85°C case temperature.

Industrial Temp parts operate up to 1 GHz core frequency under -40°C to 85°C case temperature.

VLYNQ, C64x+, C6000 are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

## 1.5 Modules

The DM6467T power estimation spreadsheet contains the following modules with adjustable parameters:

Using the Power Estimation Spreadsheet

- Digital Signal Processor (DSP)

- ARM MM (megamodule) (see Section 6)

- High-Definition Video Image Co-Processor (HDVICP) (0 and 1)

- Video Data Conversion Engine (VDCE)

- Video Port Interface (VPIF) (display and capture)

- Transport Stream Interface (TSIF) (0 and 1)

- DDR2 Memory Controller

- External Memory Interfaces (EMIFA)

- Ethernet Media Access Controller (EMAC)

- AT Attachment (ATA)

- VLYNQ<sup>™</sup>

- Universal Serial Bus (USB) 2.0 (see Section 6 for limitations)

- Peripheral Component Interconnect (PCI)

- Universal Host Port Interface (UHPI)

- Multichannel Audio Serial Port (McASP) (0 and 1)

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I2C)

- Timer (0 and 1)

- Watchdog Timer (WDT)

- Pulse Width Modulator (PWM) (0 and 1)

- Universal Asynchronous Receiver/Transmitter (UART) (0, 1 and 2)

- General-Purpose Input/Output (GPIO)

- Enhanced Direct Memory Access (EDMA3)

The EDMA3 activity power is included in the activity power of the module/peripheral serviced by the EDMA3; this includes McASP, SPI, UART, I2C, EMIFA, and DDR2.

# 2 Using the Power Estimation Spreadsheet

The power estimation spreadsheet involves entering the appropriate usage parameters as input data in the spreadsheet. Cells that are designed for user input are white in color. The following steps explain how to use the spreadsheet:

- 1. Choose the case temperature for the estimated power

- 2. Fill in the appropriate module use parameters

The spreadsheet takes the provided information and displays the details of power consumption for the chosen configuration.

As the spreadsheet is being configured, the settings are checked for conflicts, e.g., peripheral clock frequency out of allowed range, etc. For best results, enter the information from left to right starting at the top and moving downward.

# 2.1 Choosing Appropriate Values

The frequency and bit user values are determined by design and it will be clear what the correct values to enter are. For some modules, the frequency field is used to input the data rates (for instance, ATA, EMAC, etc). In order to choose appropriate values, you need a good understanding of read/write balance, bit switching required estimation, and utilization of the user application. You should also keep in mind the pin multiplexing configuration for the device to avoid enabling mutually exclusive peripherals/configurations at the same time. For available peripherals and peripheral configuration, see the device-specific data manual.

#### 2.1.1 Utilization

For modules except DSP, C64x+<sup>™</sup> and VCIP, utilization is simply the percentage of time the module spends doing something useful, versus being unused or idle. For these peripherals, there are not various degrees of use, so the value is just an average over time. For example, the EMIF performs reads and writes one-quarter of the time and has no data to move for the other three-quarters of the time (though it continues to perform background tasks like refresh); this would be 25% utilization.

For peripherals with I/O, utilization can be estimated by comparing used bandwidth with theoretical maximum bandwidth. If, for example, an application must transfer 160 Kb/s via the I2C port, with a theoretical 400 Kb/s maximum, the I2C port utilization would be about 40%. Similarly for ATA, when the DM6467T is running at 1 GHz, the max theoretical bandwidth possible is 99 Mbytes/sec in UDMA5 mode, so for an application using UDMA4 mode (expected bandwidth of around 66 Mbytes/sec), the % utilization would be 66.6%. In some cases, the max bandwidth allowed may be dependent on the device (SYSCLK1) frequency; factor this while calculating the utilization if doing the estimation at different device frequencies.

The CPU utilization is not as straightforward because there are varying degrees of use for the CPU. Here, 0% utilization means the CPU is active and does no useful work (NOP execution), where 100% utilization means all eight functional units are active every cycle and the maximum amount of data is brought in from L1P and L1D every cycle. Few DSP algorithms achieve 100% utilization because this requires everything to be used every cycle with no stalls. Even intense applications do not spend all of the time in such highly parallel loops. Time is typically also spent executing control code or less demanding algorithms. These types of code may execute only a few instructions in parallel and significantly reduce the I/O of the CPU, thus, reducing overall utilization. Since you must consider the balance of CPU use for the application, entering 100% utilization is not practical for real applications.

For example, an application that executes very dense CPU code (estimated at 90% of CPU capability) half of the time, and for the other half low activity, like waiting for commands from ARM along with some other house keeping activities (estimated at 10% of CPU capability), this application would have an average utilization of about 50% ( $10\% \times 50\% + 90\% \times 50\%$ ). If the balance were changed to 25% low activity code and 75% DSP code, the weighted average would be about 70% utilization ( $25\% \times 10\% + 90\% \times 75\%$ ). If the 25%/75% ratio is kept, but the DSP code does not fully use all the CPU resources (estimate now at 75% of CPU capability), then the overall utilization returns to about 59% ( $25\% \times 10\% + 75\% \times 75\%$ ). An estimate of the overall CPU utilization can be obtained by using estimates of intensity and duration of blocks of code in the application.

System level issues may also reduce utilization. Though the spreadsheet accepts 100% utilization for all peripherals, this is not possible in reality. As concurrency in data movement increases and/or throughput requirements on high bandwidth modules (system DMA, VPIF, etc.,) increases, overall peripheral activity is throttled back due to bottlenecks created at various common end points. In such cases, peripherals might not achieve 100% utilization; therefore, you should enter individual module utilization numbers keeping this overall limitation in mind.

### 2.1.2 % Writes

Peripherals that transmit as much data as they receive have 50% writes; the spreadsheet assumes the remaining 50% of the time is spent on reads. In some applications, peripherals move data in only one direction, or have a known balance of data movement. In these cases, % writes should be changed to 0%, 100%, or the known ratio as appropriate for the cases when the DMSoC is reading all the time, writing all the time, or a combination of the two, respectively. Otherwise, 50% is a typical number that should be used.

### 2.1.3 % Switching

4

Random data has a 50% chance any bit will change from one cycle to the next. Some applications may be able to predict this chance using a priori information about the data set. If there is a property of the algorithm that allows prediction of the bit changes, the application-specific probability can be used. All other applications should use the default number of 50%.

# 2.2 Peripheral Enabling and Disabling

As mentioned previously, the DM6467T device provides the capability to disable modules that are not being used via the power sleep controller (PSC). When a peripheral is disabled, its clock is turned off reducing the power consumption of the device.

The spreadsheet accommodates this power saving feature by including fields from which a peripheral can be specified as disabled or enabled.

If a module is not used for a given application, then it is recommended to keep it in disabled state.

It is possible that the module is kept enabled but has no activity. To achieved this, program the % utilization and/or the frequency fields to a value of 0, then the numbers in the module's row will be indicative of the power consumed by clocking the module.

The DSP spreadsheet provides three states:

- Disabled: Indicates the DSP power domain OFF (DSP Subsystem clock gated off). This is also the default power-on reset condition in the Host-boot mode or DSP\_BT =0 (see the TMS320DM6467T Digital Media System-on-Chip Data Manual (SPRS605) referred to as the DM6467T data manual throughout the remainder of this document).

- Idled: Indicates the DSP-sleep mode using the C64x+ internal power down controller (PDC)

- Active: Indicates the DSP state when it is not idled or powered down, you should put appropriate % utilization in this mode.

If DDR2 is enabled, then power estimation considers both DDR2 and PLL2 power; otherwise, it is assumed that the PLL2 is powered down and is operating in bypass mode with the DDR2 clock being directly fed by the input reference clock (33 MHz CLKIN).

If an application requires the use of VPIF, video data conversion engine (VDCE) and/or two TSIF modules in the system, this automatically implies that DDR2 is also enabled and active in the system. To estimate power for such scenarios, you need to make sure that the DDR2 fields are programmed with appropriate frequency and utilization, read/write percentage, etc., required by these modules.

# 2.3 Graphs

The output/results graphs in the spreadsheet provide a visual breakdown of the power consumption. A comparison is also provided of active power (based on the parameters supplied) and the baseline power, and pie charts show the relative contributions of each peripheral to the core and I/O power consumption.

The case temperature measurement spreadsheet shows worst case. Case temperature for an application and the heat sink calculation spreadsheet shows thermal impact adding a heat sink.

# 3 Using The Results

The intent of the power estimation spreadsheet is to provide estimates of the upper bounds in an application-specific loading and peripheral utilization scenario. The measured units were selected to be a strong unit at the maximum end of power consumption for production units. No production units will have average power consumption that exceeds the spreadsheet values; therefore, the spreadsheet data may be considered maximum average power consumption; the actual observed power may vary. That is, transient currents may cause power to spike above the spreadsheet value for a small amount of time; however, over a long period, the observed average consumption will be below the spreadsheet value. The spreadsheet value may be used for board thermal analysis and power supply design as a maximum long-term average.

### 3.1 Adjusting I/O Power Results

I/O power is dependent not only on the device and activity, but also the load being driven. For loads with CMOS inputs, the power required to drive the trace dominates, and is a better measure of load than the number of inputs or lumped load capacitance. If the target system has very different I/O loading, scale the spreadsheet results either up or down to compensate. For this reason, the spreadsheet allows you to specify the approximate load on the I/O pins for each module by using the trace length field. This parameter is used to adjust the reported I/O power numbers.

Example

### 4 Example

The following examples demonstrate how to choose appropriate values for a particular application. These values may be imported into the spreadsheet by clicking the appropriate macro button.

# 4.1 Basic Configuration(s)

The *Static* macro button reports the static power for the device, when the MXI/CLKIN is cut off and voltage is applied to the various core and I/O rails

The *Standby* macro button reports the power consumed with the 33 MHz CLKIN. PLL1 is powered down/disabled and the system is operating in bypass mode with the CLKIN as the system clock. PLL2 is also powered down/disabled and is operating in bypass mode with the CLKIN passed through to DDR2 clock. The ARM is in the *wait for interrupt* sleep mode, the DSP subsystem power domain is OFF and all peripherals are disabled.

The macro button *1 GHz* can be used to quickly visualize the power number details at DSP 1 GHz, ARM 500 MHz and DDR-400 MHz shown in Table 1.

# 4.2 Sample Application(s)

The Sample Application macro button reports the power consumed by the transcoding application. This application transcodes MPEG-2 HD into H.264 BP and streams these to a Wireless LAN enabled cell phone. HDVICP1 reads in a MPEG-2 1080i from a hard disk and decodes the MPEG-2 data content, VDCE scales it down to 480p and then HDVICP0 encodes it to H.264 BP. The transcoded stream is streamed out to a wireless LAN using RTSP protocol through EMAC. The cell phone receives the wireless stream and plays it using RealPlayer. Figure 1 shows a block diagram of this application.

**NOTE:** In *Static* configuration, a *finite* current component is shown on the I/O rails (DV<sub>DD18</sub> and DV<sub>DD33</sub>), these values are system dependent and will differ (could be lower or higher) based on the state of pull up or pull downs and load on the device I/O lines.

The details of the peripherals used in this application are:

- Voltage: 1.3 V (CV<sub>DD</sub> and CV<sub>DDDSP</sub>)

- Case temperature: 55°C

- CLKIN: 33 MHz

- ARM: Typical activity that involves configuring peripheral and other house keeping activities

- DSP: 1 GHz, 30% utilization. Estimation based on the following factors:

- Background activities (waiting for commands from ARM, polling for response from HDVICP)

- HDVICP0: Enabled, 35% utilization

- HDVICP1: Enabled, 35% utilization

- VDCE: Enabled, 20% utilization

- DDR: Enabled, 20% utilization, 50% writes, 32% switching

- EMAC: Enabled, configured for 100 Mbps, 30% utilization

- · All other modules are not used and disabled

Table 2 shows the approximate power estimation of this application calculated using the power spreadsheet.

### Table 2. Power Consumption of HD-SD Transcoder Application

|                                | Power (Watts) |                |        |        |        |           |

|--------------------------------|---------------|----------------|--------|--------|--------|-----------|

| Core Voltage (V) CPU Frequency |               | Core IO18 IO33 |        |        | Total  | Case Temp |

| 1.3                            | 1 GHz         | 3.4510         | 0.3413 | 0.0991 | 3.8914 | 55°C      |

# 5 Thermal Considerations

As integrated circuit (IC) components become more complex, the challenge of producing an end equipment product with good thermal performance also increases. Thermal performance is a system level concern, impacted by IC packaging as well as printed circuit board (PCB) design, PCB characteristics, PCB layout, ambient temperature, and chassis configuration.

In the *TMS320DM6467T Digital Media System-on-Chip Data Manual* (<u>SPRS605</u>), TI specifies not to exceed the maximum operating junction temperature so that device reliability and/or proper operation can be maintained. To meet this requirement, it is important to understand the contribution of the other system characteristics (mentioned above) and design accordingly. Before finalizing system layout and PCB design, verify that the maximum operating junction temperature documented in the DM6467T data manual is met.

This section addresses the thermal considerations specific to the DM6467T device and should be used in conjunction with the *Thermal Considerations for TMS320DM64xx, TMS320DM64x, and TMS320C6000 Devices* (SPRAAL9). The *Thermal Considerations for TMS320DM64xx, TMS320DM64x, and TMS320C6000 Devices* (SPRAAL9) discusses many general thermal considerations that apply to DM64xx, DM64x, and C6000<sup>™</sup> DSP devices. For more information regarding definitions of thermal terms, methods for calculating case temperature, recommendations for system thermal improvements, heat sink recommendations, and heat sink attachment methods, see the *Thermal Considerations for TMS320DM64xx, TMS320DM64xx, TMS320DM64xx, TMS320DM64xx, and TMS320C6000 Devices* (SPRAAL9).

One of the most commonly considered thermal improvement methods is the heat sink. A numerical approach that estimates the thermal impact of adding an off the shelf heat sink purchased from a vendor is shown below. This method requires ambient temperature, case temperature, and DM6467T power to be either measured or estimated without a heat sink in the real system. To be consistent with JEDEC measurement techniques, as well as to reference the most independent and static temperature point, TI recommends measuring the final system ambient temperature outside the enclosure; the inside the enclosure may be influenced by heating from other parts.

The spreadsheet that accompanies this application report includes a worksheet that performs the calculations described in the following heat dissipation examples. You must enter values for the following fields in the worksheet: package type, ambient temperature, case temperature, total power, and  $\theta_{CA}$  from a heat sink data sheet. All of the remaining fields in the worksheet are calculated based on your inputs.

Thermal Considerations

www.ti.com

# 5.1 Thermal Heat Dissipation Example for the ZUT Package

Numbers for an actual application need to be calculated. From system analysis, suppose you determine:

- Ambient temperature: T<sub>A</sub> = 25°C

- Case temperature: T<sub>C</sub> = 70°C

- Device power = 2.0 W

**NOTE:** This is a reasonable example, but your specific information is required.

This is a reasonable example, but your specific information is required.

Calculate an estimate of θ<sub>JA,effective</sub> using the following equation. Plug in values for ambient temperature, case temperature and device power from the list above. For the DM6467T, Ψ<sub>JT</sub> = 0.3 °C/W at 0 m/s air flow. Ψ<sub>JT</sub> is documented in the *TMS320DM6467T Digital Media System-on-Chip Data Manual* (SPRS605).

$$T_{J} = T_{C} + \left(Power \xi \parallel_{JT}\right) = 70 + \frac{2.0W}{1} \xi 0.3 \frac{^{\circ}C}{W} = 70.60 \ ^{\circ}C$$

$$\Sigma_{JA, \text{ effective }} = \frac{T_{J} - T_{A}}{Power} = \frac{70.60 - 25}{2} = 22.8 \ \frac{^{\circ}C}{W}$$

2. Estimate the percentage of heat flowing through the PCB vs. the top of the device. Based on experience with typical systems, TI estimates 80% of the heat flow is through the PCB, without a heat sink attached. The thermal resistance through the top and bottom of the device are two parallel resistances that equal  $\theta_{JA,effective}$  (see Figure 2). Therefore,  $\theta_{top}$  and  $\theta_{bot}$  can be defined as follows:

$$\frac{80\%}{20\%} = 4 \text{ therefore, } 0_{\text{top}} = 4 \xi 0_{\text{bot}}$$

$$0 \text{JA, effective} = \frac{1}{\frac{1}{0 \text{top}} + \frac{1}{0 \text{bpt}}} = \frac{1}{\frac{1}{40 \text{bot}} + \frac{1}{0 \text{bot}}}$$

$$1.25 \xi 0 \text{JA, effective} = 0 \text{bot} = \frac{1}{\frac{\xi}{4}} 0 \text{top}$$

$$5 \xi 0 \text{JA, effective} = 0 \text{top}$$

Use the following equations to calculate  $\theta_{top}$  and  $\theta_{bot}$ :

<sup>8</sup>top = <sup>8</sup>JA, effective

$$\xi$$

5 = 22.8  $\xi$  5 = 114  $\frac{^{\circ}C}{W}$

<sup>8</sup>bot = <sup>8</sup>JA, effective  $\xi$  1.25 = 22.8  $\xi$  1.25 = 28.5  $\frac{^{\circ}C}{W}$

Check by calculating the parallel resistance of  $\theta_{top}$  and  $\theta_{bot}$ .

TMS320DM6467T Power Consumption Summary

<sup>8</sup>JA, effective =

$$\frac{1}{\frac{1}{8 \text{top}} + \frac{1}{8 \text{bot}}} = \frac{1}{\frac{1}{114} + \frac{1}{28.5}} = 22.8 \frac{\text{°C}}{\text{W}}$$

3. Use the following equation to estimate the thermal resistance from the top of the DM6467T to the environment. This thermal resistance is called  $\theta_{CA}$  (see Figure 2). For the DM6467T,  $\theta_{JC}$  = 1.5 °C/W.  $\theta_{JC}$  is documented in the *TMS320DM6467T Digital Media System-on-Chip Data Manual* (SPRS605).

$$8CA = 8_{top} (step2) - 8_{JC} = 114 - 1.5 = 112.5 \frac{C}{W}$$

4. Replace  $\theta_{CA}$ , calculated in step 3, with  $\theta_{CA}$  specified from a heat sink data sheet and then recalculate the heat flow through the top of the device with a heat sink added. Note that  $\theta_{CA}$  and  $\theta_{top}$  should be reduced with the addition of a heat sink.

For this example we chose a heat sink with  $\theta_{CA} = 62.5 \text{ °C/W}$  (for example heat sink).

|      | Width    | Length   | Height  | Fin<br>Thickness<br>Across<br>Width | Fin<br>Thickness<br>Across<br>Length | Base<br>Thickness | # of Fins<br>Across<br>Width | # of Fins<br>Across<br>Length |

|------|----------|----------|---------|-------------------------------------|--------------------------------------|-------------------|------------------------------|-------------------------------|

| alte | 15.20 mm | 15.20 mm | 6.35 mm | 0.89 mm                             | 0.89 mm                              | 1.52 mm           | 8                            | 8                             |

Figure 2. Heat Sink Example Information

$$8_{top} (w / HS) = 8_{CA} (from HS) + 8_{JC} = 62.5 + 1.5 = 64.0 \frac{C}{W}$$

5. Calculate the new  $\theta_{JA,\text{effective}}$  with a heat sink as well as the improved  $T_{C}.$

<sup>8</sup>JA, effective =

$$\frac{1}{\frac{1}{8 \text{top}} + \frac{1}{8 \text{bot}}}$$

<sup>8</sup>JA, effective (w / HS)=  $\frac{1}{\frac{1}{64} + \frac{1}{28.5}}$  = 19.72  $\frac{^{\circ}\text{C}}{\text{W}}$

The new TC with heat sink can be calculated as follows:

$$T_{J} = T_{A} + (Power \xi \epsilon_{JA}, effective}) = 25 + (2.0 \xi 19.72) = 64.44 \ ^{\circ}C$$

The heat sink in this application is estimated to improve the junction temperature from a value of 70.60°C to a value of 74.44°C.

**NOTE:** This example uses published data from an off-the-shelf heat sink. The same type of method can be used to estimate the impact of using a chassis as a heat sink, but the calculation is more difficult because this is not published data.

# 6 Limitations

The current implementation of the power estimation spreadsheet has the following limitations:

- ARM CPU power representation and reporting: ARM mega module power consumption estimation does not follow the traditional CPU usage parameters (like the DSP), and is currently broken into three main categories

- Sleep Mode: Special wait-for-interrupt sleep mode

- Low Activity: This is representative of ARM just performing low activity instructions (NOPs, etc.)

- Typical Activity: This is representative of ARM performing typical activity, which would include peripheral configurations, load/stores and other house keeping activities (waiting for transfer completions, interrupts, etc.)

- USB2.0 Power representation: The USB2.0 module power consumption is based on modeled estimates and not actual measurements. Currently, the spreadsheet just allows you to estimate the core power consumed on enabling the USB2.0 module via PSC (and variations with device frequency). For USB /IO power, typical worst case *expected* numbers are provided for different usage modes (high-speed receive/transmit and full-speed receive/transmit).

- All measurements have been performed with a 33 MHz CLKIN provided by an external oscillator. The spreadsheet does not provide a capability of estimating power based on a different CLKIN value.

References

www.ti.com

# 7 References

- TMS320DM6467TDigital Media System-on-Chip Data Manual (SPRS605)

- TMS320DM646x DMSoC DSP Subsystem Reference Guide (SPRUEP8 )

- TMS320C64x+ DSP Megamodule Reference Guide (<u>SPRU871</u>)

- TMS320DM644x Power Consumption Summary (<u>SPRAAD6</u>)

- Thermal Considerations for TMS320DM64xx, TMS320DM64x, and TMS320C6000 Devices (SPRAAL9)

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated