SPRT489-OCTOBER 2008 www.ti.com

#### **Key Message**

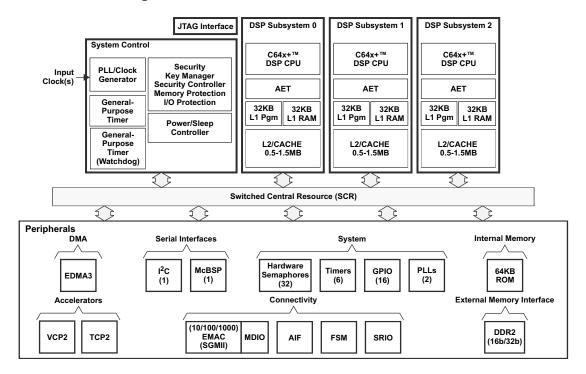

The TMS320C6474 DSP integrates three 1-GHz C64x+ DSP CPU cores, a host of high-speed peripherals, and large amounts of internal memory in a compact 23 mm by 23 mm package. These features allow the C6474 device to provide significant performance integration and high-performance density, along with substantial efficiencies in power, cost, and board space.

#### 1.1 Key Features

- **High-Performance Multicore DSP (C6474)**

- 1-ns Instruction Cycle Time

- 1.0-GHz Clock Rate

- Eight 32-Bit Instructions/Cycle

- Commercial Temperature 0°C to 100°C

- 3 TMS320C64x+™ DSP Cores

- Dedicated SPLOOP Instructions

- Compact Instructions (16-Bit)

- Exception Handling

- TMS320C64x+ Megamodule L1/L2 Memory Architecture

- 256 K-Bit (32 K-Byte) L1P Program Cache [Direct Mapped]

- 256 K-Bit (32 K-Byte) L1D Data Cache [2-Way Set-Associative]

- 24 M-Bit (3072 K-Byte) Total L2 Unified Mapped RAM/Cache [Flexible Allocation]

- Configurable at boot-time to 1 MB/ 1 MB/1 MB or 1.5 MB/1 MB/0.5 MB

- 512 K-Bit (64 K-Byte) L3 ROM

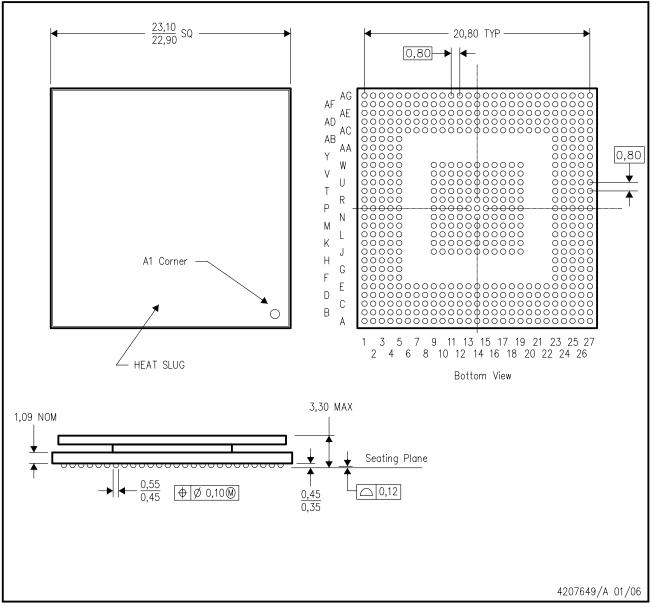

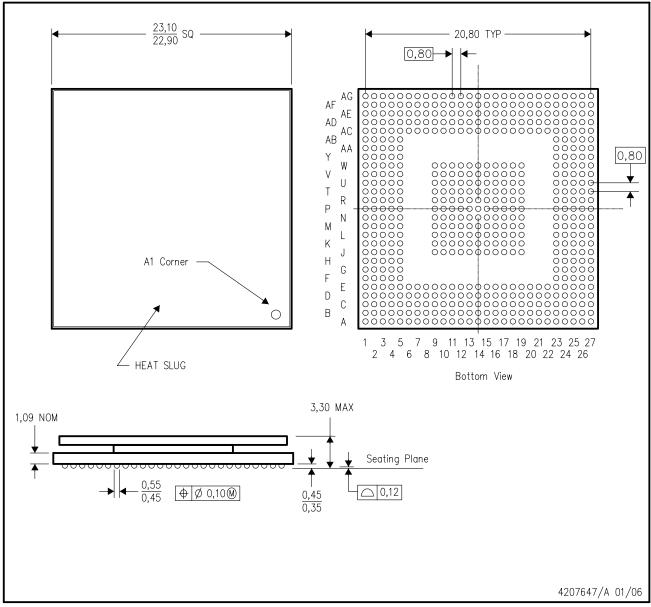

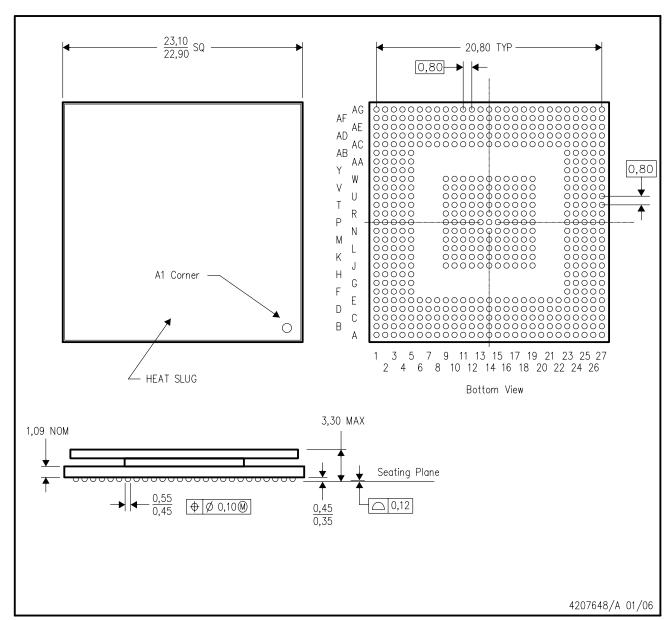

- 561-Pin Ball Grid Array (BGA) Packages (CUN, GUN, or ZUN Suffix), 0.8-mm Ball Pitch

- SmartReflex™ Class 0 Enabled 0.9-V to 1.2-V Adaptive Core Voltage

- **Applications: Range from Communications** Infrastructure/Basestations to Medical/High-Performance Imaging and Military/Aerospace/Avionics

#### 1.2 Functional Block Diagram

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this document.

All trademarks are the property of their respective owners.

Texas Instruments

# 2 Peripherals

2

#### **Table 2-1. Peripheral Description**

| PERIPHERALS                                                     | NO. | DESCRIPTION                                                                                                                         |

|-----------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------|

| EMIF DDR2 Controller                                            | 1   | 32-bit or 16-bit DDR2-667 with 512MB address space.                                                                                 |

| Enhanced DMA 3.0 [EDMA3]                                        | 1   | 64 independent channels, 8 Quick DMA (QDMA) channels, 6 transfer controllers. Programmable burst size.                              |

| 10/100/1000 Ethernet MAC [EMAC] with Management Data I/O [MDIO] | 1   | SGMII interface. IEEE 802.3 compliant.                                                                                              |

| Serial RapidIO® [SRIO]                                          | 1   | Two 1x links. Conforms to RapidIO® Interconnect Specification, Part VI: Physical Layer 1x/4x LP-Serial Specification, Revision 1.2. |

| Viterbi Decoder Coprocessor [VCP2]                              | 1   | Significantly speeds up channel-decoding operations on-chip. Flexible polynomials, can generate hard or soft decisions.             |

| Turbo Decoder Coprocessor [TCP2]                                | 1   | Implements Max*-Log-MAP, Max-Log-MAP algorithms. Supports requirements of Third-Generation Partnership Projects (3GPP).             |

| Antenna Interface [AIF]                                         | 1   | Six lanes of high-speed differential serial interface to system devices including other processors and/or antenna modules.          |

| Frame Synchronization Module [FSM]                              | 1   | Contains multiple timer/counters generates system timing references for AIF and related EDMA3 synchronization.                      |

| Multichannel Buffered Serial Port [McBSP]                       | 2   | Compatible with multiple industry standards. FIFO buffer for transmit/receive. Multichannel mode handles 128 channels.              |

| I2C Interface                                                   | 1   | With master/slave operation that supports up to 400 Kbps.                                                                           |

| Hardware Semaphores                                             | 1   | Implements 32 independent general-purpose semaphore resources.                                                                      |

| General-Purpose Timers                                          | 6   | 64-bit general-purpose timers, each also configurable as 2 separate 32-bit timers, or as a watchdog timer.                          |

| General-Purpose Input/Output [GPIO]<br>Port                     | 1   | Up to 16 general-purpose input/output pins.                                                                                         |

| PLL Clock Generators                                            | 2   | PLL1 supplies clocks to device logic other than DDR2 controller, PLL2 supplies clocks to DDR2 controller.                           |

### TMS320C6474 Multicore Digital Signal Processor Technical Brief

www.ti.com SPRT489-OCTOBER 2008

#### 3 Key Electrical Characteristics

|                        |                                                                                                      |                                         | MIN                                        | NOM                      | MAX                       | UNIT |

|------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------|--------------------------|---------------------------|------|

| CV <sub>DD</sub>       | Supply core voltage (sca                                                                             | alable)                                 | CV <sub>DD</sub> - (0.03CV <sub>DD</sub> ) | 0.9 - 1.2                | $CV_{DD} + (0.03CV_{DD})$ | V    |

| DV <sub>DD11</sub>     | 1.1-V supply core I/O vo                                                                             | ltage                                   | 1.045                                      | 1.1                      | 1.155                     | V    |

| DV <sub>DD18</sub>     | 1.8-V supply I/O voltage                                                                             |                                         | 1.71                                       | 1.8                      | 1.89                      | V    |

| V <sub>REFSSTL</sub>   | DDR2 reference voltage                                                                               |                                         | 0.49 * DV <sub>DD18</sub>                  | 0.5 * DV <sub>DD18</sub> | 0.51 * DV <sub>DD18</sub> | V    |

| AIF_V <sub>DDA11</sub> | AIF SERDES analog su                                                                                 | pply                                    | 1.045                                      | 1.1                      | 1.155                     | V    |

| AIF_V <sub>DDD11</sub> | AIF SERDES digital sup                                                                               | ply                                     | 1.045                                      | 1.1                      | 1.155                     | V    |

| AIF_V <sub>DDR18</sub> | AIF SERDES regulator s                                                                               | supply                                  | 1.71                                       | 1.8                      | 1.89                      | V    |

| AIF_V <sub>DDT11</sub> | AIF SERDES terminatio                                                                                | n supply                                | 1.045                                      | 1.1                      | 1.155                     | V    |

| SGR_V <sub>DDA11</sub> | SRIO/SGMII SERDES a                                                                                  | nalog supply                            | 1.045                                      | 1.1                      | 1.155                     | V    |

| SGR_V <sub>DDD11</sub> | SRIO/SGMII SERDES d                                                                                  | ligital supply                          | 1.045                                      | 1.1                      | 1.155                     | V    |

| SGR_V <sub>DDR18</sub> | SRIO/SGMII SERDES regulator supply                                                                   |                                         | 1.71                                       | 1.8                      | 1.89                      | V    |

| SGR_V <sub>DDT11</sub> | SRIO/SGMII SERDES termination supply                                                                 |                                         | 1.045                                      | 1.1                      | 1.155                     | V    |

| AV <sub>DD118</sub>    | PLL1 analog supply                                                                                   |                                         | 1.71                                       | 1.8                      | 1.89                      | V    |

| AV <sub>DD218</sub>    | PLL2 analog supply                                                                                   |                                         | 1.71                                       | 1.8                      | 1.89                      | V    |

| V <sub>SS</sub>        | Ground                                                                                               |                                         | 0                                          | 0                        | 0                         | V    |

| P <sub>Tot</sub>       | Total Power<br>Consumption.<br>Includes static and<br>active power for both<br>Core and I/O supplies | Use Case 1: DSP CPU operating at 1 GHz. |                                            | 6                        |                           | W    |

| T <sub>C</sub>         | Operating case temperature range                                                                     |                                         | 0                                          |                          | 100                       | °C   |

| F <sub>CPU</sub>       | DSP Operating Frequency                                                                              |                                         | 0                                          |                          | 1000                      | MHz  |

#### 3.1 Power Use Case Details

• Use Case 1: At 70°C, 1-GHz CPU frequency, 75% CPU usage, 50% 32-bit DDR2 usage at 667 MHz, 100% usage of both McBSPs, 75% usage of six timers, and 50% usage of both lanes of SRIO. The actual current draw varies across manufacturing processes and is highly application dependent.

#### 4 Tools and Software Support

The C6474 device is supported by the following tools and software:

- Code Composer Studio<sup>™</sup> 3.3

- DSP/BIOS™ 5.3

- DSP/BIOS™ 5.3-based Peripheral Device Drivers

- DSP Chip Support Library (CSL)

- TMS320C6474 Evaluation Module (EVM)

SPRT489-OCTOBER 2008 www.ti.com

#### 5 Mechanical Drawing

### CUN (S-PBGA-N561)

#### PLASTIC BALL GRID ARRAY

Instruments

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Thermally enhanced plastic package with heat slug (HSL).

- D. Flip chip application only.

- E. Lead-free die bump and solder ball.

www.ti.com

## GUN (S-PBGA-N561)

#### PLASTIC BALL GRID ARRAY

NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Thermally enhanced plastic package with heat slug (HSL).

- Flip chip application only. D.

- E. Leaded (Pb) solder balls.

SPRT489-OCTOBER 2008 www.ti.com

# ZUN (S-PBGA-N561)

# Instruments

PLASTIC BALL GRID ARRAY

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Thermally enhanced plastic package with heat slug (HSL).

- D. Flip chip application only.

- E. This package is lead-free.

- F. This package has lead-free solder balls and leaded (Pb) die bumps.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### **Products Amplifiers** amplifier.ti.com Data Converters dataconverter.ti.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mgmt power.ti.com Microcontrollers microcontroller.ti.com www.ti-rfid.com RF/IF and ZigBee® Solutions www.ti.com/lprf

| Applications       |                           |

|--------------------|---------------------------|

| Audio              | www.ti.com/audio          |

| Automotive         | www.ti.com/automotive     |

| Broadband          | www.ti.com/broadband      |

| Digital Control    | www.ti.com/digitalcontrol |

| Medical            | www.ti.com/medical        |

| Military           | www.ti.com/military       |

| Optical Networking | www.ti.com/opticalnetwork |

| Security           | www.ti.com/security       |

| Telephony          | www.ti.com/telephony      |

| Video & Imaging    | www.ti.com/video          |

| Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated